#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                  |

|---------------------------------|-----------------------------------------------------------|

| Core Processor                  | PowerPC e500                                              |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                            |

| Speed                           | 800MHz                                                    |

| Co-Processors/DSP               | Signal Processing; SPE                                    |

| RAM Controllers                 | DDR, DDR2, SDRAM                                          |

| Graphics Acceleration           | No                                                        |

| Display & Interface Controllers | -                                                         |

| Ethernet                        | 10/100/1000Mbps (4)                                       |

| SATA                            | -                                                         |

| USB                             | -                                                         |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                          |

| Operating Temperature           | 0°C ~ 105°C (TA)                                          |

| Security Features               | -                                                         |

| Package / Case                  | 783-BBGA, FCBGA                                           |

| Supplier Device Package         | 783-FCBGA (29x29)                                         |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8543vuang |

|                                 |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## NOTE

From a system standpoint, if any of the I/O power supplies ramp prior to the  $V_{DD}$  core supply, the I/Os associated with that I/O supply may drive a logic one or zero during power-up, and extra current may be drawn by the device.

Table 13 provides the recommended operating conditions for the DDR SDRAM controller when  $GV_{DD}(typ) = 2.5 \text{ V}.$

| Parameter/Condition                             | Symbol            | Min                      | Max                      | Unit | Notes |

|-------------------------------------------------|-------------------|--------------------------|--------------------------|------|-------|

| I/O supply voltage                              | GV <sub>DD</sub>  | 2.375                    | 2.625                    | V    | 1     |

| I/O reference voltage                           | MV <sub>REF</sub> | $0.49 \times GV_{DD}$    | $0.51 	imes GV_{DD}$     | V    | 2     |

| I/O termination voltage                         | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04 | MV <sub>REF</sub> + 0.04 | V    | 3     |

| Input high voltage                              | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.15 | GV <sub>DD</sub> + 0.3   | V    | —     |

| Input low voltage                               | V <sub>IL</sub>   | -0.3                     | MV <sub>REF</sub> – 0.15 | V    | —     |

| Output leakage current                          | I <sub>OZ</sub>   | -50                      | 50                       | μΑ   | 4     |

| Output high current (V <sub>OUT</sub> = 1.95 V) | I <sub>OH</sub>   | -16.2                    | —                        | mA   | —     |

| Output low current (V <sub>OUT</sub> = 0.35 V)  | I <sub>OL</sub>   | 16.2                     | —                        | mA   | —     |

| Table 13. DDR SDRAM DC Electrical | Characteristics for $GV_{DD}(typ) = 2.5 V$ |

|-----------------------------------|--------------------------------------------|

|                                   |                                            |

#### Notes:

1.  ${\rm GV}_{\rm DD}$  is expected to be within 50 mV of the DRAM  ${\rm V}_{\rm DD}$  at all times.

2. MV<sub>REF</sub> is expected to be equal to 0.5 × GV<sub>DD</sub>, and to track GV<sub>DD</sub> DC variations as measured at the receiver. Peak-to-peak noise on MV<sub>REF</sub> may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail must track variations in the DC level of MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  GV<sub>DD</sub>.

Table 14 provides the DDR I/O capacitance when  $GV_{DD}(typ) = 2.5$  V.

### Table 14. DDR SDRAM Capacitance for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition                     | Symbol           | Min | Max | Unit | Notes |

|-----------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS | C <sub>DIO</sub> |     | 0.5 | pF   | 1     |

#### Note:

1. This parameter is sampled.  $GV_{DD} = 2.5 \text{ V} \pm 0.125 \text{ V}$ , f = 1 MHz, T<sub>A</sub> = 25°C,  $V_{OUT} = GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

This table provides the current draw characteristics for MV<sub>REF</sub>.

### Table 15. Current Draw Characteristics for MV<sub>REF</sub>

| Parameter/Condition                | Symbol             | Min | Max | Unit | Notes |

|------------------------------------|--------------------|-----|-----|------|-------|

| Current draw for MV <sub>REF</sub> | I <sub>MVREF</sub> |     | 500 | μA   | 1     |

#### Note:

1. The voltage regulator for  $MV_{REF}$  must be able to supply up to 500  $\mu$ A current.

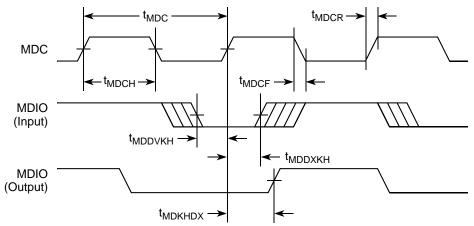

#### **Ethernet Management Interface Electrical Characteristics**

#### Table 37. MII Management AC Timing Specifications (continued)

At recommended operating conditions with  $\text{OV}_{\text{DD}}$  is 3.3 V ± 5%.

| Parameter     | Symbol <sup>1</sup> | Min | Тур | Мах | Unit | Notes |

|---------------|---------------------|-----|-----|-----|------|-------|

| MDC fall time | t <sub>MDHF</sub>   |     |     | 10  | ns   | 4     |

#### Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MDKHDX</sub> symbolizes management data timing (MD) for the time t<sub>MDC</sub> from clock reference (K) high (H) until data outputs (D) are invalid (X) or data hold time. Also, t<sub>MDDVKH</sub> symbolizes management data timing (MD) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MDC</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

- 2. This parameter is dependent on the eTSEC system clock speed, which is half of the Platform Frequency (f<sub>CCB</sub>). The actual ECn\_MDC output clock frequency for a specific eTSEC port can be programmed by configuring the MgmtClk bit field of device's MIIMCFG register, based on the platform (CCB) clock running for the device. The formula is: Platform Frequency (CCB) ÷ (2 × Frequency Divider determined by MIICFG[MgmtClk] encoding selection). For example, if MIICFG[MgmtClk] = 000 and the platform (CCB) is currently running at 533 MHz, f<sub>MDC</sub> = 533) ÷ (2 × 4 × 8) = 533) ÷ 64 = 8.3 MHz. That is, for a system running at a particular platform frequency (f<sub>CCB</sub>), the ECn\_MDC output clock frequency can be programmed between maximum f<sub>MDC</sub> = f<sub>CCB</sub> ÷ 64 and minimum f<sub>MDC</sub> = f<sub>CCB</sub> ÷ 448. See 14.5.3.6.6, "MII Management Configuration Register (MIIMCFG)," in the MPC8548E PowerQUICC™ III Integrated Processor Family Reference Manual for more detail.

- 3. The maximum ECn\_MDC output clock frequency is defined based on the maximum platform frequency for device (533 MHz) divided by 64, while the minimum ECn\_MDC output clock frequency is defined based on the minimum platform frequency for device (333 MHz) divided by 448, following the formula described in Note 2 above.

- 4. Guaranteed by design.

- 5. t<sub>CCB</sub> is the platform (CCB) clock period.

Figure 21 shows the MII management AC timing diagram.

Figure 21. MII Management Interface Timing Diagram

## 10 Local Bus

This section describes the DC and AC electrical specifications for the local bus interface of the device.

## **10.1** Local Bus DC Electrical Characteristics

This table provides the DC electrical characteristics for the local bus interface operating at  $BV_{DD} = 3.3 \text{ V DC}$ .

| Parameter                                                       | Symbol          | Min  | Мах                    | Unit |

|-----------------------------------------------------------------|-----------------|------|------------------------|------|

| High-level input voltage                                        | V <sub>IH</sub> | 2    | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                         | V <sub>IL</sub> | -0.3 | 0.8                    | V    |

| Input current $(V_{IN}^{1} = 0 V \text{ or } V_{IN} = BV_{DD})$ | I <sub>IN</sub> | _    | ±5                     | μA   |

| High-level output voltage ( $BV_{DD} = min, I_{OH} = -2 mA$ )   | V <sub>OH</sub> | 2.4  | —                      | V    |

| Low-level output voltage ( $BV_{DD} = min$ , $I_{OL} = 2 mA$ )  | V <sub>OL</sub> | —    | 0.4                    | V    |

Table 38. Local Bus DC Electrical Characteristics (3.3 V DC)

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1 and Table 2.

Table 39 provides the DC electrical characteristics for the local bus interface operating at  $BV_{DD} = 2.5 \text{ V DC}$ .

Table 39. Local Bus DC Electrical Characteristics (2.5 V DC)

| Parameter                                                       | Symbol          | Min  | Max                    | Unit |

|-----------------------------------------------------------------|-----------------|------|------------------------|------|

| High-level input voltage                                        | V <sub>IH</sub> | 1.70 | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                         | V <sub>IL</sub> | -0.3 | 0.7                    | V    |

| Input current $(V_{IN}^{1} = 0 V \text{ or } V_{IN} = BV_{DD})$ | I <sub>IH</sub> | _    | 10                     | μA   |

|                                                                 | I               |      | -15                    |      |

| High-level output voltage ( $BV_{DD} = min, I_{OH} = -1 mA$ )   | V <sub>OH</sub> | 2.0  | —                      | V    |

| Low-level output voltage ( $BV_{DD} = min$ , $I_{OL} = 1 mA$ )  | V <sub>OL</sub> | _    | 0.4                    | V    |

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1 and Table 2.

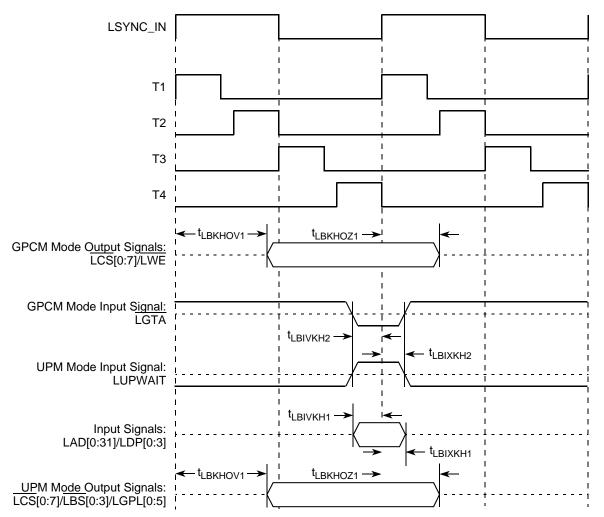

## **10.2 Local Bus AC Electrical Specifications**

This table describes the timing parameters of the local bus interface at  $BV_{DD} = 3.3$  V. For information about the frequency range of local bus, see Section 20.1, "Clock Ranges."

| Parameter                                                             | Symbol <sup>1</sup>                 | Min | Max | Unit | Notes |

|-----------------------------------------------------------------------|-------------------------------------|-----|-----|------|-------|

| Local bus cycle time                                                  | t <sub>LBK</sub>                    | 7.5 | 12  | ns   | 2     |

| Local bus duty cycle                                                  | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43  | 57  | %    | —     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                  | t <sub>LBKSKEW</sub>                | _   | 150 | ps   | 7, 8  |

| Input setup to local bus clock (except LGTA/LUPWAIT)                  | t <sub>LBIVKH1</sub>                | 1.8 |     | ns   | 3, 4  |

| LGTA/LUPWAIT input setup to local bus clock                           | t <sub>LBIVKH2</sub>                | 1.7 | _   | ns   | 3, 4  |

| Input hold from local bus clock (except LGTA/LUPWAIT)                 | t <sub>LBIXKH1</sub>                | 1.0 | _   | ns   | 3, 4  |

| LGTA/LUPWAIT input hold from local bus clock                          | t <sub>LBIXKH2</sub>                | 1.0 |     | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) | t <sub>LBOTOT</sub>                 | 1.5 | _   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)             | t <sub>LBKHOV1</sub>                | _   | 2.0 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                             | t <sub>LBKHOV2</sub>                | _   | 2.2 | ns   | 3     |

| Local bus clock to address valid for LAD                              | t <sub>LBKHOV3</sub>                | _   | 2.3 | ns   | 3     |

| Local bus clock to LALE assertion                                     | t <sub>LBKHOV4</sub>                | _   | 2.3 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)            | t <sub>LBKHOX1</sub>                | 0.7 | _   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                          | t <sub>LBKHOX2</sub>                | 0.7 | _   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)    | t <sub>LBKHOZ1</sub>                |     | 2.5 | ns   | 5     |

| Local bus clock to output high impedance for LAD/LDP                  | t <sub>LBKHOZ2</sub>                | _   | 2.5 | ns   | 5     |

### Table 40. Local Bus Timing Parameters (BV<sub>DD</sub> = 3.3 V)—PLL Enabled

#### Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKH0X</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

- 2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 3.3-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 8. Guaranteed by design.

Figure 27. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 8 or 16 (PLL Enabled)

| Parameter                                                                  | Symbol <sup>2</sup>                        | Min      | Мах      | Unit | Notes |

|----------------------------------------------------------------------------|--------------------------------------------|----------|----------|------|-------|

| Valid times:<br>Boundary-scan data<br>TDO                                  | t <sub>jtkldv</sub><br>t <sub>jtklov</sub> | 4<br>2   | 20<br>10 | ns   | 5     |

| Output hold times:<br>Boundary-scan data<br>TDO                            | t <sub>jtkldx</sub><br>t <sub>jtklox</sub> | 30<br>30 |          | ns   | 5     |

| JTAG external clock to output high impedance:<br>Boundary-scan data<br>TDO | t <sub>jtkldz</sub><br>t <sub>jtkloz</sub> | 3<br>3   | 19<br>9  | ns   | 5, 6  |

Table 44. JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup> (continued)

#### Notes:

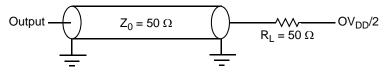

- All outputs are measured from the midpoint voltage of the falling/rising edge of t<sub>TCLK</sub> to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Figure 29). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- 3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

- 5. Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

- 6. Guaranteed by design.

Figure 29 provides the AC test load for TDO and the boundary-scan outputs.

Figure 29. AC Test Load for the JTAG Interface

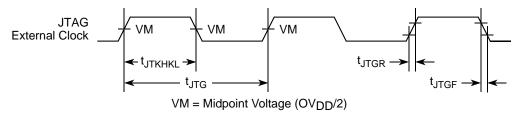

Figure 30 provides the JTAG clock input timing diagram.

Figure 30. JTAG Clock Input Timing Diagram

# 14 GP<sub>OUT</sub>/GP<sub>IN</sub>

This section describes the DC and AC electrical specifications for the GP<sub>OUT</sub>/GP<sub>IN</sub> bus of the device.

## 14.1 GP<sub>OUT</sub>/GP<sub>IN</sub> Electrical Characteristics

Table 47 and Table 48 provide the DC electrical characteristics for the GP<sub>OUT</sub> interface.

| Parameter                                                                      | Symbol           | Min                    | Мах  | Unit |

|--------------------------------------------------------------------------------|------------------|------------------------|------|------|

| Supply voltage 3.3 V                                                           | BV <sub>DD</sub> | 3.13                   | 3.47 | V    |

| High-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OH</sub> = -2 mA) | V <sub>OH</sub>  | BV <sub>DD</sub> – 0.2 | _    | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)   | V <sub>OL</sub>  | —                      | 0.2  | V    |

Table 47. GP<sub>OUT</sub> DC Electrical Characteristics (3.3 V DC)

Table 48. GP<sub>OUT</sub> DC Electrical Characteristics (2.5 V DC)

| Parameter                                                                  | Symbol           | Min       | Мах                    | Unit |

|----------------------------------------------------------------------------|------------------|-----------|------------------------|------|

| Supply voltage 2.5 V                                                       | BV <sub>DD</sub> | 2.37      | 2.63                   | V    |

| High-level output voltage<br>( $BV_{DD} = min, I_{OH} = -1 mA$ )           | V <sub>OH</sub>  | 2.0       | BV <sub>DD</sub> + 0.3 | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> min, I <sub>OL</sub> = 1 mA) | V <sub>OL</sub>  | GND – 0.3 | 0.4                    | V    |

Table 49 and Table 50 provide the DC electrical characteristics for the GP<sub>IN</sub> interface.

Table 49. GP<sub>IN</sub> DC Electrical Characteristics (3.3 V DC)

| Parameter                                                                                      | Symbol           | Min  | Мах                    | Unit |

|------------------------------------------------------------------------------------------------|------------------|------|------------------------|------|

| Supply voltage 3.3 V                                                                           | BV <sub>DD</sub> | 3.13 | 3.47                   | V    |

| High-level input voltage                                                                       | V <sub>IH</sub>  | 2    | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                                        | V <sub>IL</sub>  | -0.3 | 0.8                    | V    |

| Input current<br>(BV <sub>IN</sub> <sup>1</sup> = 0 V or BV <sub>IN</sub> = BV <sub>DD</sub> ) | I <sub>IN</sub>  | _    | ±5                     | μA   |

Note:

1. The symbol  $\mathsf{BV}_{\mathsf{IN}}$ , in this case, represents the  $\mathsf{BV}_{\mathsf{IN}}$  symbol referenced in Table 1.

#### Table 53. PCI-X AC Timing Specifications at 66 MHz (continued)

| Parameter                                        | Symbol              | Min | Max | Unit | Notes |

|--------------------------------------------------|---------------------|-----|-----|------|-------|

| HRESET to PCI-X initialization pattern hold time | t <sub>PCRHIX</sub> | 0   | 50  | ns   | 6, 11 |

Notes:

- 1. See the timing measurement conditions in the PCI-X 1.0a Specification.

- 2. Minimum times are measured at the package pin (not the test point). Maximum times are measured with the test point and load circuit.

- 3. Setup time for point-to-point signals applies to REQ and GNT only. All other signals are bused.

- 4. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 5. Setup time applies only when the device is not driving the pin. Devices cannot drive and receive signals at the same time.

- 6. Maximum value is also limited by delay to the first transaction (time for HRESET high to first configuration access, t<sub>PCRHFV</sub>). The PCI-X initialization pattern control signals after the rising edge of HRESET must be negated no later than two clocks before the first FRAME and must be floated no later than one clock before FRAME is asserted.

- 7. A PCI-X device is permitted to have the minimum values shown for t<sub>PCKHOV</sub> and t<sub>CYC</sub> only in PCI-X mode. In conventional mode, the device must meet the requirements specified in PCI 2.2 for the appropriate clock frequency.

- 8. Device must meet this specification independent of how many outputs switch simultaneously.

9. The timing parameter t<sub>PCRHFV</sub> is a minimum of 10 clocks rather than the minimum of 5 clocks in the PCI-X 1.0a Specification.

10.Guaranteed by characterization.

11.Guaranteed by design.

This table provides the PCI-X AC timing specifications at 133 MHz. Note that the maximum PCI-X frequency in synchronous mode is 110 MHz.

| Parameter                                         | Symbol              | Min | Max | Unit   | Notes         |

|---------------------------------------------------|---------------------|-----|-----|--------|---------------|

| SYSCLK to signal valid delay                      | <sup>t</sup> PCKHOV | _   | 3.8 | ns     | 1, 2, 3, 7, 8 |

| Output hold from SYSCLK                           | t <sub>PCKHOX</sub> | 0.7 | _   | ns     | 1, 11         |

| SYSCLK to output high impedance                   | t <sub>PCKHOZ</sub> |     | 7   | ns     | 1, 4, 8, 12   |

| Input setup time to SYSCLK                        | t <sub>PCIVKH</sub> | 1.2 | _   | ns     | 3, 5, 9, 11   |

| Input hold time from SYSCLK                       | t <sub>PCIXKH</sub> | 0.5 | -   | ns     | 11            |

| REQ64 to HRESET setup time                        | t <sub>PCRVRH</sub> | 10  | _   | clocks | 12            |

| HRESET to REQ64 hold time                         | t <sub>PCRHRX</sub> | 0   | 50  | ns     | 12            |

| HRESET high to first FRAME assertion              | t <sub>PCRHFV</sub> | 10  | _   | clocks | 10, 12        |

| PCI-X initialization pattern to HRESET setup time | <sup>t</sup> PCIVRH | 10  |     | clocks | 12            |

#### Table 54. PCI-X AC Timing Specifications at 133 MHz

#### Serial RapidIO

| Characteristic              | Symbol              | Range |      | Unit   | Notes                                                                      |  |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------|--|

| Characteristic              | Symbol              | Min   | Max  | Onit   | NOICES                                                                     |  |

| Output voltage              | V <sub>O</sub>      | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal comprising a differential pair |  |

| Differential output voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mVp-p  | —                                                                          |  |

| Deterministic jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                          |  |

| Total jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                          |  |

| Multiple output skew        | S <sub>MO</sub>     | —     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |  |

| Unit interval               | UI                  | 400   | 400  | ps     | ±100 ppm                                                                   |  |

### Table 64. Long Run Transmitter AC Timing Specifications—3.125 GBaud

| Characteristic              | Symbol              | Ra    | nge  | Unit   | Notes                                                                         |

|-----------------------------|---------------------|-------|------|--------|-------------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Onic   | NULES                                                                         |

| Output voltage              | V <sub>O</sub>      | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal<br>comprising a differential pair |

| Differential output voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mVp-p  | —                                                                             |

| Deterministic jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                             |

| Total jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                             |

| Multiple output skew        | S <sub>MO</sub>     | —     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link              |

| Unit interval               | UI                  | 320   | 320  | ps     | ±100 ppm                                                                      |

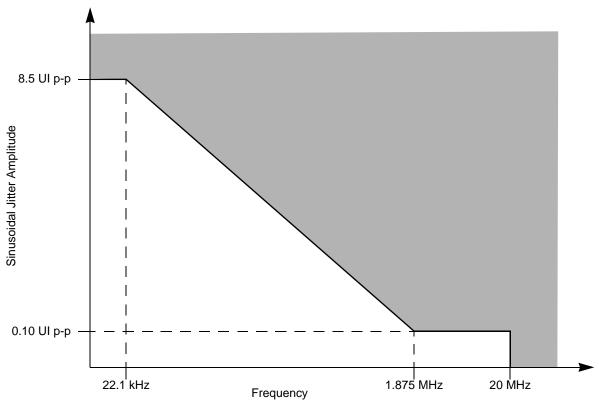

For each baud rate at which an LP-serial transmitter is specified to operate, the output eye pattern of the transmitter shall fall entirely within the unshaded portion of the transmitter output compliance mask shown in Figure 52 with the parameters specified in Table 65 when measured at the output pins of the device and the device is driving a  $100-\Omega \pm 5\%$  differential resistive load. The output eye pattern of an LP-serial

| Characteristic                                     | Symbol          | Range |                   | Unit   | Notes                                                        |

|----------------------------------------------------|-----------------|-------|-------------------|--------|--------------------------------------------------------------|

| Characteristic                                     | Symbol          | Min   | Max               | Onit   | NOICES                                                       |

| Differential input voltage                         | V <sub>IN</sub> | 200   | 1600              | mVp-p  | Measured at receiver                                         |

| Deterministic jitter tolerance                     | J <sub>D</sub>  | 0.37  | —                 | UI p-p | Measured at receiver                                         |

| Combined deterministic and random jitter tolerance | J <sub>DR</sub> | 0.55  | —                 | UI p-p | Measured at receiver                                         |

| Total jitter tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65  | _                 | UI p-p | Measured at receiver                                         |

| Multiple input skew                                | S <sub>MI</sub> | _     | 22                | ns     | Skew at the receiver input between lanes of a multilane link |

| Bit error rate                                     | BER             | _     | 10 <sup>-12</sup> |        | —                                                            |

| Unit interval                                      | UI              | 320   | 320               | ps     | ±100 ppm                                                     |

| Table 68. Receiver | <b>AC Timing</b> | Specifications- | -3.125 GBaud |

|--------------------|------------------|-----------------|--------------|

|--------------------|------------------|-----------------|--------------|

### Note:

1. Total jitter is composed of three components, deterministic jitter, random jitter and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 53. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk and other variable system effects.

Figure 53. Single Frequency Sinusoidal Jitter Limits

#### Notes:

- 1. All dimensions are in millimeters.

- 2. Dimensioning and tolerancing per ASME Y14.5M-1994.

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

- 5. Parallelism measurement shall exclude any effect of mark on top surface of package.

- 6. All dimensions are symmetric across the package center lines unless dimensioned otherwise.

## **19.3 Pinout Listings**

## NOTE

The DMA\_DACK[0:1] and TEST\_SEL/TEST\_SEL pins must be set to a proper state during POR configuration. See the pinlist table of the individual device for more details.

For MPC8548/47/45, GPIOs are still available on PCI1\_AD[63:32]/PC2\_AD[31:0] pins if they are not used for PCI functionality.

For MPC8545/43, eTSEC does not support 16 bit FIFO mode.

Table 71 provides the pinout listing for the MPC8548E 783 FC-PBGA package.

| Signal                                   | Package Pin Number                                                                                                                                                                                     | Pin Type | Power<br>Supply  | Notes    |  |  |

|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|--|--|

| PCI1 and PCI2 (One 64-Bit or Two 32-Bit) |                                                                                                                                                                                                        |          |                  |          |  |  |

| PCI1_AD[63:32]/PCI2_AD[31:0]             | AB14, AC15, AA15, Y16, W16, AB16, AC16,<br>AA16, AE17, AA18, W18, AC17, AD16, AE16,<br>Y17, AC18, AB18, AA19, AB19, AB21, AA20,<br>AC20, AB20, AB22, AC22, AD21, AB23, AF23,<br>AD23, AE23, AC23, AC24 | I/O      | OV <sub>DD</sub> | 17       |  |  |

| PCI1_AD[31:0]                            | AH6, AE7, AF7, AG7, AH7, AF8, AH8, AE9,<br>AH9, AC10, AB10, AD10, AG10, AA10, AH10,<br>AA11, AB12, AE12, AG12, AH12, AB13, AA12,<br>AC13, AE13, Y14, W13, AG13, V14, AH13,<br>AC14, Y15, AB15          | I/O      | OV <sub>DD</sub> | 17       |  |  |

| PCI1_C_BE[7:4]/PCI2_C_BE[3:0]            | AF15, AD14, AE15, AD15                                                                                                                                                                                 | I/O      | OV <sub>DD</sub> | 17       |  |  |

| PCI1_C_BE[3:0]                           | AF9, AD11, Y12, Y13                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 17       |  |  |

| PCI1_PAR64/PCI2_PAR                      | W15                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> |          |  |  |

| PCI1_GNT[4:1]                            | AG6, AE6, AF5, AH5                                                                                                                                                                                     | 0        | OV <sub>DD</sub> | 5, 9, 35 |  |  |

| PCI1_GNT0                                | AG5                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | —        |  |  |

| PCI1_IRDY                                | AF11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |  |  |

| PCI1_PAR                                 | AD12                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | —        |  |  |

| PCI1_PERR                                | AC12                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |  |  |

| PCI1_SERR                                | V13                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2, 4     |  |  |

| PCI1_STOP                                | W12                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2        |  |  |

| PCI1_TRDY                                | AG11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |  |  |

#### Table 71. MPC8548E Pinout Listing

## Table 71. MPC8548E Pinout Listing (continued)

| Signal                                                                                                             | Package Pin Number                                                                                                                                                                                                                                                                                     | Pin Type                                                      | Power<br>Supply                                          | Notes                        |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------|------------------------------|

| 25.These are test signals for factory u                                                                            | ise only and must be pulled up (100 $\Omega$ –1 k $\Omega$ ) to                                                                                                                                                                                                                                        | OV <sub>DD</sub> for normal                                   | machine oper                                             | ration.                      |

| 26.Independent supplies derived from                                                                               | n board V <sub>DD</sub> .                                                                                                                                                                                                                                                                              |                                                               |                                                          |                              |

| 27.Recommend a pull-up resistor (~1                                                                                | $k\Omega$ ) be placed on this pin to $OV_{DD}$ .                                                                                                                                                                                                                                                       |                                                               |                                                          |                              |

|                                                                                                                    | oul <u>led down du</u> ring power-on reset: TSEC3_TXD<br>Y/QUIESCE, MSRCID[2:4], ASLEEP.                                                                                                                                                                                                               | [3], TSEC4_TXD                                                | 93/TSEC3_TX                                              | D7,                          |

| 30.This pin requires an external 4.7-ks driven.                                                                    | 2 pull-down resistor to prevent PHY from seeing a                                                                                                                                                                                                                                                      | valid transmit en                                             | able before it i                                         | s active                     |

| 31.This pin is only an output in eTSE                                                                              | C3 FIFO mode when used as Rx flow control.                                                                                                                                                                                                                                                             |                                                               |                                                          |                              |

| 32. These pins must be connected to 2                                                                              | XV <sub>DD</sub> .                                                                                                                                                                                                                                                                                     |                                                               |                                                          |                              |

| 33. <u>TSEC2_</u> TXD1, TSEC2_TX_ER ar<br>HRESET assertion.                                                        | e multiplexed as cfg_dram_type[0:1]. They must                                                                                                                                                                                                                                                         | be valid at powe                                              | er-up, even bet                                          | fore                         |

| 34.These pins must be pulled to grou                                                                               | nd through a 300- $\Omega$ (±10%) resistor.                                                                                                                                                                                                                                                            |                                                               |                                                          |                              |

| down to select external arbiter if the<br>connect' or terminated through 2–1<br>connected to any other PCI device. | er the POR config pin that selects between inter<br>ere is any other PCI device connected on the PC<br>0 k $\Omega$ pull-up resistors with the default of internal<br>. The PCI block drives the PCI <i>n</i> _AD pins if it is con-<br>thether it is disabled via the DEVDISR register of<br>the bus. | l bus, or leave th<br>arbiter if the PC<br>onfigured to be th | e PCI <i>n_</i> AD pi<br>n_AD pins are<br>e PCI arbiter– | ns as 'n<br>e not<br>–throug |

|                                                                                                                    | $2-\Omega$ precision 1% resistor and MDIC1 is connector automatic calibration of the DDR IOs.                                                                                                                                                                                                          | ed to GV <sub>DD</sub> throu                                  | gh an 18.2-Ω                                             | precisio                     |

| 38.These pins must be left floating.                                                                               |                                                                                                                                                                                                                                                                                                        |                                                               |                                                          |                              |

| 39. If PCI1 or PCI2 is configured as P<br>Otherwise the processor will not be                                      | CI asynchronous mode, a valid clock must be pr<br>oot up.                                                                                                                                                                                                                                              | ovided on pin PC                                              | CI1_CLK or PC                                            | CI2_CL                       |

| 40.These pins must be connected to                                                                                 | GND.                                                                                                                                                                                                                                                                                                   |                                                               |                                                          |                              |

| 101.This pin requires an external 4.7-                                                                             | $k\Omega$ resistor to GND.                                                                                                                                                                                                                                                                             |                                                               |                                                          |                              |

| 102.For Rev. 2.x silicon, DMA_DACK<br>POR configuration are don't care.                                            | [0:1] must be 0b11 during POR configuration; for                                                                                                                                                                                                                                                       | r rev. 1.x silicon, t                                         | the pin values                                           | during                       |

| 103.If these pins are not used as GPI<br>2–10 kΩ resistors.                                                        | Nn (general-purpose input), they must be pulled                                                                                                                                                                                                                                                        | low (to GND) or                                               | high (to LV <sub>DD</sub> )                              | ) throug                     |

| 104.These must be pulled low to GNI                                                                                | D through 2–10 k $\Omega$ resistors if they are not used.                                                                                                                                                                                                                                              |                                                               |                                                          |                              |

|                                                                                                                    | to $\text{LV}_{\text{DD}}$ through 2–10 k $\Omega$ resistors if they are no                                                                                                                                                                                                                            |                                                               |                                                          |                              |

| 106.For rev. 2.x silicon, DMA_DACK[(<br>configuration are don't care.                                              | ):1] must be 0b10 during POR configuration; for re                                                                                                                                                                                                                                                     | ev. 1.x silicon, the                                          | pin values du                                            | ring PO                      |

| 107.For rev. 2.x silicon, DMA_DACK[0 configuration are don't care.                                                 | ):1] must be 0b01 during POR configuration; for re                                                                                                                                                                                                                                                     | ev. 1.x silicon, the                                          | pin values du                                            | ring PO                      |

| 108.For rev. 2.x silicon, DMA_DACK[C configuration are don't care.                                                 | 0:1] must be 0b11 during POR configuration; for re                                                                                                                                                                                                                                                     | ev. 1.x silicon, the                                          | pin values du                                            | ring PO                      |

| 109.This is a test signal for factory us                                                                           | e only and must be pulled down (100 $\Omega$ – 1 k $\Omega$ )                                                                                                                                                                                                                                          | to GND for norm                                               | al machine op                                            | eration.                     |

| 110.These pins must be pulled high to                                                                              | o OV <sub>DD</sub> through 2–10 k $\Omega$ resistors.                                                                                                                                                                                                                                                  |                                                               |                                                          |                              |

| 111.If these pins are not used as GPII 2–10 k $\Omega$ resistors.                                                  | Nn (general-purpose input), they must be pulled                                                                                                                                                                                                                                                        | low (to GND) or I                                             | high (to OV <sub>DD</sub> )                              | ) throug                     |

| 112.This pin must not be pulled down                                                                               | during POR configuration.                                                                                                                                                                                                                                                                              |                                                               |                                                          |                              |

|                                                                                                                    |                                                                                                                                                                                                                                                                                                        |                                                               |                                                          |                              |

Table 72 provides the pin-out listing for the MPC8547E 783 FC-PBGA package.

### NOTE

All note references in the following table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

| Signal         | Package Pin Number                                                                                                                                                                                     | Pin Type | Power<br>Supply  | Notes    |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

|                | PCI1 (One 64-Bit or One 32-Bit)                                                                                                                                                                        |          | 1                |          |

| PCI1_AD[63:32] | AB14, AC15, AA15, Y16, W16, AB16, AC16,<br>AA16, AE17, AA18, W18, AC17, AD16, AE16,<br>Y17, AC18, AB18, AA19, AB19, AB21, AA20,<br>AC20, AB20, AB22, AC22, AD21, AB23, AF23,<br>AD23, AE23, AC23, AC24 | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_AD[31:0]  | AH6, AE7, AF7, AG7, AH7, AF8, AH8, AE9,<br>AH9, AC10, AB10, AD10, AG10, AA10, AH10,<br>AA11, AB12, AE12, AG12, AH12, AB13, AA12,<br>AC13, AE13, Y14, W13, AG13, V14, AH13,<br>AC14, Y15, AB15          | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_C_BE[7:4] | AF15, AD14, AE15, AD15                                                                                                                                                                                 | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_C_BE[3:0] | AF9, AD11, Y12, Y13                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_PAR64     | W15                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | —        |

| PCI1_GNT[4:1]  | AG6, AE6, AF5, AH5                                                                                                                                                                                     | 0        | OV <sub>DD</sub> | 5, 9, 35 |

| PCI1_GNT0      | AG5                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | —        |

| PCI1_IRDY      | AF11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_PAR       | AD12                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | —        |

| PCI1_PERR      | AC12                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_SERR      | V13                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2, 4     |

| PCI1_STOP      | W12                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_TRDY      | AG11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_REQ[4:1]  | AH2, AG4, AG3, AH4                                                                                                                                                                                     | I        | OV <sub>DD</sub> | —        |

| PCI1_REQ0      | AH3                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | —        |

| PCI1_CLK       | AH26                                                                                                                                                                                                   | I        | OV <sub>DD</sub> | 39       |

| PCI1_DEVSEL    | AH11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_FRAME     | AE11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_IDSEL     | AG9                                                                                                                                                                                                    | I        | OV <sub>DD</sub> | —        |

| PCI1_REQ64     | AF14                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2, 5,10  |

| PCI1_ACK64     | V15                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2        |

| Reserved       | AE28                                                                                                                                                                                                   | —        | —                | 2        |

| Reserved       | AD26                                                                                                                                                                                                   | _        | —                | 2        |

| Reserved       | AD25                                                                                                                                                                                                   | —        | —                | 2        |

#### Table 72. MPC8547E Pinout Listing

| Table 72 | . MPC8547E | <b>Pinout Listing</b> | (continued) |

|----------|------------|-----------------------|-------------|

|----------|------------|-----------------------|-------------|

| Signal       | Package Pin Number                                                                                                                                                                                                                                                                                               | Pin Type | Power<br>Supply  | Notes |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

| Reserved     | AE26                                                                                                                                                                                                                                                                                                             | _        | —                | 2     |

| cfg_pci1_clk | AG24                                                                                                                                                                                                                                                                                                             | I        | OV <sub>DD</sub> | 5     |

| Reserved     | AF25                                                                                                                                                                                                                                                                                                             | _        | —                | 101   |

| Reserved     | AE25                                                                                                                                                                                                                                                                                                             | _        | —                | 2     |

| Reserved     | AG25                                                                                                                                                                                                                                                                                                             | _        | —                | 2     |

| Reserved     | AD24                                                                                                                                                                                                                                                                                                             | _        | —                | 2     |

| Reserved     | AF24                                                                                                                                                                                                                                                                                                             | _        | —                | 2     |

| Reserved     | AD27                                                                                                                                                                                                                                                                                                             | _        | —                | 2     |

| Reserved     | AD28, AE27, W17, AF26                                                                                                                                                                                                                                                                                            | _        | —                | 2     |

| Reserved     | AH25                                                                                                                                                                                                                                                                                                             | _        | —                | 2     |

|              | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                                       |          |                  | 1     |

| MDQ[0:63]    | L18, J18, K14, L13, L19, M18, L15, L14, A17,<br>B17, A13, B12, C18, B18, B13, A12, H18, F18,<br>J14, F15, K19, J19, H16, K15, D17, G16, K13,<br>D14, D18, F17, F14, E14, A7, A6, D5, A4, C8,<br>D7, B5, B4, A2, B1, D1, E4, A3, B2, D2, E3, F3,<br>G4, J5, K5, F6, G5, J6, K4, J1, K2, M5, M3, J3,<br>J2, L1, M6 | I/O      | GV <sub>DD</sub> | _     |

| MECC[0:7]    | H13, F13, F11, C11, J13, G13, D12, M12                                                                                                                                                                                                                                                                           | I/O      | GV <sub>DD</sub> | —     |

| MDM[0:8]     | M17, C16, K17, E16, B6, C4, H4, K1, E13                                                                                                                                                                                                                                                                          | 0        | GV <sub>DD</sub> | —     |

| MDQS[0:8]    | M15, A16, G17, G14, A5, D3, H1, L2, C13                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> | —     |

| MDQS[0:8]    | L17, B16, J16, H14, C6, C2, H3, L4, D13                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> | —     |

| MA[0:15]     | A8, F9, D9, B9, A9, L10, M10, H10, K10, G10,<br>B8, E10, B10, G6, A10, L11                                                                                                                                                                                                                                       | 0        | GV <sub>DD</sub> | _     |

| MBA[0:2]     | F7, J7, M11                                                                                                                                                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —     |

| MWE          | E7                                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub> | —     |

| MCAS         | H7                                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub> | —     |

| MRAS         | L8                                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub> | —     |

| MCKE[0:3]    | F10, C10, J11, H11                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub> | 11    |

| MCS[0:3]     | K8, J8, G8, F8                                                                                                                                                                                                                                                                                                   | 0        | GV <sub>DD</sub> | —     |

| MCK[0:5]     | H9, B15, G2, M9, A14, F1                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub> | —     |

| MCK[0:5]     | J9, A15, G1, L9, B14, F2                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub> | —     |

| MODT[0:3]    | E6, K6, L7, M7                                                                                                                                                                                                                                                                                                   | 0        | GV <sub>DD</sub> | —     |

| MDIC[0:1]    | A19, B19                                                                                                                                                                                                                                                                                                         | I/O      | GV <sub>DD</sub> | 36    |

| Signal                         | Package Pin Number                                                                                                                                                      | Pin Type | Power<br>Supply  | Notes        |  |  |  |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|--------------|--|--|--|

| Local Bus Controller Interface |                                                                                                                                                                         |          |                  |              |  |  |  |

| LAD[0:31]                      | E27, B20, H19, F25, A20, C19, E28, J23, A25,<br>K22, B28, D27, D19, J22, K20, D28, D25, B25,<br>E22, F22, F21, C25, C22, B23, F20, A23, A22,<br>E19, A21, D21, F19, B21 | I/O      | BV <sub>DD</sub> | _            |  |  |  |

| LDP[0:3]                       | K21, C28, B26, B22                                                                                                                                                      | I/O      | BV <sub>DD</sub> | —            |  |  |  |

| LA[27]                         | H21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |  |  |  |

| LA[28:31]                      | H20, A27, D26, A28                                                                                                                                                      | 0        | BV <sub>DD</sub> | 5, 7, 9      |  |  |  |

| LCS[0:4]                       | J25, C20, J24, G26, A26                                                                                                                                                 | 0        | BV <sub>DD</sub> | —            |  |  |  |

| LCS5/DMA_DREQ2                 | D23                                                                                                                                                                     | I/O      | BV <sub>DD</sub> | 1            |  |  |  |

| LCS6/DMA_DACK2                 | G20                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 1            |  |  |  |

| LCS7/DMA_DDONE2                | E21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 1            |  |  |  |

| LWE0/LBS0/LSDDQM[0]            | G25                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |  |  |  |

| LWE1/LBS1/LSDDQM[1]            | C23                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |  |  |  |

| LWE2/LBS2/LSDDQM[2]            | J21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |  |  |  |

| LWE3/LBS3/LSDDQM[3]            | A24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |  |  |  |

| LALE                           | H24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9      |  |  |  |

| LBCTL                          | G27                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9      |  |  |  |

| LGPL0/LSDA10                   | F23                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |  |  |  |

| LGPL1/LSDWE                    | G22                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |  |  |  |

| LGPL2/LOE/LSDRAS               | B27                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9      |  |  |  |

| LGPL3/LSDCAS                   | F24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |  |  |  |

| LGPL4/LGTA/LUPWAIT/LPBSE       | H23                                                                                                                                                                     | I/O      | BV <sub>DD</sub> | —            |  |  |  |

| LGPL5                          | E26                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |  |  |  |