#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

ĿХF

| Product Status                  | Obsolete                                                   |

|---------------------------------|------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                               |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                             |

| Speed                           | 1.0GHz                                                     |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                      |

| RAM Controllers                 | DDR, DDR2, SDRAM                                           |

| Graphics Acceleration           | No                                                         |

| Display & Interface Controllers | -                                                          |

| Ethernet                        | 10/100/1000Mbps (4)                                        |

| SATA                            | -                                                          |

| USB                             | -                                                          |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                           |

| Operating Temperature           | 0°C ~ 105°C (TA)                                           |

| Security Features               | Cryptography, Random Number Generator                      |

| Package / Case                  | 783-BBGA, FCBGA                                            |

| Supplier Device Package         | 783-FCBGA (29x29)                                          |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8545ehxaqg |

|                                 |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Overview

- Single inbound doorbell message structure

- Facility to accept port-write messages

- PCI Express interface

- PCI Express 1.0a compatible

- Supports x8,x4,x2, and x1 link widths

- Auto-detection of number of connected lanes

- Selectable operation as root complex or endpoint

- Both 32- and 64-bit addressing

- 256-byte maximum payload size

- Virtual channel 0 only

- Traffic class 0 only

- Full 64-bit decode with 32-bit wide windows

- Pin multiplexing for the high-speed I/O interfaces supports one of the following configurations:

- 8 PCI Express

- 4 PCI Express and 4 serial RapidIO

- Power management

- Supports power saving modes: doze, nap, and sleep

- Employs dynamic power management, which automatically minimizes power consumption of blocks when they are idle

- System performance monitor

- Supports eight 32-bit counters that count the occurrence of selected events

- Ability to count up to 512 counter-specific events

- Supports 64 reference events that can be counted on any of the eight counters

- Supports duration and quantity threshold counting

- Burstiness feature that permits counting of burst events with a programmable time between bursts

- Triggering and chaining capability

- Ability to generate an interrupt on overflow

- System access port

- Uses JTAG interface and a TAP controller to access entire system memory map

- Supports 32-bit accesses to configuration registers

- Supports cache-line burst accesses to main memory

- Supports large block (4-Kbyte) uploads and downloads

- Supports continuous bit streaming of entire block for fast upload and download

- JTAG boundary scan, designed to comply with IEEE Std. 1149.1<sup>TM</sup>

Table 13 provides the recommended operating conditions for the DDR SDRAM controller when  $GV_{DD}(typ) = 2.5 \text{ V}.$

| Parameter/Condition                             | Symbol            | Symbol Min                  |                          | Unit | Notes |

|-------------------------------------------------|-------------------|-----------------------------|--------------------------|------|-------|

| I/O supply voltage                              | GV <sub>DD</sub>  | 2.375                       | 2.625                    | V    | 1     |

| I/O reference voltage                           | MV <sub>REF</sub> | $MV_{REF}$ 0.49 × $GV_{DD}$ |                          | V    | 2     |

| I/O termination voltage                         | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04    | MV <sub>REF</sub> + 0.04 | V    | 3     |

| Input high voltage                              | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.15    | GV <sub>DD</sub> + 0.3   | V    | —     |

| Input low voltage                               | V <sub>IL</sub>   | -0.3                        | MV <sub>REF</sub> – 0.15 | V    | —     |

| Output leakage current                          | I <sub>OZ</sub>   | -50                         | 50                       | μΑ   | 4     |

| Output high current (V <sub>OUT</sub> = 1.95 V) | I <sub>OH</sub>   | -16.2                       | —                        | mA   | —     |

| Output low current (V <sub>OUT</sub> = 0.35 V)  | I <sub>OL</sub>   | 16.2                        | —                        | mA   | —     |

| Table 13. DDR SDRAM DC Electrical | Characteristics for GV <sub>DD</sub> (typ) = 2.5 V |

|-----------------------------------|----------------------------------------------------|

|                                   |                                                    |

#### Notes:

1.  ${\rm GV}_{\rm DD}$  is expected to be within 50 mV of the DRAM  ${\rm V}_{\rm DD}$  at all times.

2. MV<sub>REF</sub> is expected to be equal to 0.5 × GV<sub>DD</sub>, and to track GV<sub>DD</sub> DC variations as measured at the receiver. Peak-to-peak noise on MV<sub>REF</sub> may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail must track variations in the DC level of MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled,  $0 V \le V_{OUT} \le GV_{DD}$ .

Table 14 provides the DDR I/O capacitance when  $GV_{DD}(typ) = 2.5$  V.

#### Table 14. DDR SDRAM Capacitance for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition                     | Symbol           | Min | Max | Unit | Notes |

|-----------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS | C <sub>DIO</sub> |     | 0.5 | pF   | 1     |

#### Note:

1. This parameter is sampled.  $GV_{DD} = 2.5 \text{ V} \pm 0.125 \text{ V}$ , f = 1 MHz, T<sub>A</sub> = 25°C,  $V_{OUT} = GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

This table provides the current draw characteristics for MV<sub>REF</sub>.

#### Table 15. Current Draw Characteristics for MV<sub>REF</sub>

| Parameter/Condition                | Symbol             | Min | Max | Unit | Notes |

|------------------------------------|--------------------|-----|-----|------|-------|

| Current draw for MV <sub>REF</sub> | I <sub>MVREF</sub> |     | 500 | μA   | 1     |

#### Note:

1. The voltage regulator for  $MV_{REF}$  must be able to supply up to 500  $\mu$ A current.

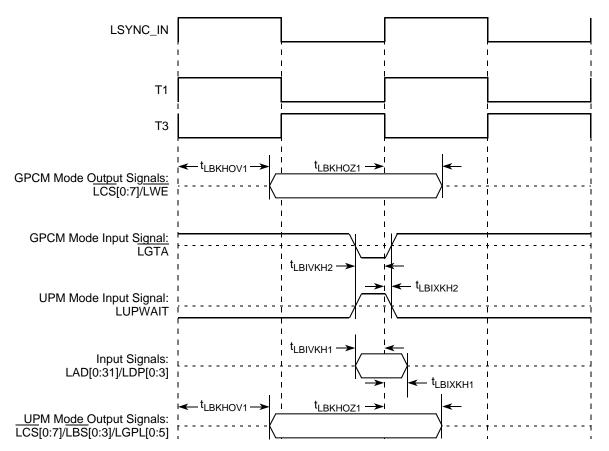

Figure 25. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 (PLL Enabled)

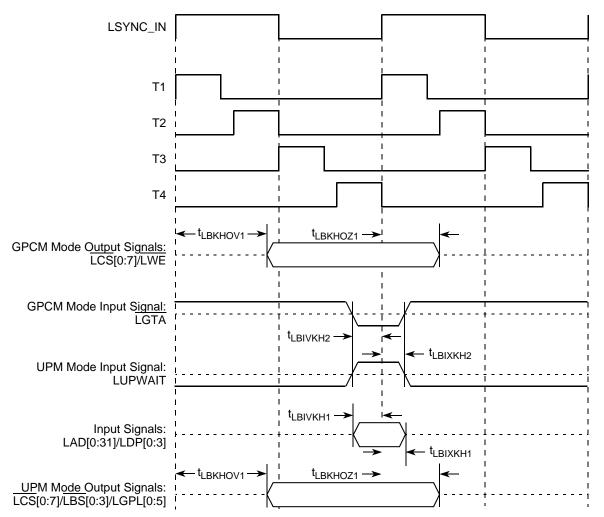

Figure 27. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 8 or 16 (PLL Enabled)

#### l<sup>2</sup>C

# 13 I<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the I<sup>2</sup>C interfaces of the device.

# **13.1** I<sup>2</sup>C DC Electrical Characteristics

This table provides the DC electrical characteristics for the  $I^2C$  interfaces.

#### Table 45. I<sup>2</sup>C DC Electrical Characteristics

| Parameter                                                                                                | Symbol              | Min                  | Мах                                | Unit | Notes |

|----------------------------------------------------------------------------------------------------------|---------------------|----------------------|------------------------------------|------|-------|

| Input high voltage level                                                                                 | V <sub>IH</sub>     | $0.7 \times OV_{DD}$ | OV <sub>DD</sub> + 0.3             | V    | _     |

| Input low voltage level                                                                                  | V <sub>IL</sub>     | -0.3                 | $0.3 	imes OV_{DD}$                | V    | —     |

| Low level output voltage                                                                                 | V <sub>OL</sub>     | 0                    | $0.2 \times \text{OV}_{\text{DD}}$ | V    | 1     |

| Pulse width of spikes which must be suppressed by the input filter                                       | t <sub>I2KHKL</sub> | 0                    | 50                                 | ns   | 2     |

| Input current each I/O pin (input voltage is between $0.1 \times OV_{DD}$ and $0.9 \times OV_{DD}$ (max) | I                   | -10                  | 10                                 | μΑ   | 3     |

| Capacitance for each I/O pin                                                                             | Cl                  | —                    | 10                                 | pF   | —     |

#### Notes:

1. Output voltage (open drain or open collector) condition = 3 mA sink current.

- 2. See the MPC8548E PowerQUICC<sup>™</sup> III Integrated Processor Family Reference Manual, for information on the digital filter used.

- 3. I/O pins obstruct the SDA and SCL lines if  $\ensuremath{\mathsf{OV}_{\mathsf{DD}}}$  is switched off.

# **13.2** I<sup>2</sup>C AC Electrical Specifications

This table provides the AC timing parameters for the  $I^2C$  interfaces.

Table 46. I<sup>2</sup>C AC Electrical Specifications

| Parameter                                                                                    | Symbol <sup>1</sup> | Min | Max | Unit | Notes |

|----------------------------------------------------------------------------------------------|---------------------|-----|-----|------|-------|

| SCL clock frequency                                                                          | f <sub>I2C</sub>    | 0   | 400 | kHz  | —     |

| Low period of the SCL clock                                                                  | t <sub>I2CL</sub>   | 1.3 | —   | μS   | 4     |

| High period of the SCL clock                                                                 | t <sub>I2CH</sub>   | 0.6 | —   | μS   | 4     |

| Setup time for a repeated START condition                                                    | t <sub>I2SVKH</sub> | 0.6 | —   | μS   | 4     |

| Hold time (repeated) START condition (after this period, the first clock pulse is generated) | t <sub>I2SXKL</sub> | 0.6 | —   | μS   | 4     |

| Data setup time                                                                              | t <sub>I2DVKH</sub> | 100 | —   | ns   | 4     |

| Data input hold time:<br>CBUS compatible masters<br>I <sup>2</sup> C bus devices             | t <sub>I2DXKL</sub> | 0   |     | μs   | 2     |

| Data output delay time:                                                                      | t <sub>I2OVKL</sub> | —   | 0.9 | —    | 3     |

| Set-up time for STOP condition                                                               | t <sub>I2PVKH</sub> | 0.6 | —   | μS   | —     |

| Bus free time between a STOP and START condition                                             | t <sub>I2KHDX</sub> | 1.3 |     | μS   |       |

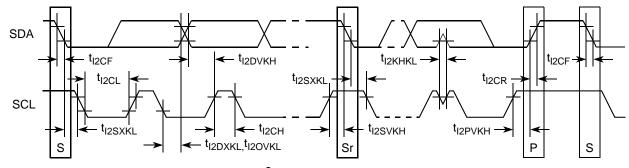

Figure 34 shows the AC timing diagram for the  $I^2C$  bus.

Figure 34. I<sup>2</sup>C Bus AC Timing Diagram

#### High-Speed Serial Interfaces (HSSI)

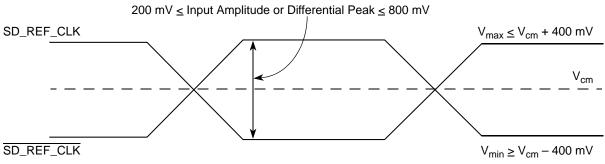

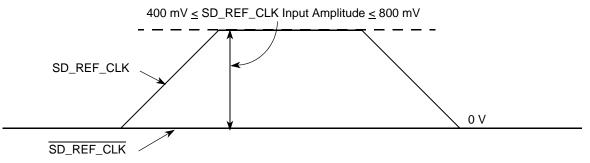

Figure 42. Single-Ended Reference Clock Input DC Requirements

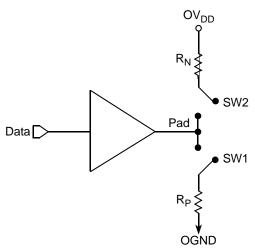

### 16.2.3 Interfacing with Other Differential Signaling Levels

- With on-chip termination to SGND\_SRDSn (xcorevss), the differential reference clocks inputs are HCSL (high-speed current steering logic) compatible DC-coupled.

- Many other low voltage differential type outputs like LVDS (low voltage differential signaling) can be used but may need to be AC-coupled due to the limited common mode input range allowed (100 to 400 mV) for DC-coupled connection.

- LVPECL outputs can produce signal with too large amplitude and may need to be DC-biased at clock driver output first, then followed with series attenuation resistor to reduce the amplitude, in addition to AC-coupling.

#### NOTE

Figure 43 through Figure 46 below are for conceptual reference only. Due to the fact that clock driver chip's internal structure, output impedance, and termination requirements are different between various clock driver chip manufacturers, it is very possible that the clock circuit reference designs provided by clock driver chip vendor are different from what is shown below. They might also vary from one vendor to the other. Therefore, Freescale Semiconductor can neither provide the optimal clock driver reference circuits, nor guarantee the correctness of the following clock driver connection reference circuits. The system designer is recommended to contact the selected clock driver chip vendor for the optimal reference circuits with the SerDes reference clock receiver requirement provided in this document.

#### Serial RapidIO

| Characteristic              | Symbol              | Ra    | nge  | Unit   | Notes                                                                      |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Unit   | Notes                                                                      |

| Output voltage              | Vo                  | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal comprising a differential pair |

| Differential output voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mV p-p | —                                                                          |

| Deterministic jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                          |

| Total jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                          |

| Multiple output skew        | S <sub>MO</sub>     | —     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |

| Unit interval               | UI                  | 400   | 400  | ps     | ±100 ppm                                                                   |

#### Table 61. Short Run Transmitter AC Timing Specifications—3.125 GBaud

| Characteristic              | Symbol              | Rai   | nge  | Unit   | Notes                                                                      |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Onic   | NOICS                                                                      |

| Output voltage              | Vo                  | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal comprising a differential pair |

| Differential output voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mVp-p  | -                                                                          |

| Deterministic jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | -                                                                          |

| Total jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | _                                                                          |

| Multiple output skew        | S <sub>MO</sub>     | —     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |

| Unit interval               | UI                  | 320   | 320  | ps     | ±100 ppm                                                                   |

#### Table 62. Long Run Transmitter AC Timing Specifications—1.25 GBaud

| Characteristic              | Symbol              | Rai   | nge  | Unit   | Notes                                                                      |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Onit   | NULES                                                                      |

| Output voltage              | V <sub>O</sub>      | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal comprising a differential pair |

| Differential output voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mVp-p  | —                                                                          |

| Deterministic jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                          |

| Total jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                          |

| Multiple output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |

| Unit interval               | UI                  | 800   | 800  | ps     | ±100 ppm                                                                   |

| Characteristic                                     | Symbol          | Range |                   | Unit   | Notes                                                        |  |

|----------------------------------------------------|-----------------|-------|-------------------|--------|--------------------------------------------------------------|--|

| Characteristic                                     | Symbol          | Min   | Max               | Onit   | NOICES                                                       |  |

| Differential input voltage                         | V <sub>IN</sub> | 200   | 1600              | mVp-p  | Measured at receiver                                         |  |

| Deterministic jitter tolerance                     | J <sub>D</sub>  | 0.37  | —                 | UI p-p | Measured at receiver                                         |  |

| Combined deterministic and random jitter tolerance | J <sub>DR</sub> | 0.55  | —                 | UI p-p | Measured at receiver                                         |  |

| Total jitter tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65  | _                 | UI p-p | Measured at receiver                                         |  |

| Multiple input skew                                | S <sub>MI</sub> | _     | 22                | ns     | Skew at the receiver input between lanes of a multilane link |  |

| Bit error rate                                     | BER             | _     | 10 <sup>-12</sup> |        | —                                                            |  |

| Unit interval                                      | UI              | 320   | 320               | ps     | ±100 ppm                                                     |  |

| Table 68. Receiver | AC Timing | Specifications- | -3.125 GBaud |

|--------------------|-----------|-----------------|--------------|

|--------------------|-----------|-----------------|--------------|

#### Note:

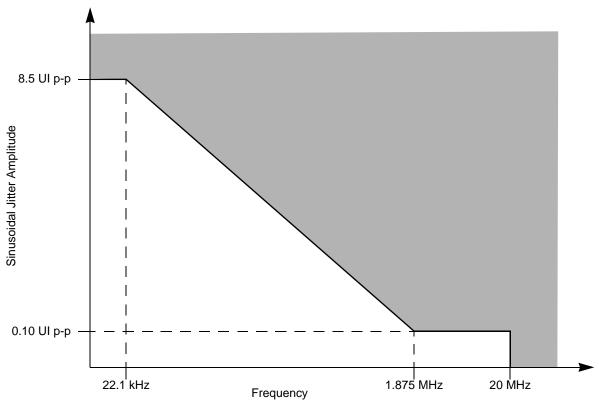

1. Total jitter is composed of three components, deterministic jitter, random jitter and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 53. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk and other variable system effects.

Figure 53. Single Frequency Sinusoidal Jitter Limits

#### Notes:

- 1. All dimensions are in millimeters.

- 2. Dimensioning and tolerancing per ASME Y14.5M-1994.

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

- 5. Parallelism measurement shall exclude any effect of mark on top surface of package.

- 6. All dimensions are symmetric across the package center lines unless dimensioned otherwise.

| Signal                 | Package Pin Number                                                                                                                                                                                                                                                                                               | Pin Type | Power<br>Supply  | Notes    |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

| PCI1_REQ[4:1]          | AH2, AG4, AG3, AH4                                                                                                                                                                                                                                                                                               | I        | OV <sub>DD</sub> |          |

|                        |                                                                                                                                                                                                                                                                                                                  |          |                  |          |

|                        |                                                                                                                                                                                                                                                                                                                  |          |                  |          |

|                        |                                                                                                                                                                                                                                                                                                                  |          |                  |          |

|                        |                                                                                                                                                                                                                                                                                                                  |          |                  |          |

| PCI1_REQ0              | AH3                                                                                                                                                                                                                                                                                                              | I/O      | OV <sub>DD</sub> | —        |

| PCI1_CLK               | AH26                                                                                                                                                                                                                                                                                                             | I        | OV <sub>DD</sub> | 39       |

| PCI1_DEVSEL            | AH11                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_FRAME             | AE11                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_IDSEL             | AG9                                                                                                                                                                                                                                                                                                              | I        | OV <sub>DD</sub> |          |

| PCI1_REQ64/PCI2_FRAME  | AF14                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2, 5, 10 |

| PCI1_ACK64/PCI2_DEVSEL | V15                                                                                                                                                                                                                                                                                                              | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_CLK               | AE28                                                                                                                                                                                                                                                                                                             | I        | OV <sub>DD</sub> | 39       |

| PCI2_IRDY              | AD26                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_PERR              | AD25                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_GNT[4:1]          | AE26, AG24, AF25, AE25                                                                                                                                                                                                                                                                                           | 0        | OV <sub>DD</sub> | 5, 9, 35 |

| PCI2_GNT0              | AG25                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | —        |

| PCI2_SERR              | AD24                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2, 4     |

| PCI2_STOP              | AF24                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_TRDY              | AD27                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_REQ[4:1]          | AD28, AE27, W17, AF26                                                                                                                                                                                                                                                                                            | I        | OV <sub>DD</sub> | —        |

| PCI2_REQ0              | AH25                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | —        |

|                        | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                                       |          | •                |          |

| MDQ[0:63]              | L18, J18, K14, L13, L19, M18, L15, L14, A17,<br>B17, A13, B12, C18, B18, B13, A12, H18, F18,<br>J14, F15, K19, J19, H16, K15, D17, G16, K13,<br>D14, D18, F17, F14, E14, A7, A6, D5, A4, C8,<br>D7, B5, B4, A2, B1, D1, E4, A3, B2, D2, E3, F3,<br>G4, J5, K5, F6, G5, J6, K4, J1, K2, M5, M3, J3,<br>J2, L1, M6 | I/O      | GV <sub>DD</sub> | _        |

| MECC[0:7]              | H13, F13, F11, C11, J13, G13, D12, M12                                                                                                                                                                                                                                                                           | I/O      | GV <sub>DD</sub> |          |

| MDM[0:8]               | M17, C16, K17, E16, B6, C4, H4, K1, E13                                                                                                                                                                                                                                                                          | 0        | GV <sub>DD</sub> | -        |

| MDQS[0:8]              | M15, A16, G17, G14, A5, D3, H1, L2, C13                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> | -        |

| MDQS[0:8]              | L17, B16, J16, H14, C6, C2, H3, L4, D13                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> | —        |

| MA[0:15]               | A8, F9, D9, B9, A9, L10, M10, H10, K10, G10,<br>B8, E10, B10, G6, A10, L11                                                                                                                                                                                                                                       | 0        | GV <sub>DD</sub> | —        |

| MBA[0:2]               | F7, J7, M11                                                                                                                                                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —        |

#### Table 71. MPC8548E Pinout Listing (continued)

| Signal           | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin Type                                           | Power<br>Supply  | Notes        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------|--------------|

|                  | Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                    |                  | 1            |

| RTC              | AF16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | —            |

| SYSCLK           | AH17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | —            |

|                  | JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                    |                  | 1            |

| ТСК              | AG28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | —            |

| TDI              | AH28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 12           |

| TDO              | AF28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                  | OV <sub>DD</sub> | _            |

| TMS              | AH27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 12           |

| TRST             | AH23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 12           |

|                  | DFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                    |                  |              |

| L1_TSTCLK        | AC25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 25           |

| L2_TSTCLK        | AE22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 25           |

| LSSD_MODE        | AH20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 25           |

| TEST_SEL         | AH14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 25           |

|                  | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                    |                  |              |

| THERM0           | AG1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                  | _                | 14           |

| THERM1           | AH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                  |                  | 14           |

|                  | Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                    |                  |              |

| ASLEEP           | AH18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                  | OV <sub>DD</sub> | 9, 19,<br>29 |

|                  | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                    |                  | •            |

| GND              | <ul> <li>A11, B7, B24, C1, C3, C5, C12, C15, C26, D8,<br/>D11, D16, D20, D22, E1, E5, E9, E12, E15, E17,<br/>F4, F26, G12, G15, G18, G21, G24, H2, H6, H8,<br/>H28, J4, J12, J15, J17, J27, K7, K9, K11, K27,<br/>L3, L5, L12, L16, N11, N13, N15, N17, N19, P4,<br/>P9, P12, P14, P16, P18, R11, R13, R15, R17,<br/>R19, T4, T12, T14, T16, T18, U8, U11, U13,<br/>U15, U17, U19, V4, V12, V18, W6, W19, Y4, Y9,<br/>Y11, Y19, AA6, AA14, AA17, AA22, AA23, AB4,<br/>AC2, AC11, AC19, AC26, AD5, AD9, AD22,<br/>AE3, AE14, AF6, AF10, AF13, AG8, AG27,<br/>K28, L24, L26, N24, N27, P25, R28, T24, T26,<br/>U24, V25, W28, Y24, Y26, AA24, AA27, AB25,<br/>AC28, L21, L23, N22, P20, R23, T21, U22, V20,<br/>W23, Y21, U27</li> </ul> | _                                                  |                  |              |

| OV <sub>DD</sub> | V16, W11, W14, Y18, AA13, AA21, AB11,<br>AB17, AB24, AC4, AC9, AC21, AD6, AD13,<br>AD17, AD19, AE10, AE8, AE24, AF4, AF12,<br>AF22, AF27, AG26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Power for PCI<br>and other<br>standards<br>(3.3 V) | OV <sub>DD</sub> | _            |

| Table 72. MPC8547E Pinout Listing (continued | I) |

|----------------------------------------------|----|

|----------------------------------------------|----|

| Signal                 | Package Pin Number                     | Pin Type | Power<br>Supply  | Notes           |

|------------------------|----------------------------------------|----------|------------------|-----------------|

| Reserved               | U20, V22, W20, Y22                     | _        |                  | 15              |

| Reserved               | U21, V23, W21, Y23                     | —        | —                | 15              |

| SD_PLL_TPD             | U28                                    | 0        | XV <sub>DD</sub> | 24              |

| SD_REF_CLK             | T28                                    | I        | XV <sub>DD</sub> | —               |

| SD_REF_CLK             | T27                                    | I        | XV <sub>DD</sub> | —               |

| Reserved               | AC1, AC3                               | —        | _                | 2               |

| Reserved               | M26, V28                               | —        | —                | 32              |

| Reserved               | M25, V27                               | —        | —                | 34              |

| Reserved               | M20, M21, T22, T23                     | —        | —                | 38              |

| · · · · ·              | General-Purpose Output                 |          |                  | •               |

| GPOUT[24:31]           | K26, K25, H27, G28, H25, J26, K24, K23 | 0        | BV <sub>DD</sub> | —               |

|                        | System Control                         |          |                  | •               |

| HRESET                 | AG17                                   | I        | OV <sub>DD</sub> | —               |

| HRESET_REQ             | AG16                                   | 0        | OV <sub>DD</sub> | 29              |

| SRESET                 | AG20                                   | I        | OV <sub>DD</sub> | —               |

| CKSTP_IN               | AA9                                    | I        | OV <sub>DD</sub> | —               |

| CKSTP_OUT              | AA8                                    | 0        | OV <sub>DD</sub> | 2, 4            |

|                        | Debug                                  |          |                  |                 |

| TRIG_IN                | AB2                                    | I        | OV <sub>DD</sub> | —               |

| TRIG_OUT/READY/QUIESCE | AB1                                    | 0        | OV <sub>DD</sub> | 6, 9,<br>19, 29 |

| MSRCID[0:1]            | AE4, AG2                               | 0        | OV <sub>DD</sub> | 5, 6, 9         |

| MSRCID[2:4]            | AF3, AF1, AF2                          | 0        | OV <sub>DD</sub> | 6, 19,<br>29    |

| MDVAL                  | AE5                                    | 0        | OV <sub>DD</sub> | 6               |

| CLK_OUT                | AE21                                   | 0        | OV <sub>DD</sub> | 11              |

|                        | Clock                                  | -        |                  |                 |

| RTC                    | AF16                                   | I        | OV <sub>DD</sub> | —               |

| SYSCLK                 | AH17                                   | I        | OV <sub>DD</sub> | —               |

|                        | JTAG                                   | •        |                  |                 |

| ТСК                    | AG28                                   | I        | OV <sub>DD</sub> | —               |

| TDI                    | AH28                                   | I        | OV <sub>DD</sub> | 12              |

| TDO                    | AF28                                   | 0        | OV <sub>DD</sub> | —               |

| TMS                    | AH27                                   | I        | OV <sub>DD</sub> | 12              |

| TRST                   | AH23                                   | I        | OV <sub>DD</sub> | 12              |

| Signal        | Package Pin Number | Pin Type | Power<br>Supply | Notes |

|---------------|--------------------|----------|-----------------|-------|

| SD_IMP_CAL_RX | L28                | I        | 200 Ω to<br>GND | —     |

| SD_IMP_CAL_TX | AB26               | I        | 100 Ω to<br>GND | —     |

| SD_PLL_TPA    | U26                | 0        | —               | 24    |

#### Table 73. MPC8545E Pinout Listing (continued)

Note: All note references in this table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

Table 74 provides the pin-out listing for the MPC8543E 783 FC-PBGA package.

#### NOTE

All note references in the following table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

Table 74. MPC8543E Pinout Listing

| Signal         | Package Pin Number                                                                                                                                                                            | Pin Type | Power<br>Supply  | Notes    |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

|                | PCI1 (One 32-Bit)                                                                                                                                                                             |          |                  | •        |

| Reserved       | AB14, AC15, AA15, Y16, W16, AB16, AC16,<br>AA16, AE17, AA18, W18, AC17, AD16, AE16,<br>Y17, AC18,                                                                                             |          | _                | 110      |

| GPOUT[8:15]    | AB18, AA19, AB19, AB21, AA20, AC20, AB20, AB22                                                                                                                                                | 0        | OV <sub>DD</sub> | —        |

| GPIN[8:15]     | AC22, AD21, AB23, AF23, AD23, AE23, AC23, AC24                                                                                                                                                | I        | OV <sub>DD</sub> | 111      |

| PCI1_AD[31:0]  | AH6, AE7, AF7, AG7, AH7, AF8, AH8, AE9,<br>AH9, AC10, AB10, AD10, AG10, AA10, AH10,<br>AA11, AB12, AE12, AG12, AH12, AB13, AA12,<br>AC13, AE13, Y14, W13, AG13, V14, AH13,<br>AC14, Y15, AB15 | I/O      | OV <sub>DD</sub> | 17       |

| Reserved       | AF15, AD14, AE15, AD15                                                                                                                                                                        | _        | -                | 110      |

| PCI1_C_BE[3:0] | AF9, AD11, Y12, Y13                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 17       |

| Reserved       | W15                                                                                                                                                                                           |          |                  | 110      |

| PCI1_GNT[4:1]  | AG6, AE6, AF5, AH5                                                                                                                                                                            | 0        | OV <sub>DD</sub> | 5, 9, 35 |

| PCI1_GNT0      | AG5                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | —        |

| PCI1_IRDY      | AF11                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_PAR       | AD12                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | —        |

| PCI1_PERR      | AC12                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_SERR      | V13                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2, 4     |

| PCI1_STOP      | W12                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |

| Signal                | Package Pin Number                    | Pin Type    | Power<br>Supply  | Notes    |

|-----------------------|---------------------------------------|-------------|------------------|----------|

| GPOUT[0:5]            | N9, N10, P8, N7, R9, N5               | 0           | LV <sub>DD</sub> |          |

| cfg_dram_type0/GPOUT6 | R8                                    | 0           | LV <sub>DD</sub> | 5, 9     |

| GPOUT7                | N6                                    | 0           | LV <sub>DD</sub> | -        |

| Reserved              | P1                                    | —           | _                | 104      |

| Reserved              | R6                                    | —           | _                | 104      |

| Reserved              | P6                                    | —           | —                | 15       |

| Reserved              | N4                                    | —           | _                | 105      |

| FIFO1_RXC2            | P5                                    | I           | LV <sub>DD</sub> | 104      |

| Reserved              | R1                                    | —           | _                | 104      |

| Reserved              | P10                                   | —           | _                | 105      |

| FIFO1_TXC2            | P7                                    | 0           | LV <sub>DD</sub> | 15       |

| cfg_dram_type1        | R10                                   | 0           | LV <sub>DD</sub> | 5, 9     |

| Thre                  | ee-Speed Ethernet Controller (Gigabit | Ethernet 3) |                  |          |

| TSEC3_TXD[3:0]        | V8, W10, Y10, W7                      | 0           | TV <sub>DD</sub> | 5, 9, 2  |

| TSEC3_RXD[3:0]        | Y1, W3, W5, W4                        | I           | TV <sub>DD</sub> | _        |

| TSEC3_GTX_CLK         | W8                                    | 0           | TV <sub>DD</sub> | _        |

| TSEC3_RX_CLK          | W2                                    | I           | TV <sub>DD</sub> | <b>—</b> |

| TSEC3_RX_DV           | W1                                    | I           | TV <sub>DD</sub> | _        |

| TSEC3_RX_ER           | Y2                                    | I           | TV <sub>DD</sub> | _        |

| TSEC3_TX_CLK          | V10                                   | I           | TV <sub>DD</sub> | _        |

| TSEC3_TX_EN           | V9                                    | 0           | TV <sub>DD</sub> | 30       |

| TSEC3_TXD[7:4]        | AB8, Y7, AA7, Y8                      | 0           | TV <sub>DD</sub> | 5, 9, 2  |

| TSEC3_RXD[7:4]        | AA1, Y3, AA2, AA4                     | I           | TV <sub>DD</sub> | _        |

| Reserved              | AA5                                   | _           | _                | 15       |

| TSEC3_COL             | Y5                                    | I           | TV <sub>DD</sub> | - 1      |

| TSEC3_CRS             | AA3                                   | I/O         | TV <sub>DD</sub> | 31       |

| TSEC3_TX_ER           | AB6                                   | 0           | TV <sub>DD</sub> | - 1      |

|                       | DUART                                 | 1           |                  |          |

| UART_CTS[0:1]         | AB3, AC5                              | I           | OV <sub>DD</sub> | -        |

| UART_RTS[0:1]         | AC6, AD7                              | 0           | OV <sub>DD</sub> | 1 -      |

| UART_SIN[0:1]         | AB5, AC7                              | I           | OV <sub>DD</sub> | <u> </u> |

| UART_SOUT[0:1]        | AB7, AD8                              | 0           | OV <sub>DD</sub> | <u> </u> |

|                       | I <sup>2</sup> C interface            | I           |                  | _1       |

| IIC1_SCL              | AG22                                  | I/O         | OV <sub>DD</sub> | 4, 27    |

|                       |                                       |             |                  | _1       |

#### Table 74. MPC8543E Pinout Listing (continued)

| Signal                 | Package Pin Number                       | Pin Type | Power<br>Supply  | Notes           |

|------------------------|------------------------------------------|----------|------------------|-----------------|

| IIC1_SDA               | AG21                                     | I/O      | OV <sub>DD</sub> | 4, 27           |

| IIC2_SCL               | AG15                                     | I/O      | OV <sub>DD</sub> | 4, 27           |

| IIC2_SDA               | AG14                                     | I/O      | OV <sub>DD</sub> | 4, 27           |

|                        | SerDes                                   | 1        |                  |                 |

| SD_RX[0:7]             | M28, N26, P28, R26, W26, Y28, AA26, AB28 | Ι        | XV <sub>DD</sub> | —               |

| SD_RX[0:7]             | M27, N25, P27, R25, W25, Y27, AA25, AB27 | I        | XV <sub>DD</sub> | _               |

| SD_TX[0:7]             | M22, N20, P22, R20, U20, V22, W20, Y22   | 0        | XV <sub>DD</sub> | —               |

| SD_TX[0:7]             | M23, N21, P23, R21, U21, V23, W21, Y23   | 0        | XV <sub>DD</sub> | _               |

| SD_PLL_TPD             | U28                                      | 0        | XV <sub>DD</sub> | 24              |

| SD_REF_CLK             | T28                                      | Ι        | XV <sub>DD</sub> | —               |

| SD_REF_CLK             | T27                                      | Ι        | XV <sub>DD</sub> | _               |

| Reserved               | AC1, AC3                                 | —        | _                | 2               |

| Reserved               | M26, V28                                 | _        | —                | 32              |

| Reserved               | M25, V27                                 | _        | _                | 34              |

| Reserved               | M20, M21, T22, T23                       | —        | _                | 38              |

|                        | General-Purpose Output                   |          |                  |                 |

| GPOUT[24:31]           | K26, K25, H27, G28, H25, J26, K24, K23   | 0        | BV <sub>DD</sub> | —               |

|                        | System Control                           |          |                  |                 |

| HRESET                 | AG17                                     | Ι        | OV <sub>DD</sub> | —               |

| HRESET_REQ             | AG16                                     | 0        | $OV_DD$          | 29              |

| SRESET                 | AG20                                     | I        | OV <sub>DD</sub> | —               |

| CKSTP_IN               | AA9                                      | Ι        | $OV_{DD}$        | —               |

| CKSTP_OUT              | AA8                                      | 0        | $OV_{DD}$        | 2, 4            |

|                        | Debug                                    |          |                  |                 |

| TRIG_IN                | AB2                                      | Ι        | OV <sub>DD</sub> | —               |

| TRIG_OUT/READY/QUIESCE | AB1                                      | 0        | OV <sub>DD</sub> | 6, 9, 19,<br>29 |

| MSRCID[0:1]            | AE4, AG2                                 | 0        | OV <sub>DD</sub> | 5, 6, 9         |

| MSRCID[2:4]            | AF3, AF1, AF2                            | 0        | OV <sub>DD</sub> | 6, 19, 29       |

| MDVAL                  | AE5                                      | 0        | $OV_{DD}$        | 6               |

| CLK_OUT                | AE21                                     | 0        | OV <sub>DD</sub> | 11              |

|                        | Clock                                    |          |                  |                 |

| RTC                    | AF16                                     | Ι        | $OV_{DD}$        | —               |

| SYSCLK                 | AH17                                     | I        | OV <sub>DD</sub> |                 |

| Signal           | Package Pin Number                                                                                                                                                | Pin Type                                                              | Power<br>Supply  | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------|-------|

| TV <sub>DD</sub> | W9, Y6                                                                                                                                                            | Power for<br>TSEC3 and<br>TSEC4<br>(2,5 V, 3.3 V)                     | TV <sub>DD</sub> | _     |

| GV <sub>DD</sub> | B3, B11, C7, C9, C14, C17, D4, D6, D10, D15,<br>E2, E8, E11, E18, F5, F12, F16, G3, G7, G9,<br>G11, H5, H12, H15, H17, J10, K3, K12, K16,<br>K18, L6, M4, M8, M13 | Power for<br>DDR1 and<br>DDR2<br>DRAM I/O<br>voltage<br>(1.8 V,2.5 V) | GV <sub>DD</sub> | _     |

| BV <sub>DD</sub> | C21, C24, C27, E20, E25, G19, G23, H26, J20                                                                                                                       | Power for<br>local bus<br>(1.8 V, 2.5 V,<br>3.3 V)                    | BV <sub>DD</sub> | _     |

| V <sub>DD</sub>  | M19, N12, N14, N16, N18, P11, P13, P15, P17,<br>P19, R12, R14, R16, R18, T11, T13, T15, T17,<br>T19, U12, U14, U16, U18, V17, V19                                 | Power for core (1.1 V)                                                | V <sub>DD</sub>  | -     |

| SV <sub>DD</sub> | L25, L27, M24, N28, P24, P26, R24, R27, T25,<br>V24, V26, W24, W27, Y25, AA28, AC27                                                                               | Core power<br>for SerDes<br>transceivers<br>(1.1 V)                   | SV <sub>DD</sub> | _     |

| XV <sub>DD</sub> | L20, L22, N23, P21, R22, T20, U23, V21, W22,<br>Y20                                                                                                               | Pad power<br>for SerDes<br>transceivers<br>(1.1 V)                    | XV <sub>DD</sub> | _     |

| AVDD_LBIU        | J28                                                                                                                                                               | Power for<br>local bus<br>PLL<br>(1.1 V)                              | _                | 26    |

| AVDD_PCI1        | AH21                                                                                                                                                              | Power for<br>PCI1 PLL<br>(1.1 V)                                      | _                | 26    |

| AVDD_PCI2        | AH22                                                                                                                                                              | Power for<br>PCI2 PLL<br>(1.1 V)                                      | _                | 26    |

| AVDD_CORE        | AH15                                                                                                                                                              | Power for<br>e500 PLL<br>(1.1 V)                                      | _                | 26    |

| AVDD_PLAT        | AH19                                                                                                                                                              | Power for<br>CCB PLL<br>(1.1 V)                                       | _                | 26    |

| AVDD_SRDS        | U25                                                                                                                                                               | Power for<br>SRDSPLL<br>(1.1 V)                                       | _                | 26    |

| SENSEVDD         | M14                                                                                                                                                               | 0                                                                     | V <sub>DD</sub>  | 13    |

#### Table 74. MPC8543E Pinout Listing (continued)

## 20.3 e500 Core PLL Ratio

This table describes the clock ratio between the e500 core complex bus (CCB) and the e500 core clock. This ratio is determined by the binary value of LBCTL, LALE, and LGPL2 at power up, as shown in this table.

| Binary Value of<br>LBCTL, LALE, LGPL2<br>Signals | e500 core:CCB Clock Ratio | Binary Value of<br>LBCTL, LALE, LGPL2<br>Signals | e500 core:CCB Clock Ratio |  |

|--------------------------------------------------|---------------------------|--------------------------------------------------|---------------------------|--|

| 000                                              | 4:1                       | 100                                              | 2:1                       |  |

| 001                                              | 9:2                       | 101                                              | 5:2                       |  |

| 010                                              | Reserved                  | 110                                              | 3:1                       |  |

| 011                                              | 3:2                       | 111                                              | 7:2                       |  |

| Table 82. e500 | Core to CCB | <b>Clock Ratio</b> |

|----------------|-------------|--------------------|

|----------------|-------------|--------------------|

### 20.4 Frequency Options

Table 83This table shows the expected frequency values for the platform frequency when using a CCB clock to SYSCLK ratio in comparison to the memory bus clock speed.

| CCB to<br>SYSCLK Ratio | SYSCLK (MHz)                 |     |       |       |       |     |     |     |        |

|------------------------|------------------------------|-----|-------|-------|-------|-----|-----|-----|--------|

|                        | 16.66                        | 25  | 33.33 | 41.66 | 66.66 | 83  | 100 | 111 | 133.33 |

|                        | Platform/CCB Frequency (MHz) |     |       |       |       |     |     |     |        |

| 2                      |                              |     |       |       |       |     |     |     |        |

| 3                      |                              |     |       |       |       |     |     | 333 | 400    |

| 4                      |                              |     |       |       |       | 333 | 400 | 445 | 533    |