#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

•XF

| Product Status                  | Obsolete                                                    |

|---------------------------------|-------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 800MHz                                                      |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                       |

| RAM Controllers                 | DDR, DDR2, SDRAM                                            |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | · ·                                                         |

| Ethernet                        | 10/100/1000Mbps (4)                                         |

| SATA                            | · ·                                                         |

| USB                             | · ·                                                         |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                            |

| Operating Temperature           | 0°C ~ 105°C (TA)                                            |

| Security Features               | Cryptography, Random Number Generator                       |

| Package / Case                  | 783-BBGA, FCBGA                                             |

| Supplier Device Package         | 783-FCBGA (29x29)                                           |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8545epxangb |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Performance monitor facility that is similar to, but separate from, the device performance monitor

The e500 defines features that are not implemented on this device. It also generally defines some features that this device implements more specifically. An understanding of these differences can be critical to ensure proper operations.

- 512-Kbyte L2 cache/SRAM

- Flexible configuration.

- Full ECC support on 64-bit boundary in both cache and SRAM modes

- Cache mode supports instruction caching, data caching, or both.

- External masters can force data to be allocated into the cache through programmed memory ranges or special transaction types (stashing).

- 1, 2, or 4 ways can be configured for stashing only.

- Eight-way set-associative cache organization (32-byte cache lines)

- Supports locking entire cache or selected lines. Individual line locks are set and cleared through Book E instructions or by externally mastered transactions.

- Global locking and Flash clearing done through writes to L2 configuration registers

- Instruction and data locks can be Flash cleared separately.

- SRAM features include the following:

- I/O devices access SRAM regions by marking transactions as snoopable (global).

- Regions can reside at any aligned location in the memory map.

- Byte-accessible ECC is protected using read-modify-write transaction accesses for smaller-than-cache-line accesses.

- Address translation and mapping unit (ATMU)

- Eight local access windows define mapping within local 36-bit address space.

- Inbound and outbound ATMUs map to larger external address spaces.

- Three inbound windows plus a configuration window on PCI/PCI-X and PCI Express

- Four inbound windows plus a default window on RapidIO<sup>™</sup>

- Four outbound windows plus default translation for PCI/PCI-X and PCI Express

- Eight outbound windows plus default translation for RapidIO with segmentation and sub-segmentation support

- DDR/DDR2 memory controller

- Programmable timing supporting DDR and DDR2 SDRAM

- 64-bit data interface

- Four banks of memory supported, each up to 4 Gbytes, to a maximum of 16 Gbytes

- DRAM chip configurations from 64 Mbits to 4 Gbits with ×8/×16 data ports

- Full ECC support

- Page mode support

- Up to 16 simultaneous open pages for DDR

- VRRP and HSRP support for seamless router fail-over

- Up to 16 exact-match MAC addresses supported

- Broadcast address (accept/reject)

- Hash table match on up to 512 multicast addresses

- Promiscuous mode

- Buffer descriptors backward compatible with MPC8260 and MPC860T 10/100 Ethernet programming models

- RMON statistics support

- 10-Kbyte internal transmit and 2-Kbyte receive FIFOs

- MII management interface for control and status

- Ability to force allocation of header information and buffer descriptors into L2 cache

- OCeaN switch fabric

- Full crossbar packet switch

- Reorders packets from a source based on priorities

- Reorders packets to bypass blocked packets

- Implements starvation avoidance algorithms

- Supports packets with payloads of up to 256 bytes

- Integrated DMA controller

- Four-channel controller

- All channels accessible by both the local and remote masters

- Extended DMA functions (advanced chaining and striding capability)

- Support for scatter and gather transfers

- Misaligned transfer capability

- Interrupt on completed segment, link, list, and error

- Supports transfers to or from any local memory or I/O port

- Selectable hardware-enforced coherency (snoop/no snoop)

- Ability to start and flow control each DMA channel from external 3-pin interface

- Ability to launch DMA from single write transaction

- Two PCI/PCI-X controllers

- PCI 2.2 and PCI-X 1.0 compatible

- One 32-/64-bit PCI/PCI-X port with support for speeds of up to 133 MHz (maximum PCI-X frequency in synchronous mode is 110 MHz)

- One 32-bit PCI port with support for speeds from 16 to 66 MHz (available when the other port is in 32-bit mode)

- Host and agent mode support

- 64-bit dual address cycle (DAC) support

- PCI-X supports multiple split transactions

- Supports PCI-to-memory and memory-to-PCI streaming

# 4.3 eTSEC Gigabit Reference Clock Timing

The following table provides the eTSEC gigabit reference clocks (EC\_GTX\_CLK125) AC timing specifications for the device.

| Parameter/Condition                                                  | Symbol            | Min      | Тур | Max         | Unit | Notes |

|----------------------------------------------------------------------|-------------------|----------|-----|-------------|------|-------|

| EC_GTX_CLK125 frequency                                              | f <sub>G125</sub> | _        | 125 | —           | MHz  | _     |

| EC_GTX_CLK125 cycle time                                             | t <sub>G125</sub> | —        | 8   | —           | ns   |       |

| EC_GTX_CLK125 rise and fall time<br>L/TVDD = 2.5 V<br>L/TVDD = 3.3 V |                   | —        | _   | 0.75<br>1.0 | ns   | 1     |

| EC_GTX_CLK125 duty cycle<br>GMII, TBI<br>1000Base-T for RGMII, RTBI  |                   | 45<br>47 | _   | 55<br>53    | %    | 2, 3  |

| Table 6. EC_ | GTX_CLK125 AC Tim | ning Specifications |

|--------------|-------------------|---------------------|

|--------------|-------------------|---------------------|

Notes:

1. Rise and fall times for EC\_GTX\_CLK125 are measured from 0.5 and 2.0 V for L/TV<sub>DD</sub> = 2.5 V, and from 0.6 and 2.7 V for L/TV<sub>DD</sub> = 3.3 V.

- 2. Timing is guaranteed by design and characterization.

- 3. EC\_GTX\_CLK125 is used to generate the GTX clock TSEC*n*\_GTX\_CLK for the eTSEC transmitter with 2% degradation. EC\_GTX\_CLK125 duty cycle can be loosened from 47/53% as long as the PHY device can tolerate the duty cycle generated by the TSEC*n*\_GTX\_CLK. See Section 8.2.6, "RGMII and RTBI AC Timing Specifications," for duty cycle for 10Base-T and 100Base-T reference clock.

# 4.4 PCI/PCI-X Reference Clock Timing

When the PCI/PCI-X controller is configured for asynchronous operation, the reference clock for the PCI/PCI-x controller is not the SYSCLK input, but instead the PCIn\_CLK. The following table provides the PCI/PCI-X reference clock AC timing specifications for the device.

| Table 7. PCIn_CLK AC Timing Specifications | Table 7. PCI <i>n</i> | CLK | AC Timing | Specifications |

|--------------------------------------------|-----------------------|-----|-----------|----------------|

|--------------------------------------------|-----------------------|-----|-----------|----------------|

At recommended operating conditions (see Table 2) with  $OV_{DD} = 3.3 \text{ V} \pm 165 \text{ mV}$ .

| Parameter/Condition         | Symbol                                    | Min | Тур | Мах | Unit | Notes |

|-----------------------------|-------------------------------------------|-----|-----|-----|------|-------|

| PCIn_CLK frequency          | f <sub>PCICLK</sub>                       | 16  | —   | 133 | MHz  | —     |

| PCIn_CLK cycle time         | t <sub>PCICLK</sub>                       | 7.5 | —   | 60  | ns   | —     |

| PCIn_CLK rise and fall time | t <sub>PCIKH</sub> , t <sub>PCIKL</sub>   | 0.6 | 1.0 | 2.1 | ns   | 1, 2  |

| PCIn_CLK duty cycle         | t <sub>PCIKHKL</sub> /t <sub>PCICLK</sub> | 40  | —   | 60  | %    | 2     |

Notes:

1. Rise and fall times for SYSCLK are measured at 0.6 and 2.7 V.

2. Timing is guaranteed by design and characterization.

# 6.2.2 DDR SDRAM Output AC Timing Specifications

### Table 19. DDR SDRAM Output AC Timing Specifications

At recommended operating conditions.

| Parameter                                                                          | Symbol <sup>1</sup>                         | Min                             | Max                         | Unit | Notes |

|------------------------------------------------------------------------------------|---------------------------------------------|---------------------------------|-----------------------------|------|-------|

| MCK[n] cycle time, MCK[n]/MCK[n] crossing                                          | t <sub>MCK</sub>                            | 3.75                            | 6                           | ns   | 2     |

| ADDR/CMD output setup with respect to MCK<br>533 MHz<br>400 MHz<br>333 MHz         | t <sub>DDKHAS</sub>                         | 1.48<br>1.95<br>2.40            |                             | ns   | 3     |

| ADDR/CMD output hold with respect to MCK<br>533 MHz<br>400 MHz<br>333 MHz          | t <sub>DDKHAX</sub>                         | 1.48<br>1.95<br>2.40            |                             | ns   | 3     |

| MCS[ <i>n</i> ] output setup with respect to MCK<br>533 MHz<br>400 MHz<br>333 MHz  | t <sub>DDKHCS</sub>                         | 1.48<br>1.95<br>2.40            |                             | ns   | 3     |

| MCS[ <i>n</i> ] output hold with respect to MCK<br>533 MHz<br>400 MHz<br>333 MHz   | t <sub>DDKHCX</sub>                         | 1.48<br>1.95<br>2.40            |                             | ns   | 3     |

| MCK to MDQS Skew                                                                   | t <sub>DDKHMH</sub>                         | -0.6                            | 0.6                         | ns   | 4     |

| MDQ/MECC/MDM output setup with respect<br>to MDQS<br>533 MHz<br>400 MHz<br>333 MHz | <sup>t</sup> DDKHDS,<br><sup>t</sup> DDKLDS | 538<br>700<br>900               |                             | ps   | 5     |

| MDQ/MECC/MDM output hold with respect to<br>MDQS<br>533 MHz<br>400 MHz<br>333 MHz  | <sup>t</sup> DDKHDX,<br><sup>t</sup> DDKLDX | 538<br>700<br>900               |                             | ps   | 5     |

| MDQS preamble start                                                                | t <sub>DDKHMP</sub>                         | $-0.5\times t_{\text{MCK}}-0.6$ | $-0.5 \times t_{MCK}$ + 0.6 | ns   | 6     |

| Parameters                                                                      | Symbol                             | Min    | Мах                                      | Unit | Notes   |

|---------------------------------------------------------------------------------|------------------------------------|--------|------------------------------------------|------|---------|

| Supply voltage 2.5 V                                                            | LV <sub>DD</sub> /TV <sub>DD</sub> | 2.37   | 2.63                                     | V    | 1, 2    |

| Output high voltage ( $LV_{DD}/TV_{DD} = Min$ ,<br>$I_{OH} = -1.0 \text{ mA}$ ) | V <sub>OH</sub>                    | 2.00   | LV <sub>DD</sub> /TV <sub>DD</sub> + 0.3 | V    | _       |

| Output low voltage ( $LV_{DD}/TV_{DD} = Min$ ,<br>I <sub>OL</sub> = 1.0 mA)     | V <sub>OL</sub>                    | GND0.3 | 0.40                                     | V    | _       |

| Input high voltage                                                              | V <sub>IH</sub>                    | 1.70   | $LV_{DD}/TV_{DD} + 0.3$                  | V    | —       |

| Input low voltage                                                               | V <sub>IL</sub>                    | -0.3   | 0.90                                     | V    | —       |

| Input high current ( $V_{IN} = LV_{DD}$ , $V_{IN} = TV_{DD}$ )                  | Ι <sub>ΙΗ</sub>                    | —      | 10                                       | μA   | 1, 2, 3 |

| Input low current (V <sub>IN</sub> = GND)                                       | ١ <sub>١L</sub>                    | -15    | —                                        | μA   | 3       |

Table 23. GMII, MII, RMII, TBI, RGMII, RTBI, and FIFO DC Electrical Characteristics

Notes:

1.  $LV_{DD}$  supports eTSECs 1 and 2.

2.  $\mathsf{TV}_{\mathsf{DD}}$  supports eTSECs 3 and 4.

3. Note that the symbol  $V_{IN}$ , in this case, represents the  $LV_{IN}$  and  $TV_{IN}$  symbols referenced in Table 1 and Table 2.

# 8.2 FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications

The AC timing specifications for FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI are presented in this section.

# 8.2.1 FIFO AC Specifications

The basis for the AC specifications for the eTSEC's FIFO modes is the double data rate RGMII and RTBI specifications, since they have similar performances and are described in a source-synchronous fashion like FIFO modes. However, the FIFO interface provides deliberate skew between the transmitted data and source clock in GMII fashion.

When the eTSEC is configured for FIFO modes, all clocks are supplied from external sources to the relevant eTSEC interface. That is, the transmit clock must be applied to the eTSEC*n*'s TSEC*n*\_TX\_CLK, while the receive clock must be applied to pin TSEC*n*\_RX\_CLK. The eTSEC internally uses the transmit clock to synchronously generate transmit data and outputs an echoed copy of the transmit clock back out onto the TSEC*n*\_GTX\_CLK pin (while transmit data appears on TSEC*n*\_TXD[7:0], for example). It is intended that external receivers capture eTSEC transmit data using the clock on TSEC*n*\_GTX\_CLK as a source- synchronous timing reference. Typically, the clock edge that launched the data can be used, since the clock is delayed by the eTSEC to allow acceptable set-up margin at the receiver. Note that there is relationship between the maximum FIFO speed and the platform speed. For more information see Section 4.5, "Platform to FIFO Restrictions."

# **10.2 Local Bus AC Electrical Specifications**

This table describes the timing parameters of the local bus interface at  $BV_{DD} = 3.3$  V. For information about the frequency range of local bus, see Section 20.1, "Clock Ranges."

| Parameter                                                             | Symbol <sup>1</sup>                 | Min | Max | Unit | Notes |

|-----------------------------------------------------------------------|-------------------------------------|-----|-----|------|-------|

| Local bus cycle time                                                  | t <sub>LBK</sub>                    | 7.5 | 12  | ns   | 2     |

| Local bus duty cycle                                                  | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43  | 57  | %    | —     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                  | t <sub>LBKSKEW</sub>                | _   | 150 | ps   | 7, 8  |

| Input setup to local bus clock (except LGTA/LUPWAIT)                  | t <sub>LBIVKH1</sub>                | 1.8 |     | ns   | 3, 4  |

| LGTA/LUPWAIT input setup to local bus clock                           | t <sub>LBIVKH2</sub>                | 1.7 | _   | ns   | 3, 4  |

| Input hold from local bus clock (except LGTA/LUPWAIT)                 | t <sub>LBIXKH1</sub>                | 1.0 | _   | ns   | 3, 4  |

| LGTA/LUPWAIT input hold from local bus clock                          | t <sub>LBIXKH2</sub>                | 1.0 |     | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) | t <sub>LBOTOT</sub>                 | 1.5 | _   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)             | t <sub>LBKHOV1</sub>                | _   | 2.0 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                             | t <sub>LBKHOV2</sub>                | _   | 2.2 | ns   | 3     |

| Local bus clock to address valid for LAD                              | t <sub>LBKHOV3</sub>                | _   | 2.3 | ns   | 3     |

| Local bus clock to LALE assertion                                     | t <sub>LBKHOV4</sub>                | _   | 2.3 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)            | t <sub>LBKHOX1</sub>                | 0.7 | _   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                          | t <sub>LBKHOX2</sub>                | 0.7 | _   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)    | t <sub>LBKHOZ1</sub>                |     | 2.5 | ns   | 5     |

| Local bus clock to output high impedance for LAD/LDP                  | t <sub>LBKHOZ2</sub>                | _   | 2.5 | ns   | 5     |

### Table 40. Local Bus Timing Parameters (BV<sub>DD</sub> = 3.3 V)—PLL Enabled

#### Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKH0X</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

- 2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 3.3-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 8. Guaranteed by design.

| Parameter                                                             | Symbol <sup>1</sup>  | Min  | Max  | Unit | Notes |

|-----------------------------------------------------------------------|----------------------|------|------|------|-------|

| LGTA/LUPWAIT input hold from local bus clock                          | t <sub>LBIXKL2</sub> | -1.3 |      | ns   | 4, 5  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) | t <sub>LBOTOT</sub>  | 1.5  |      | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)             | t <sub>LBKLOV1</sub> | _    | -0.3 | ns   |       |

| Local bus clock to data valid for LAD/LDP                             | t <sub>LBKLOV2</sub> | _    | -0.1 | ns   | 4     |

| Local bus clock to address valid for LAD                              | t <sub>LBKLOV3</sub> | _    | 0    | ns   | 4     |

| Local bus clock to LALE assertion                                     | t <sub>LBKLOV4</sub> | _    | 0    | ns   | 4     |

| Output hold from local bus clock (except LAD/LDP and LALE)            | t <sub>LBKLOX1</sub> | -3.7 |      | ns   | 4     |

| Output hold from local bus clock for LAD/LDP                          | t <sub>LBKLOX2</sub> | -3.7 |      | ns   | 4     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)    | t <sub>LBKLOZ1</sub> | _    | 0.2  | ns   | 7     |

| Local bus clock to output high impedance for LAD/LDP                  | t <sub>LBKLOZ2</sub> | _    | 0.2  | ns   | 7     |

#### Table 42. Local Bus Timing Parameters—PLL Bypassed (continued)

#### Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKH0X</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

All timings are in reference to local bus clock for PLL bypass mode. Timings may be negative with respect to the local bus clock because the actual launch and capture of signals is done with the internal launch/capture clock, which precedes LCLK by t<sub>LBKHKT</sub>.

Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

4. All signals are measured from  $BV_{DD}/2$  of the rising edge of local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 3.3-V signaling levels.

5. Input timings are measured at the pin.

6. The value of t<sub>LBOTOT</sub> is the measurement of the minimum time between the negation of LALE and any change in LAD.

7. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 8. Guaranteed by characterization.

- 9. Guaranteed by design.

# 16.2.4 AC Requirements for SerDes Reference Clocks

The clock driver selected must provide a high quality reference clock with low phase noise and cycle-to-cycle jitter. Phase noise less than 100 kHz can be tracked by the PLL and data recovery loops and is less of a problem. Phase noise above 15 MHz is filtered by the PLL. The most problematic phase noise occurs in the 1–15 MHz range. The source impedance of the clock driver must be 50  $\Omega$  to match the transmission line and reduce reflections which are a source of noise to the system.

The detailed AC requirements of the SerDes reference clocks are defined by each interface protocol based on application usage. See the following sections for detailed information:

- Section 17.2, "AC Requirements for PCI Express SerDes Clocks"

- Section 18.2, "AC Requirements for Serial RapidIO SD\_REF\_CLK and SD\_REF\_CLK"

## 16.2.4.1 Spread Spectrum Clock

SD\_REF\_CLK/SD\_REF\_CLK are designed to work with a spread spectrum clock (+0% to -0.5% spreading at 30–33 kHz rate is allowed), assuming both ends have same reference clock. For better results, a source without significant unintended modulation must be used.

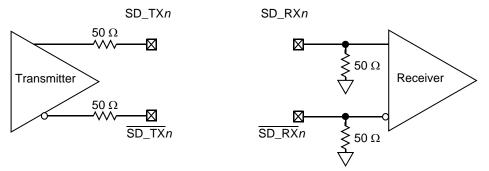

# 16.3 SerDes Transmitter and Receiver Reference Circuits

Figure 47 shows the reference circuits for SerDes data lane's transmitter and receiver.

Figure 47. SerDes Transmitter and Receiver Reference Circuits

The DC and AC specification of SerDes data lanes are defined in each interface protocol section below (PCI Express, Serial Rapid IO, or SGMII) in this document based on the application usage:

- Section 17, "PCI Express"

- Section 18, "Serial RapidIO"

Note that external an AC coupling capacitor is required for the above three serial transmission protocols with the capacitor value defined in the specification of each protocol section.

components are included in this requirement. The reference impedance for return loss measurements is  $100-\Omega$  resistive for differential return loss and  $25-\Omega$  resistive for common mode.

| Characteristic                                     | Symbol          | Rai  | nge               | Unit   | Notes                                                        |

|----------------------------------------------------|-----------------|------|-------------------|--------|--------------------------------------------------------------|

| Characteristic                                     | Symbol          | Min  | Max               | Unit   | NOICS                                                        |

| Differential input voltage                         | V <sub>IN</sub> | 200  | 1600              | mVp-p  | Measured at receiver                                         |

| Deterministic jitter tolerance                     | J <sub>D</sub>  | 0.37 | —                 | UI p-p | Measured at receiver                                         |

| Combined deterministic and random jitter tolerance | J <sub>DR</sub> | 0.55 | —                 | UI p-p | Measured at receiver                                         |

| Total jitter tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65 | _                 | UI p-p | Measured at receiver                                         |

| Multiple input skew                                | S <sub>MI</sub> | —    | 24                | ns     | Skew at the receiver input between lanes of a multilane link |

| Bit error rate                                     | BER             | —    | 10 <sup>-12</sup> | —      | —                                                            |

| Unit interval                                      | UI              | 800  | 800               | ps     | ±100 ppm                                                     |

#### Note:

1. Total jitter is composed of three components, deterministic jitter, random jitter, and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 53. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk, and other variable system effects.

#### Table 67. Receiver AC Timing Specifications—2.5 GBaud

| Characteristic                                     | Symbol          | Rai  | nge               | Unit   | Notes                                                        |

|----------------------------------------------------|-----------------|------|-------------------|--------|--------------------------------------------------------------|

| Characteristic                                     | Symbol          | Min  | Max               | Unit   | NULES                                                        |

| Differential input voltage                         | V <sub>IN</sub> | 200  | 1600              | mVp-p  | Measured at receiver                                         |

| Deterministic jitter tolerance                     | J <sub>D</sub>  | 0.37 | _                 | UI p-p | Measured at receiver                                         |

| Combined deterministic and random jitter tolerance | J <sub>DR</sub> | 0.55 | —                 | UI p-p | Measured at receiver                                         |

| Total jitter tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65 | —                 | UI p-p | Measured at receiver                                         |

| Multiple input skew                                | S <sub>MI</sub> | _    | 24                | ns     | Skew at the receiver input between lanes of a multilane link |

| Bit error rate                                     | BER             | _    | 10 <sup>-12</sup> |        | —                                                            |

| Unit interval                                      | UI              | 400  | 400               | ps     | ±100 ppm                                                     |

#### Note:

1. Total jitter is composed of three components, deterministic jitter, random jitter, and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 53. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk, and other variable system effects.

Package Description

| Signal           | Package Pin Number                                                                                                                                                | Pin Type                                                          | Power<br>Supply  | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------|-------|

| LV <sub>DD</sub> | N8, R7, T9, U6                                                                                                                                                    | Power for<br>TSEC1 and<br>TSEC2<br>(2.5 V, 3.3 V)                 | LV <sub>DD</sub> | _     |

| TV <sub>DD</sub> | W9, Y6                                                                                                                                                            | Power for<br>TSEC3 and<br>TSEC4<br>(2,5 V, 3.3 V)                 | TV <sub>DD</sub> | _     |

| GV <sub>DD</sub> | B3, B11, C7, C9, C14, C17, D4, D6, D10, D15,<br>E2, E8, E11, E18, F5, F12, F16, G3, G7, G9,<br>G11, H5, H12, H15, H17, J10, K3, K12, K16,<br>K18, L6, M4, M8, M13 | Power for<br>DDR1 and<br>DDR2 DRAM<br>I/O voltage<br>(1.8 V, 2.5) | GV <sub>DD</sub> |       |

| BV <sub>DD</sub> | C21, C24, C27, E20, E25, G19, G23, H26, J20                                                                                                                       | Power for local<br>bus (1.8 V,<br>2.5 V, 3.3 V)                   | BV <sub>DD</sub> |       |

| V <sub>DD</sub>  | M19, N12, N14, N16, N18, P11, P13, P15, P17,<br>P19, R12, R14, R16, R18, T11, T13, T15, T17,<br>T19, U12, U14, U16, U18, V17, V19                                 | Power for core<br>(1.1 V)                                         | V <sub>DD</sub>  |       |

| SV <sub>DD</sub> | L25, L27, M24, N28, P24, P26, R24, R27, T25,<br>V24, V26, W24, W27, Y25, AA28, AC27                                                                               | Core Power<br>for SerDes<br>transceivers<br>(1.1 V)               | SV <sub>DD</sub> | —     |

| XV <sub>DD</sub> | L20, L22, N23, P21, R22, T20, U23, V21, W22,<br>Y20                                                                                                               | Pad Power for<br>SerDes<br>transceivers<br>(1.1 V)                | XV <sub>DD</sub> |       |

| AVDD_LBIU        | J28                                                                                                                                                               | Power for local<br>bus PLL<br>(1.1 V)                             | _                | 26    |

| AVDD_PCI1        | AH21                                                                                                                                                              | Power for<br>PCI1 PLL<br>(1.1 V)                                  | _                | 26    |

| AVDD_PCI2        | AH22                                                                                                                                                              | Power for<br>PCI2 PLL<br>(1.1 V)                                  | _                | 26    |

| AVDD_CORE        | AH15                                                                                                                                                              | Power for<br>e500 PLL (1.1<br>V)                                  | _                | 26    |

| AVDD_PLAT        | AH19                                                                                                                                                              | Powerfor CCB<br>PLL (1.1 V)                                       | —                | 26    |

| AVDD_SRDS        | U25                                                                                                                                                               | Power for<br>SRDSPLL<br>(1.1 V)                                   | _                | 26    |

| SENSEVDD         | M14                                                                                                                                                               | 0                                                                 | V <sub>DD</sub>  | 13    |

### Table 71. MPC8548E Pinout Listing (continued)

|                               |                                      |           | _                |                |  |

|-------------------------------|--------------------------------------|-----------|------------------|----------------|--|

| Signal                        | Package Pin Number                   | Pin Type  | Power<br>Supply  | Notes          |  |

| TSEC2_TX_ER                   | R10                                  | 0         | LV <sub>DD</sub> | 5, 9, 33       |  |

| Three-S                       | peed Ethernet Controller (Gigabit Et | hernet 3) |                  | -              |  |

| TSEC3_TXD[3:0]                | V8, W10, Y10, W7                     | 0         | TV <sub>DD</sub> | 5, 9, 29       |  |

| TSEC3_RXD[3:0]                | Y1, W3, W5, W4                       | I         | TV <sub>DD</sub> | —              |  |

| TSEC3_GTX_CLK                 | W8                                   | 0         | TV <sub>DD</sub> | _              |  |

| TSEC3_RX_CLK                  | W2                                   | I         | TV <sub>DD</sub> | —              |  |

| TSEC3_RX_DV                   | W1                                   | I         | TV <sub>DD</sub> | —              |  |

| TSEC3_RX_ER                   | Y2                                   | I         | TV <sub>DD</sub> | —              |  |

| TSEC3_TX_CLK                  | V10                                  | I         | TV <sub>DD</sub> | —              |  |

| TSEC3_TX_EN                   | V9                                   | 0         | TV <sub>DD</sub> | 30             |  |

| Three-S                       | peed Ethernet Controller (Gigabit Et | hernet 4) |                  | -              |  |

| TSEC4_TXD[3:0]/TSEC3_TXD[7:4] | AB8, Y7, AA7, Y8                     | 0         | TV <sub>DD</sub> | 1, 5, 9,<br>29 |  |

| TSEC4_RXD[3:0]/TSEC3_RXD[7:4] | AA1, Y3, AA2, AA4                    | I         | TV <sub>DD</sub> | 1              |  |

| TSEC4_GTX_CLK                 | AA5                                  | 0         | TV <sub>DD</sub> |                |  |

| TSEC4_RX_CLK/TSEC3_COL        | Y5                                   | I         | TV <sub>DD</sub> | 1              |  |

| TSEC4_RX_DV/TSEC3_CRS         | X_DV/TSEC3_CRS AA3 I/O               |           |                  |                |  |

| TSEC4_TX_EN/TSEC3_TX_ER       | AB6                                  | 0         | TV <sub>DD</sub> | 1, 30          |  |

|                               | DUART                                |           |                  |                |  |

| UART_CTS[0:1]                 | AB3, AC5                             | I         | OV <sub>DD</sub> | —              |  |

| UART_RTS[0:1]                 | AC6, AD7                             | 0         | OV <sub>DD</sub> | —              |  |

| UART_SIN[0:1]                 | AB5, AC7                             | I         | OV <sub>DD</sub> | —              |  |

| UART_SOUT[0:1]                | AB7, AD8                             | 0         | OV <sub>DD</sub> | —              |  |

|                               | I <sup>2</sup> C Interface           |           |                  | -              |  |

| IIC1_SCL                      | AG22                                 | I/O       | OV <sub>DD</sub> | 4, 27          |  |

| IIC1_SDA                      | AG21                                 | I/O       | OV <sub>DD</sub> | 4, 27          |  |

| IIC2_SCL                      | IIC2_SCL AG15                        |           |                  |                |  |

| IIC2_SDA                      | AG14                                 | I/O       | OV <sub>DD</sub> | 4, 27          |  |

|                               | SerDes                               |           |                  | -              |  |

| SD_RX[0:3]                    | M28, N26, P28, R26                   | I         | XV <sub>DD</sub> | —              |  |

| SD_RX[0:3]                    | M27, N25, P27, R25                   | I         | XV <sub>DD</sub> |                |  |

| SD_TX[0:3]                    | M22, N20, P22, R20                   | 0         | XV <sub>DD</sub> | _              |  |

| SD_TX[0:3]                    | M23, N21, P23, R21                   | 0         | XV <sub>DD</sub> | _              |  |

| Reserved                      | W26, Y28, AA26, AB28                 | —         | —                | 40             |  |

| Reserved                      | W25, Y27, AA25, AB27                 | —         |                  | 40             |  |

### Table 72. MPC8547E Pinout Listing (continued)

| Signal         | Package Pin Number                       | Pin Type   | Power<br>Supply  | Notes    |

|----------------|------------------------------------------|------------|------------------|----------|

| FIFO1_RXC2     | P5                                       | I          | LV <sub>DD</sub> | 104      |

| Reserved       | R1                                       | —          | _                | 104      |

| Reserved       | P10                                      | —          | —                | 105      |

| FIFO1_TXC2     | P7                                       | 0          | LV <sub>DD</sub> | 15       |

| cfg_dram_type1 | R10                                      | I          | LV <sub>DD</sub> | 5        |

| Thre           | ee-Speed Ethernet Controller (Gigabit Et | thernet 3) |                  |          |

| TSEC3_TXD[3:0] | V8, W10, Y10, W7                         | 0          | TV <sub>DD</sub> | 5, 9, 29 |

| TSEC3_RXD[3:0] | Y1, W3, W5, W4                           | I          | TV <sub>DD</sub> |          |

| TSEC3_GTX_CLK  | W8                                       | 0          | TV <sub>DD</sub> |          |

| TSEC3_RX_CLK   | W2                                       | I          | TV <sub>DD</sub> | —        |

| TSEC3_RX_DV    | W1                                       | I          | TV <sub>DD</sub> | _        |

| TSEC3_RX_ER    | Y2                                       | I          | TV <sub>DD</sub> | _        |

| TSEC3_TX_CLK   | V10                                      | I          | TV <sub>DD</sub> | _        |

| TSEC3_TX_EN    | V9                                       | 0          | TV <sub>DD</sub> | 30       |

| TSEC3_TXD[7:4] | AB8, Y7, AA7, Y8                         | 0          | TV <sub>DD</sub> | 5, 9, 29 |

| TSEC3_RXD[7:4] | AA1, Y3, AA2, AA4                        | I          | TV <sub>DD</sub> | _        |

| Reserved       | AA5                                      | —          | —                | 15       |

| TSEC3_COL      | Y5                                       | I          | TV <sub>DD</sub> | —        |

| TSEC3_CRS      | AA3                                      | I/O        | TV <sub>DD</sub> | 31       |

| TSEC3_TX_ER    | AB6                                      | 0          | TV <sub>DD</sub> | —        |

|                | DUART                                    |            | •                |          |

| UART_CTS[0:1]  | AB3, AC5                                 | I          | OV <sub>DD</sub> |          |

| UART_RTS[0:1]  | AC6, AD7                                 | 0          | OV <sub>DD</sub> |          |

| UART_SIN[0:1]  | AB5, AC7                                 | I          | OV <sub>DD</sub> |          |

| UART_SOUT[0:1] | AB7, AD8                                 | 0          | OV <sub>DD</sub> | _        |

| <b>I</b>       | I <sup>2</sup> C interface               |            |                  | 1        |

| IIC1_SCL       | AG22                                     | I/O        | OV <sub>DD</sub> | 4, 27    |

| IIC1_SDA       | IIC1_SDA AG21 I/                         |            | OV <sub>DD</sub> | 4, 27    |

| IIC2_SCL       | AG15                                     | I/O        | OV <sub>DD</sub> | 4, 27    |

| IIC2_SDA       | AG14                                     | I/O        | OV <sub>DD</sub> | 4, 27    |

|                | SerDes                                   | 1          |                  |          |

| SD_RX[0:3]     | M28, N26, P28, R26                       | I          | XV <sub>DD</sub> | _        |

| SD_RX[0:3]     | M27, N25, P27, R25                       | I          | XV <sub>DD</sub> | —        |

| SD_TX[0:3]     | M22, N20, P22, R20                       | 0          | XV <sub>DD</sub> |          |

### Table 74. MPC8543E Pinout Listing (continued)

| Signal                   | Package Pin Number                                                                                                                                                      | Pin Type | Power<br>Supply    | Notes   |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|---------|

| MWE                      | E7                                                                                                                                                                      | 0        | GV <sub>DD</sub>   |         |

| MCAS                     | H7                                                                                                                                                                      | 0        | GV <sub>DD</sub>   | -       |

| MRAS                     | L8                                                                                                                                                                      | 0        | GV <sub>DD</sub>   | —       |

| MCKE[0:3]                | F10, C10, J11, H11                                                                                                                                                      | 0        | GV <sub>DD</sub>   | 11      |

| MCS[0:3]                 | K8, J8, G8, F8                                                                                                                                                          | 0        | GV <sub>DD</sub>   | —       |

| MCK[0:5]                 | H9, B15, G2, M9, A14, F1                                                                                                                                                | 0        | GV <sub>DD</sub>   | —       |

| MCK[0:5]                 | J9, A15, G1, L9, B14, F2                                                                                                                                                | 0        | GV <sub>DD</sub>   | —       |

| MODT[0:3]                | E6, K6, L7, M7                                                                                                                                                          | 0        | GV <sub>DD</sub>   | —       |

| MDIC[0:1]                | A19, B19                                                                                                                                                                | I/O      | GV <sub>DD</sub>   | 36      |

|                          | Local Bus Controller Interface                                                                                                                                          |          |                    |         |

| LAD[0:31]                | E27, B20, H19, F25, A20, C19, E28, J23, A25,<br>K22, B28, D27, D19, J22, K20, D28, D25, B25,<br>E22, F22, F21, C25, C22, B23, F20, A23, A22,<br>E19, A21, D21, F19, B21 | I/O      | BV <sub>DD</sub>   | _       |

| LDP[0:3]                 | K21, C28, B26, B22                                                                                                                                                      | I/O      | BV <sub>DD</sub>   | —       |

| LA[27]                   | H21                                                                                                                                                                     | 0        | BV <sub>DD</sub>   | 5, 9    |

| LA[28:31]                | H20, A27, D26, A28                                                                                                                                                      | 0        | BV <sub>DD</sub>   | 5, 7, 9 |

| LCS[0:4]                 | J25, C20, J24, G26, A26                                                                                                                                                 | 0        | BV <sub>DD</sub>   | —       |

| LCS5/DMA_DREQ2           | D23                                                                                                                                                                     | I/O      | BV <sub>DD</sub>   | 1       |

| LCS6/DMA_DACK2           | G20                                                                                                                                                                     | 0        | BV <sub>DD</sub>   | 1       |

| LCS7/DMA_DDONE2          | E21                                                                                                                                                                     | 0        | O BV <sub>DD</sub> |         |

| LWE0/LBS0/LSDDQM[0]      | G25                                                                                                                                                                     | 0        | BV <sub>DD</sub>   | 5, 9    |

| LWE1/LBS1/LSDDQM[1]      | C23                                                                                                                                                                     | 0        | BV <sub>DD</sub>   | 5, 9    |

| LWE2/LBS2/LSDDQM[2]      | J21                                                                                                                                                                     | 0        | BV <sub>DD</sub>   | 5, 9    |

| LWE3/LBS3/LSDDQM[3]      | A24                                                                                                                                                                     | 0        | BV <sub>DD</sub>   | 5, 9    |

| LALE                     | H24                                                                                                                                                                     | 0        | BV <sub>DD</sub>   | 5, 8, 9 |

| LBCTL                    | G27                                                                                                                                                                     |          | BV <sub>DD</sub>   | 5, 8, 9 |

| LGPL0/LSDA10             | F23                                                                                                                                                                     | 0        | BV <sub>DD</sub>   | 5, 9    |

| LGPL1/LSDWE              | G22                                                                                                                                                                     | 0        | BV <sub>DD</sub>   | 5, 9    |

| LGPL2/LOE/LSDRAS         | B27                                                                                                                                                                     | 0        | BV <sub>DD</sub>   | 5, 8, 9 |

| LGPL3/LSDCAS             | F24                                                                                                                                                                     | 0        | BV <sub>DD</sub>   | 5, 9    |

| LGPL4/LGTA/LUPWAIT/LPBSE | H23                                                                                                                                                                     | I/O      | BV <sub>DD</sub>   | —       |

| LGPL5                    | E26                                                                                                                                                                     | 0        | BV <sub>DD</sub>   | 5, 9    |

| LCKE                     | E24                                                                                                                                                                     | 0        | BV <sub>DD</sub>   | —       |

| LCLK[0:2]                | E23, D24, H22                                                                                                                                                           | 0        | BV <sub>DD</sub>   | _       |

# 20 Clocking

This section describes the PLL configuration of the device. Note that the platform clock is identical to the core complex bus (CCB) clock.

# 20.1 Clock Ranges

Table 75 through Table 77 provide the clocking specifications for the processor cores and Table 78, through Table 80 provide the clocking specifications for the memory bus.

|                               |                         | aximum | Process | or Core I | Frequenc | су.  |      |       |

|-------------------------------|-------------------------|--------|---------|-----------|----------|------|------|-------|

| Characteristic                | Characteristic 1000 MHz |        | 1200    | MHz       | 1333 MHz |      | Unit | Notes |

|                               | Min                     | Max    | Min     | Max       | Min      | Max  |      |       |

| e500 core processor frequency | 800                     | 1000   | 800     | 1200      | 800      | 1333 | MHz  | 1, 2  |

Table 75. Processor Core Clocking Specifications (MPC8548E and MPC8547E)

Notes:

Caution: The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

2.)The minimum e500 core frequency is based on the minimum platform frequency of 333 MHz.

### Table 76. Processor Core Clocking Specifications (MPC8545E)

|                               |     | aximum | Process | or Core I | requent    | cy ( |      |       |

|-------------------------------|-----|--------|---------|-----------|------------|------|------|-------|

| Characteristic                | 800 | MHz    | 1000    | MHz       | 1200 MHz U |      | Unit | Notes |

|                               | Min | Max    | Min     | Max       | Min        | Max  |      |       |

| e500 core processor frequency | 800 | 800    | 800     | 1000      | 800        | 1200 | MHz  | 1, 2  |

Notes:

1. **Caution:** The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

2.)The minimum e500 core frequency is based on the minimum platform frequency of 333 MHz.

| Characteristic         |     | or Core Frequency<br>00 MHz | Unit | Notes |

|------------------------|-----|-----------------------------|------|-------|

|                        | Min | Мах                         |      |       |

| Memory bus clock speed | 166 | 200                         | MHz  | 1, 2  |

### Table 80. Memory Bus Clocking Specifications (MPC8543E)

Notes:

1. **Caution:** The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

2. The memory bus speed is half of the DDR/DDR2 data rate, hence, half of the platform clock frequency.

# 20.2 CCB/SYSCLK PLL Ratio

The CCB clock is the clock that drives the e500 core complex bus (CCB), and is also called the platform clock. The frequency of the CCB is set using the following reset signals, as shown in Table 81:

- SYSCLK input signal

- Binary value on LA[28:31] at power up

Note that there is no default for this PLL ratio; these signals must be pulled to the desired values. Also note that the DDR data rate is the determining factor in selecting the CCB bus frequency, since the CCB frequency must equal the DDR data rate.

For specifications on the PCI\_CLK, see the PCI 2.2 Specification.

| Binary Value of LA[28:31] Signals | CCB:SYSCLK Ratio | Binary Value of LA[28:31] Signals | CCB:SYSCLK Ratio |

|-----------------------------------|------------------|-----------------------------------|------------------|

| 0000                              | 16:1             | 1000                              | 8:1              |

| 0001                              | Reserved         | 1001                              | 9:1              |

| 0010                              | 2:1              | 1010                              | 10:1             |

| 0011                              | 3:1              | 1011                              | Reserved         |

| 0100                              | 4:1              | 1100                              | 12:1             |

| 0101                              | 5:1              | 1101                              | 20:1             |

| 0110                              | 6:1              | 1110                              | Reserved         |

| 0111                              | Reserved         | 1111                              | Reserved         |

### Table 81. CCB Clock Ratio

- First, the board must have at least 10 × 10-nF SMT ceramic chip capacitors as close as possible to the supply balls of the device. Where the board has blind vias, these capacitors must be placed directly below the chip supply and ground connections. Where the board does not have blind vias, these capacitors must be placed in a ring around the device as close to the supply and ground connections as possible.

- Second, there must be a  $1-\mu F$  ceramic chip capacitor from each SerDes supply (SV<sub>DD</sub> and XV<sub>DD</sub>) to the board ground plane on each side of the device. This must be done for all SerDes supplies.

- Third, between the device and any SerDes voltage regulator there must be a 10- $\mu$ F, low equivalent series resistance (ESR) SMT tantalum chip capacitor and a 100- $\mu$ F, low ESR SMT tantalum chip capacitor. This must be done for all SerDes supplies.

# 22.5 Connection Recommendations

To ensure reliable operation, it is highly recommended to connect unused inputs to an appropriate signal level. All unused active low inputs must be tied to  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$ , as required. All unused active high inputs must be connected to GND. All NC (no-connect) signals must remain unconnected. Power and ground connections must be made to all external  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$ , and GND pins of the device.

# 22.6 Pull-Up and Pull-Down Resistor Requirements

The device requires weak pull-up resistors (2–10 k $\Omega$  is recommended) on open drain type pins including I<sup>2</sup>C pins and PIC (interrupt) pins.

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 63. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions as most have asynchronous behavior and spurious assertion gives unpredictable results.

The following pins must not be pulled down during power-on reset: TSEC3\_TXD[3], HRESET\_REQ, TRIG\_OUT/READY/QUIESCE, MSRCID[2:4], ASLEEP. The DMA\_DACK[0:1], and TEST\_SEL/TEST\_SEL pins must be set to a proper state during POR configuration. See the pinlist table of the individual device for more details

See the PCI 2.2 specification for all pull ups required for PCI.

# 22.7 Output Buffer DC Impedance

The device drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ).

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $OV_{DD}$  or GND. Then, the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 61). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open) and  $R_P$  is trimmed until the voltage at the pad equals  $OV_{DD}/2$ .  $R_P$  then becomes the resistance of the pull-up devices.  $R_P$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_P + R_N)/2$ .

• SD\_REF\_CLK

### NOTE

It is recommended to power down the unused lane through SRDSCR1[0:7] register (offset =  $0xE_0F08$ ) (this prevents the oscillations and holds the receiver output in a fixed state) that maps to SERDES lane 0 to lane 7 accordingly.

Pins V28 and M26 must be tied to  $XV_{DD}$ . Pins V27 and M25 must be tied to GND through a 300- $\Omega$  resistor.

# 22.11 Guideline for PCI Interface Termination

PCI termination if PCI 1 or PCI 2 is not used at all.

Option 1

If PCI arbiter is enabled during POR:

- All AD pins are driven to the stable states after POR. Therefore, all ADs pins can be floating.

- All PCI control pins can be grouped together and tied to  $OV_{DD}$  through a single 10-k $\Omega$  resistor.

- It is optional to disable PCI block through DEVDISR register after POR reset.

### Option 2

If PCI arbiter is disabled during POR:

- All AD pins are in the input state. Therefore, all ADs pins need to be grouped together and tied to  $OV_{DD}$  through a single (or multiple) 10-k $\Omega$  resistor(s).

- All PCI control pins can be grouped together and tied to  $OV_{DD}$  through a single 10-k $\Omega$  resistor.

- It is optional to disable PCI block through DEVDISR register after POR reset.

# 22.12 Guideline for LBIU Termination

If the LBIU parity pins are not used, the following is the termination recommendation:

- For LDP[0:3]—tie them to ground or the power supply rail via a 4.7-k $\Omega$  resistor.

- For LPBSE—tie it to the power supply rail via a 4.7-k $\Omega$  resistor (pull-up resistor).

# 23 Ordering Information

Ordering information for the parts fully covered by this specification document is provided in Section 23.1, "Part Numbers Fully Addressed by this Document."

# 23.1 Part Numbers Fully Addressed by this Document

This table provides the Freescale part numbering nomenclature for the device. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the processor frequency, the part-numbering scheme also includes an application modifier that may specify special application conditions. Each part number also contains a revision code that refers to the die mask revision number.

| MPC             | nnnnn              | t                                       | рр                                                               | ff                                                            | С                                          | r                                                                                                                                                                              |

|-----------------|--------------------|-----------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product<br>Code | Part<br>Identifier | Temperature                             | Package <sup>1, 2, 3</sup>                                       | Processor<br>Frequency <sup>4</sup>                           | Core<br>Frequency                          | Silicon Version                                                                                                                                                                |

| MPC             | 8548E<br>8548      | Blank = 0 to 105°C<br>C = −40° to 105°C | HX = CBGA<br>VU = Pb-free CBGA<br>PX = PBGA<br>VT = Pb-free PBGA | AV = 1500 <sup>3</sup><br>AU = 1333<br>AT = 1200<br>AQ = 1000 | J = 533<br>H = 500 <sup>5</sup><br>G = 400 | Blank = Ver. 2.0<br>(SVR = 0x80390020)<br>A = Ver. 2.1.1<br>B = Ver. 2.1.2<br>C = Ver. 2.1.3<br>(SVR = 0x80390021)<br>D = Ver. 3.1.x<br>(SVR = 0x80390031)<br>Blank = Ver. 2.0 |

|                 |                    |                                         |                                                                  |                                                               |                                            | (SVR = 0x80310020)<br>A = Ver. 2.1.1<br>B = Ver. 2.1.2<br>C = Ver. 2.1.3<br>(SVR = 0x80310021)<br>D = Ver. 3.1.x<br>(SVR = 0x80310031)                                         |

|                 | 8547E              |                                         |                                                                  | AU = 1333<br>AT = 1200<br>AQ = 1000                           | J = 533<br>G = 400                         | Blank = Ver. 2.0 (SVR = 0x80390120) A = Ver. 2.1.1 B = Ver. 2.1.2 C = Ver. 2.1.3 (SVR = 0x80390121) D = Ver. 3.1.x (SVR = 0x80390131)                                          |

|                 | 8547               |                                         |                                                                  |                                                               |                                            | Blank = Ver. 2.0 (SVR = 0x80390120)<br>A = Ver. 2.1.1<br>B = Ver. 2.1.2<br>C = Ver. 2.1.3<br>(SVR = 0x80310121)<br>D = Ver. 3.1.x<br>(SVR = 0x80310131)                        |

### Table 87. Part Numbering Nomenclature

...

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4              | 04/2009 | <ul> <li>In Table 1, "Absolute Maximum Ratings <sup>1</sup>," and in Table 2, "Recommended Operating Conditions," moved text, "MII management voltage" from LV<sub>DD</sub>/TV<sub>DD</sub> to OV<sub>DD</sub>, added "Ethernet management" to OVDD row of input voltage section.</li> <li>In Table 5, "SYSCLK AC Timing Specifications," added notes 7 and 8 to SYSCLK frequency and cycle time.</li> <li>In Table 36, "MII Management DC Electrical Characteristics," changed all instances of LV<sub>DD</sub>/OV<sub>DD</sub> to OV<sub>DD</sub>.</li> <li>Modified Section 16, "High-Speed Serial Interfaces (HSSI)," to reflect that there is only one SerDes.</li> <li>Modified DDR clk rate min from 133 to 166 MHz.</li> <li>Modified note in Table 75, "Processor Core Clocking Specifications (MPC8548E and MPC8547E), "."</li> <li>In Table 56, "Differential Transmitter (TX) Output Specifications," modified equations in Comments column, and changed all instances of "LO" to "L0." Also added note 8.</li> <li>In Table 57, "Differential Receiver (RX) Input Specifications," modified equations in Comments column, and in note 3, changed "TRX-EYE-MEDIAN-to-MAX-JITTER," to "T<sub>RX-EYE-MEDIAN-to-MAX-JITTER</sub>."</li> <li>Modified Table 83, "Frequency Options of SYSCLK with Respect to Memory Bus Speeds."</li> <li>Added a note on Section 4.1, "System Clock Timing," to limit the SYSCLK to 100 MHz if the core frequency is less than 1200 MHz</li> <li>In Table 71, "MPC8543E Pinout ListingTable 72, "MPC8547E Pinout ListingTable 73, "MPC8545E Pinout ListingTable 74, "MPC8543E Pinout Listing," added note 5 to LA[28:31].</li> <li>Added note to Table 83, "Frequency Options of SYSCLK with Respect to Memory Bus Speeds."</li> </ul>                                                                                                 |

| 3              | 01/2009 | <ul> <li>[Section 4.6, "Platform Frequency Requirements for PCI-Express and Serial RapidIO." Changed minimum frequency equation to be 527 MHz for PCI x8.</li> <li>In Table 5, added note 7.</li> <li>Section 4.5, "Platform to FIFO Restrictions." Changed platform clock frequency to 4.2.</li> <li>Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1Gb Mbps)—GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics." Added MII after GMII and add 'or 2.5 V' after 3.3 V.</li> <li>In Table 23, modified table title to include GMII, MII, RMII, and TBI.</li> <li>In Table 24 and Table 25, changed clock period minimum to 5.3.</li> <li>In Table 26, Table 27, Table 28, Table 29, and Table 30, removed subtitle from table title.</li> <li>In Table 30 and Figure 15, changed all instances of PMA to TSEC<i>n</i>.</li> <li>In Table 34, Table 35, Figure 18, and Figure 20, changed all instances of REF_CLK to TSEC<i>n</i>_TX_CLK.</li> <li>In Table 36, changed all instances of OV<sub>DD</sub> to LV<sub>DD</sub>/TV<sub>DD</sub>.</li> <li>In Table 36, changed all instances of OV<sub>DD</sub> to LV<sub>DD</sub>/TV<sub>DD</sub>.</li> <li>In Table 37, "MII Management AC Timing Specifications," changed MDC minimum clock pulse width high from 32 to 48 ns.</li> <li>Added new section, Section 16, "High-Speed Serial Interfaces (HSSI)."</li> <li>Section 16.1, "DC Requirements for PCI Express SD_REF_CLK and SD_REF_CLK." Added new paragraph.</li> <li>Section 17.1, "DC Requirements for Serial RapidIO SD_REF_CLK and SD_REF_CLK." Added new paragraph.</li> <li>Added information to Figure 63, both in figure and in note.</li> <li>Section 22.3, "Decoupling Recommendations." Modified the recommendation.</li> <li>Table 87, "Part Numbering Nomenclature." In Silicon Version column added Ver. 2.1.2.</li> </ul> |

### Table 88. Document Revision History (continued)

| Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|