Welcome to **E-XFL.COM**

### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

## **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                             |

|---------------------------------|-------------------------------------------------------------|

| Product Status                  | Obsolete                                                    |

| Core Processor                  | PowerPC e500                                                |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 1.0GHz                                                      |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                       |

| RAM Controllers                 | DDR, DDR2, SDRAM                                            |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | -                                                           |

| Ethernet                        | 10/100/1000Mbps (4)                                         |

| SATA                            | -                                                           |

| USB                             | -                                                           |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                            |

| Operating Temperature           | 0°C ~ 105°C (TA)                                            |

| Security Features               | Cryptography, Random Number Generator                       |

| Package / Case                  | 783-BBGA, FCBGA                                             |

| Supplier Device Package         | 783-FCBGA (29x29)                                           |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8545epxaqgb |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Performance monitor facility that is similar to, but separate from, the device performance monitor

The e500 defines features that are not implemented on this device. It also generally defines some features that this device implements more specifically. An understanding of these differences can be critical to ensure proper operations.

- 512-Kbyte L2 cache/SRAM

- Flexible configuration.

- Full ECC support on 64-bit boundary in both cache and SRAM modes

- Cache mode supports instruction caching, data caching, or both.

- External masters can force data to be allocated into the cache through programmed memory ranges or special transaction types (stashing).

- 1, 2, or 4 ways can be configured for stashing only.

- Eight-way set-associative cache organization (32-byte cache lines)

- Supports locking entire cache or selected lines. Individual line locks are set and cleared through Book E instructions or by externally mastered transactions.

- Global locking and Flash clearing done through writes to L2 configuration registers

- Instruction and data locks can be Flash cleared separately.

- SRAM features include the following:

- I/O devices access SRAM regions by marking transactions as snoopable (global).

- Regions can reside at any aligned location in the memory map.

- Byte-accessible ECC is protected using read-modify-write transaction accesses for smaller-than-cache-line accesses.

- Address translation and mapping unit (ATMU)

- Eight local access windows define mapping within local 36-bit address space.

- Inbound and outbound ATMUs map to larger external address spaces.

- Three inbound windows plus a configuration window on PCI/PCI-X and PCI Express

- Four inbound windows plus a default window on RapidIO<sup>TM</sup>

- Four outbound windows plus default translation for PCI/PCI-X and PCI Express

- Eight outbound windows plus default translation for RapidIO with segmentation and sub-segmentation support

- DDR/DDR2 memory controller

- Programmable timing supporting DDR and DDR2 SDRAM

- 64-bit data interface

- Four banks of memory supported, each up to 4 Gbytes, to a maximum of 16 Gbytes

- DRAM chip configurations from 64 Mbits to 4 Gbits with  $\times 8/\times 16$  data ports

- Full ECC support

- Page mode support

- Up to 16 simultaneous open pages for DDR

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

#### Overview

- Up to 32 simultaneous open pages for DDR2

- Contiguous or discontiguous memory mapping

- Read-modify-write support for RapidIO atomic increment, decrement, set, and clear transactions

- Sleep mode support for self-refresh SDRAM

- On-die termination support when using DDR2

- Supports auto refreshing

- On-the-fly power management using CKE signal

- Registered DIMM support

- Fast memory access via JTAG port

- 2.5-V SSTL\_2 compatible I/O (1.8-V SSTL\_1.8 for DDR2)

- Support for battery-backed main memory

- Programmable interrupt controller (PIC)

- Programming model is compliant with the OpenPIC architecture.

- Supports 16 programmable interrupt and processor task priority levels

- Supports 12 discrete external interrupts

- Supports 4 message interrupts with 32-bit messages

- Supports connection of an external interrupt controller such as the 8259 programmable interrupt controller

- Four global high-resolution timers/counters that can generate interrupts

- Supports a variety of other internal interrupt sources

- Supports fully nested interrupt delivery

- Interrupts can be routed to external pin for external processing.

- Interrupts can be routed to the e500 core's standard or critical interrupt inputs.

- Interrupt summary registers allow fast identification of interrupt source.

- Integrated security engine (SEC) optimized to process all the algorithms associated with IPSec, IKE, WTLS/WAP, SSL/TLS, and 3GPP

- Four crypto-channels, each supporting multi-command descriptor chains

- Dynamic assignment of crypto-execution units via an integrated controller

- Buffer size of 256 bytes for each execution unit, with flow control for large data sizes

- PKEU—public key execution unit

- RSA and Diffie-Hellman; programmable field size up to 2048 bits

- Elliptic curve cryptography with F<sub>2</sub>m and F(p) modes and programmable field size up to 511 bits

- DEU—Data Encryption Standard execution unit

- DES, 3DES

- Two key (K1, K2) or three key (K1, K2, K3)

- ECB and CBC modes for both DES and 3DES

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

- AESU—Advanced Encryption Standard unit

- Implements the Rijndael symmetric key cipher

- ECB, CBC, CTR, and CCM modes

- 128-, 192-, and 256-bit key lengths

- AFEU—ARC four execution unit

- Implements a stream cipher compatible with the RC4 algorithm

- 40- to 128-bit programmable key

- MDEU—message digest execution unit

- SHA with 160- or 256-bit message digest

- MD5 with 128-bit message digest

- HMAC with either algorithm

- KEU—Kasumi execution unit

- Implements F8 algorithm for encryption and F9 algorithm for integrity checking

- Also supports A5/3 and GEA-3 algorithms

- RNG—random number generator

- XOR engine for parity checking in RAID storage applications

- Dual I<sup>2</sup>C controllers

- Two-wire interface

- Multiple master support

- Master or slave I<sup>2</sup>C mode support

- On-chip digital filtering rejects spikes on the bus

- Boot sequencer

- Optionally loads configuration data from serial ROM at reset via the I<sup>2</sup>C interface

- Can be used to initialize configuration registers and/or memory

- Supports extended I<sup>2</sup>C addressing mode

- Data integrity checked with preamble signature and CRC

- DUART

- Two 4-wire interfaces (SIN, SOUT, RTS, CTS)

- Programming model compatible with the original 16450 UART and the PC16550D

- Local bus controller (LBC)

- Multiplexed 32-bit address and data bus operating at up to 133 MHz

- Eight chip selects support eight external slaves

- Up to eight-beat burst transfers

- The 32-, 16-, and 8-bit port sizes are controlled by an on-chip memory controller.

- Three protocol engines available on a per chip select basis:

- General-purpose chip select machine (GPCM)

- Three user programmable machines (UPMs)

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

#### Overview

- Dedicated single data rate SDRAM controller

- Parity support

- Default boot ROM chip select with configurable bus width (8, 16, or 32 bits)

- Four enhanced three-speed Ethernet controllers (eTSECs)

- Three-speed support (10/100/1000 Mbps)

- Four controllers designed to comply with IEEE Std. 802.3®, 802.3u, 802.3x, 802.3z, 802.3ac, and 802.3ab

- Support for various Ethernet physical interfaces:

- 1000 Mbps full-duplex IEEE 802.3 GMII, IEEE 802.3z TBI, RTBI, and RGMII

- 10/100 Mbps full and half-duplex IEEE 802.3 MII, IEEE 802.3 RGMII, and RMII

- Flexible configuration for multiple PHY interface configurations. See Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC)

(10/100/1Gb Mbps)—GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics," for more information.

- TCP/IP acceleration and QoS features available

- IP v4 and IP v6 header recognition on receive

- IP v4 header checksum verification and generation

- TCP and UDP checksum verification and generation

- Per-packet configurable acceleration

- Recognition of VLAN, stacked (queue in queue) VLAN, IEEE Std 802.2™, PPPoE session, MPLS stacks, and ESP/AH IP-security headers

- Supported in all FIFO modes

- Quality of service support:

- Transmission from up to eight physical queues

- Reception to up to eight physical queues

- Full- and half-duplex Ethernet support (1000 Mbps supports only full duplex):

- IEEE 802.3 full-duplex flow control (automatic PAUSE frame generation or software-programmed PAUSE frame generation and recognition)

- Programmable maximum frame length supports jumbo frames (up to 9.6 Kbytes) and IEEE Std. 802.1<sup>TM</sup> virtual local area network (VLAN) tags and priority

- VLAN insertion and deletion

- Per-frame VLAN control word or default VLAN for each eTSEC

- Extracted VLAN control word passed to software separately

- Retransmission following a collision

- CRC generation and verification of inbound/outbound frames

- Programmable Ethernet preamble insertion and extraction of up to 7 bytes

- MAC address recognition:

- Exact match on primary and virtual 48-bit unicast addresses

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

Input Clocks

#### 4 Input Clocks

This section discusses the timing for the input clocks.

#### 4.1 System Clock Timing

The following table provides the system clock (SYSCLK) AC timing specifications for the device.

### Table 5. SYSCLK AC Timing Specifications

At recommended operating conditions (see Table 2) with  $OV_{DD} = 3.3 \text{ V} \pm 165 \text{ mV}$ .

| Parameter/Condition       | Symbol                                | Min | Тур | Max  | Unit | Notes      |

|---------------------------|---------------------------------------|-----|-----|------|------|------------|

| SYSCLK frequency          | f <sub>SYSCLK</sub>                   | 16  | _   | 133  | MHz  | 1, 6, 7, 8 |

| SYSCLK cycle time         | t <sub>SYSCLK</sub>                   | 7.5 | _   | 60   | ns   | 6, 7, 8    |

| SYSCLK rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>     | 0.6 | 1.0 | 1.2  | ns   | 2          |

| SYSCLK duty cycle         | t <sub>KHK</sub> /t <sub>SYSCLK</sub> | 40  | _   | 60   | %    | 3          |

| SYSCLK jitter             | _                                     | _   | _   | ±150 | ps   | 4, 5       |

#### Notes:

- 1. Caution: The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

- 2. Rise and fall times for SYSCLK are measured at 0.6 and 2.7 V.

- 3. Timing is guaranteed by design and characterization.

- 4. This represents the total input jitter—short term and long term—and is guaranteed by design.

- 5. The SYSCLK driver's closed loop jitter bandwidth must be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track SYSCLK drivers with the specified jitter.

- 6. This parameter has been adjusted slower according to the workaround for device erratum GEN 13.

- 7. For spread spectrum clocking, Guidelines are + 0% to -1% down spread at modulation rate between 20 and 60 kHz on SYSCLK.

- 8. System with operating core frequency less than 1200 MHz must limit SYSCLK frequency to 100 MHz maximum.

#### 4.2 **Real Time Clock Timing**

The RTC input is sampled by the platform clock (CCB clock). The output of the sampling latch is then used as an input to the counters of the PIC and the TimeBase unit of the e500. There is no jitter specification. The minimum pulse width of the RTC signal must be greater than 2x the period of the CCB clock. That is, minimum clock high time is  $2 \times t_{CCB}$ , and minimum clock low time is  $2 \times t_{CCB}$ . There is no minimum RTC frequency; RTC may be grounded if not needed.

# 4.3 eTSEC Gigabit Reference Clock Timing

GMII. TBI

The following table provides the eTSEC gigabit reference clocks (EC\_GTX\_CLK125) AC timing specifications for the device.

Parameter/Condition **Symbol** Min Max Unit **Notes** Typ EC\_GTX\_CLK125 frequency 125 MHz f<sub>G125</sub> EC\_GTX\_CLK125 cycle time 8 ns t<sub>G125</sub> EC\_GTX\_CLK125 rise and fall time 1 ns t<sub>G125R</sub>, t<sub>G125F</sub> 0.75 L/TVDD = 2.5 V1.0 L/TVDD = 3.3 V% EC\_GTX\_CLK125 duty cycle 2, 3 t<sub>G125H</sub>/t<sub>G125</sub>

45

47

55

53

Table 6. EC\_GTX\_CLK125 AC Timing Specifications

### Notes:

- 1. Rise and fall times for EC\_GTX\_CLK125 are measured from 0.5 and 2.0 V for L/TV<sub>DD</sub> = 2.5 V, and from 0.6 and 2.7 V for L/TV<sub>DD</sub> = 3.3 V.

- 2. Timing is guaranteed by design and characterization.

1000Base-T for RGMII, RTBI

3. EC\_GTX\_CLK125 is used to generate the GTX clock TSEC\_n\_GTX\_CLK for the eTSEC transmitter with 2% degradation. EC\_GTX\_CLK125 duty cycle can be loosened from 47/53% as long as the PHY device can tolerate the duty cycle generated by the TSEC\_n\_GTX\_CLK. See Section 8.2.6, "RGMII and RTBI AC Timing Specifications," for duty cycle for 10Base-T and 100Base-T reference clock.

# 4.4 PCI/PCI-X Reference Clock Timing

When the PCI/PCI-X controller is configured for asynchronous operation, the reference clock for the PCI/PCI-x controller is not the SYSCLK input, but instead the PCIn\_CLK. The following table provides the PCI/PCI-X reference clock AC timing specifications for the device.

Table 7. PCIn\_CLK AC Timing Specifications

At recommended operating conditions (see Table 2) with  $OV_{DD} = 3.3 \text{ V} \pm 165 \text{ mV}$ .

| Parameter/Condition         | Symbol                                    | Min | Тур | Max | Unit | Notes |

|-----------------------------|-------------------------------------------|-----|-----|-----|------|-------|

| PCIn_CLK frequency          | f <sub>PCICLK</sub>                       | 16  | _   | 133 | MHz  | _     |

| PCIn_CLK cycle time         | t <sub>PCICLK</sub>                       | 7.5 | _   | 60  | ns   | _     |

| PCIn_CLK rise and fall time | t <sub>PCIKH</sub> , t <sub>PCIKL</sub>   | 0.6 | 1.0 | 2.1 | ns   | 1, 2  |

| PCIn_CLK duty cycle         | t <sub>PCIKHKL</sub> /t <sub>PCICLK</sub> | 40  | _   | 60  | %    | 2     |

#### Notes:

- 1. Rise and fall times for SYSCLK are measured at 0.6 and 2.7 V.

- 2. Timing is guaranteed by design and characterization.

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

### **Enhanced Three-Speed Ethernet (eTSEC)**

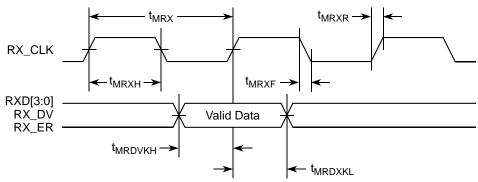

Figure 13 shows the MII receive AC timing diagram.

Figure 13. MII Receive AC Timing Diagram

## 8.2.4 TBI AC Timing Specifications

This section describes the TBI transmit and receive AC timing specifications.

## 8.2.4.1 TBI Transmit AC Timing Specifications

This table provides the TBI transmit AC timing specifications.

| Parameter/Condition                        | Symbol <sup>1</sup>            | Min | Тур | Max | Unit |

|--------------------------------------------|--------------------------------|-----|-----|-----|------|

| TCG[9:0] setup time GTX_CLK going high     | t <sub>TTKHDV</sub>            | 2.0 | _   | _   | ns   |

| TCG[9:0] hold time from GTX_CLK going high | t <sub>TTKHDX</sub>            | 1.0 | _   | _   | ns   |

| GTX_CLK rise (20%-80%)                     | t <sub>TTXR</sub> <sup>2</sup> | _   | _   | 1.0 | ns   |

| GTX_CLK fall time (80%–20%)                | t <sub>TTXF</sub> <sup>2</sup> | _   | _   | 1.0 | ns   |

**Table 30. TBI Transmit AC Timing Specifications**

#### Notes:

34

- 1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>TTKHDV</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the valid state (V) or setup time. Also, t<sub>TTKHDX</sub> symbolizes the TBI transmit timing (TT) with respect to the time from t<sub>TTX</sub> (K) going high (H) until the referenced data signals (D) reach the invalid state (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>TTX</sub> represents the TBI (T) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 2. Guaranteed by design.

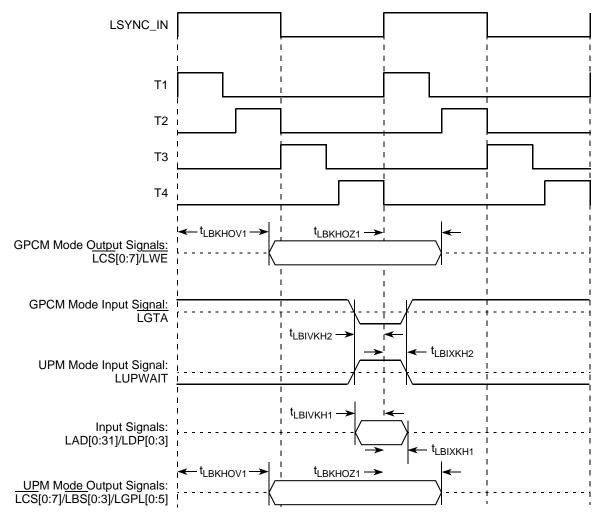

Table 41 describes the timing parameters of the local bus interface at  $BV_{DD} = 2.5 \text{ V}$ .

Table 41. Local Bus Timing Parameters (BV<sub>DD</sub> = 2.5 V)—PLL Enabled

| Parameter                                                              | Symbol <sup>1</sup>                 | Min | Max | Unit | Notes |

|------------------------------------------------------------------------|-------------------------------------|-----|-----|------|-------|

| Local bus cycle time                                                   | t <sub>LBK</sub>                    | 7.5 | 12  | ns   | 2     |

| Local bus duty cycle                                                   | t <sub>LBKH</sub> /t <sub>LBK</sub> | 43  | 57  | %    | _     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                   | t <sub>LBKSKEW</sub>                | _   | 150 | ps   | 7, 8  |

| Input setup to local bus clock (except LGTA/UPWAIT)                    | t <sub>LBIVKH1</sub>                | 1.9 | _   | ns   | 3, 4  |

| LGTA/LUPWAIT input setup to local bus clock                            | t <sub>LBIVKH2</sub>                | 1.8 | _   | ns   | 3, 4  |

| Input hold from local bus clock (except \( \overline{LGTA} \) LUPWAIT) | t <sub>LBIXKH1</sub>                | 1.1 | _   | ns   | 3, 4  |

| LGTA/LUPWAIT input hold from local bus clock                           | t <sub>LBIXKH2</sub>                | 1.1 | _   | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH hold time)  | t <sub>LBOTOT</sub>                 | 1.5 | _   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)              | t <sub>LBKHOV1</sub>                | _   | 2.1 | ns   | _     |

| Local bus clock to data valid for LAD/LDP                              | t <sub>LBKHOV2</sub>                | _   | 2.3 | ns   | 3     |

| Local bus clock to address valid for LAD                               | t <sub>LBKHOV3</sub>                | _   | 2.4 | ns   | 3     |

| Local bus clock to LALE assertion                                      | t <sub>LBKHOV4</sub>                | _   | 2.4 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)             | t <sub>LBKHOX1</sub>                | 0.8 | _   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                           | t <sub>LBKHOX2</sub>                | 0.8 | _   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)     | t <sub>LBKHOZ1</sub>                | _   | 2.6 | ns   | 5     |

| Local bus clock to output high impedance for LAD/LDP                   | t <sub>LBKHOZ2</sub>                | _   | 2.6 | ns   | 5     |

#### Notes:

- 1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)</sub>(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

- 2. All timings are in reference to LSYNC IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 3.3-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 8. Guaranteed by design.

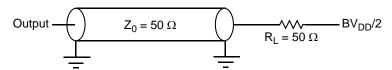

Figure 22 provides the AC test load for the local bus.

Figure 22. Local Bus AC Test Load

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

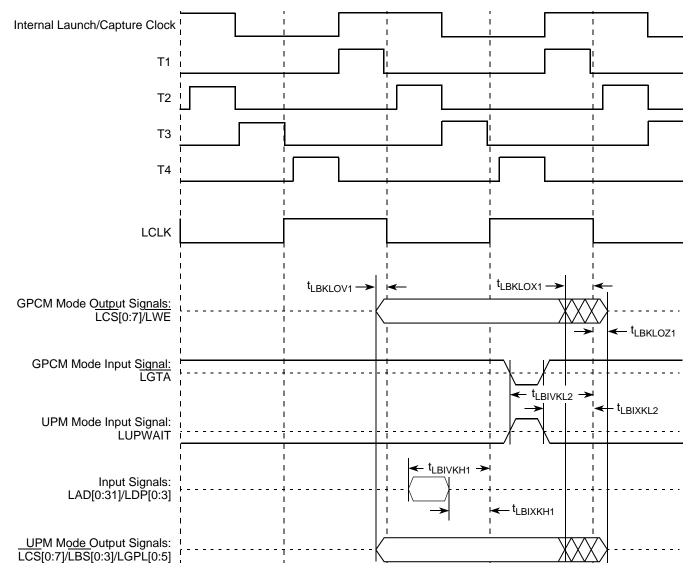

Figure 27. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 8 or 16 (PLL Enabled)

### **Local Bus**

Figure 28. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 8 or 16 (PLL Bypass Mode)

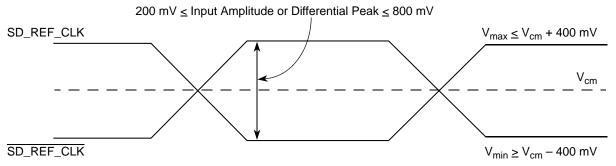

Figure 41. Differential Reference Clock Input DC Requirements (External AC-Coupled)

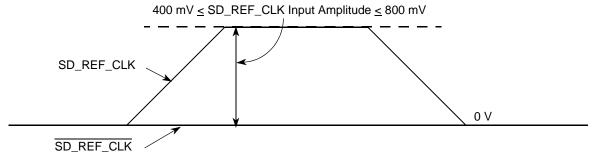

Figure 42. Single-Ended Reference Clock Input DC Requirements

## 16.2.3 Interfacing with Other Differential Signaling Levels

- With on-chip termination to SGND\_SRDSn (xcorevss), the differential reference clocks inputs are HCSL (high-speed current steering logic) compatible DC-coupled.

- Many other low voltage differential type outputs like LVDS (low voltage differential signaling) can

be used but may need to be AC-coupled due to the limited common mode input range allowed (100

to 400 mV) for DC-coupled connection.

- LVPECL outputs can produce signal with too large amplitude and may need to be DC-biased at clock driver output first, then followed with series attenuation resistor to reduce the amplitude, in addition to AC-coupling.

### NOTE

Figure 43 through Figure 46 below are for conceptual reference only. Due to the fact that clock driver chip's internal structure, output impedance, and termination requirements are different between various clock driver chip manufacturers, it is very possible that the clock circuit reference designs provided by clock driver chip vendor are different from what is shown below. They might also vary from one vendor to the other. Therefore, Freescale Semiconductor can neither provide the optimal clock driver reference circuits, nor guarantee the correctness of the following clock driver connection reference circuits. The system designer is recommended to contact the selected clock driver chip vendor for the optimal reference circuits with the SerDes reference clock receiver requirement provided in this document.

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

## Serial RapidIO

Table 60. Short Run Transmitter AC Timing Specifications—2.5 GBaud

| Characteristic              | Symbol              | Range |      | Unit   | Notes                                                                      |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------|

| Cital actel istic           | Symbol              | Min   | Max  | Onit   | Notes                                                                      |

| Output voltage              | Vo                  | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal comprising a differential pair |

| Differential output voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mV p-p | _                                                                          |

| Deterministic jitter        | J <sub>D</sub>      | _     | 0.17 | UI p-p | _                                                                          |

| Total jitter                | J <sub>T</sub>      | _     | 0.35 | UI p-p | _                                                                          |

| Multiple output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |

| Unit interval               | UI                  | 400   | 400  | ps     | ±100 ppm                                                                   |

Table 61. Short Run Transmitter AC Timing Specifications—3.125 GBaud

| Characteristic              | Symbol              | Range |      | Unit   | Notes                                                                      |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Unit   | Notes                                                                      |

| Output voltage              | Vo                  | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal comprising a differential pair |

| Differential output voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mVp-p  | _                                                                          |

| Deterministic jitter        | J <sub>D</sub>      | _     | 0.17 | UI p-p | _                                                                          |

| Total jitter                | J <sub>T</sub>      | _     | 0.35 | UI p-p | _                                                                          |

| Multiple output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |

| Unit interval               | UI                  | 320   | 320  | ps     | ±100 ppm                                                                   |

Table 62. Long Run Transmitter AC Timing Specifications—1.25 GBaud

| Characteristic              | Symbol              | Range |      | Unit   | Notes                                                                      |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------|

| Citaracteristic             | Symbol              | Min   | Max  | Oilit  | Notes                                                                      |

| Output voltage              | V <sub>O</sub>      | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal comprising a differential pair |

| Differential output voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mVp-p  | _                                                                          |

| Deterministic jitter        | $J_D$               | _     | 0.17 | UI p-p | _                                                                          |

| Total jitter                | J <sub>T</sub>      | _     | 0.35 | UI p-p | _                                                                          |

| Multiple output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |

| Unit interval               | UI                  | 800   | 800  | ps     | ±100 ppm                                                                   |

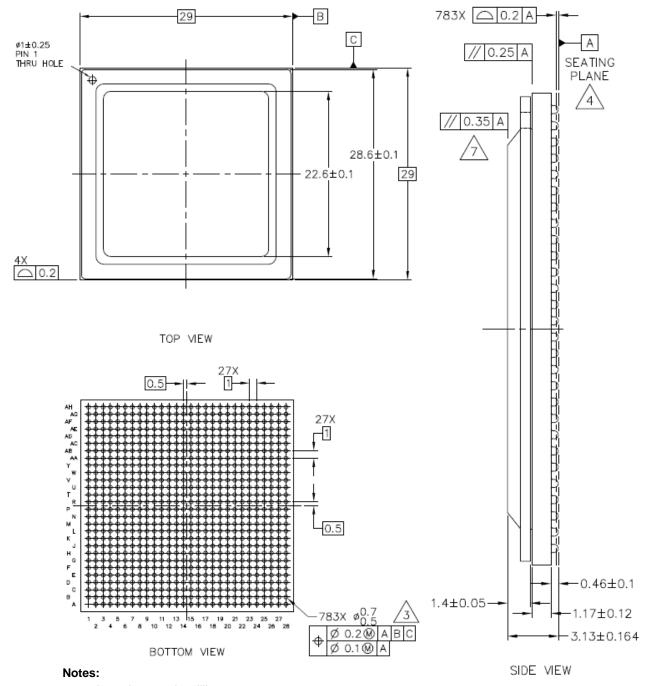

- 1. All dimensions are in millimeters.

- 2. Dimensioning and tolerancing per ASME Y14.5M-1994.

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

- 5. Capacitors may not be present on all devices.

- 6. Caution must be taken not to short capacitors or exposed metal capacitor pads on package top.

- 7. Parallelism measurement shall exclude any effect of mark on top surface of package.

- 8. All dimensions are symmetric across the package center lines unless dimensioned otherwise.

Figure 56. Mechanical Dimensions and Bottom Surface Nomenclature of the FC-PBGA with Stamped Lid

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

Table 71. MPC8548E Pinout Listing (continued)

| Signal             | Package Pin Number                               | Pin Type | Power<br>Supply  | Notes        |

|--------------------|--------------------------------------------------|----------|------------------|--------------|

| LSYNC_IN           | F27                                              | l        | BV <sub>DD</sub> | _            |

| LSYNC_OUT          | F28                                              | 0        | BV <sub>DD</sub> | _            |

|                    | DMA                                              |          |                  |              |

| DMA_DACK[0:1]      | AD3, AE1                                         | 0        | OV <sub>DD</sub> | 5, 9,<br>102 |

| DMA_DREQ[0:1]      | AD4, AE2                                         | I        | OV <sub>DD</sub> | _            |

| DMA_DDONE[0:1]     | AD2, AD1                                         | 0        | OV <sub>DD</sub> | _            |

|                    | Programmable Interrupt Controller                |          |                  |              |

| UDE                | AH16                                             | ļ        | OV <sub>DD</sub> | _            |

| MCP                | AG19                                             | I        | OV <sub>DD</sub> | _            |

| IRQ[0:7]           | AG23, AF18, AE18, AF20, AG18, AF17, AH24, AE20   | I        | OV <sub>DD</sub> | _            |

| IRQ[8]             | AF19                                             | ļ        | OV <sub>DD</sub> | _            |

| IRQ[9]/DMA_DREQ3   | AF21                                             | I        | OV <sub>DD</sub> | 1            |

| IRQ[10]/DMA_DACK3  | AE19                                             | I/O      | OV <sub>DD</sub> | 1            |

| IRQ[11]/DMA_DDONE3 | AD20                                             | I/O      | OV <sub>DD</sub> | 1            |

| ĪRQ_OUT            | AD18                                             | 0        | OV <sub>DD</sub> | 2, 4         |

|                    | Ethernet Management Interface                    |          |                  |              |

| EC_MDC             | AB9                                              | 0        | OV <sub>DD</sub> | 5, 9         |

| EC_MDIO            | AC8                                              | I/O      | OV <sub>DD</sub> | _            |

|                    | Gigabit Reference Clock                          |          |                  |              |

| EC_GTX_CLK125      | V11                                              | I        | LV <sub>DD</sub> | _            |

|                    | Three-Speed Ethernet Controller (Gigabit Etherne | et 1)    |                  | 1            |

| TSEC1_RXD[7:0]     | R5, U1, R3, U2, V3, V1, T3, T2                   | ļ        | LV <sub>DD</sub> | _            |

| TSEC1_TXD[7:0]     | T10, V7, U10, U5, U4, V6, T5, T8                 | 0        | LV <sub>DD</sub> | 5, 9         |

| TSEC1_COL          | R4                                               | ļ        | LV <sub>DD</sub> | _            |

| TSEC1_CRS          | V5                                               | I/O      | LV <sub>DD</sub> | 20           |

| TSEC1_GTX_CLK      | U7                                               | 0        | LV <sub>DD</sub> | _            |

| TSEC1_RX_CLK       | U3                                               | I        | LV <sub>DD</sub> | _            |

| TSEC1_RX_DV        | V2                                               | I        | LV <sub>DD</sub> | _            |

| TSEC1_RX_ER        | T1                                               | I        | LV <sub>DD</sub> | _            |

| TSEC1_TX_CLK       | Т6                                               | I        | LV <sub>DD</sub> | _            |

| TSEC1_TX_EN        | U9                                               | 0        | LV <sub>DD</sub> | 30           |

| TSEC1_TX_ER        | T7                                               | 0        | LV <sub>DD</sub> | _            |

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

Table 71. MPC8548E Pinout Listing (continued)

| Signal           | Signal Package Pin Number                                                                                                                                |                                                                   |                  |    |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------|----|

| LV <sub>DD</sub> | N8, R7, T9, U6                                                                                                                                           | Power for<br>TSEC1 and<br>TSEC2<br>(2.5 V, 3.3 V)                 | LV <sub>DD</sub> | _  |

| TV <sub>DD</sub> | W9, Y6                                                                                                                                                   | Power for<br>TSEC3 and<br>TSEC4<br>(2,5 V, 3.3 V)                 | TV <sub>DD</sub> | _  |

| GV <sub>DD</sub> | B3, B11, C7, C9, C14, C17, D4, D6, D10, D15, E2, E8, E11, E18, F5, F12, F16, G3, G7, G9, G11, H5, H12, H15, H17, J10, K3, K12, K16, K18, L6, M4, M8, M13 | Power for<br>DDR1 and<br>DDR2 DRAM<br>I/O voltage<br>(1.8 V, 2.5) | GV <sub>DD</sub> | -  |

| BV <sub>DD</sub> | C21, C24, C27, E20, E25, G19, G23, H26, J20                                                                                                              | Power for local<br>bus (1.8 V,<br>2.5 V, 3.3 V)                   | BV <sub>DD</sub> |    |

| V <sub>DD</sub>  | M19, N12, N14, N16, N18, P11, P13, P15, P17, P19, R12, R14, R16, R18, T11, T13, T15, T17, T19, U12, U14, U16, U18, V17, V19                              | Power for core<br>(1.1 V)                                         | V <sub>DD</sub>  | _  |

| SV <sub>DD</sub> | L25, L27, M24, N28, P24, P26, R24, R27, T25, V24, V26, W24, W27, Y25, AA28, AC27                                                                         | Core Power<br>for SerDes<br>transceivers<br>(1.1 V)               | SV <sub>DD</sub> |    |

| XV <sub>DD</sub> | L20, L22, N23, P21, R22, T20, U23, V21, W22,<br>Y20                                                                                                      | Pad Power for<br>SerDes<br>transceivers<br>(1.1 V)                | XV <sub>DD</sub> | _  |

| AVDD_LBIU        | J28                                                                                                                                                      | Power for local<br>bus PLL<br>(1.1 V)                             | _                | 26 |

| AVDD_PCI1        | AH21                                                                                                                                                     | Power for<br>PCI1 PLL<br>(1.1 V)                                  | _                | 26 |

| AVDD_PCI2        | AH22                                                                                                                                                     | Power for<br>PCI2 PLL<br>(1.1 V)                                  | _                | 26 |

| AVDD_CORE        | AH15                                                                                                                                                     | Power for<br>e500 PLL (1.1<br>V)                                  | _                | 26 |

| AVDD_PLAT        | AH19                                                                                                                                                     | Powerfor CCB<br>PLL (1.1 V)                                       | _                | 26 |

| AVDD_SRDS        | U25                                                                                                                                                      | Power for<br>SRDSPLL<br>(1.1 V)                                   | _                | 26 |

| SENSEVDD         | M14                                                                                                                                                      | 0                                                                 | $V_{DD}$         | 13 |

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

Table 72. MPC8547E Pinout Listing (continued)

| Signal     | Package Pin Number | Pin Type | Power<br>Supply | Notes |

|------------|--------------------|----------|-----------------|-------|

| SD_PLL_TPA | U26                | 0        | _               | 24    |

**Note:** All note references in this table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

Table 73 provides the pin-out listing for the MPC8545E 783 FC-PBGA package.

## **NOTE**

All note references in the following table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

Table 73. MPC8545E Pinout Listing

| Signal                        | Package Pin Number                                                                                                                                                                            | Pin Type         | Power<br>Supply  | Notes    |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|----------|

|                               | PCI1 and PCI2 (One 64-Bit or Two 32-Bit)                                                                                                                                                      |                  | I.               | ·        |

| PCI1_AD[63:32]/PCI2_AD[31:0]  | I/O                                                                                                                                                                                           | OV <sub>DD</sub> | 17               |          |

| PCI1_AD[31:0]                 | AH6, AE7, AF7, AG7, AH7, AF8, AH8, AE9,<br>AH9, AC10, AB10, AD10, AG10, AA10, AH10,<br>AA11, AB12, AE12, AG12, AH12, AB13, AA12,<br>AC13, AE13, Y14, W13, AG13, V14, AH13,<br>AC14, Y15, AB15 | I/O              | OV <sub>DD</sub> | 17       |

| PCI1_C_BE[7:4]/PCI2_C_BE[3:0] | AF15, AD14, AE15, AD15                                                                                                                                                                        | I/O              | OV <sub>DD</sub> | 17       |

| PCI1_C_BE[3:0]                | AF9, AD11, Y12, Y13                                                                                                                                                                           | I/O              | OV <sub>DD</sub> | 17       |

| PCI1_PAR64/PCI2_PAR           | W15                                                                                                                                                                                           | I/O              | OV <sub>DD</sub> | _        |

| PCI1_GNT[4:1]                 | AG6, AE6, AF5, AH5                                                                                                                                                                            | 0                | OV <sub>DD</sub> | 5, 9, 35 |

| PCI1_GNT0                     | AG5                                                                                                                                                                                           | I/O              | OV <sub>DD</sub> | _        |

| PCI1_IRDY                     | AF11                                                                                                                                                                                          | I/O              | OV <sub>DD</sub> | 2        |

| PCI1_PAR                      | AD12                                                                                                                                                                                          | I/O              | OV <sub>DD</sub> | _        |

| PCI1_PERR                     | AC12                                                                                                                                                                                          | I/O              | OV <sub>DD</sub> | 2        |

| PCI1_SERR                     | V13                                                                                                                                                                                           | I/O              | OV <sub>DD</sub> | 2, 4     |

| PCI1_STOP                     | W12                                                                                                                                                                                           | I/O              | OV <sub>DD</sub> | 2        |

| PCI1_TRDY                     | AG11                                                                                                                                                                                          | I/O              | OV <sub>DD</sub> | 2        |

| PCI1_REQ[4:1]                 | AH2, AG4, AG3, AH4                                                                                                                                                                            | 1                | OV <sub>DD</sub> | _        |

| PCI1_REQ0                     | AH3                                                                                                                                                                                           | I/O              | OV <sub>DD</sub> | _        |

| PCI1_CLK                      | AH26                                                                                                                                                                                          | 1                | OV <sub>DD</sub> | 39       |

| PCI1_DEVSEL                   | AH11                                                                                                                                                                                          | I/O              | OV <sub>DD</sub> | 2        |

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

Table 73. MPC8545E Pinout Listing (continued)

| Signal                 | Package Pin Number                                                                                                                                                                                                                                                                             | Pin Type | Power<br>Supply  | Notes    |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

| PCI1_FRAME             | AE11                                                                                                                                                                                                                                                                                           | I/O      | $OV_{DD}$        | 2        |

| PCI1_IDSEL             | AG9                                                                                                                                                                                                                                                                                            | I        | $OV_{DD}$        | _        |

| PCI1_REQ64/PCI2_FRAME  | AF14                                                                                                                                                                                                                                                                                           | I/O      | $OV_{DD}$        | 2, 5, 10 |

| PCI1_ACK64/PCI2_DEVSEL | V15                                                                                                                                                                                                                                                                                            | I/O      | $OV_{DD}$        | 2        |

| PCI2_CLK               | AE28                                                                                                                                                                                                                                                                                           | I        | $OV_{DD}$        | 39       |

| PCI2_IRDY              | AD26                                                                                                                                                                                                                                                                                           | I/O      | $OV_{DD}$        | 2        |

| PCI2_PERR              | AD25                                                                                                                                                                                                                                                                                           | I/O      | $OV_{DD}$        | 2        |

| PCI2_GNT[4:1]          | AE26, AG24, AF25, AE25                                                                                                                                                                                                                                                                         | 0        | $OV_{DD}$        | 5, 9, 35 |

| PCI2_GNT0              | AG25                                                                                                                                                                                                                                                                                           | I/O      | $OV_{DD}$        | _        |

| PCI2_SERR              | AD24                                                                                                                                                                                                                                                                                           | I/O      | $OV_{DD}$        | 2,4      |

| PCI2_STOP              | AF24                                                                                                                                                                                                                                                                                           | I/O      | $OV_{DD}$        | 2        |

| PCI2_TRDY              | AD27                                                                                                                                                                                                                                                                                           | I/O      | $OV_{DD}$        | 2        |

| PCI2_REQ[4:1]          | AD28, AE27, W17, AF26                                                                                                                                                                                                                                                                          | I        | OV <sub>DD</sub> | _        |

| PCI2_REQ0              | AH25                                                                                                                                                                                                                                                                                           | I/O      | $OV_{DD}$        | _        |

|                        | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                     |          |                  |          |

| MDQ[0:63]              | L18, J18, K14, L13, L19, M18, L15, L14, A17, B17, A13, B12, C18, B18, B13, A12, H18, F18, J14, F15, K19, J19, H16, K15, D17, G16, K13, D14, D18, F17, F14, E14, A7, A6, D5, A4, C8, D7, B5, B4, A2, B1, D1, E4, A3, B2, D2, E3, F3, G4, J5, K5, F6, G5, J6, K4, J1, K2, M5, M3, J3, J2, L1, M6 | I/O      | GV <sub>DD</sub> | _        |

| MECC[0:7]              | H13, F13, F11, C11, J13, G13, D12, M12                                                                                                                                                                                                                                                         | I/O      | GV <sub>DD</sub> | _        |

| MDM[0:8]               | M17, C16, K17, E16, B6, C4, H4, K1, E13                                                                                                                                                                                                                                                        | 0        | GV <sub>DD</sub> | _        |

| MDQS[0:8]              | M15, A16, G17, G14, A5, D3, H1, L2, C13                                                                                                                                                                                                                                                        | I/O      | GV <sub>DD</sub> | _        |

| MDQS[0:8]              | L17, B16, J16, H14, C6, C2, H3, L4, D13                                                                                                                                                                                                                                                        | I/O      | GV <sub>DD</sub> | _        |

| MA[0:15]               | A8, F9, D9, B9, A9, L10, M10, H10, K10, G10,<br>B8, E10, B10, G6, A10, L11                                                                                                                                                                                                                     | 0        | GV <sub>DD</sub> | _        |

| MBA[0:2]               | F7, J7, M11                                                                                                                                                                                                                                                                                    | 0        | GV <sub>DD</sub> | _        |

| MWE                    | E7                                                                                                                                                                                                                                                                                             | 0        | GV <sub>DD</sub> | _        |

| MCAS                   | H7                                                                                                                                                                                                                                                                                             | 0        | GV <sub>DD</sub> | <u> </u> |

| MRAS                   | L8                                                                                                                                                                                                                                                                                             | 0        | GV <sub>DD</sub> | <u> </u> |

| MCKE[0:3]              | F10, C10, J11, H11                                                                                                                                                                                                                                                                             | 0        | $GV_DD$          | 11       |

| MCS[0:3]               | K8, J8, G8, F8                                                                                                                                                                                                                                                                                 | 0        | GV <sub>DD</sub> | T -      |

| MCK[0:5]               | H9, B15, G2, M9, A14, F1                                                                                                                                                                                                                                                                       | 0        | GV <sub>DD</sub> | T -      |

| MCK[0:5]               | J9, A15, G1, L9, B14, F2                                                                                                                                                                                                                                                                       | 0        | GV <sub>DD</sub> | T -      |

| MODT[0:3]              | E6, K6, L7, M7                                                                                                                                                                                                                                                                                 | 0        | GV <sub>DD</sub> | _        |

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

133

## 20.3 e500 Core PLL Ratio

This table describes the clock ratio between the e500 core complex bus (CCB) and the e500 core clock. This ratio is determined by the binary value of LBCTL, LALE, and LGPL2 at power up, as shown in this table.

**Binary Value of Binary Value of** LBCTL, LALE, LGPL2 e500 core:CCB Clock Ratio LBCTL, LALE, LGPL2 e500 core:CCB Clock Ratio **Signals Signals** 000 4:1 100 2:1 001 9:2 101 5:2 010 110 3:1 Reserved 011 7:2 3:2 111

Table 82. e500 Core to CCB Clock Ratio

# 20.4 Frequency Options

Table 83This table shows the expected frequency values for the platform frequency when using a CCB clock to SYSCLK ratio in comparison to the memory bus clock speed.

CCB to SYSCLK (MHz) **SYSCLK Ratio** 16.66 25 33.33 41.66 66.66 100 133.33 83 111 Platform/CCB Frequency (MHz) 2 3 333 400 4 333 400 445 533 5 333 415 500 6 500 400 8 333 533 9 375 10 333 417 12 400 500 16 400 533 333 20 500

Table 83. Frequency Options of SYSCLK with Respect to Memory Bus Speeds

**Note:** Due to errata Gen 13 the max sys clk frequency must not exceed 100 MHz if the core clk frequency is below 1200 MHz.

# 23 Ordering Information

Ordering information for the parts fully covered by this specification document is provided in Section 23.1, "Part Numbers Fully Addressed by this Document."

# 23.1 Part Numbers Fully Addressed by this Document

This table provides the Freescale part numbering nomenclature for the device. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the processor frequency, the part-numbering scheme also includes an application modifier that may specify special application conditions. Each part number also contains a revision code that refers to the die mask revision number.

Table 87. Part Numbering Nomenclature

| MPC             | nnnnn              | t                                       | рр                                                               | ff                                                            | С                                          | r                                                                                                                                                          |  |

|-----------------|--------------------|-----------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Product<br>Code | Part<br>Identifier | Temperature                             | Package <sup>1, 2, 3</sup>                                       | Processor<br>Frequency <sup>4</sup>                           | Core<br>Frequency                          | Silicon Version                                                                                                                                            |  |

| MPC             | 8548E              | Blank = 0 to 105°C<br>C = -40° to 105°C | HX = CBGA<br>VU = Pb-free CBGA<br>PX = PBGA<br>VT = Pb-free PBGA | AV = 1500 <sup>3</sup><br>AU = 1333<br>AT = 1200<br>AQ = 1000 | J = 533<br>H = 500 <sup>5</sup><br>G = 400 | Blank = Ver. 2.0<br>(SVR = 0x80390020)<br>A = Ver. 2.1.1<br>B = Ver. 2.1.2<br>C = Ver. 2.1.3<br>(SVR = 0x80390021)<br>D = Ver. 3.1.x<br>(SVR = 0x80390031) |  |

|                 | 8548               |                                         |                                                                  |                                                               |                                            | Blank = Ver. 2.0<br>(SVR = 0x80310020)<br>A = Ver. 2.1.1<br>B = Ver. 2.1.2<br>C = Ver. 2.1.3<br>(SVR = 0x80310021)<br>D = Ver. 3.1.x<br>(SVR = 0x80310031) |  |

|                 | 8547E              |                                         |                                                                  | AU = 1333<br>AT = 1200<br>AQ = 1000                           | J = 533<br>G = 400                         | Blank = Ver. 2.0<br>(SVR = 0x80390120)<br>A = Ver. 2.1.1<br>B = Ver. 2.1.2<br>C = Ver. 2.1.3<br>(SVR = 0x80390121)<br>D = Ver. 3.1.x<br>(SVR = 0x80390131) |  |

|                 | 8547               |                                         |                                                                  |                                                               |                                            | Blank = Ver. 2.0<br>(SVR = 0x80390120)<br>A = Ver. 2.1.1<br>B = Ver. 2.1.2<br>C = Ver. 2.1.3<br>(SVR = 0x80310121)<br>D = Ver. 3.1.x<br>(SVR = 0x80310131) |  |

## **Table 88. Document Revision History (continued)**

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|----------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 4              | 04/2009 | <ul> <li>In Table 1, "Absolute Maximum Ratings 1," and in Table 2, "Recommended Operating Conditions," moved text, "MII management voltage" from LV<sub>DD</sub>/TV<sub>DD</sub> to OV<sub>DD</sub>, added "Ethernet management" to OVDD row of input voltage section.</li> <li>In Table 5, "SYSCLK AC Timing Specifications," added notes 7 and 8 to SYSCLK frequency and cycle time.</li> <li>In Table 36, "MII Management DC Electrical Characteristics," changed all instances of LV<sub>DD</sub>/OV<sub>DD</sub> to OV<sub>DD</sub>.</li> <li>Modified Section 16, "High-Speed Serial Interfaces (HSSI)," to reflect that there is only one SerDes.</li> <li>Modified DDR clk rate min from 133 to 166 MHz.</li> <li>Modified note in Table 75, "Processor Core Clocking Specifications (MPC8548E and MPC8547E), "."</li> <li>In Table 56, "Differential Transmitter (TX) Output Specifications," modified equations in Comments column, and changed all instances of "LO" to "LO." Also added note 8.</li> <li>In Table 57, "Differential Receiver (RX) Input Specifications," modified equations in Comments column, and in note 3, changed "TRX-EYE-MEDIAN-to-MAX-JITTER," to "T<sub>RX-EYE-MEDIAN-to-MAX-JITTER</sub>."</li> <li>Modified Table 83, "Frequency Options of SYSCLK with Respect to Memory Bus Speeds."</li> <li>Added a note on Section 4.1, "System Clock Timing," to limit the SYSCLK to 100 MHz if the core frequency is less than 1200 MHz</li> <li>In Table 71, "MPC8543E Pinout ListingTable 72, "MPC8547E Pinout ListingTable 73, "MPC8545E Pinout ListingTable 74, "MPC8543E Pinout Listing," added note 5 to LA[28:31].</li> <li>Added note to Table 83, "Frequency Options of SYSCLK with Respect to Memory Bus Speeds."</li> </ul>   |  |

| 3              | 01/2009 | <ul> <li>[Section 4.6, "Platform Frequency Requirements for PCI-Express and Serial RapidIO." Changed minimum frequency equation to be 527 MHz for PCI x8.</li> <li>In Table 5, added note 7.</li> <li>Section 4.5, "Platform to FIFO Restrictions." Changed platform clock frequency to 4.2.</li> <li>Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1Gb Mbps)—GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics." Added MII after GMII and add 'or 2.5 V' after 3.3 V.</li> <li>In Table 23, modified table title to include GMII, MII, RMII, and TBI.</li> <li>In Table 24 and Table 25, changed clock period minimum to 5.3.</li> <li>In Table 26, Table 27, Table 28, Table 29, and Table 30, removed subtitle from table title.</li> <li>In Table 30 and Figure 15, changed all instances of PMA to TSECn.</li> <li>In Section 8.2.5, "TBI Single-Clock Mode AC Specifications." Replaced first paragraph.</li> <li>In Table 34, Table 35, Figure 18, and Figure 20, changed all instances of REF_CLK to TSECn_TX_CLK.</li> <li>In Table 36, changed all instances of OV<sub>DD</sub>/TV<sub>DD</sub>.</li> <li>In Table 37, "MII Management AC Timing Specifications," changed MDC minimum clock pulse width high from 32 to 48 ns.</li> <li>Added new section, Section 16, "High-Speed Serial Interfaces (HSSI)."</li> <li>Section 16.1, "DC Requirements for PCI Express SD_REF_CLK and SD_REF_CLK." Added new paragraph.</li> <li>Section 17.1, "DC Requirements for Serial RapidIO SD_REF_CLK and SD_REF_CLK." Added new paragraph.</li> <li>Section 22.3, "Decoupling Recommendations." Modified the recommendation.</li> <li>Table 87, "Part Numbering Nomenclature." In Silicon Version column added Ver. 2.1.2.</li> </ul> |  |

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9