#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 800MHz                                                                |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                                 |

| RAM Controllers                 | DDR, DDR2, SDRAM                                                      |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (4)                                                   |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                      |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | Cryptography, Random Number Generator                                 |

| Package / Case                  | 783-BBGA, FCBGA                                                       |

| Supplier Device Package         | 783-FCBGA (29x29)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8545evuang |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.1.3 Output Driver Characteristics

The following table provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

| Driver Type                           | Programmable<br>Output Impedance<br>(Ω) | Supply<br>Voltage                                    | Notes |

|---------------------------------------|-----------------------------------------|------------------------------------------------------|-------|

| Local bus interface utilities signals | 25<br>25                                | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V | 1     |

|                                       | 45(default)<br>45(default)              | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V |       |

| PCI signals                           | 25                                      | OV <sub>DD</sub> = 3.3 V                             | 2     |

|                                       | 45(default)                             |                                                      |       |

| DDR signal                            | 18<br>36 (half strength mode)           | GV <sub>DD</sub> = 2.5 V                             | 3     |

| DDR2 signal                           | 18<br>36 (half strength mode)           | GV <sub>DD</sub> = 1.8 V                             | 3     |

| TSEC/10/100 signals                   | 45                                      | L/TV <sub>DD</sub> = 2.5/3.3 V                       | —     |

| DUART, system control, JTAG           | 45                                      | OV <sub>DD</sub> = 3.3 V                             | —     |

| 12C                                   | 150                                     | OV <sub>DD</sub> = 3.3 V                             |       |

Table 3. Output Drive Capability

Notes:

1. The drive strength of the local bus interface is determined by the configuration of the appropriate bits in PORIMPSCR.

2. The drive strength of the PCI interface is determined by the setting of the PCI\_GNT1 signal at reset.

3. The drive strength of the DDR interface in half-strength mode is at  $T_i = 105^{\circ}C$  and at  $GV_{DD}$  (min).

# 2.2 Power Sequencing

The device requires its power rails to be applied in a specific sequence in order to ensure proper device operation. These requirements are as follows for power-up:

- 1. V<sub>DD</sub>, AV<sub>DD</sub>, BV<sub>DD</sub>, LV<sub>DD</sub>, OV<sub>DD</sub>, SV<sub>DD</sub>, TV<sub>DD</sub>, XV<sub>DD</sub>

- 2.  $GV_{DD}$

All supplies must be at their stable values within 50 ms.

## NOTE

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90% of their value before the voltage rails on the current step reach 10% of theirs.

## NOTE

In order to guarantee MCKE low during power-up, the above sequencing for  $GV_{DD}$  is required. If there is no concern about any of the DDR signals being in an indeterminate state during power-up, then the sequencing for  $GV_{DD}$  is not required.

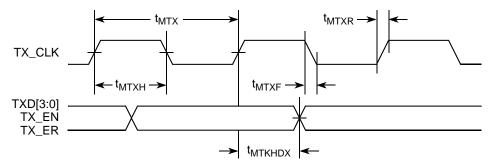

Figure 11 shows the MII transmit AC timing diagram.

Figure 11. MII Transmit AC Timing Diagram

## 8.2.3.2 MII Receive AC Timing Specifications

This table provides the MII receive AC timing specifications.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min  | Тур | Max | Unit |

|---------------------------------------------|-------------------------------------|------|-----|-----|------|

| RX_CLK clock period 10 Mbps                 | t <sub>MRX</sub> 2                  | _    | 400 | _   | ns   |

| RX_CLK clock period 100 Mbps                | t <sub>MRX</sub>                    |      | 40  |     | ns   |

| RX_CLK duty cycle                           | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35   | _   | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>MRDVKH</sub>                 | 10.0 | _   | _   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>MRDXKH</sub>                 | 10.0 | _   | _   | ns   |

| RX_CLK clock rise (20%–80%)                 | t <sub>MRXR</sub> <sup>2</sup>      | 1.0  | _   | 4.0 | ns   |

| RX_CLK clock fall time (80%–20%)            | t <sub>MRXF</sub> <sup>2</sup>      | 1.0  | _   | 4.0 | ns   |

Notes:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

2. Guaranteed by design.

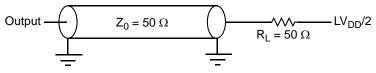

Figure 12 provides the AC test load for eTSEC.

Figure 12. eTSEC AC Test Load

| Parameter                                                             | Symbol <sup>1</sup>                 | Min | Max | Unit | Notes |

|-----------------------------------------------------------------------|-------------------------------------|-----|-----|------|-------|

| Local bus cycle time                                                  | t <sub>LBK</sub>                    | 7.5 | 12  | ns   | 2     |

| Local bus duty cycle                                                  | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43  | 57  | %    | —     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                  | t <sub>LBKSKEW</sub>                | —   | 150 | ps   | 7, 8  |

| Input setup to local bus clock (except LGTA/UPWAIT)                   | t <sub>LBIVKH1</sub>                | 1.9 | —   | ns   | 3, 4  |

| LGTA/LUPWAIT input setup to local bus clock                           | t <sub>LBIVKH2</sub>                | 1.8 | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LGTA/LUPWAIT)                 | t <sub>LBIXKH1</sub>                | 1.1 | —   | ns   | 3, 4  |

| LGTA/LUPWAIT input hold from local bus clock                          | t <sub>LBIXKH2</sub>                | 1.1 | —   | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) | t <sub>LBOTOT</sub>                 | 1.5 | —   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)             | t <sub>LBKHOV1</sub>                | —   | 2.1 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                             | t <sub>LBKHOV2</sub>                | —   | 2.3 | ns   | 3     |

| Local bus clock to address valid for LAD                              | t <sub>LBKHOV3</sub>                | —   | 2.4 | ns   | 3     |

| Local bus clock to LALE assertion                                     | t <sub>LBKHOV4</sub>                | —   | 2.4 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)            | t <sub>LBKHOX1</sub>                | 0.8 | —   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                          | t <sub>LBKHOX2</sub>                | 0.8 | —   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)    | t <sub>LBKHOZ1</sub>                | —   | 2.6 | ns   | 5     |

| Local bus clock to output high impedance for LAD/LDP                  | t <sub>LBKHOZ2</sub>                | _   | 2.6 | ns   | 5     |

Table 41 describes the timing parameters of the local bus interface at  $BV_{DD} = 2.5$  V.

### Table 41. Local Bus Timing Parameters (BV<sub>DD</sub> = 2.5 V)—PLL Enabled

#### Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKH0X</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub></sub>

- 2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 3.3-V signaling levels.

- 4. Input timings are measured at the pin.

5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 8. Guaranteed by design.

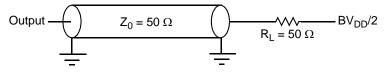

Figure 22 provides the AC test load for the local bus.

Figure 22. Local Bus AC Test Load

| Parameter                                                             | Symbol <sup>1</sup>  | Min  | Max  | Unit | Notes |

|-----------------------------------------------------------------------|----------------------|------|------|------|-------|

| LGTA/LUPWAIT input hold from local bus clock                          | t <sub>LBIXKL2</sub> | -1.3 |      | ns   | 4, 5  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) | t <sub>LBOTOT</sub>  | 1.5  |      | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)             | t <sub>LBKLOV1</sub> | _    | -0.3 | ns   |       |

| Local bus clock to data valid for LAD/LDP                             | t <sub>LBKLOV2</sub> | _    | -0.1 | ns   | 4     |

| Local bus clock to address valid for LAD                              | t <sub>LBKLOV3</sub> | _    | 0    | ns   | 4     |

| Local bus clock to LALE assertion                                     | t <sub>LBKLOV4</sub> | _    | 0    | ns   | 4     |

| Output hold from local bus clock (except LAD/LDP and LALE)            | t <sub>LBKLOX1</sub> | -3.7 |      | ns   | 4     |

| Output hold from local bus clock for LAD/LDP                          | t <sub>LBKLOX2</sub> | -3.7 |      | ns   | 4     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)    | t <sub>LBKLOZ1</sub> | _    | 0.2  | ns   | 7     |

| Local bus clock to output high impedance for LAD/LDP                  | t <sub>LBKLOZ2</sub> | _    | 0.2  | ns   | 7     |

#### Table 42. Local Bus Timing Parameters—PLL Bypassed (continued)

#### Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKH0X</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

All timings are in reference to local bus clock for PLL bypass mode. Timings may be negative with respect to the local bus clock because the actual launch and capture of signals is done with the internal launch/capture clock, which precedes LCLK by t<sub>LBKHKT</sub>.

3. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

4. All signals are measured from  $BV_{DD}/2$  of the rising edge of local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 3.3-V signaling levels.

5. Input timings are measured at the pin.

6. The value of t<sub>LBOTOT</sub> is the measurement of the minimum time between the negation of LALE and any change in LAD.

7. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 8. Guaranteed by characterization.

- 9. Guaranteed by design.

#### Local Bus

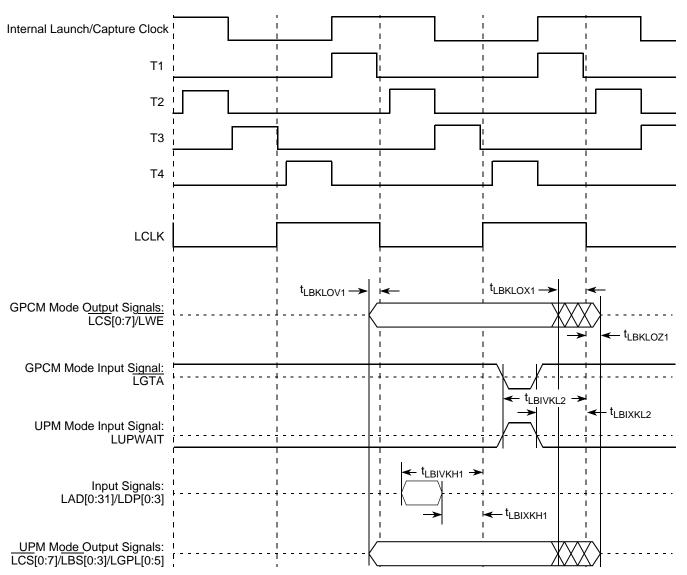

Figure 28. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 8 or 16 (PLL Bypass Mode)

# 11 Programmable Interrupt Controller

In IRQ edge trigger mode, when an external interrupt signal is asserted (according to the programmed polarity), it must remain the assertion for at least 3 system clocks (SYSCLK periods).

# 12 JTAG

This section describes the DC and AC electrical specifications for the IEEE 1149.1 (JTAG) interface of the device.

# **12.1 JTAG DC Electrical Characteristics**

This table provides the DC electrical characteristics for the JTAG interface.

| Parameter                                                      | Symbol <sup>1</sup> | Min  | Мах                    | Unit |

|----------------------------------------------------------------|---------------------|------|------------------------|------|

| High-level input voltage                                       | V <sub>IH</sub>     | 2    | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                        | V <sub>IL</sub>     | -0.3 | 0.8                    | V    |

| Input current ( $V_{IN}^{1} = 0$ V or $V_{IN} = V_{DD}$ )      | I <sub>IN</sub>     | —    | ±5                     | μA   |

| High-level output voltage ( $OV_{DD}$ = min, $I_{OH}$ = -2 mA) | V <sub>OH</sub>     | 2.4  | _                      | V    |

| Low-level output voltage ( $OV_{DD} = min, I_{OL} = 2 mA$ )    | V <sub>OL</sub>     | —    | 0.4                    | V    |

Table 43. JTAG DC Electrical Characteristics

Note:

1. Note that the symbol  $V_{\text{IN}}$  in this case, represents the  $\text{OV}_{\text{IN}}$

# **12.2 JTAG AC Electrical Specifications**

This table provides the JTAG AC timing specifications as defined in Figure 30 through Figure 32.

| Parameter                                            | Symbol <sup>2</sup>                        | Min      | Мах  | Unit | Notes |

|------------------------------------------------------|--------------------------------------------|----------|------|------|-------|

| JTAG external clock frequency of operation           | f <sub>JTG</sub>                           | 0        | 33.3 | MHz  |       |

| JTAG external clock cycle time                       | t <sub>JTG</sub>                           | 30       | _    | ns   | _     |

| JTAG external clock pulse width measured at 1.4 V    | t <sub>JTKHKL</sub>                        | 15       | _    | ns   | _     |

| JTAG external clock rise and fall times              | t <sub>JTGR</sub> & t <sub>JTGF</sub>      | 0        | 2    | ns   | 6     |

| TRST assert time                                     | t <sub>TRST</sub>                          | 25       | _    | ns   | 3     |

| Input setup times:<br>Boundary-scan data<br>TMS, TDI | t <sub>JTDVKH</sub><br>t <sub>JTIVKH</sub> | 4<br>0   |      | ns   | 4     |

| Input hold times:<br>Boundary-scan data<br>TMS, TDI  | <sup>t</sup> jtdxkh<br><sup>t</sup> jtixkh | 20<br>25 |      | ns   | 4     |

Table 44. JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup>

| Parameter                                                                                      | Symbol           | Min  | Мах                    | Unit |

|------------------------------------------------------------------------------------------------|------------------|------|------------------------|------|

| Supply voltage 2.5 V                                                                           | BV <sub>DD</sub> | 2.37 | 2.63                   | V    |

| High-level input voltage                                                                       | V <sub>IH</sub>  | 1.70 | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                                        | V <sub>IL</sub>  | -0.3 | 0.7                    | V    |

| Input current<br>(BV <sub>IN</sub> <sup>1</sup> = 0 V or BV <sub>IN</sub> = BV <sub>DD</sub> ) | I <sub>IH</sub>  | _    | 10                     | μΑ   |

Table 50. GP<sub>IN</sub> DC Electrical Characteristics (2.5 V DC)

Note:

1. The symbol  $\mathsf{BV}_{\mathsf{IN}}$  in this case, represents the  $\mathsf{BV}_{\mathsf{IN}}$  symbol referenced in Table 1.

# 15 PCI/PCI-X

This section describes the DC and AC electrical specifications for the PCI/PCI-X bus of the device.

Note that the maximum PCI-X frequency in synchronous mode is 110 MHz.

# 15.1 PCI/PCI-X DC Electrical Characteristics

This table provides the DC electrical characteristics for the PCI/PCI-X interface.

Table 51. PCI/PCI-X DC Electrical Characteristics<sup>1</sup>

| Parameter                                                     | Symbol          | Min  | Мах                    | Unit | Notes |

|---------------------------------------------------------------|-----------------|------|------------------------|------|-------|

| High-level input voltage                                      | V <sub>IH</sub> | 2    | OV <sub>DD</sub> + 0.3 | V    | _     |

| Low-level input voltage                                       | V <sub>IL</sub> | -0.3 | 0.8                    | V    | —     |

| Input current ( $V_{IN} = 0 V \text{ or } V_{IN} = V_{DD}$ )  | I <sub>IN</sub> | —    | ±5                     | μA   | 2     |

| High-level output voltage ( $OV_{DD} = min, I_{OH} = -2 mA$ ) | V <sub>OH</sub> | 2.4  | —                      | V    | —     |

| Low-level output voltage ( $OV_{DD} = min, I_{OL} = 2 mA$ )   | V <sub>OL</sub> | —    | 0.4                    | V    | —     |

Notes:

1. Ranges listed do not meet the full range of the DC specifications of the PCI 2.2 Local Bus Specifications.

2. The symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

# 15.2 PCI/PCI-X AC Electrical Specifications

This section describes the general AC timing parameters of the PCI/PCI-X bus. Note that the clock reference CLK is represented by SYSCLK when the PCI controller is configured for synchronous mode and by PCIn\_CLK when it is configured for asynchronous mode.

# 16.2.4 AC Requirements for SerDes Reference Clocks

The clock driver selected must provide a high quality reference clock with low phase noise and cycle-to-cycle jitter. Phase noise less than 100 kHz can be tracked by the PLL and data recovery loops and is less of a problem. Phase noise above 15 MHz is filtered by the PLL. The most problematic phase noise occurs in the 1–15 MHz range. The source impedance of the clock driver must be 50  $\Omega$  to match the transmission line and reduce reflections which are a source of noise to the system.

The detailed AC requirements of the SerDes reference clocks are defined by each interface protocol based on application usage. See the following sections for detailed information:

- Section 17.2, "AC Requirements for PCI Express SerDes Clocks"

- Section 18.2, "AC Requirements for Serial RapidIO SD\_REF\_CLK and SD\_REF\_CLK"

## 16.2.4.1 Spread Spectrum Clock

SD\_REF\_CLK/SD\_REF\_CLK are designed to work with a spread spectrum clock (+0% to -0.5% spreading at 30–33 kHz rate is allowed), assuming both ends have same reference clock. For better results, a source without significant unintended modulation must be used.

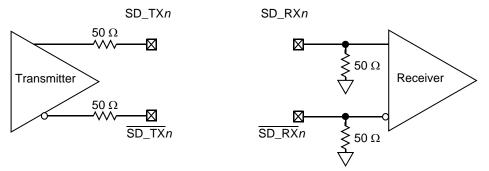

# 16.3 SerDes Transmitter and Receiver Reference Circuits

Figure 47 shows the reference circuits for SerDes data lane's transmitter and receiver.

Figure 47. SerDes Transmitter and Receiver Reference Circuits

The DC and AC specification of SerDes data lanes are defined in each interface protocol section below (PCI Express, Serial Rapid IO, or SGMII) in this document based on the application usage:

- Section 17, "PCI Express"

- Section 18, "Serial RapidIO"

Note that external an AC coupling capacitor is required for the above three serial transmission protocols with the capacitor value defined in the specification of each protocol section.

| Symbol                 | Parameter                   | Min | Nom | Max | Unit | Comments                                                                                                                                                 |

|------------------------|-----------------------------|-----|-----|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>crosslink</sub> | Crosslink<br>random timeout | 0   |     | 1   | ms   | This random timeout helps resolve conflicts in crosslink configuration by eventually resulting in only one downstream and one upstream port. See Note 7. |

Notes:

1. No test load is necessarily associated with this value.

- 2. Specified at the measurement point into a timing and voltage compliance test load as shown in Figure 50 and measured over any 250 consecutive TX UIs. (Also see the transmitter compliance eye diagram shown in Figure 48.)

- 3. A T<sub>TX-EYE</sub> = 0.70 UI provides for a total sum of deterministic and random jitter budget of T<sub>TX-JITTER-MAX</sub> = 0.30 UI for the transmitter collected over any 250 consecutive TX UIs. The T<sub>TX-EYE-MEDIAN-to-MAX-JITTER</sub> median is less than half of the total TX jitter budget collected over any 250 consecutive TX UIs. Note that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value.

- 4. The transmitter input impedance shall result in a differential return loss greater than or equal to 12 dB and a common mode return loss greater than or equal to 6 dB over a frequency range of 50 MHz to 1.25 GHz. This input impedance requirement applies to all valid input levels. The reference impedance for return loss measurements is 50  $\Omega$  to ground for both the D+ and D- line (that is, as measured by a vector network analyzer with 50- $\Omega$  probes—see Figure 50). Note that the series capacitors C<sub>TX</sub> is optional for the return loss measurement.

- 5. Measured between 20%–80% at transmitter package pins into a test load as shown in Figure 50 for both V<sub>TX-D+</sub> and V<sub>TX-D-</sub>.

- 6. See Section 4.3.1.8 of the PCI Express Base Specifications Rev 1.0a.

- 7. See Section 4.2.6.3 of the PCI Express Base Specifications Rev 1.0a.

- 8. MPC8548E SerDes transmitter does not have CTX built in. An external AC coupling capacitor is required.

## 17.4.2 Transmitter Compliance Eye Diagrams

The TX eye diagram in Figure 48 is specified using the passive compliance/test measurement load (see Figure 50) in place of any real PCI Express interconnect +RX component.

There are two eye diagrams that must be met for the transmitter. Both eye diagrams must be aligned in time using the jitter median to locate the center of the eye diagram. The different eye diagrams differ in voltage depending whether it is a transition bit or a de-emphasized bit. The exact reduced voltage level of the de-emphasized bit is always relative to the transition bit.

The eye diagram must be valid for any 250 consecutive UIs.

A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. The eye diagram is created using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI.

## NOTE

It is recommended that the recovered TX UI is calculated using all edges in the 3500 consecutive UI interval with a fit algorithm using a minimization merit function (for example, least squares and median deviation fits).

#### **PCI Express**

Figure 48. Minimum Transmitter Timing and Voltage Output Compliance Specifications

## 17.4.3 Differential Receiver (RX) Input Specifications

Table 57 defines the specifications for the differential input at all receivers (RXs). The parameters are specified at the component pins.

| Symbol                                       | Parameter                                                                                   | Min    | Nom | Max    | Unit | Comments                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------|---------------------------------------------------------------------------------------------|--------|-----|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI                                           | Unit interval                                                                               | 399.88 | 400 | 400.12 | ps   | Each UI is 400 ps $\pm$ 300 ppm. UI does not account<br>for spread spectrum clock dictated variations.<br>See Note 1.                                                                                                                                                                                                                                                                        |

| V <sub>RX-DIFFp-p</sub>                      | Differential<br>peak-to-peak<br>input voltage                                               | 0.175  | —   | 1.200  | V    | $V_{RX-DIFFp-p} = 2 \times  V_{RX-D+} - V_{RX-D-} $ . See Note 2.                                                                                                                                                                                                                                                                                                                            |

| T <sub>RX-EYE</sub>                          | Minimum<br>receiver eye<br>width                                                            | 0.4    | _   | _      | UI   | The maximum interconnect media and transmitter jitter that can be tolerated by the receiver can be derived as $T_{RX-MAX-JITTER} = 1 - T_{RX-EYE} = 0.6$ UI. See Notes 2 and 3.                                                                                                                                                                                                              |

| T <sub>RX-EYE-MEDIAN-to-</sub><br>MAX-JITTER | Maximum time<br>between the<br>jitter median and<br>maximum<br>deviation from<br>the median | —      |     | 0.3    | UI   | Jitter is defined as the measurement variation of<br>the crossing points ( $V_{RX-DIFFp-p} = 0$ V) in relation<br>to a recovered TX UI. A recovered TX UI is<br>calculated over 3500 consecutive unit intervals of<br>sample data. Jitter is measured using all edges of<br>the 250 consecutive UI in the center of the<br>3500 UI used for calculating the TX UI.<br>See Notes 2, 3, and 7. |

Table 57. Differential Receiver (RX) Input Specifications

#### Serial RapidIO

| Characteristic              | Cumhal              | Range |      | Unit   | Notes                                                                      |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Unit   | Notes                                                                      |

| Output voltage              | Vo                  | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal comprising a differential pair |

| Differential output voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mV p-p | —                                                                          |

| Deterministic jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                          |

| Total jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                          |

| Multiple output skew        | S <sub>MO</sub>     | —     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |

| Unit interval               | UI                  | 400   | 400  | ps     | ±100 ppm                                                                   |

### Table 61. Short Run Transmitter AC Timing Specifications—3.125 GBaud

| Characteristic              | Symbol              | Range |      | Unit   | Notes                                                                      |  |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------|--|

| Characteristic              |                     |       | Max  | Onic   | Notes                                                                      |  |

| Output voltage              | Vo                  | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal comprising a differential pair |  |

| Differential output voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mVp-p  | -                                                                          |  |

| Deterministic jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | -                                                                          |  |

| Total jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                          |  |

| Multiple output skew        | S <sub>MO</sub>     | —     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |  |

| Unit interval               | UI                  | 320   | 320  | ps     | ±100 ppm                                                                   |  |

## Table 62. Long Run Transmitter AC Timing Specifications—1.25 GBaud

| Characteristic              | Symbol              | Range |      | Unit   | Notes                                                                      |  |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------|--|

| Characteristic              |                     | Min   | Max  | onit   | NOLES                                                                      |  |

| Output voltage              | V <sub>O</sub>      | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal comprising a differential pair |  |

| Differential output voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mVp-p  | —                                                                          |  |

| Deterministic jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                          |  |

| Total jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                          |  |

| Multiple output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |  |

| Unit interval               | UI                  | 800   | 800  | ps     | ±100 ppm                                                                   |  |

#### Serial RapidIO

| Characteristic              | Symbol              | Range |      | Unit   | Notes                                                                      |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Unit   | notes                                                                      |

| Output voltage              | Vo                  | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal comprising a differential pair |

| Differential output voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mVp-p  | —                                                                          |

| Deterministic jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                          |

| Total jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                          |

| Multiple output skew        | S <sub>MO</sub>     | —     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |

| Unit interval               | UI                  | 400   | 400  | ps     | ±100 ppm                                                                   |

Table 63. Long Run Transmitter AC Timing Specifications—2.5 GBaud

## Table 64. Long Run Transmitter AC Timing Specifications—3.125 GBaud

| Characteristic              | Symbol              | Range |      | Unit   | Notes                                                                      |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Onic   | NULES                                                                      |

| Output voltage              | Vo                  | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal comprising a differential pair |

| Differential output voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mVp-p  | —                                                                          |

| Deterministic jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                          |

| Total jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                          |

| Multiple output skew        | S <sub>MO</sub>     | —     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |

| Unit interval               | UI                  | 320   | 320  | ps     | ±100 ppm                                                                   |

For each baud rate at which an LP-serial transmitter is specified to operate, the output eye pattern of the transmitter shall fall entirely within the unshaded portion of the transmitter output compliance mask shown in Figure 52 with the parameters specified in Table 65 when measured at the output pins of the device and the device is driving a  $100-\Omega \pm 5\%$  differential resistive load. The output eye pattern of an LP-serial

## Table 71. MPC8548E Pinout Listing (continued)

| Signal                   | Package Pin Number                                                                                                                                                      | Pin Type | Power<br>Supply  | Notes   |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|---------|

| MWE                      | E7                                                                                                                                                                      | 0        | GV <sub>DD</sub> |         |

| MCAS                     | H7                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —       |

| MRAS                     | L8                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —       |

| MCKE[0:3]                | F10, C10, J11, H11                                                                                                                                                      | 0        | GV <sub>DD</sub> | 11      |

| MCS[0:3]                 | K8, J8, G8, F8                                                                                                                                                          | 0        | GV <sub>DD</sub> | —       |

| MCK[0:5]                 | H9, B15, G2, M9, A14, F1                                                                                                                                                | 0        | GV <sub>DD</sub> | —       |

| MCK[0:5]                 | J9, A15, G1, L9, B14, F2                                                                                                                                                | 0        | GV <sub>DD</sub> | —       |

| MODT[0:3]                | E6, K6, L7, M7                                                                                                                                                          | 0        | GV <sub>DD</sub> | —       |

| MDIC[0:1]                | A19, B19                                                                                                                                                                | I/O      | GV <sub>DD</sub> | 36      |

|                          | Local Bus Controller Interface                                                                                                                                          |          | •                | -       |

| LAD[0:31]                | E27, B20, H19, F25, A20, C19, E28, J23, A25,<br>K22, B28, D27, D19, J22, K20, D28, D25, B25,<br>E22, F22, F21, C25, C22, B23, F20, A23, A22,<br>E19, A21, D21, F19, B21 | I/O      | BV <sub>DD</sub> | _       |

| LDP[0:3]                 | K21, C28, B26, B22                                                                                                                                                      | I/O      | BV <sub>DD</sub> | —       |

| LA[27]                   | H21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LA[28:31]                | H20, A27, D26, A28                                                                                                                                                      | 0        | BV <sub>DD</sub> | 5, 7, 9 |

| LCS[0:4]                 | J25, C20, J24, G26, A26                                                                                                                                                 | 0        | BV <sub>DD</sub> |         |

| LCS5/DMA_DREQ2           | D23                                                                                                                                                                     | I/O      | BV <sub>DD</sub> | 1       |

| LCS6/DMA_DACK2           | G20                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 1       |

| LCS7/DMA_DDONE2          | E21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 1       |

| LWE0/LBS0/LSDDQM[0]      | G25                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE1/LBS1/LSDDQM[1]      | C23                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE2/LBS2/LSDDQM[2]      | J21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE3/LBS3/LSDDQM[3]      | A24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LALE                     | H24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| LBCTL                    | G27                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| LGPL0/LSDA10             | F23                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LGPL1/LSDWE              | G22                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LGPL2/LOE/LSDRAS         | B27                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| LGPL3/LSDCAS             | F24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LGPL4/LGTA/LUPWAIT/LPBSE | H23                                                                                                                                                                     | I/O      | BV <sub>DD</sub> | —       |

| LGPL5                    | E26                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LCKE                     | E24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | -       |

| LCLK[0:2]                | E23, D24, H22                                                                                                                                                           | 0        | BV <sub>DD</sub> | —       |

| Signal         | Package Pin Number                       | Pin Type   | Power<br>Supply  | Notes    |

|----------------|------------------------------------------|------------|------------------|----------|

| FIFO1_RXC2     | P5                                       | I          | LV <sub>DD</sub> | 104      |

| Reserved       | R1                                       | —          | _                | 104      |

| Reserved       | P10                                      | —          | —                | 105      |

| FIFO1_TXC2     | P7                                       | 0          | LV <sub>DD</sub> | 15       |

| cfg_dram_type1 | R10                                      | I          | LV <sub>DD</sub> | 5        |

| Thre           | ee-Speed Ethernet Controller (Gigabit Et | thernet 3) |                  |          |

| TSEC3_TXD[3:0] | V8, W10, Y10, W7                         | 0          | TV <sub>DD</sub> | 5, 9, 29 |

| TSEC3_RXD[3:0] | Y1, W3, W5, W4                           | I          | TV <sub>DD</sub> |          |

| TSEC3_GTX_CLK  | W8                                       | 0          | TV <sub>DD</sub> |          |

| TSEC3_RX_CLK   | W2                                       | I          | TV <sub>DD</sub> | —        |

| TSEC3_RX_DV    | W1                                       | I          | TV <sub>DD</sub> | _        |

| TSEC3_RX_ER    | Y2                                       | I          | TV <sub>DD</sub> | _        |

| TSEC3_TX_CLK   | V10                                      | I          | TV <sub>DD</sub> | _        |

| TSEC3_TX_EN    | V9                                       | 0          | TV <sub>DD</sub> | 30       |

| TSEC3_TXD[7:4] | AB8, Y7, AA7, Y8                         | 0          | TV <sub>DD</sub> | 5, 9, 29 |

| TSEC3_RXD[7:4] | AA1, Y3, AA2, AA4                        | I          | TV <sub>DD</sub> | _        |

| Reserved       | AA5                                      | —          | —                | 15       |

| TSEC3_COL      | Y5                                       | I          | TV <sub>DD</sub> | —        |

| TSEC3_CRS      | AA3                                      | I/O        | TV <sub>DD</sub> | 31       |

| TSEC3_TX_ER    | AB6                                      | 0          | TV <sub>DD</sub> | —        |

|                | DUART                                    |            | •                |          |

| UART_CTS[0:1]  | AB3, AC5                                 | I          | OV <sub>DD</sub> |          |

| UART_RTS[0:1]  | AC6, AD7                                 | 0          | OV <sub>DD</sub> |          |

| UART_SIN[0:1]  | AB5, AC7                                 | I          | OV <sub>DD</sub> |          |

| UART_SOUT[0:1] | AB7, AD8                                 | 0          | OV <sub>DD</sub> | _        |

| <b>I</b>       | I <sup>2</sup> C interface               |            |                  | 1        |

| IIC1_SCL       | AG22                                     | I/O        | OV <sub>DD</sub> | 4, 27    |

| IIC1_SDA       | AG21                                     | I/O        | OV <sub>DD</sub> | 4, 27    |

| IIC2_SCL       | AG15                                     | I/O        | OV <sub>DD</sub> | 4, 27    |

| IIC2_SDA       | AG14                                     | I/O        | OV <sub>DD</sub> | 4, 27    |

|                | SerDes                                   | 1          |                  |          |

| SD_RX[0:3]     | M28, N26, P28, R26                       | I          | XV <sub>DD</sub> | _        |

| SD_RX[0:3]     | M27, N25, P27, R25                       | I          | XV <sub>DD</sub> | —        |

| SD_TX[0:3]     | M22, N20, P22, R20                       | 0          | XV <sub>DD</sub> |          |

Package Description

| Signal                 | Package Pin Number                     | Pin Type | Power<br>Supply  | Notes           |

|------------------------|----------------------------------------|----------|------------------|-----------------|

| SD_TX[0:3]             | M23, N21, P23, R21                     | 0        | XV <sub>DD</sub> | —               |

| Reserved               | W26, Y28, AA26, AB28                   | _        | _                | 40              |

| Reserved               | W25, Y27, AA25, AB27                   | —        | —                | 40              |

| Reserved               | U20, V22, W20, Y22                     | —        | —                | 15              |

| Reserved               | U21, V23, W21, Y23                     | —        | —                | 15              |

| SD_PLL_TPD             | U28                                    | 0        | XV <sub>DD</sub> | 24              |

| SD_REF_CLK             | T28                                    | I        | XV <sub>DD</sub> | —               |

| SD_REF_CLK             | T27                                    | I        | XV <sub>DD</sub> | —               |

| Reserved               | AC1, AC3                               | _        | —                | 2               |

| Reserved               | M26, V28                               | _        | —                | 32              |

| Reserved               | M25, V27                               | _        | —                | 34              |

| Reserved               | M20, M21, T22, T23                     | _        | —                | 38              |

|                        | General-Purpose Output                 |          |                  |                 |

| GPOUT[24:31]           | K26, K25, H27, G28, H25, J26, K24, K23 | 0        | BV <sub>DD</sub> | —               |

|                        | System Control                         |          |                  |                 |

| HRESET                 | AG17                                   | I        | OV <sub>DD</sub> | —               |

| HRESET_REQ             | AG16                                   | 0        | OV <sub>DD</sub> | 29              |

| SRESET                 | AG20                                   | I        | OV <sub>DD</sub> | —               |

| CKSTP_IN               | AA9                                    | I        | OV <sub>DD</sub> | —               |

| CKSTP_OUT              | AA8                                    | 0        | OV <sub>DD</sub> | 2, 4            |

|                        | Debug                                  |          | •                |                 |

| TRIG_IN                | AB2                                    | I        | OV <sub>DD</sub> | —               |

| TRIG_OUT/READY/QUIESCE | AB1                                    | 0        | OV <sub>DD</sub> | 6, 9,<br>19, 29 |

| MSRCID[0:1]            | AE4, AG2                               | 0        | OV <sub>DD</sub> | 5, 6, 9         |

| MSRCID[2:4]            | AF3, AF1, AF2                          | 0        | OV <sub>DD</sub> | 6, 19,<br>29    |

| MDVAL                  | AE5                                    | 0        | OV <sub>DD</sub> | 6               |

| CLK_OUT                | AE21                                   | 0        | OV <sub>DD</sub> | 11              |

|                        | Clock                                  |          |                  |                 |

| RTC                    | AF16                                   | I        | OV <sub>DD</sub> | —               |

| SYSCLK                 | AH17                                   | I        | OV <sub>DD</sub> | —               |

|                        | JTAG                                   | •        |                  |                 |

| ТСК                    | AG28                                   | I        | OV <sub>DD</sub> | —               |

| TDI                    | AH28                                   | I        | OV <sub>DD</sub> | 12              |

| Signal             | Package Pin Number                             | Pin Type | Power<br>Supply  | Notes     |

|--------------------|------------------------------------------------|----------|------------------|-----------|

| LSYNC_IN           | F27                                            | I        | BV <sub>DD</sub> | —         |

| LSYNC_OUT          | F28                                            | 0        | BV <sub>DD</sub> | —         |

|                    | DMA                                            |          |                  | 1         |

| DMA_DACK[0:1]      | AD3, AE1                                       | 0        | OV <sub>DD</sub> | 5, 9, 108 |

| DMA_DREQ[0:1]      | AD4, AE2                                       | I        | OV <sub>DD</sub> | —         |

| DMA_DDONE[0:1]     | AD2, AD1                                       | 0        | OV <sub>DD</sub> | —         |

|                    | Programmable Interrupt Controller              |          |                  | •         |

| UDE                | AH16                                           | Ι        | OV <sub>DD</sub> | —         |

| MCP                | AG19                                           | I        | OV <sub>DD</sub> | —         |

| IRQ[0:7]           | AG23, AF18, AE18, AF20, AG18, AF17, AH24, AE20 | I        | $OV_{DD}$        | —         |

| IRQ[8]             | AF19                                           | I        | OV <sub>DD</sub> | —         |

| IRQ[9]/DMA_DREQ3   | AF21                                           | I        | OV <sub>DD</sub> | 1         |

| IRQ[10]/DMA_DACK3  | AE19                                           | I/O      | OV <sub>DD</sub> | 1         |

| IRQ[11]/DMA_DDONE3 | AD20                                           | I/O      | OV <sub>DD</sub> | 1         |

| IRQ_OUT            | AD18                                           | 0        | OV <sub>DD</sub> | 2, 4      |

|                    | Ethernet Management Interface                  |          |                  | 1         |

| EC_MDC             | AB9                                            | 0        | OV <sub>DD</sub> | 5, 9      |

| EC_MDIO            | AC8                                            | I/O      | $OV_{DD}$        | —         |

|                    | Gigabit Reference Clock                        |          |                  |           |

| EC_GTX_CLK125      | V11                                            | Ι        | LV <sub>DD</sub> | —         |

|                    | Three-Speed Ethernet Controller (Gigabit Ether | rnet 1)  |                  | •         |

| TSEC1_RXD[7:0]     | R5, U1, R3, U2, V3, V1, T3, T2                 | Ι        | $LV_{DD}$        | —         |

| TSEC1_TXD[7:0]     | T10, V7, U10, U5, U4, V6, T5, T8               | 0        | $LV_{DD}$        | 5, 9      |

| TSEC1_COL          | R4                                             | I        | LV <sub>DD</sub> | —         |

| TSEC1_CRS          | V5                                             | I/O      | LV <sub>DD</sub> | 20        |

| TSEC1_GTX_CLK      | U7                                             | 0        | $LV_{DD}$        | —         |

| TSEC1_RX_CLK       | U3                                             | I        | LV <sub>DD</sub> | —         |

| TSEC1_RX_DV        | V2                                             | I        | LV <sub>DD</sub> | —         |

| TSEC1_RX_ER        | T1                                             | I        | LV <sub>DD</sub> | —         |

| TSEC1_TX_CLK       | Т6                                             | I        | LV <sub>DD</sub> | —         |

| TSEC1_TX_EN        | U9                                             | 0        | LV <sub>DD</sub> | 30        |

| TSEC1_TX_ER        | Т7                                             | 0        | $LV_{DD}$        | —         |

| GPIN[0:7]          | P2, R2, N1, N2, P3, M2, M1, N3                 | I        | LV <sub>DD</sub> | 103       |

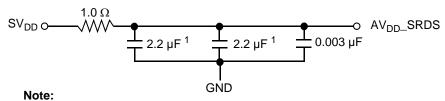

the ground plane. Use ceramic chip capacitors with the highest possible self-resonant frequency. All traces must be kept short, wide and direct.

1. An 0805 sized capacitor is recommended for system initial bring-up.

### Figure 60. SerDes PLL Power Supply Filter

Note the following:

- AV<sub>DD</sub>\_SRDS must be a filtered version of SV<sub>DD</sub>.

- Signals on the SerDes interface are fed from the XV<sub>DD</sub> power plane.

# 22.3 Decoupling Recommendations

Due to large address and data buses, and high operating frequencies, the device can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the device system, and the device itself requires a clean, tightly regulated source of power. Therefore, it is recommended that the system designer place at least one decoupling capacitor at each  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  pin of the device. These decoupling capacitors must receive their power from separate  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $DV_{DD}$ ,  $DV_{DD}$ ,  $DV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $DV_{DD}$ ,  $DV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $DV_{DD}$ ,  $DV_{DD}$ ,  $DV_{DD}$ ,  $DV_{DD}$ ,  $DV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $DV_{DD}$ , DV

These capacitors must have a value of 0.1  $\mu$ F. Only ceramic SMT (surface mount technology) capacitors must be used to minimize lead inductance, preferably 0402 or 0603 sizes. Besides, it is recommended that there be several bulk storage capacitors distributed around the PCB, feeding the V<sub>DD</sub>, TV<sub>DD</sub>, BV<sub>DD</sub>, OV<sub>DD</sub>, GV<sub>DD</sub>, and LV<sub>DD</sub>, planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors must have a low ESR (equivalent series resistance) rating to ensure the quick response time necessary. They must also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors—100–330  $\mu$ F (AVX TPS tantalum or Sanyo OSCON). However, customers must work directly with their power regulator vendor for best values, types and quantity of bulk capacitors.

# 22.4 SerDes Block Power Supply Decoupling Recommendations

The SerDes block requires a clean, tightly regulated source of power ( $SV_{DD}$  and  $XV_{DD}$ ) to ensure low jitter on transmit and reliable recovery of data in the receiver. An appropriate decoupling scheme is outlined below.

Only surface mount technology (SMT) capacitors must be used to minimize inductance. Connections from all capacitors to power and ground must be done with multiple vias to further reduce inductance.

#### System Design Information

The platform PLL ratio and e500 PLL ratio configuration pins are not equipped with these default pull-up devices.

# 22.9 JTAG Configuration Signals

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 63. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions as most have asynchronous behavior and spurious assertion gives unpredictable results.

Boundary-scan testing is enabled through the JTAG interface signals. The TRST signal is optional in the IEEE 1149.1 specification, but it is provided on all processors built on Power Architecture technology. The device requires TRST to be asserted during power-on reset flow to ensure that the JTAG boundary logic does not interfere with normal chip operation. While the TAP controller can be forced to the reset state using only the TCK and TMS signals, generally systems assert TRST during the power-on reset flow. Simply tying TRST to HRESET is not practical because the JTAG interface is also used for accessing the common on-chip processor (COP), which implements the debug interface to the chip.

The COP function of these processors allow a remote computer system (typically, a PC with dedicated hardware and debugging software) to access and control the internal operations of the processor. The COP interface connects primarily through the JTAG port of the processor, with some additional status monitoring signals. The COP port requires the ability to independently assert HRESET or TRST in order to fully control the processor. If the target system has independent reset sources, such as voltage monitors, watchdog timers, power supply failures, or push-button switches, then the COP reset signals must be merged into these signals with logic.

The arrangement shown in Figure 63 allows the COP port to independently assert  $\overline{\text{HRESET}}$  or  $\overline{\text{TRST}}$ , while ensuring that the target can drive  $\overline{\text{HRESET}}$  as well.

The COP interface has a standard header, shown in Figure 62, for connection to the target system, and is based on the 0.025" square-post, 0.100" centered header assembly (often called a Berg header). The connector typically has pin 14 removed as a connector key.

The COP header adds many benefits such as breakpoints, watchpoints, register and memory examination/modification, and other standard debugger features. An inexpensive option can be to leave the COP header unpopulated until needed.

There is no standardized way to number the COP header; so emulator vendors have issued many different pin numbering schemes. Some COP headers are numbered top-to-bottom then left-to-right, while others use left-to-right then top-to-bottom. Still others number the pins counter-clockwise from pin 1 (as with an IC). Regardless of the numbering scheme, the signal placement recommended in Figure 62 is common to all known emulators.

# 22.9.1 Termination of Unused Signals

Freescale recommends the following connections, when the JTAG interface and COP header are not used:

• TRST must be tied to HRESET through a 0 k $\Omega$  isolation resistor so that it is asserted when the system reset signal (HRESET) is asserted, ensuring that the JTAG scan chain is initialized during the power-on reset flow. Freescale recommends that the COP header be designed into the system

System Design Information

# 22.10 Guidelines for High-Speed Interface Termination

This section provides the guidelines for high-speed interface termination when the SerDes interface is entirely unused and when it is partly unused.

# 22.10.1 SerDes Interface Entirely Unused

If the high-speed SerDes interface is not used at all, the unused pin must be terminated as described in this section.

The following pins must be left unconnected (float):

- SD\_TX[7:0]

- <u>SD\_TX</u>[7:0]

- Reserved pins T22, T23, M20, M21

The following pins must be connected to GND:

- SD\_RX[7:0]

- <u>SD\_RX</u>[7:0]

- SD\_REF\_CLK

- SD\_REF\_CLK

## NOTE

It is recommended to power down the unused lane through SRDSCR1[0:7] register (offset =  $0xE_0F08$ ) (This prevents the oscillations and holds the receiver output in a fixed state.) that maps to SERDES lane 0 to lane 7 accordingly.

Pins V28 and M26 must be tied to  $XV_{DD}$ . Pins V27 and M25 must be tied to GND through a 300- $\Omega$  resistor.

In Rev 2.0 silicon, POR configuration pin cfg\_srds\_en on TSEC4\_TXD[2]/TSEC3\_TXD[6] can be used to power down SerDes block.

# 22.10.2 SerDes Interface Partly Unused

If only part of the high-speed SerDes interface pins are used, the remaining high-speed serial I/O pins must be terminated as described in this section.

The following pins must be left unconnected (float) if not used:

- SD\_TX[7:0]

- <u>SD\_TX</u>[7:0]

- Reserved pins: T22, T23, M20, M21

The following pins must be connected to GND if not used:

- SD\_RX[7:0]

- $\overline{\text{SD}_{RX}}[7:0]$

- SD\_REF\_CLK

# 24 Document Revision History

The following table provides a revision history for this hardware specification.

#### Rev. Date Substantive Change(s) Number • Updated Section 21.2, "Thermal for Version 2.1.1, 2.1.2, and 2.1.3 Silicon FC-PBGA with Full Lid and 9 02/2012 Version 3.1.x Silicon with Stamped Lid," with version 3.0 silicon information. Added Figure 56, "Mechanical Dimensions and Bottom Surface Nomenclature of the FC-PBGA with Stamped Lid." • Updated Table 87, "Part Numbering Nomenclature," with version 3.0 silicon information. Removed Note from Section 5.1. "Power-On Ramp Rate". • Changed the Table 10 title to "Power Supply Ramp Rate". • Removed table 11. • Updated the title of Section 21.2, "Thermal for Version 2.1.1, 2.1.2, and 2.1.3 Silicon FC-PBGA with Full Lid and Version 3.1.x Silicon with Stamped Lid" to include Thermal Version 2.1.3 and Version 3.1.x Silicon. Corrected the leaded Solder Ball composition in Table 70, "Package Parameters" • Updated Table 87, "Part Numbering Nomenclature," with Version 3.1.x silicon information. • Updated the Min and Max value of TDO in the valid times row of Table 44, "JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup>" from 4 and 25 to 2 and 10 respectively . 8 04/2011 Added Section 14.1, "GPOUT/GPIN Electrical Characteristics." • Updated Table 71, "MPC8548E Pinout Listing," Table 72, "MPC8547E Pinout Listing," Table 73, "MPC8545E Pinout Listing," and Table 74, "MPC8543E Pinout Listing," to reflect that the TDO signal is not driven during HRSET\* assertion. • Updated Table 87, "Part Numbering Nomenclature" with Ver. 2.1.3 silicon information. In Table 37, "MII Management AC Timing Specifications, modified the fifth row from "MDC to MDIO 7 09/2010 delay tMDKHDX (16 x tptb\_clk x 8) - 3 - (16 x tptb\_clk x 8) + 3" to "MDC to MDIO delay tMDKHDX $(16 \times tCCB \times 8) - 3 - (16 \times tCCB \times 8) + 3."$ Updated Figure 55, "Mechanical Dimensions and Bottom Surface Nomenclature of the HiCTE FC-CBGA and FC-PBGA with Full Lid and figure notes. 6 12/2009 • In Section 5.1, "Power-On Ramp Rate" added explanation that Power-On Ramp Rate is required to avoid falsely triggering ESD circuitry. In Table 13 changed required ramp rate from 545 V/s for MVREF and VDD/XVDD/SVDD to 3500 V/s for MVREF and 4000 V/s for VDD. • In Table 13 deleted ramp rate requirement for XVDD/SVDD. In Table 13 footnote 1 changed voltage range of concern from 0-400 mV to 20-500mV. In Table 13 added footnote 2 explaining that VDD voltage ramp rate is intended to control ramp rate of AVDD pins. 5 10/2009 • In Table 27, "GMII Receive AC Timing Specifications," changed duty cycle specification from 40/60 to 35/75 for RX CLK duty cycle. Updated tMDKHDX in Table 37, "MII Management AC Timing Specifications." • Added a reference to Revision 2.1.2. • Updated Table 55, "MII Management AC Timing Specifications." Added Section 5.1, "Power-On Ramp Rate."

### Table 88. Document Revision History