# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 1.2GHz                                                                |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                                 |

| RAM Controllers                 | DDR, DDR2, SDRAM                                                      |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (4)                                                   |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                      |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | Cryptography, Random Number Generator                                 |

| Package / Case                  | 783-BBGA, FCBGA                                                       |

| Supplier Device Package         | 783-FCBGA (29x29)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8545evuatg |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Performance monitor facility that is similar to, but separate from, the device performance monitor

The e500 defines features that are not implemented on this device. It also generally defines some features that this device implements more specifically. An understanding of these differences can be critical to ensure proper operations.

- 512-Kbyte L2 cache/SRAM

- Flexible configuration.

- Full ECC support on 64-bit boundary in both cache and SRAM modes

- Cache mode supports instruction caching, data caching, or both.

- External masters can force data to be allocated into the cache through programmed memory ranges or special transaction types (stashing).

- 1, 2, or 4 ways can be configured for stashing only.

- Eight-way set-associative cache organization (32-byte cache lines)

- Supports locking entire cache or selected lines. Individual line locks are set and cleared through Book E instructions or by externally mastered transactions.

- Global locking and Flash clearing done through writes to L2 configuration registers

- Instruction and data locks can be Flash cleared separately.

- SRAM features include the following:

- I/O devices access SRAM regions by marking transactions as snoopable (global).

- Regions can reside at any aligned location in the memory map.

- Byte-accessible ECC is protected using read-modify-write transaction accesses for smaller-than-cache-line accesses.

- Address translation and mapping unit (ATMU)

- Eight local access windows define mapping within local 36-bit address space.

- Inbound and outbound ATMUs map to larger external address spaces.

- Three inbound windows plus a configuration window on PCI/PCI-X and PCI Express

- Four inbound windows plus a default window on RapidIO<sup>™</sup>

- Four outbound windows plus default translation for PCI/PCI-X and PCI Express

- Eight outbound windows plus default translation for RapidIO with segmentation and sub-segmentation support

- DDR/DDR2 memory controller

- Programmable timing supporting DDR and DDR2 SDRAM

- 64-bit data interface

- Four banks of memory supported, each up to 4 Gbytes, to a maximum of 16 Gbytes

- DRAM chip configurations from 64 Mbits to 4 Gbits with ×8/×16 data ports

- Full ECC support

- Page mode support

- Up to 16 simultaneous open pages for DDR

#### Overview

- Memory prefetching of PCI read accesses

- Supports posting of processor-to-PCI and PCI-to-memory writes

- PCI 3.3-V compatible

- Selectable hardware-enforced coherency

- Serial RapidIO<sup>™</sup> interface unit

- Supports RapidIO<sup>™</sup> Interconnect Specification, Revision 1.2

- Both  $1 \times$  and  $4 \times$  LP-serial link interfaces

- Long- and short-haul electricals with selectable pre-compensation

- Transmission rates of 1.25, 2.5, and 3.125 Gbaud (data rates of 1.0, 2.0, and 2.5 Gbps) per lane

- Auto detection of 1- and 4-mode operation during port initialization

- Link initialization and synchronization

- Large and small size transport information field support selectable at initialization time

- 34-bit addressing

- Up to 256 bytes data payload

- All transaction flows and priorities

- Atomic set/clr/inc/dec for read-modify-write operations

- Generation of IO\_READ\_HOME and FLUSH with data for accessing cache-coherent data at a remote memory system

- Receiver-controlled flow control

- Error detection, recovery, and time-out for packets and control symbols as required by the RapidIO specification

- Register and register bit extensions as described in part VIII (Error Management) of the RapidIO specification

- Hardware recovery only

- Register support is not required for software-mediated error recovery.

- Accept-all mode of operation for fail-over support

- Support for RapidIO error injection

- Internal LP-serial and application interface-level loopback modes

- Memory and PHY BIST for at-speed production test

- RapidIO-compatible message unit

- 4 Kbytes of payload per message

- Up to sixteen 256-byte segments per message

- Two inbound data message structures within the inbox

- Capable of receiving three letters at any mailbox

- Two outbound data message structures within the outbox

- Capable of sending three letters simultaneously

- Single segment multicast to up to 32 devIDs

- Chaining and direct modes in the outbox

#### Overview

- Single inbound doorbell message structure

- Facility to accept port-write messages

- PCI Express interface

- PCI Express 1.0a compatible

- Supports x8,x4,x2, and x1 link widths

- Auto-detection of number of connected lanes

- Selectable operation as root complex or endpoint

- Both 32- and 64-bit addressing

- 256-byte maximum payload size

- Virtual channel 0 only

- Traffic class 0 only

- Full 64-bit decode with 32-bit wide windows

- Pin multiplexing for the high-speed I/O interfaces supports one of the following configurations:

- 8 PCI Express

- 4 PCI Express and 4 serial RapidIO

- Power management

- Supports power saving modes: doze, nap, and sleep

- Employs dynamic power management, which automatically minimizes power consumption of blocks when they are idle

- System performance monitor

- Supports eight 32-bit counters that count the occurrence of selected events

- Ability to count up to 512 counter-specific events

- Supports 64 reference events that can be counted on any of the eight counters

- Supports duration and quantity threshold counting

- Burstiness feature that permits counting of burst events with a programmable time between bursts

- Triggering and chaining capability

- Ability to generate an interrupt on overflow

- System access port

- Uses JTAG interface and a TAP controller to access entire system memory map

- Supports 32-bit accesses to configuration registers

- Supports cache-line burst accesses to main memory

- Supports large block (4-Kbyte) uploads and downloads

- Supports continuous bit streaming of entire block for fast upload and download

- JTAG boundary scan, designed to comply with IEEE Std. 1149.1<sup>TM</sup>

#### DDR and DDR2 SDRAM

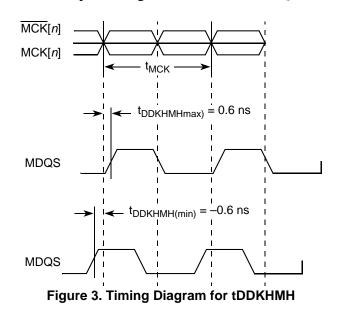

#### Table 19. DDR SDRAM Output AC Timing Specifications (continued)

At recommended operating conditions.

| Parameter         | Symbol <sup>1</sup> | Min  | Мах | Unit | Notes |

|-------------------|---------------------|------|-----|------|-------|

| MDQS epilogue end | t <sub>DDKHME</sub> | -0.6 | 0.6 | ns   | 6     |

Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

- 2. All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

- 3. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS.

- 4. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK[n] clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the MDQS override bits (called WR\_DATA\_DELAY) in the TIMING\_CFG\_2 register. This is typically set to the same delay as in DDR\_SDRAM\_CLK\_CNTL[CLK\_ADJUST]. The timing parameters listed in the table assume that these 2 parameters have been set to the same adjustment value. See the MPC8548E PowerQUICC III Integrated Processor Reference Manual for a description and understanding of the timing modifications enabled by use of these bits.

- Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe must be centered inside of the data eye at the pins of the microprocessor.

- 6. All outputs are referenced to the rising edge of MCK[*n*] at the pins of the microprocessor. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

#### NOTE

For the ADDR/CMD setup and hold specifications in Table 19, it is assumed that the clock control register is set to adjust the memory clocks by 1/2 applied cycle.

Figure 3 shows the DDR SDRAM output timing for the MCK to MDQS skew measurement (t<sub>DDKHMH</sub>).

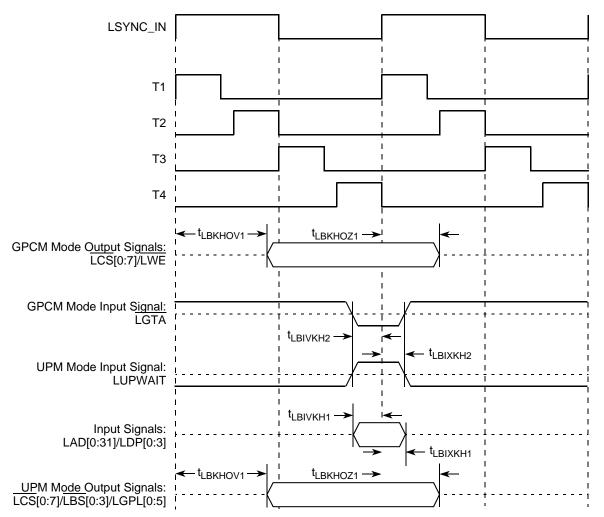

Figure 27. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 8 or 16 (PLL Enabled)

# 16 High-Speed Serial Interfaces (HSSI)

The device features one Serializer/Deserializer (SerDes) interface to be used for high-speed serial interconnect applications. The SerDes interface can be used for PCI Express and/or serial RapidIO data transfers.

This section describes the common portion of SerDes DC electrical specifications, which is the DC requirement for SerDes reference clocks. The SerDes data lane's transmitter and receiver reference circuits are also shown.

## 16.1 Signal Terms Definition

The SerDes utilizes differential signaling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals.

Figure 38 shows how the signals are defined. For illustration purpose, only one SerDes lane is used for the description. The figure shows a waveform for either a transmitter output (SD\_TX and  $\overline{SD}_TX$ ) or a receiver input (SD\_RX and  $\overline{SD}_RX$ ). Each signal swings between A volts and B volts where A > B.

Using this waveform, the definitions are as follows. To simplify the illustration, the following definitions assume that the SerDes transmitter and receiver operate in a fully symmetrical differential signaling environment.

• Single-ended swing

The transmitter output signals and the receiver input signals SD\_TX,  $\overline{SD}_TX$ ,  $\overline{SD}_RX$  and  $\overline{SD}_RX$  each have a peak-to-peak swing of A – B volts. This is also referred as each signal wire's single-ended swing.

- Differential output voltage,  $V_{OD}$  (or differential output swing): The differential output voltage (or swing) of the transmitter,  $V_{OD}$ , is defined as the difference of the two complimentary output voltages:  $V_{SD_TX} - V_{\overline{SD_TX}}$ . The  $V_{OD}$  value can be either positive or negative.

- Differential input voltage, V<sub>ID</sub> (or differential input swing): The differential input voltage (or swing) of the receiver, V<sub>ID</sub>, is defined as the difference of the two complimentary input voltages: V<sub>SD\_RX</sub> – V<sub>SD\_RX</sub>. The V<sub>ID</sub> value can be either positive or negative.

- Differential peak voltage,  $V_{DIFFp}$ The peak value of the differential transmitter output signal or the differential receiver input signal is defined as differential peak voltage,  $V_{DIFFp} = |A - B|$  volts.

- Differential peak-to-peak,  $V_{DIFFp-p}$ Because the differential output signal of the transmitter and the differential input signal of the receiver each range from A – B to –(A – B) volts, the peak-to-peak value of the differential transmitter output signal or the differential receiver input signal is defined as differential peak-to-peak voltage,  $V_{DIFFp-p} = 2 \times V_{DIFFp} = 2 \times |(A - B)|$  volts, which is twice of differential swing in amplitude, or twice of the differential peak. For example, the output differential peak-to-peak voltage can also be calculated as  $V_{TX-DIFFp-p} = 2 \times |V_{OD}|$ .

- Common mode voltage,  $V_{cm}$ The common mode voltage is equal to one half of the sum of the voltages between each conductor

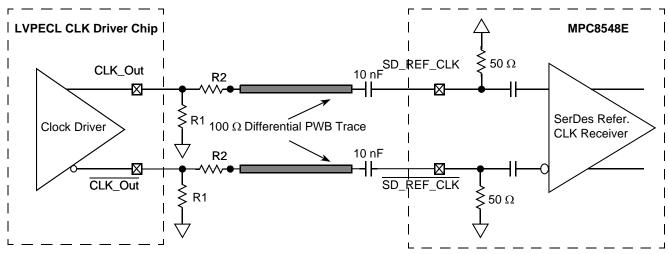

to AC-coupling. Its value could be ranged from 140 to 240  $\Omega$  depending on the clock driver vendor's requirement. R2 is used together with the SerDes reference clock receiver's 50- $\Omega$  termination resistor to attenuate the LVPECL output's differential peak level such that it meets the SerDes reference clock's differential input amplitude requirement (between 200 and 800 mV differential peak). For example, if the LVPECL output's differential peak is 900 mV and the desired SerDes reference clock input amplitude is selected as 600 mV, the attenuation factor is 0.67, which requires R2 = 25  $\Omega$ . Consult a clock driver chip manufacturer to verify whether this connection scheme is compatible with a particular clock driver chip.

Figure 45. AC-Coupled Differential Connection with LVPECL Clock Driver (Reference Only)

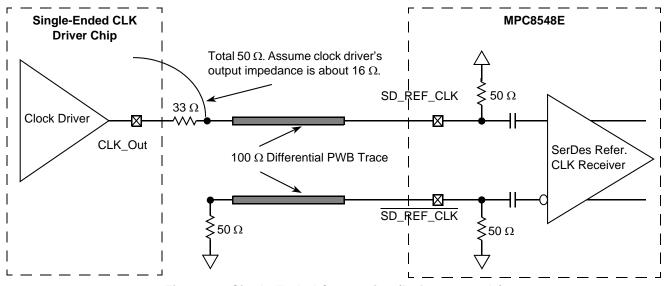

Figure 46 shows the SerDes reference clock connection reference circuits for a single-ended clock driver. It assumes the DC levels of the clock driver are compatible with the SerDes reference clock input's DC requirement.

Figure 46. Single-Ended Connection (Reference Only)

components are included in this requirement. The reference impedance for return loss measurements is  $100-\Omega$  resistive for differential return loss and  $25-\Omega$  resistive for common mode.

| Characteristic                                     | Symbol          | Range<br>Symbol |                   | Unit   | Notes                                                        |  |

|----------------------------------------------------|-----------------|-----------------|-------------------|--------|--------------------------------------------------------------|--|

| Characteristic                                     | Symbol          | Min             | Max               | Unit   | NOICS                                                        |  |

| Differential input voltage                         | V <sub>IN</sub> | 200             | 1600              | mVp-p  | Measured at receiver                                         |  |

| Deterministic jitter tolerance                     | J <sub>D</sub>  | 0.37            | —                 | UI p-p | Measured at receiver                                         |  |

| Combined deterministic and random jitter tolerance | J <sub>DR</sub> | 0.55            | —                 | UI p-p | Measured at receiver                                         |  |

| Total jitter tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65            | _                 | UI p-p | Measured at receiver                                         |  |

| Multiple input skew                                | S <sub>MI</sub> | —               | 24                | ns     | Skew at the receiver input between lanes of a multilane link |  |

| Bit error rate                                     | BER             | —               | 10 <sup>-12</sup> | —      | —                                                            |  |

| Unit interval                                      | UI              | 800             | 800               | ps     | ±100 ppm                                                     |  |

#### Note:

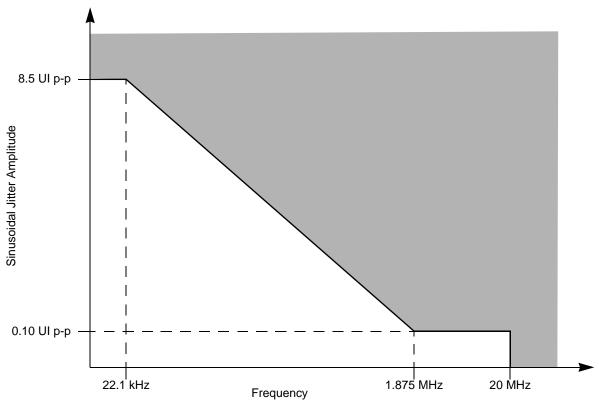

1. Total jitter is composed of three components, deterministic jitter, random jitter, and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 53. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk, and other variable system effects.

#### Table 67. Receiver AC Timing Specifications—2.5 GBaud

| Characteristic                                     | Symbol          | Range |                   | Unit   | Notes                                                        |

|----------------------------------------------------|-----------------|-------|-------------------|--------|--------------------------------------------------------------|

| Characteristic                                     | Symbol          | Min   | Max               | Unit   | NULES                                                        |

| Differential input voltage                         | V <sub>IN</sub> | 200   | 1600              | mVp-p  | Measured at receiver                                         |

| Deterministic jitter tolerance                     | J <sub>D</sub>  | 0.37  | _                 | UI p-p | Measured at receiver                                         |

| Combined deterministic and random jitter tolerance | J <sub>DR</sub> | 0.55  | —                 | UI p-p | Measured at receiver                                         |

| Total jitter tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65  | —                 | UI p-p | Measured at receiver                                         |

| Multiple input skew                                | S <sub>MI</sub> | _     | 24                | ns     | Skew at the receiver input between lanes of a multilane link |

| Bit error rate                                     | BER             | _     | 10 <sup>-12</sup> |        | —                                                            |

| Unit interval                                      | UI              | 400   | 400               | ps     | ±100 ppm                                                     |

#### Note:

1. Total jitter is composed of three components, deterministic jitter, random jitter, and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 53. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk, and other variable system effects.

| Characteristic                                     | Range Symbol    |      | Unit              | Notes  |                                                              |

|----------------------------------------------------|-----------------|------|-------------------|--------|--------------------------------------------------------------|

| Characteristic                                     | Symbol          | Min  | Max               | Onit   | NOICES                                                       |

| Differential input voltage                         | V <sub>IN</sub> | 200  | 1600              | mVp-p  | Measured at receiver                                         |

| Deterministic jitter tolerance                     | J <sub>D</sub>  | 0.37 | —                 | UI p-p | Measured at receiver                                         |

| Combined deterministic and random jitter tolerance | J <sub>DR</sub> | 0.55 | —                 | UI p-p | Measured at receiver                                         |

| Total jitter tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65 | _                 | UI p-p | Measured at receiver                                         |

| Multiple input skew                                | S <sub>MI</sub> | _    | 22                | ns     | Skew at the receiver input between lanes of a multilane link |

| Bit error rate                                     | BER             | _    | 10 <sup>-12</sup> |        | —                                                            |

| Unit interval                                      | UI              | 320  | 320               | ps     | ±100 ppm                                                     |

| Table 68. Receiver | <b>AC Timing</b> | Specifications- | -3.125 GBaud |

|--------------------|------------------|-----------------|--------------|

|--------------------|------------------|-----------------|--------------|

#### Note:

1. Total jitter is composed of three components, deterministic jitter, random jitter and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 53. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk and other variable system effects.

Figure 53. Single Frequency Sinusoidal Jitter Limits

## **19 Package Description**

This section details package parameters, pin assignments, and dimensions.

## **19.1 Package Parameters**

The package parameters for both the HiCTE FC-CBGA and FC-PBGA are provided in Table 70.

| Parameter               | CBGA <sup>1</sup> | PBGA <sup>2</sup> |

|-------------------------|-------------------|-------------------|

| Package outline         | 29 mm × 29 mm     | 29 mm × 29 mm     |

| Interconnects           | 783               | 783               |

| Ball pitch              | 1 mm              | 1 mm              |

| Ball diameter (typical) | 0.6 mm            | 0.6 mm            |

| Solder ball             | 63% Sn            | 63% Sn            |

|                         | 37% Pb            | 37% Pb            |

|                         | 0% Ag             | 0% Ag             |

| Solder ball (lead-free) | 95% Sn            | 96.5% Sn          |

|                         | 4.5% Ag           | 3.5% Ag           |

|                         | 0.5% Cu           |                   |

Table 70. Package Parameters

Notes:

1. The HiCTE FC-CBGA package is available on only Version 2.0 of the device.

2. The FC-PBGA package is available on only versions 2.1.1 and 2.1.2, and 3.0 of the device.

#### Package Description

| Signal                   | Package Pin Number                                                                                                                                                      | Pin Type | Power<br>Supply  | Notes        |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|--------------|

|                          | Local Bus Controller Interface                                                                                                                                          |          |                  |              |

| LAD[0:31]                | E27, B20, H19, F25, A20, C19, E28, J23, A25,<br>K22, B28, D27, D19, J22, K20, D28, D25, B25,<br>E22, F22, F21, C25, C22, B23, F20, A23, A22,<br>E19, A21, D21, F19, B21 | I/O      | BV <sub>DD</sub> | _            |

| LDP[0:3]                 | K21, C28, B26, B22                                                                                                                                                      | I/O      | BV <sub>DD</sub> | —            |

| LA[27]                   | H21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LA[28:31]                | H20, A27, D26, A28                                                                                                                                                      | 0        | BV <sub>DD</sub> | 5, 7, 9      |

| LCS[0:4]                 | J25, C20, J24, G26, A26                                                                                                                                                 | 0        | BV <sub>DD</sub> | —            |

| LCS5/DMA_DREQ2           | D23                                                                                                                                                                     | I/O      | BV <sub>DD</sub> | 1            |

| LCS6/DMA_DACK2           | G20                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 1            |

| LCS7/DMA_DDONE2          | E21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 1            |

| LWE0/LBS0/LSDDQM[0]      | G25                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LWE1/LBS1/LSDDQM[1]      | C23                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LWE2/LBS2/LSDDQM[2]      | J21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LWE3/LBS3/LSDDQM[3]      | A24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LALE                     | H24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9      |

| LBCTL                    | G27                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9      |

| LGPL0/LSDA10             | F23                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LGPL1/LSDWE              | G22                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LGPL2/LOE/LSDRAS         | B27                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9      |

| LGPL3/LSDCAS             | F24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LGPL4/LGTA/LUPWAIT/LPBSE | H23                                                                                                                                                                     | I/O      | BV <sub>DD</sub> | —            |

| LGPL5                    | E26                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LCKE                     | E24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | —            |

| LCLK[0:2]                | E23, D24, H22                                                                                                                                                           | 0        | BV <sub>DD</sub> | —            |

| LSYNC_IN                 | F27                                                                                                                                                                     | I        | BV <sub>DD</sub> | —            |

| LSYNC_OUT                | F28                                                                                                                                                                     | 0        | BV <sub>DD</sub> | —            |

|                          | DMA                                                                                                                                                                     |          |                  |              |

| DMA_DACK[0:1]            | AD3, AE1                                                                                                                                                                | 0        | OV <sub>DD</sub> | 5, 9,<br>107 |

| DMA_DREQ[0:1]            | AD4, AE2                                                                                                                                                                | I        | OV <sub>DD</sub> | _            |

| DMA_DDONE[0:1]           | AD2, AD1                                                                                                                                                                | 0        | OV <sub>DD</sub> | _            |

|                          | Programmable Interrupt Controller                                                                                                                                       |          |                  |              |

| UDE                      | AH16                                                                                                                                                                    | I        | OV <sub>DD</sub> | _            |

| MCP                      | AG19                                                                                                                                                                    | l        | OV <sub>DD</sub> |              |

| Signal           | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin Type                                           | Power<br>Supply  | Notes        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------|--------------|

| TDO              | AF28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                  | $OV_{DD}$        | _            |

| TMS              | AH27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | $OV_{DD}$        | 12           |

| TRST             | AH23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | $OV_{DD}$        | 12           |

|                  | DFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                    |                  |              |

| L1_TSTCLK        | AC25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | $OV_{DD}$        | 25           |

| L2_TSTCLK        | AE22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | $OV_{DD}$        | 25           |

| LSSD_MODE        | AH20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ļ                                                  | $OV_{DD}$        | 25           |

| TEST_SEL         | AH14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | $OV_{DD}$        | 25           |

|                  | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                    |                  | 1            |

| THERM0           | AG1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                  | —                | 14           |

| THERM1           | AH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                  | —                | 14           |

|                  | Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                    |                  | 1            |

| ASLEEP           | AH18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                  | OV <sub>DD</sub> | 9, 19,<br>29 |

|                  | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                    |                  |              |

| GND              | <ul> <li>A11, B7, B24, C1, C3, C5, C12, C15, C26, D8,<br/>D11, D16, D20, D22, E1, E5, E9, E12, E15, E17,<br/>F4, F26, G12, G15, G18, G21, G24, H2, H6, H8,<br/>H28, J4, J12, J15, J17, J27, K7, K9, K11, K27,<br/>L3, L5, L12, L16, N11, N13, N15, N17, N19, P4,<br/>P9, P12, P14, P16, P18, R11, R13, R15, R17,<br/>R19, T4, T12, T14, T16, T18, U8, U11, U13,<br/>U15, U17, U19, V4, V12, V18, W6, W19, Y4, Y9,<br/>Y11, Y19, AA6, AA14, AA17, AA22, AA23, AB4,<br/>AC2, AC11, AC19, AC26, AD5, AD9, AD22,<br/>AE3, AE14, AF6, AF10, AF13, AG8, AG27,<br/>K28, L24, L26, N24, N27, P25, R28, T24, T26,<br/>U24, V25, W28, Y24, Y26, AA24, AA27, AB25,<br/>AC28, L21, L23, N22, P20, R23, T21, U22, V20,<br/>W23, Y21, U27</li> </ul> |                                                    |                  |              |

| OV <sub>DD</sub> | V16, W11, W14, Y18, AA13, AA21, AB11,<br>AB17, AB24, AC4, AC9, AC21, AD6, AD13,<br>AD17, AD19, AE10, AE8, AE24, AF4, AF12,<br>AF22, AF27, AG26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Power for PCI<br>and other<br>standards<br>(3.3 V) | OV <sub>DD</sub> | _            |

| LV <sub>DD</sub> | N8, R7, T9, U6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Power for<br>TSEC1 and<br>TSEC2<br>(2.5 V, 3.3 V)  | LV <sub>DD</sub> |              |

| TV <sub>DD</sub> | W9, Y6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Power for<br>TSEC3 and<br>TSEC4<br>(2,5 V, 3.3 V)  | TV <sub>DD</sub> |              |

# 20 Clocking

This section describes the PLL configuration of the device. Note that the platform clock is identical to the core complex bus (CCB) clock.

## 20.1 Clock Ranges

Table 75 through Table 77 provide the clocking specifications for the processor cores and Table 78, through Table 80 provide the clocking specifications for the memory bus.

| Characteristic                |     | Maximum Processor Core Frequency |               |      |     |      |       |      |

|-------------------------------|-----|----------------------------------|---------------|------|-----|------|-------|------|

|                               |     | MHz                              | 1200 MHz 1333 |      | MHz | Unit | Notes |      |

|                               | Min | Max                              | Min           | Мах  | Min | Max  |       |      |

| e500 core processor frequency | 800 | 1000                             | 800           | 1200 | 800 | 1333 | MHz   | 1, 2 |

Table 75. Processor Core Clocking Specifications (MPC8548E and MPC8547E)

Notes:

Caution: The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

2.)The minimum e500 core frequency is based on the minimum platform frequency of 333 MHz.

#### Table 76. Processor Core Clocking Specifications (MPC8545E)

|                               | Maximum Processor Core Frequency |     |      |      |              |      |      |       |

|-------------------------------|----------------------------------|-----|------|------|--------------|------|------|-------|

| Characteristic                | 800                              | MHz | 1000 | MHz  | MHz 1200 MHz |      | Unit | Notes |

|                               | Min                              | Max | Min  | Max  | Min          | Max  |      |       |

| e500 core processor frequency | 800                              | 800 | 800  | 1000 | 800          | 1200 | MHz  | 1, 2  |

Notes:

1. **Caution:** The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

2.)The minimum e500 core frequency is based on the minimum platform frequency of 333 MHz.

| Characteristic         | Maximum Process<br>800, 10 | Unit | Notes |      |

|------------------------|----------------------------|------|-------|------|

|                        | Min N                      | Мах  |       |      |

| Memory bus clock speed | 166 200                    |      | MHz   | 1, 2 |

#### Table 80. Memory Bus Clocking Specifications (MPC8543E)

Notes:

1. **Caution:** The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

2. The memory bus speed is half of the DDR/DDR2 data rate, hence, half of the platform clock frequency.

## 20.2 CCB/SYSCLK PLL Ratio

The CCB clock is the clock that drives the e500 core complex bus (CCB), and is also called the platform clock. The frequency of the CCB is set using the following reset signals, as shown in Table 81:

- SYSCLK input signal

- Binary value on LA[28:31] at power up

Note that there is no default for this PLL ratio; these signals must be pulled to the desired values. Also note that the DDR data rate is the determining factor in selecting the CCB bus frequency, since the CCB frequency must equal the DDR data rate.

For specifications on the PCI\_CLK, see the PCI 2.2 Specification.

| Binary Value of LA[28:31] Signals | CCB:SYSCLK Ratio | Binary Value of LA[28:31] Signals | CCB:SYSCLK Ratio |

|-----------------------------------|------------------|-----------------------------------|------------------|

| 0000                              | 16:1             | 1000                              | 8:1              |

| 0001                              | Reserved         | 1001                              | 9:1              |

| 0010                              | 2:1              | 1010                              | 10:1             |

| 0011                              | 3:1              | 1011                              | Reserved         |

| 0100                              | 4:1              | 1100                              | 12:1             |

| 0101                              | 5:1              | 1101                              | 20:1             |

| 0110                              | 6:1              | 1110                              | Reserved         |

| 0111                              | Reserved         | 1111                              | Reserved         |

#### Table 81. CCB Clock Ratio

# 21 Thermal

This section describes the thermal specifications of the device.

## 21.1 Thermal for Version 2.0 Silicon HiCTE FC-CBGA with Full Lid

This section describes the thermal specifications for the HiCTE FC-CBGA package for revision 2.0 silicon.

This table shows the package thermal characteristics.

| Characteristic                               | JEDEC Board             | Symbol                | Value | Unit | Notes |

|----------------------------------------------|-------------------------|-----------------------|-------|------|-------|

| Die junction-to-ambient (natural convection) | Single-layer board (1s) | $R_{	extsf{	heta}JA}$ | 17    | °C/W | 1, 2  |

| Die junction-to-ambient (natural convection) | Four-layer board (2s2p) | $R_{	ext{	heta}JA}$   | 12    | °C/W | 1, 2  |

| Die junction-to-ambient (200 ft/min)         | Single-layer board (1s) | $R_{	ext{	heta}JA}$   | 11    | °C/W | 1, 2  |

| Die junction-to-ambient (200 ft/min)         | Four-layer board (2s2p) | $R_{	ext{	heta}JA}$   | 8     | °C/W | 1, 2  |

| Die junction-to-board                        | N/A                     | $R_{\thetaJB}$        | 3     | °C/W | 3     |

| Die junction-to-case                         | N/A                     | $R_{	ext{	heta}JC}$   | 0.8   | °C/W | 4     |

Table 84. Package Thermal Characteristics for HiCTE FC-CBGA

Notes:

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, airflow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-6 with the board (JESD51-7) horizontal.

- 3. Thermal resistance between the die and the printed-circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 4. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1). The cold plate temperature is used for the case temperature, measured value includes the thermal resistance of the interface layer.

# 21.2 Thermal for Version 2.1.1, 2.1.2, and 2.1.3 Silicon FC-PBGA with Full Lid and Version 3.1.x Silicon with Stamped Lid

This section describes the thermal specifications for the FC-PBGA package for revision 2.1.1, 2.1.2, and 3.0 silicon.

This table shows the package thermal characteristics.

| Table 85. Package Thermal | <b>Characteristics for FC-PBGA</b> |

|---------------------------|------------------------------------|

|---------------------------|------------------------------------|

| Characteristic                               | JEDEC Board             | Symbol                | Value | Unit | Notes |

|----------------------------------------------|-------------------------|-----------------------|-------|------|-------|

| Die junction-to-ambient (natural convection) | Single-layer board (1s) | $R_{	extsf{	heta}JA}$ | 18    | °C/W | 1, 2  |

| Die junction-to-ambient (natural convection) | Four-layer board (2s2p) | $R_{	extsf{	heta}JA}$ | 13    | °C/W | 1, 2  |

| Die junction-to-ambient (200 ft/min)         | Single-layer board (1s) | $R_{	extsf{	heta}JA}$ | 13    | °C/W | 1, 2  |

| Die junction-to-ambient (200 ft/min)         | Four-layer board (2s2p) | $R_{	extsf{	heta}JA}$ | 9     | °C/W | 1, 2  |

| Characteristic        | JEDEC Board | Symbol                | Value | Unit | Notes |

|-----------------------|-------------|-----------------------|-------|------|-------|

| Die junction-to-board | N/A         | $R_{	extsf{	heta}JB}$ | 5     | °C/W | 3     |

| Die junction-to-case  | N/A         | $R_{	ext{	heta}JC}$   | 0.8   | °C/W | 4     |

Table 85. Package Thermal Characteristics for FC-PBGA (continued)

Notes:

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, airflow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-6 with the board (JESD51-7) horizontal.

- 3. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 4. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1). The cold plate temperature is used for the case temperature, measured value includes the thermal resistance of the interface layer.

## 21.3 Heat Sink Solution

Every system application has different conditions that the thermal management solution must solve. As such, providing a recommended heat sink has not been found to be very useful. When a heat sink is chosen, give special consideration to the mounting technique. Mounting the heat sink to the printed-circuit board is the recommended procedure using a maximum of 10 lbs force (45 Newtons) perpendicular to the package and board. Clipping the heat sink to the package is not recommended.

# 22 System Design Information

This section provides electrical design recommendations for successful application of the device.

## 22.1 System Clocking

This device includes five PLLs, as follows:

- 1. The platform PLL generates the platform clock from the externally supplied SYSCLK input. The frequency ratio between the platform and SYSCLK is selected using the platform PLL ratio configuration bits as described in Section 20.2, "CCB/SYSCLK PLL Ratio."

- 2. The e500 core PLL generates the core clock as a slave to the platform clock. The frequency ratio between the e500 core clock and the platform clock is selected using the e500 PLL ratio configuration bits as described in Section 20.3, "e500 Core PLL Ratio."

- 3. The PCI PLL generates the clocking for the PCI bus.

- 4. The local bus PLL generates the clock for the local bus.

- 5. There is a PLL for the SerDes block.

## 22.2 PLL Power Supply Filtering

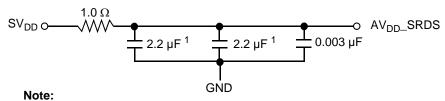

Each of the PLLs listed above is provided with power through independent power supply pins (AV<sub>DD</sub>\_PLAT, AV<sub>DD</sub>\_CORE, AV<sub>DD</sub>\_PCI, AV<sub>DD</sub>\_LBIU, and AV<sub>DD</sub>\_SRDS, respectively). The AV<sub>DD</sub>

the ground plane. Use ceramic chip capacitors with the highest possible self-resonant frequency. All traces must be kept short, wide and direct.

1. An 0805 sized capacitor is recommended for system initial bring-up.

#### Figure 60. SerDes PLL Power Supply Filter

Note the following:

- AV<sub>DD</sub>\_SRDS must be a filtered version of SV<sub>DD</sub>.

- Signals on the SerDes interface are fed from the XV<sub>DD</sub> power plane.

## 22.3 Decoupling Recommendations

Due to large address and data buses, and high operating frequencies, the device can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the device system, and the device itself requires a clean, tightly regulated source of power. Therefore, it is recommended that the system designer place at least one decoupling capacitor at each  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  pin of the device. These decoupling capacitors must receive their power from separate  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $DV_{DD}$ ,  $DV_{DD}$ ,  $DV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $DV_{DD}$ ,  $DV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $DV_{DD}$ ,  $DV_{DD}$ ,  $DV_{DD}$ ,  $DV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $DV_{DD}$ , DV

These capacitors must have a value of 0.1  $\mu$ F. Only ceramic SMT (surface mount technology) capacitors must be used to minimize lead inductance, preferably 0402 or 0603 sizes. Besides, it is recommended that there be several bulk storage capacitors distributed around the PCB, feeding the V<sub>DD</sub>, TV<sub>DD</sub>, BV<sub>DD</sub>, OV<sub>DD</sub>, GV<sub>DD</sub>, and LV<sub>DD</sub>, planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors must have a low ESR (equivalent series resistance) rating to ensure the quick response time necessary. They must also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors—100–330  $\mu$ F (AVX TPS tantalum or Sanyo OSCON). However, customers must work directly with their power regulator vendor for best values, types and quantity of bulk capacitors.

## 22.4 SerDes Block Power Supply Decoupling Recommendations

The SerDes block requires a clean, tightly regulated source of power ( $SV_{DD}$  and  $XV_{DD}$ ) to ensure low jitter on transmit and reliable recovery of data in the receiver. An appropriate decoupling scheme is outlined below.

Only surface mount technology (SMT) capacitors must be used to minimize inductance. Connections from all capacitors to power and ground must be done with multiple vias to further reduce inductance.

#### System Design Information

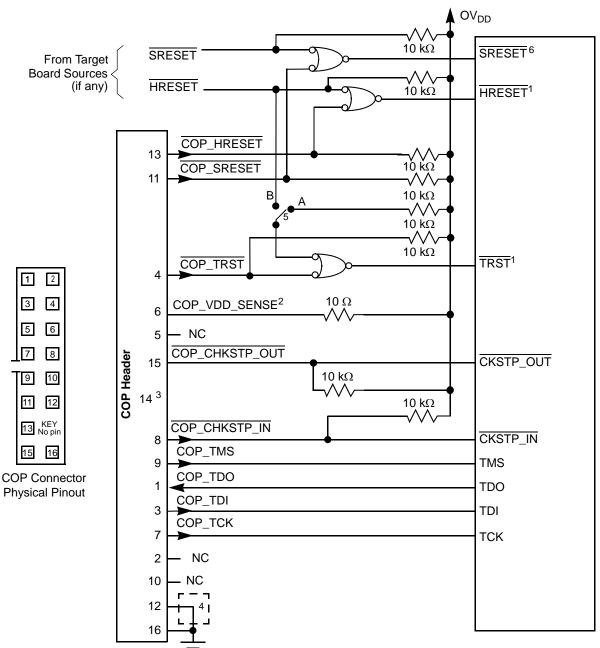

#### Notes:

- 1. The COP port and target board must be able to independently assert HRESET and TRST to the processor in order to fully control the processor as shown here.

- 2. Populate this with a 10– $\Omega$  resistor for short-circuit/current-limiting protection.

- 3. The KEY location (pin 14) is not physically present on the COP header.

- 4. Although pin 12 is defined as a No-Connect, some debug tools may use pin 12 as an additional GND pin for improved signal integrity.

- This switch is included as a precaution for BSDL testing. The switch must be closed to position A during BSDL testing to avoid accidentally asserting the TRST line. If BSDL testing is not being performed, this switch must be closed to position B.

- 6. Asserting SRESET causes a machine check interrupt to the e500 core.

#### Figure 63. JTAG Interface Connection

System Design Information

## 22.10 Guidelines for High-Speed Interface Termination

This section provides the guidelines for high-speed interface termination when the SerDes interface is entirely unused and when it is partly unused.

## 22.10.1 SerDes Interface Entirely Unused

If the high-speed SerDes interface is not used at all, the unused pin must be terminated as described in this section.

The following pins must be left unconnected (float):

- SD\_TX[7:0]

- <u>SD\_TX</u>[7:0]

- Reserved pins T22, T23, M20, M21

The following pins must be connected to GND:

- SD\_RX[7:0]

- <u>SD\_RX</u>[7:0]

- SD\_REF\_CLK

- SD\_REF\_CLK

#### NOTE

It is recommended to power down the unused lane through SRDSCR1[0:7] register (offset =  $0xE_0F08$ ) (This prevents the oscillations and holds the receiver output in a fixed state.) that maps to SERDES lane 0 to lane 7 accordingly.

Pins V28 and M26 must be tied to  $XV_{DD}$ . Pins V27 and M25 must be tied to GND through a 300- $\Omega$  resistor.

In Rev 2.0 silicon, POR configuration pin cfg\_srds\_en on TSEC4\_TXD[2]/TSEC3\_TXD[6] can be used to power down SerDes block.

## 22.10.2 SerDes Interface Partly Unused

If only part of the high-speed SerDes interface pins are used, the remaining high-speed serial I/O pins must be terminated as described in this section.

The following pins must be left unconnected (float) if not used:

- SD\_TX[7:0]

- <u>SD\_TX</u>[7:0]

- Reserved pins: T22, T23, M20, M21

The following pins must be connected to GND if not used:

- SD\_RX[7:0]

- $\overline{\text{SD}_{RX}}[7:0]$

- SD\_REF\_CLK

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4              | 04/2009 | <ul> <li>In Table 1, "Absolute Maximum Ratings <sup>1</sup>," and in Table 2, "Recommended Operating Conditions," moved text, "MII management voltage" from LV<sub>DD</sub>/TV<sub>DD</sub> to OV<sub>DD</sub>, added "Ethernet management" to OVDD row of input voltage section.</li> <li>In Table 5, "SYSCLK AC Timing Specifications," added notes 7 and 8 to SYSCLK frequency and cycle time.</li> <li>In Table 36, "MII Management DC Electrical Characteristics," changed all instances of LV<sub>DD</sub>/OV<sub>DD</sub> to OV<sub>DD</sub>.</li> <li>Modified Section 16, "High-Speed Serial Interfaces (HSSI)," to reflect that there is only one SerDes.</li> <li>Modified DDR clk rate min from 133 to 166 MHz.</li> <li>Modified note in Table 75, "Processor Core Clocking Specifications (MPC8548E and MPC8547E), "."</li> <li>In Table 56, "Differential Transmitter (TX) Output Specifications," modified equations in Comments column, and changed all instances of "LO" to "L0." Also added note 8.</li> <li>In Table 57, "Differential Receiver (RX) Input Specifications," modified equations in Comments column, and in note 3, changed "TRX-EYE-MEDIAN-to-MAX-JITTER," to "T<sub>RX-EYE-MEDIAN-to-MAX-JITTER</sub>."</li> <li>Modified Table 83, "Frequency Options of SYSCLK with Respect to Memory Bus Speeds."</li> <li>Added a note on Section 4.1, "System Clock Timing," to limit the SYSCLK to 100 MHz if the core frequency is less than 1200 MHz</li> <li>In Table 71, "MPC8543E Pinout ListingTable 72, "MPC8547E Pinout ListingTable 73, "MPC8545E Pinout ListingTable 74, "MPC8543E Pinout Listing," added note 5 to LA[28:31].</li> <li>Added note to Table 83, "Frequency Options of SYSCLK with Respect to Memory Bus Speeds."</li> </ul>                                                                                                 |

| 3              | 01/2009 | <ul> <li>[Section 4.6, "Platform Frequency Requirements for PCI-Express and Serial RapidIO." Changed minimum frequency equation to be 527 MHz for PCI x8.</li> <li>In Table 5, added note 7.</li> <li>Section 4.5, "Platform to FIFO Restrictions." Changed platform clock frequency to 4.2.</li> <li>Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1Gb Mbps)—GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics." Added MII after GMII and add 'or 2.5 V' after 3.3 V.</li> <li>In Table 23, modified table title to include GMII, MII, RMII, and TBI.</li> <li>In Table 24 and Table 25, changed clock period minimum to 5.3.</li> <li>In Table 26, Table 27, Table 28, Table 29, and Table 30, removed subtitle from table title.</li> <li>In Table 30 and Figure 15, changed all instances of PMA to TSEC<i>n</i>.</li> <li>In Table 34, Table 35, Figure 18, and Figure 20, changed all instances of REF_CLK to TSEC<i>n</i>_TX_CLK.</li> <li>In Table 36, changed all instances of OV<sub>DD</sub> to LV<sub>DD</sub>/TV<sub>DD</sub>.</li> <li>In Table 36, changed all instances of OV<sub>DD</sub> to LV<sub>DD</sub>/TV<sub>DD</sub>.</li> <li>In Table 37, "MII Management AC Timing Specifications," changed MDC minimum clock pulse width high from 32 to 48 ns.</li> <li>Added new section, Section 16, "High-Speed Serial Interfaces (HSSI)."</li> <li>Section 16.1, "DC Requirements for PCI Express SD_REF_CLK and SD_REF_CLK." Added new paragraph.</li> <li>Section 17.1, "DC Requirements for Serial RapidIO SD_REF_CLK and SD_REF_CLK." Added new paragraph.</li> <li>Added information to Figure 63, both in figure and in note.</li> <li>Section 22.3, "Decoupling Recommendations." Modified the recommendation.</li> <li>Table 87, "Part Numbering Nomenclature." In Silicon Version column added Ver. 2.1.2.</li> </ul> |

#### Table 88. Document Revision History (continued)