# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                             |

|---------------------------------|----------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                         |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                       |

| Speed                           | 1.2GHz                                                               |

| Co-Processors/DSP               | Signal Processing; SPE                                               |

| RAM Controllers                 | DDR, DDR2, SDRAM                                                     |

| Graphics Acceleration           | No                                                                   |

| Display & Interface Controllers | -                                                                    |

| Ethernet                        | 10/100/1000Mbps (4)                                                  |

| SATA                            | -                                                                    |

| USB                             | -                                                                    |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                     |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                     |

| Security Features               | -                                                                    |

| Package / Case                  | 783-BBGA, FCBGA                                                      |

| Supplier Device Package         | 783-FCBGA (29x29)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8545vuatg |

|                                 |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Overview

- AESU-Advanced Encryption Standard unit

- Implements the Rijndael symmetric key cipher

- ECB, CBC, CTR, and CCM modes

- 128-, 192-, and 256-bit key lengths

- AFEU—ARC four execution unit

- Implements a stream cipher compatible with the RC4 algorithm

- 40- to 128-bit programmable key

- MDEU—message digest execution unit

- SHA with 160- or 256-bit message digest

- MD5 with 128-bit message digest

- HMAC with either algorithm

- KEU—Kasumi execution unit

- Implements F8 algorithm for encryption and F9 algorithm for integrity checking

- Also supports A5/3 and GEA-3 algorithms

- RNG—random number generator

- XOR engine for parity checking in RAID storage applications

- Dual I<sup>2</sup>C controllers

- Two-wire interface

- Multiple master support

- Master or slave  $I^2C$  mode support

- On-chip digital filtering rejects spikes on the bus

- Boot sequencer

- Optionally loads configuration data from serial ROM at reset via the  $I^2C$  interface

- Can be used to initialize configuration registers and/or memory

- Supports extended I<sup>2</sup>C addressing mode

- Data integrity checked with preamble signature and CRC

- DUART

- Two 4-wire interfaces (SIN, SOUT,  $\overline{\text{RTS}}$ ,  $\overline{\text{CTS}}$ )

- Programming model compatible with the original 16450 UART and the PC16550D

- Local bus controller (LBC)

- Multiplexed 32-bit address and data bus operating at up to 133 MHz

- Eight chip selects support eight external slaves

- Up to eight-beat burst transfers

- The 32-, 16-, and 8-bit port sizes are controlled by an on-chip memory controller.

- Three protocol engines available on a per chip select basis:

- General-purpose chip select machine (GPCM)

- Three user programmable machines (UPMs)

### NOTE

From a system standpoint, if any of the I/O power supplies ramp prior to the  $V_{DD}$  core supply, the I/Os associated with that I/O supply may drive a logic one or zero during power-up, and extra current may be drawn by the device.

# 4.5 Platform to FIFO Restrictions

Note the following FIFO maximum speed restrictions based on platform speed.

For FIFO GMII mode:

FIFO TX/RX clock frequency ≤ platform clock frequency/4.2

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency must be no more than 127 MHz.

For FIFO encoded mode:

FIFO TX/RX clock frequency  $\leq$  platform clock frequency/4.2

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency must be no more than 167 MHz.

# 4.6 Platform Frequency Requirements for PCI-Express and Serial RapidIO

The CCB clock frequency must be considered for proper operation of the high-speed PCI-Express and Serial RapidIO interfaces as described below.

For proper PCI Express operation, the CCB clock frequency must be greater than:

See *MPC8548ERM*, *Rev.* 2, *PowerQUICC III Integrated Processor Family Reference Manual*, Section 18.1.3.2, "Link Width," for PCI Express interface width details.

For proper serial RapidIO operation, the CCB clock frequency must be greater than:

$2 \times (0.80) \times (Serial RapidIO interface frequency) \times (Serial RapidIO link width)$

64

See *MPC8548ERM*, *Rev.* 2, *PowerQUICC III Integrated Processor Family Reference Manual*, Section 17.4, "1x/4x LP-Serial Signal Descriptions," for serial RapidIO interface width and frequency details.

# 4.7 Other Input Clocks

For information on the input clocks of other functional blocks of the platform see the specific section of this document.

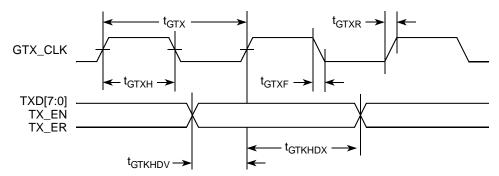

Figure 8 shows the GMII transmit AC timing diagram.

Figure 8. GMII Transmit AC Timing Diagram

## 8.2.2.2 GMII Receive AC Timing Specifications

This table provides the GMII receive AC timing specifications.

| Table 27. GMII Receive AC | Timing Specifications |

|---------------------------|-----------------------|

|---------------------------|-----------------------|

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|---------------------------------------------|-------------------------------------|-----|-----|-----|------|

| RX_CLK clock period                         | t <sub>GRX</sub>                    | —   | 8.0 | —   | ns   |

| RX_CLK duty cycle                           | t <sub>GRXH</sub> /t <sub>GRX</sub> | 35  | _   | 75  | ns   |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>GRDVKH</sub>                 | 2.0 | _   | —   | ns   |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>GRDXKH</sub>                 | 0   | _   | —   | ns   |

| RX_CLK clock rise (20%-80%)                 | t <sub>GRXR</sub> 2                 | —   | _   | 1.0 | ns   |

| RX_CLK clock fall time (80%-20%)            | t <sub>GRXF</sub> 2                 |     |     | 1.0 | ns   |

#### Notes:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>GRDVKH</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GRX</sub> represents the GMII (G) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

2. Guaranteed by design.

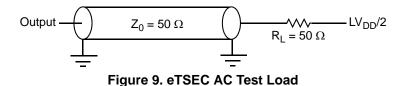

Figure 9 provides the AC test load for eTSEC.

# 10 Local Bus

This section describes the DC and AC electrical specifications for the local bus interface of the device.

# **10.1** Local Bus DC Electrical Characteristics

This table provides the DC electrical characteristics for the local bus interface operating at  $BV_{DD} = 3.3 \text{ V DC}$ .

| Parameter                                                       | Symbol          | Min  | Мах                    | Unit |

|-----------------------------------------------------------------|-----------------|------|------------------------|------|

| High-level input voltage                                        | V <sub>IH</sub> | 2    | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                         | V <sub>IL</sub> | -0.3 | 0.8                    | V    |

| Input current $(V_{IN}^{1} = 0 V \text{ or } V_{IN} = BV_{DD})$ | I <sub>IN</sub> | _    | ±5                     | μA   |

| High-level output voltage ( $BV_{DD} = min, I_{OH} = -2 mA$ )   | V <sub>OH</sub> | 2.4  | —                      | V    |

| Low-level output voltage ( $BV_{DD} = min$ , $I_{OL} = 2 mA$ )  | V <sub>OL</sub> | —    | 0.4                    | V    |

Table 38. Local Bus DC Electrical Characteristics (3.3 V DC)

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1 and Table 2.

Table 39 provides the DC electrical characteristics for the local bus interface operating at  $BV_{DD} = 2.5 \text{ V DC}$ .

Table 39. Local Bus DC Electrical Characteristics (2.5 V DC)

| Parameter                                                       | Symbol          | Min  | Max                    | Unit |

|-----------------------------------------------------------------|-----------------|------|------------------------|------|

| High-level input voltage                                        | V <sub>IH</sub> | 1.70 | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                         | V <sub>IL</sub> | -0.3 | 0.7                    | V    |

| Input current $(V_{IN}^{1} = 0 V \text{ or } V_{IN} = BV_{DD})$ | I <sub>IH</sub> | _    | 10                     | μA   |

|                                                                 | I               |      | -15                    |      |

| High-level output voltage ( $BV_{DD} = min, I_{OH} = -1 mA$ )   | V <sub>OH</sub> | 2.0  | —                      | V    |

| Low-level output voltage ( $BV_{DD} = min$ , $I_{OL} = 1 mA$ )  | V <sub>OL</sub> | _    | 0.4                    | V    |

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $BV_{IN}$  symbol referenced in Table 1 and Table 2.

# 11 Programmable Interrupt Controller

In IRQ edge trigger mode, when an external interrupt signal is asserted (according to the programmed polarity), it must remain the assertion for at least 3 system clocks (SYSCLK periods).

# 12 JTAG

This section describes the DC and AC electrical specifications for the IEEE 1149.1 (JTAG) interface of the device.

# **12.1 JTAG DC Electrical Characteristics**

This table provides the DC electrical characteristics for the JTAG interface.

| Parameter                                                     | Symbol <sup>1</sup> | Min  | Мах                    | Unit |

|---------------------------------------------------------------|---------------------|------|------------------------|------|

| High-level input voltage                                      | V <sub>IH</sub>     | 2    | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                       | V <sub>IL</sub>     | -0.3 | 0.8                    | V    |

| Input current ( $V_{IN}^{1} = 0$ V or $V_{IN} = V_{DD}$ )     | I <sub>IN</sub>     | —    | ±5                     | μA   |

| High-level output voltage ( $OV_{DD} = min, I_{OH} = -2 mA$ ) | V <sub>OH</sub>     | 2.4  | _                      | V    |

| Low-level output voltage ( $OV_{DD} = min, I_{OL} = 2 mA$ )   | V <sub>OL</sub>     | —    | 0.4                    | V    |

Table 43. JTAG DC Electrical Characteristics

Note:

1. Note that the symbol  $V_{\text{IN}}$  in this case, represents the  $\text{OV}_{\text{IN}}$

# **12.2 JTAG AC Electrical Specifications**

This table provides the JTAG AC timing specifications as defined in Figure 30 through Figure 32.

| Parameter                                            | Symbol <sup>2</sup>                        | Min      | Мах  | Unit | Notes |

|------------------------------------------------------|--------------------------------------------|----------|------|------|-------|

| JTAG external clock frequency of operation           | f <sub>JTG</sub>                           | 0        | 33.3 | MHz  |       |

| JTAG external clock cycle time                       | t <sub>JTG</sub>                           | 30       | _    | ns   | _     |

| JTAG external clock pulse width measured at 1.4 V    | t <sub>JTKHKL</sub>                        | 15       | _    | ns   | _     |

| JTAG external clock rise and fall times              | t <sub>JTGR</sub> & t <sub>JTGF</sub>      | 0        | 2    | ns   | 6     |

| TRST assert time                                     | t <sub>TRST</sub>                          | 25       | _    | ns   | 3     |

| Input setup times:<br>Boundary-scan data<br>TMS, TDI | t <sub>JTDVKH</sub><br>t <sub>JTIVKH</sub> | 4<br>0   |      | ns   | 4     |

| Input hold times:<br>Boundary-scan data<br>TMS, TDI  | <sup>t</sup> jtdxkh<br><sup>t</sup> jtixkh | 20<br>25 |      | ns   | 4     |

Table 44. JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup>

| Symbol                                      | Parameter                                                                                    | Min    | Nom  | Мах    | Unit | Comments                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------|----------------------------------------------------------------------------------------------|--------|------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI                                          | Unit interval                                                                                | 399.88 | 400  | 400.12 | ps   | Each UI is 400 ps ± 300 ppm. UI does not account<br>for spread spectrum clock dictated variations.<br>See Note 1.                                                                                                                                                                                                                                                                        |

| V <sub>TX-DIFFp-p</sub>                     | Differential<br>peak-to-peak<br>output voltage                                               | 0.8    | —    | 1.2    | V    | $V_{TX-DIFFp-p} = 2 \times  V_{TX-D+} - V_{TX-D-} $ . See Note 2.                                                                                                                                                                                                                                                                                                                        |

| V <sub>TX-DE-RATIO</sub>                    | De-emphasized<br>differential<br>output voltage<br>(ratio)                                   | -3.0   | -3.5 | -4.0   | dB   | Ratio of the $V_{TX-DIFFp-p}$ of the second and following bits after a transition divided by the $V_{TX-DIFFp-p}$ of the first bit after a transition. See Note 2.                                                                                                                                                                                                                       |

| T <sub>TX-EYE</sub>                         | Minimum TX<br>eye width                                                                      | 0.70   | _    | _      | UI   | The maximum transmitter jitter can be derived as $T_{TX-MAX-JITTER} = 1 - T_{TX-EYE} = 0.3$ UI.<br>See Notes 2 and 3.                                                                                                                                                                                                                                                                    |

| T <sub>TX-EYE-MEDIAN-to-</sub> MAX-JITTER   | Maximum time<br>between the<br>jitter median and<br>maximum<br>deviation from<br>the median. | _      |      | 0.15   | UI   | Jitter is defined as the measurement variation of<br>the crossing points ( $V_{TX-DIFFp-p} = 0$ V) in relation<br>to a recovered TX UI. A recovered TX UI is<br>calculated over 3500 consecutive unit intervals of<br>sample data. Jitter is measured using all edges of<br>the 250 consecutive UI in the center of the 3500<br>UI used for calculating the TX UI.<br>See Notes 2 and 3. |

| T <sub>TX-RISE</sub> , T <sub>TX-FALL</sub> | D+/D-TX output<br>rise/fall time                                                             | 0.125  | _    | —      | UI   | See Notes 2 and 5.                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>TX-CM-ACp</sub>                      | RMS AC peak<br>common mode<br>output voltage                                                 |        |      | 20     | mV   | $\begin{split} & V_{TX\text{-}CM\text{-}ACp} = RMS( V_{TXD\text{+}} + V_{TXD\text{-}} /2 - V_{TX\text{-}CM\text{-}DC}) \\ & V_{TX\text{-}CM\text{-}DC} = DC_{(avg)} \text{ of }  V_{TX\text{-}D\text{+}} + V_{TX\text{-}D\text{-}} /2. \\ & See Note 2. \end{split}$                                                                                                                     |

| V <sub>TX-CM-DC-ACTIVE-</sub> IDLE-DELTA    | Absolute delta of<br>dc common<br>mode voltage<br>during L0 and<br>electrical idle           | 0      | _    | 100    | mV   | $\begin{split}  V_{TX-CM-DC} & (during L0) + V_{TX-CM-Idle-DC} & (during electrical idle)  \leq 100 mV \\ V_{TX-CM-DC} &= DC_{(avg)} & of  V_{TX-D+} + V_{TX-D-} /2 \ [L0] \\ V_{TX-CM-Idle-DC} &= DC_{(avg)} & of  V_{TX-D+} + V_{TX-D-} /2 \\ [electrical idle] \\ See Note 2. \end{split}$                                                                                            |

| V <sub>TX-CM</sub> -DC-LINE-DELTA           | Absolute delta of<br>DC common<br>mode between<br>D+ and D–                                  | 0      |      | 25     | mV   | $\begin{split}  V_{TX-CM-DC-D+} - V_{TX-CM-DC-D-}  &\leq 25 \text{ mV} \\ V_{TX-CM-DC-D+} &= DC_{(avg)} \text{ of }  V_{TX-D+}  \\ V_{TX-CM-DC-D-} &= DC_{(avg)} \text{ of }  V_{TX-D-} . \\ \text{See Note 2.} \end{split}$                                                                                                                                                             |

| V <sub>TX</sub> -IDLE-DIFFp                 | Electrical idle<br>differential peak<br>output voltage                                       | 0      | _    | 20     | mV   | $V_{TX-IDLE-DIFFp} =  V_{TX-IDLE-D+} - V_{TX-IDLE-D-}  \le 20 \text{ mV.}$<br>See Note 2.                                                                                                                                                                                                                                                                                                |

| V <sub>TX-RCV-DETECT</sub>                  | The amount of<br>voltage change<br>allowed during<br>receiver<br>detection                   |        |      | 600    | mV   | The total amount of voltage change that a transmitter can apply to sense whether a low impedance receiver is present. See Note 6.                                                                                                                                                                                                                                                        |

#### **PCI Express**

Figure 48. Minimum Transmitter Timing and Voltage Output Compliance Specifications

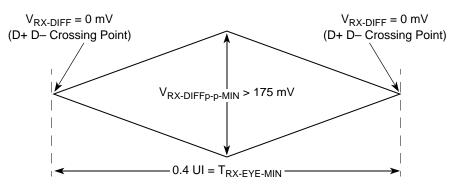

# 17.4.3 Differential Receiver (RX) Input Specifications

Table 57 defines the specifications for the differential input at all receivers (RXs). The parameters are specified at the component pins.

| Symbol                                       | Parameter                                                                                   | Min    | Nom | Max    | Unit | Comments                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------|---------------------------------------------------------------------------------------------|--------|-----|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI                                           | Unit interval                                                                               | 399.88 | 400 | 400.12 | ps   | Each UI is 400 ps $\pm$ 300 ppm. UI does not account<br>for spread spectrum clock dictated variations.<br>See Note 1.                                                                                                                                                                                                                                                                        |

| V <sub>RX-DIFFp-p</sub>                      | Differential<br>peak-to-peak<br>input voltage                                               | 0.175  | —   | 1.200  | V    | $V_{RX-DIFFp-p} = 2 \times  V_{RX-D+} - V_{RX-D-} $ . See Note 2.                                                                                                                                                                                                                                                                                                                            |

| T <sub>RX-EYE</sub>                          | Minimum<br>receiver eye<br>width                                                            | 0.4    | _   | _      | UI   | The maximum interconnect media and transmitter jitter that can be tolerated by the receiver can be derived as $T_{RX-MAX-JITTER} = 1 - T_{RX-EYE} = 0.6$ UI. See Notes 2 and 3.                                                                                                                                                                                                              |

| T <sub>RX-EYE-MEDIAN-to-</sub><br>MAX-JITTER | Maximum time<br>between the<br>jitter median and<br>maximum<br>deviation from<br>the median | —      |     | 0.3    | UI   | Jitter is defined as the measurement variation of<br>the crossing points ( $V_{RX-DIFFp-p} = 0$ V) in relation<br>to a recovered TX UI. A recovered TX UI is<br>calculated over 3500 consecutive unit intervals of<br>sample data. Jitter is measured using all edges of<br>the 250 consecutive UI in the center of the<br>3500 UI used for calculating the TX UI.<br>See Notes 2, 3, and 7. |

Table 57. Differential Receiver (RX) Input Specifications

#### PCI Express

The eye diagram must be valid for any 250 consecutive UIs.

A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. The eye diagram is created using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI.

### NOTE

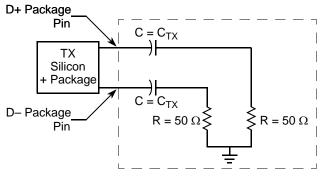

The reference impedance for return loss measurements is 50. to ground for both the D+ and D– line (that is, as measured by a vector network analyzer with 50- $\Omega$  probes—see Figure 50). Note that the series capacitors, CTX, are optional for the return loss measurement.

Figure 49. Minimum Receiver Eye Timing and Voltage Compliance Specification

# 17.5.1 Compliance Test and Measurement Load

The AC timing and voltage parameters must be verified at the measurement point, as specified within 0.2 inches of the package pins, into a test/measurement load shown in Figure 50.

### NOTE

The allowance of the measurement point to be within 0.2 inches of the package pins is meant to acknowledge that package/board routing may benefit from D+ and D- not being exactly matched in length at the package pin boundary.

Figure 50. Compliance Test/Measurement Load

#### Notes:

- 1. All dimensions are in millimeters.

- 2. Dimensioning and tolerancing per ASME Y14.5M-1994.

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

- 5. Parallelism measurement shall exclude any effect of mark on top surface of package.

- 6. All dimensions are symmetric across the package center lines unless dimensioned otherwise.

| Signal                 | Package Pin Number                                                                                                                                                                                                                                                                                               | Pin Type | Power<br>Supply  | Notes    |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

| PCI1_REQ[4:1]          | AH2, AG4, AG3, AH4                                                                                                                                                                                                                                                                                               | I        | OV <sub>DD</sub> |          |

|                        |                                                                                                                                                                                                                                                                                                                  |          |                  |          |

|                        |                                                                                                                                                                                                                                                                                                                  |          |                  |          |

|                        |                                                                                                                                                                                                                                                                                                                  |          |                  |          |

|                        |                                                                                                                                                                                                                                                                                                                  |          |                  |          |

| PCI1_REQ0              | AH3                                                                                                                                                                                                                                                                                                              | I/O      | OV <sub>DD</sub> | —        |

| PCI1_CLK               | AH26                                                                                                                                                                                                                                                                                                             | I        | OV <sub>DD</sub> | 39       |

| PCI1_DEVSEL            | AH11                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_FRAME             | AE11                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_IDSEL             | AG9                                                                                                                                                                                                                                                                                                              | I        | OV <sub>DD</sub> |          |

| PCI1_REQ64/PCI2_FRAME  | AF14                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2, 5, 10 |

| PCI1_ACK64/PCI2_DEVSEL | V15                                                                                                                                                                                                                                                                                                              | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_CLK               | AE28                                                                                                                                                                                                                                                                                                             | I        | OV <sub>DD</sub> | 39       |

| PCI2_IRDY              | AD26                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_PERR              | AD25                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_GNT[4:1]          | AE26, AG24, AF25, AE25                                                                                                                                                                                                                                                                                           | 0        | OV <sub>DD</sub> | 5, 9, 35 |

| PCI2_GNT0              | AG25                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | _        |

| PCI2_SERR              | AD24                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2, 4     |

| PCI2_STOP              | AF24                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_TRDY              | AD27                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_REQ[4:1]          | AD28, AE27, W17, AF26                                                                                                                                                                                                                                                                                            | I        | OV <sub>DD</sub> | —        |

| PCI2_REQ0              | AH25                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | —        |

|                        | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                                       |          | •                |          |

| MDQ[0:63]              | L18, J18, K14, L13, L19, M18, L15, L14, A17,<br>B17, A13, B12, C18, B18, B13, A12, H18, F18,<br>J14, F15, K19, J19, H16, K15, D17, G16, K13,<br>D14, D18, F17, F14, E14, A7, A6, D5, A4, C8,<br>D7, B5, B4, A2, B1, D1, E4, A3, B2, D2, E3, F3,<br>G4, J5, K5, F6, G5, J6, K4, J1, K2, M5, M3, J3,<br>J2, L1, M6 | I/O      | GV <sub>DD</sub> | _        |

| MECC[0:7]              | H13, F13, F11, C11, J13, G13, D12, M12                                                                                                                                                                                                                                                                           | I/O      | GV <sub>DD</sub> |          |

| MDM[0:8]               | M17, C16, K17, E16, B6, C4, H4, K1, E13                                                                                                                                                                                                                                                                          | 0        | GV <sub>DD</sub> | -        |

| MDQS[0:8]              | M15, A16, G17, G14, A5, D3, H1, L2, C13                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> | -        |

| MDQS[0:8]              | L17, B16, J16, H14, C6, C2, H3, L4, D13                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> | —        |

| MA[0:15]               | A8, F9, D9, B9, A9, L10, M10, H10, K10, G10,<br>B8, E10, B10, G6, A10, L11                                                                                                                                                                                                                                       | 0        | GV <sub>DD</sub> | —        |

| MBA[0:2]               | F7, J7, M11                                                                                                                                                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —        |

### Table 71. MPC8548E Pinout Listing (continued)

### Table 71. MPC8548E Pinout Listing (continued)

| Signal                                                                                                             | Package Pin Number                                                                                                                                                                                                                                                                                     | Pin Type                                                      | Power<br>Supply                                                  | Notes                        |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------|------------------------------|

| 25.These are test signals for factory u                                                                            | ise only and must be pulled up (100 $\Omega$ –1 k $\Omega$ ) to                                                                                                                                                                                                                                        | OV <sub>DD</sub> for normal                                   | machine oper                                                     | ration.                      |

| 26.Independent supplies derived from                                                                               | n board V <sub>DD</sub> .                                                                                                                                                                                                                                                                              |                                                               |                                                                  |                              |

| 27.Recommend a pull-up resistor (~1                                                                                | $k\Omega$ ) be placed on this pin to $OV_{DD}$ .                                                                                                                                                                                                                                                       |                                                               |                                                                  |                              |

|                                                                                                                    | oul <u>led down du</u> ring power-on reset: TSEC3_TXD<br>Y/QUIESCE, MSRCID[2:4], ASLEEP.                                                                                                                                                                                                               | [3], TSEC4_TXD                                                | 93/TSEC3_TX                                                      | D7,                          |

| 30.This pin requires an external 4.7-ks driven.                                                                    | 2 pull-down resistor to prevent PHY from seeing a                                                                                                                                                                                                                                                      | valid transmit en                                             | able before it i                                                 | s active                     |

| 31.This pin is only an output in eTSE                                                                              | C3 FIFO mode when used as Rx flow control.                                                                                                                                                                                                                                                             |                                                               |                                                                  |                              |

| 32. These pins must be connected to 2                                                                              | XV <sub>DD</sub> .                                                                                                                                                                                                                                                                                     |                                                               |                                                                  |                              |

| 33. <u>TSEC2_</u> TXD1, TSEC2_TX_ER ar<br>HRESET assertion.                                                        | e multiplexed as cfg_dram_type[0:1]. They must                                                                                                                                                                                                                                                         | be valid at powe                                              | er-up, even bet                                                  | fore                         |

| 34.These pins must be pulled to grou                                                                               | nd through a 300- $\Omega$ (±10%) resistor.                                                                                                                                                                                                                                                            |                                                               |                                                                  |                              |

| down to select external arbiter if the<br>connect' or terminated through 2–1<br>connected to any other PCI device. | er the POR config pin that selects between inter<br>ere is any other PCI device connected on the PC<br>0 k $\Omega$ pull-up resistors with the default of internal<br>. The PCI block drives the PCI <i>n</i> _AD pins if it is con-<br>thether it is disabled via the DEVDISR register of<br>the bus. | l bus, or leave th<br>arbiter if the PC<br>onfigured to be th | e PCI <i>n_</i> AD pi<br><i>n_</i> AD pins are<br>e PCI arbiter– | ns as 'n<br>e not<br>–throug |

|                                                                                                                    | $2-\Omega$ precision 1% resistor and MDIC1 is connector automatic calibration of the DDR IOs.                                                                                                                                                                                                          | ed to GV <sub>DD</sub> throu                                  | gh an 18.2-Ω                                                     | precisio                     |

| 38.These pins must be left floating.                                                                               |                                                                                                                                                                                                                                                                                                        |                                                               |                                                                  |                              |

| 39. If PCI1 or PCI2 is configured as P<br>Otherwise the processor will not be                                      | CI asynchronous mode, a valid clock must be pr<br>oot up.                                                                                                                                                                                                                                              | ovided on pin PC                                              | CI1_CLK or PC                                                    | CI2_CL                       |

| 40.These pins must be connected to                                                                                 | GND.                                                                                                                                                                                                                                                                                                   |                                                               |                                                                  |                              |

| 101.This pin requires an external 4.7-                                                                             | $k\Omega$ resistor to GND.                                                                                                                                                                                                                                                                             |                                                               |                                                                  |                              |

| 102.For Rev. 2.x silicon, DMA_DACK<br>POR configuration are don't care.                                            | [0:1] must be 0b11 during POR configuration; for                                                                                                                                                                                                                                                       | r rev. 1.x silicon, t                                         | the pin values                                                   | during                       |

| 103.If these pins are not used as GPI<br>2–10 kΩ resistors.                                                        | Nn (general-purpose input), they must be pulled                                                                                                                                                                                                                                                        | low (to GND) or                                               | high (to LV <sub>DD</sub> )                                      | ) throug                     |

| 104.These must be pulled low to GNI                                                                                | D through 2–10 k $\Omega$ resistors if they are not used.                                                                                                                                                                                                                                              |                                                               |                                                                  |                              |

|                                                                                                                    | to $\text{LV}_{\text{DD}}$ through 2–10 k $\Omega$ resistors if they are no                                                                                                                                                                                                                            |                                                               |                                                                  |                              |

| 106.For rev. 2.x silicon, DMA_DACK[(<br>configuration are don't care.                                              | ):1] must be 0b10 during POR configuration; for re                                                                                                                                                                                                                                                     | ev. 1.x silicon, the                                          | pin values du                                                    | ring PO                      |

| 107.For rev. 2.x silicon, DMA_DACK[0 configuration are don't care.                                                 | ):1] must be 0b01 during POR configuration; for re                                                                                                                                                                                                                                                     | ev. 1.x silicon, the                                          | pin values du                                                    | ring PO                      |

| 108.For rev. 2.x silicon, DMA_DACK[C configuration are don't care.                                                 | 0:1] must be 0b11 during POR configuration; for re                                                                                                                                                                                                                                                     | ev. 1.x silicon, the                                          | pin values du                                                    | ring PO                      |

| 109.This is a test signal for factory us                                                                           | e only and must be pulled down (100 $\Omega$ – 1 k $\Omega$ )                                                                                                                                                                                                                                          | to GND for norm                                               | al machine op                                                    | eration.                     |

| 110.These pins must be pulled high to                                                                              | o OV <sub>DD</sub> through 2–10 k $\Omega$ resistors.                                                                                                                                                                                                                                                  |                                                               |                                                                  |                              |

| 111.If these pins are not used as GPII 2–10 k $\Omega$ resistors.                                                  | Nn (general-purpose input), they must be pulled                                                                                                                                                                                                                                                        | low (to GND) or I                                             | high (to OV <sub>DD</sub> )                                      | ) throug                     |

| 112.This pin must not be pulled down                                                                               | during POR configuration.                                                                                                                                                                                                                                                                              |                                                               |                                                                  |                              |

|                                                                                                                    |                                                                                                                                                                                                                                                                                                        |                                                               |                                                                  |                              |

| Table 72 | . MPC8547E | <b>Pinout Listing</b> | (continued) |

|----------|------------|-----------------------|-------------|

|----------|------------|-----------------------|-------------|

| Signal       | Package Pin Number                                                                                                                                                                                                                                                                                               | Pin Type | Power<br>Supply  | Notes |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

| Reserved     | AE26                                                                                                                                                                                                                                                                                                             | _        | —                | 2     |

| cfg_pci1_clk | AG24                                                                                                                                                                                                                                                                                                             | I        | OV <sub>DD</sub> | 5     |

| Reserved     | AF25                                                                                                                                                                                                                                                                                                             | _        | —                | 101   |

| Reserved     | AE25                                                                                                                                                                                                                                                                                                             | _        | —                | 2     |

| Reserved     | AG25                                                                                                                                                                                                                                                                                                             | _        | —                | 2     |

| Reserved     | AD24                                                                                                                                                                                                                                                                                                             | _        | —                | 2     |

| Reserved     | AF24                                                                                                                                                                                                                                                                                                             | _        | —                | 2     |

| Reserved     | AD27                                                                                                                                                                                                                                                                                                             | _        | —                | 2     |

| Reserved     | AD28, AE27, W17, AF26                                                                                                                                                                                                                                                                                            | _        | —                | 2     |

| Reserved     | AH25                                                                                                                                                                                                                                                                                                             | _        | —                | 2     |

|              | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                                       |          |                  | 1     |

| MDQ[0:63]    | L18, J18, K14, L13, L19, M18, L15, L14, A17,<br>B17, A13, B12, C18, B18, B13, A12, H18, F18,<br>J14, F15, K19, J19, H16, K15, D17, G16, K13,<br>D14, D18, F17, F14, E14, A7, A6, D5, A4, C8,<br>D7, B5, B4, A2, B1, D1, E4, A3, B2, D2, E3, F3,<br>G4, J5, K5, F6, G5, J6, K4, J1, K2, M5, M3, J3,<br>J2, L1, M6 | I/O      | GV <sub>DD</sub> | _     |

| MECC[0:7]    | H13, F13, F11, C11, J13, G13, D12, M12                                                                                                                                                                                                                                                                           | I/O      | GV <sub>DD</sub> | —     |

| MDM[0:8]     | M17, C16, K17, E16, B6, C4, H4, K1, E13                                                                                                                                                                                                                                                                          | 0        | GV <sub>DD</sub> | —     |

| MDQS[0:8]    | M15, A16, G17, G14, A5, D3, H1, L2, C13                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> | —     |

| MDQS[0:8]    | L17, B16, J16, H14, C6, C2, H3, L4, D13                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> | —     |

| MA[0:15]     | A8, F9, D9, B9, A9, L10, M10, H10, K10, G10,<br>B8, E10, B10, G6, A10, L11                                                                                                                                                                                                                                       | 0        | GV <sub>DD</sub> | _     |

| MBA[0:2]     | F7, J7, M11                                                                                                                                                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —     |

| MWE          | E7                                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub> | —     |

| MCAS         | H7                                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub> | —     |

| MRAS         | L8                                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub> | —     |

| MCKE[0:3]    | F10, C10, J11, H11                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub> | 11    |

| MCS[0:3]     | K8, J8, G8, F8                                                                                                                                                                                                                                                                                                   | 0        | GV <sub>DD</sub> | —     |

| MCK[0:5]     | H9, B15, G2, M9, A14, F1                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub> | —     |

| MCK[0:5]     | J9, A15, G1, L9, B14, F2                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub> | —     |

| MODT[0:3]    | E6, K6, L7, M7                                                                                                                                                                                                                                                                                                   | 0        | GV <sub>DD</sub> | —     |

| MDIC[0:1]    | A19, B19                                                                                                                                                                                                                                                                                                         | I/O      | GV <sub>DD</sub> | 36    |

| Signal                   | Package Pin Number                                                                                                                                                      | Pin Type | Power<br>Supply  | Notes        |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|--------------|

| MDIC[0:1]                | A19, B19                                                                                                                                                                | I/O      | GV <sub>DD</sub> | 36           |

|                          | Local Bus Controller Interface                                                                                                                                          |          |                  |              |

| LAD[0:31]                | E27, B20, H19, F25, A20, C19, E28, J23, A25,<br>K22, B28, D27, D19, J22, K20, D28, D25, B25,<br>E22, F22, F21, C25, C22, B23, F20, A23, A22,<br>E19, A21, D21, F19, B21 | I/O      | BV <sub>DD</sub> | _            |

| LDP[0:3]                 | K21, C28, B26, B22                                                                                                                                                      | I/O      | BV <sub>DD</sub> | —            |

| LA[27]                   | H21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LA[28:31]                | H20, A27, D26, A28                                                                                                                                                      | 0        | BV <sub>DD</sub> | 5, 7, 9      |

| LCS[0:4]                 | J25, C20, J24, G26, A26                                                                                                                                                 | 0        | BV <sub>DD</sub> | _            |

| LCS5/DMA_DREQ2           | D23                                                                                                                                                                     | I/O      | BV <sub>DD</sub> | 1            |

| LCS6/DMA_DACK2           | G20                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 1            |

| LCS7/DMA_DDONE2          | E21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 1            |

| LWE0/LBS0/LSDDQM[0]      | G25                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LWE1/LBS1/LSDDQM[1]      | C23                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LWE2/LBS2/LSDDQM[2]      | J21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LWE3/LBS3/LSDDQM[3]      | A24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LALE                     | H24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9      |

| LBCTL                    | G27                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9      |

| LGPL0/LSDA10             | F23                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LGPL1/LSDWE              | G22                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LGPL2/LOE/LSDRAS         | B27                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9      |

| LGPL3/LSDCAS             | F24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LGPL4/LGTA/LUPWAIT/LPBSE | H23                                                                                                                                                                     | I/O      | BV <sub>DD</sub> | _            |

| LGPL5                    | E26                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9         |

| LCKE                     | E24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | _            |

| LCLK[0:2]                | E23, D24, H22                                                                                                                                                           | 0        | BV <sub>DD</sub> | _            |

| LSYNC_IN                 | F27                                                                                                                                                                     | I        | BV <sub>DD</sub> | _            |

| LSYNC_OUT                | F28                                                                                                                                                                     | 0        | BV <sub>DD</sub> | _            |

|                          | DMA                                                                                                                                                                     |          |                  | 1            |

| DMA_DACK[0:1]            | AD3, AE1                                                                                                                                                                | 0        | OV <sub>DD</sub> | 5, 9,<br>106 |

| DMA_DREQ[0:1]            | AD4, AE2                                                                                                                                                                | I        | OV <sub>DD</sub> | —            |

| DMA_DDONE[0:1]           | AD2, AD1                                                                                                                                                                | 0        | OV <sub>DD</sub> | —            |

|                          | Programmable Interrupt Controller                                                                                                                                       |          | 1                | 1            |

| Signal                | Package Pin Number                              | Pin Type | Power<br>Supply  | Notes |

|-----------------------|-------------------------------------------------|----------|------------------|-------|

| UDE                   | AH16                                            | I        | OV <sub>DD</sub> | _     |

| MCP                   | AG19                                            | I        | OV <sub>DD</sub> | _     |

| IRQ[0:7]              | AG23, AF18, AE18, AF20, AG18, AF17, AH24, AE20  | I        | OV <sub>DD</sub> | -     |

| IRQ[8]                | AF19                                            | I        | OV <sub>DD</sub> | —     |

| IRQ[9]/DMA_DREQ3      | AF21                                            | I        | OV <sub>DD</sub> | 1     |

| IRQ[10]/DMA_DACK3     | AE19                                            | I/O      | OV <sub>DD</sub> | 1     |

| IRQ[11]/DMA_DDONE3    | AD20                                            | I/O      | OV <sub>DD</sub> | 1     |

| IRQ_OUT               | AD18                                            | 0        | OV <sub>DD</sub> | 2, 4  |

|                       | Ethernet Management Interface                   |          | 1                |       |

| EC_MDC                | AB9                                             | 0        | OV <sub>DD</sub> | 5, 9  |

| EC_MDIO               | AC8                                             | I/O      | OV <sub>DD</sub> | _     |

|                       | Gigabit Reference Clock                         |          |                  |       |

| EC_GTX_CLK125         | V11                                             | I        | LV <sub>DD</sub> |       |

|                       | Three-Speed Ethernet Controller (Gigabit Ethern | et 1)    | 1                |       |

| TSEC1_RXD[7:0]        | R5, U1, R3, U2, V3, V1, T3, T2                  | I        | LV <sub>DD</sub> |       |

| TSEC1_TXD[7:0]        | T10, V7, U10, U5, U4, V6, T5, T8                | 0        | LV <sub>DD</sub> | 5, 9  |

| TSEC1_COL             | R4                                              | I        | LV <sub>DD</sub> |       |

| TSEC1_CRS             | V5                                              | I/O      | LV <sub>DD</sub> | 20    |

| TSEC1_GTX_CLK         | U7                                              | 0        | LV <sub>DD</sub> |       |

| TSEC1_RX_CLK          | U3                                              | I        | LV <sub>DD</sub> |       |

| TSEC1_RX_DV           | V2                                              | I        | LV <sub>DD</sub> | _     |

| TSEC1_RX_ER           | T1                                              | I        | LV <sub>DD</sub> | _     |

| TSEC1_TX_CLK          | Т6                                              | I        | LV <sub>DD</sub> |       |

| TSEC1_TX_EN           | U9                                              | 0        | LV <sub>DD</sub> | 30    |

| TSEC1_TX_ER           | Τ7                                              | 0        | LV <sub>DD</sub> | _     |

| GPIN[0:7]             | P2, R2, N1, N2, P3, M2, M1, N3                  | I        | LV <sub>DD</sub> | 103   |

| GPOUT[0:5]            | N9, N10, P8, N7, R9, N5                         | 0        | LV <sub>DD</sub> | _     |

| cfg_dram_type0/GPOUT6 | R8                                              | 0        | LV <sub>DD</sub> | 5, 9  |