# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                            |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 1.0GHz                                                                  |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                                   |

| RAM Controllers                 | DDR, DDR2, SDRAM                                                        |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | -                                                                       |

| Ethernet                        | 10/100/1000Mbps (4)                                                     |

| SATA                            | -                                                                       |

| USB                             | -                                                                       |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                        |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                      |

| Security Features               | Cryptography, Random Number Generator                                   |

| Package / Case                  | 783-BBGA, FCBGA                                                         |

| Supplier Device Package         | 783-FCPBGA (29x29)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8547ecvtaqgd |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Overview

- Up to 32 simultaneous open pages for DDR2

- Contiguous or discontiguous memory mapping

- Read-modify-write support for RapidIO atomic increment, decrement, set, and clear transactions

- Sleep mode support for self-refresh SDRAM

- On-die termination support when using DDR2

- Supports auto refreshing

- On-the-fly power management using CKE signal

- Registered DIMM support

- Fast memory access via JTAG port

- 2.5-V SSTL\_2 compatible I/O (1.8-V SSTL\_1.8 for DDR2)

- Support for battery-backed main memory

- Programmable interrupt controller (PIC)

- Programming model is compliant with the OpenPIC architecture.

- Supports 16 programmable interrupt and processor task priority levels

- Supports 12 discrete external interrupts

- Supports 4 message interrupts with 32-bit messages

- Supports connection of an external interrupt controller such as the 8259 programmable interrupt controller

- Four global high-resolution timers/counters that can generate interrupts

- Supports a variety of other internal interrupt sources

- Supports fully nested interrupt delivery

- Interrupts can be routed to external pin for external processing.

- Interrupts can be routed to the e500 core's standard or critical interrupt inputs.

- Interrupt summary registers allow fast identification of interrupt source.

- Integrated security engine (SEC) optimized to process all the algorithms associated with IPSec, IKE, WTLS/WAP, SSL/TLS, and 3GPP

- Four crypto-channels, each supporting multi-command descriptor chains

- Dynamic assignment of crypto-execution units via an integrated controller

- Buffer size of 256 bytes for each execution unit, with flow control for large data sizes

- PKEU—public key execution unit

- RSA and Diffie-Hellman; programmable field size up to 2048 bits

- Elliptic curve cryptography with  $F_2m$  and F(p) modes and programmable field size up to 511 bits

- DEU—Data Encryption Standard execution unit

- DES, 3DES

- Two key (K1, K2) or three key (K1, K2, K3)

- ECB and CBC modes for both DES and 3DES

#### Overview

- Memory prefetching of PCI read accesses

- Supports posting of processor-to-PCI and PCI-to-memory writes

- PCI 3.3-V compatible

- Selectable hardware-enforced coherency

- Serial RapidIO<sup>™</sup> interface unit

- Supports RapidIO<sup>™</sup> Interconnect Specification, Revision 1.2

- Both  $1 \times$  and  $4 \times$  LP-serial link interfaces

- Long- and short-haul electricals with selectable pre-compensation

- Transmission rates of 1.25, 2.5, and 3.125 Gbaud (data rates of 1.0, 2.0, and 2.5 Gbps) per lane

- Auto detection of 1- and 4-mode operation during port initialization

- Link initialization and synchronization

- Large and small size transport information field support selectable at initialization time

- 34-bit addressing

- Up to 256 bytes data payload

- All transaction flows and priorities

- Atomic set/clr/inc/dec for read-modify-write operations

- Generation of IO\_READ\_HOME and FLUSH with data for accessing cache-coherent data at a remote memory system

- Receiver-controlled flow control

- Error detection, recovery, and time-out for packets and control symbols as required by the RapidIO specification

- Register and register bit extensions as described in part VIII (Error Management) of the RapidIO specification

- Hardware recovery only

- Register support is not required for software-mediated error recovery.

- Accept-all mode of operation for fail-over support

- Support for RapidIO error injection

- Internal LP-serial and application interface-level loopback modes

- Memory and PHY BIST for at-speed production test

- RapidIO-compatible message unit

- 4 Kbytes of payload per message

- Up to sixteen 256-byte segments per message

- Two inbound data message structures within the inbox

- Capable of receiving three letters at any mailbox

- Two outbound data message structures within the outbox

- Capable of sending three letters simultaneously

- Single segment multicast to up to 32 devIDs

- Chaining and direct modes in the outbox

Table 13 provides the recommended operating conditions for the DDR SDRAM controller when  $GV_{DD}(typ) = 2.5 \text{ V}.$

| Parameter/Condition                             | Symbol            | Min Max                  |                          | Unit | Notes |

|-------------------------------------------------|-------------------|--------------------------|--------------------------|------|-------|

| I/O supply voltage                              | GV <sub>DD</sub>  | 2.375                    | 2.625                    | V    | 1     |

| I/O reference voltage                           | MV <sub>REF</sub> | $0.49 \times GV_{DD}$    | $0.51 	imes GV_{DD}$     | V    | 2     |

| I/O termination voltage                         | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04 | MV <sub>REF</sub> + 0.04 | V    | 3     |

| Input high voltage                              | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.15 | GV <sub>DD</sub> + 0.3   | V    | —     |

| Input low voltage                               | V <sub>IL</sub>   | -0.3                     | MV <sub>REF</sub> – 0.15 | V    | —     |

| Output leakage current                          | I <sub>OZ</sub>   | -50                      | 50                       | μΑ   | 4     |

| Output high current (V <sub>OUT</sub> = 1.95 V) | I <sub>OH</sub>   | -16.2                    | —                        | mA   | —     |

| Output low current (V <sub>OUT</sub> = 0.35 V)  | I <sub>OL</sub>   | 16.2                     | —                        | mA   | —     |

| Table 13. DDR SDRAM DC Electrical | Characteristics for GV <sub>DD</sub> (typ) = 2.5 V |

|-----------------------------------|----------------------------------------------------|

|                                   |                                                    |

#### Notes:

1.  ${\rm GV}_{\rm DD}$  is expected to be within 50 mV of the DRAM  ${\rm V}_{\rm DD}$  at all times.

2. MV<sub>REF</sub> is expected to be equal to 0.5 × GV<sub>DD</sub>, and to track GV<sub>DD</sub> DC variations as measured at the receiver. Peak-to-peak noise on MV<sub>REF</sub> may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail must track variations in the DC level of MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  GV<sub>DD</sub>.

Table 14 provides the DDR I/O capacitance when  $GV_{DD}(typ) = 2.5$  V.

## Table 14. DDR SDRAM Capacitance for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition                     | Symbol           | Min | Max | Unit | Notes |

|-----------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS | C <sub>DIO</sub> |     | 0.5 | pF   | 1     |

#### Note:

1. This parameter is sampled.  $GV_{DD} = 2.5 \text{ V} \pm 0.125 \text{ V}$ , f = 1 MHz, T<sub>A</sub> = 25°C,  $V_{OUT} = GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

This table provides the current draw characteristics for MV<sub>REF</sub>.

## Table 15. Current Draw Characteristics for MV<sub>REF</sub>

| Parameter/Condition                | Symbol             | Min | Max | Unit | Notes |

|------------------------------------|--------------------|-----|-----|------|-------|

| Current draw for MV <sub>REF</sub> | I <sub>MVREF</sub> |     | 500 | μA   | 1     |

#### Note:

1. The voltage regulator for  $MV_{REF}$  must be able to supply up to 500  $\mu$ A current.

#### Enhanced Three-Speed Ethernet (eTSEC)

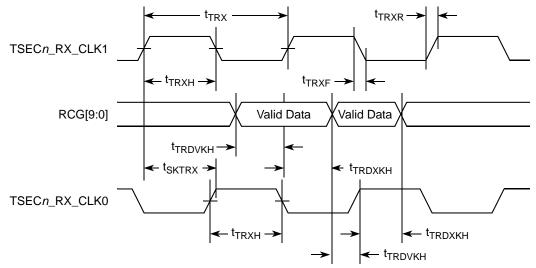

Figure 15 shows the TBI receive AC timing diagram.

Figure 15. TBI Receive AC Timing Diagram

# 8.2.5 TBI Single-Clock Mode AC Specifications

When the eTSEC is configured for TBI modes, all clocks are supplied from external sources to the relevant eTSEC interface. In single-clock TBI mode, when TBICON[CLKSEL] = 1, a 125-MHz TBI receive clock is supplied on the TSEC $n_RX_CLK$  pin (no receive clock is used on TSEC $n_TX_CLK$  in this mode, whereas for the dual-clock mode this is the PMA1 receive clock). The 125-MHz transmit clock is applied on the TSEC\_GTX\_CLK125 pin in all TBI modes.

A summary of the single-clock TBI mode AC specifications for receive appears in Table 32.

| Parameter/Condition                       | Symbol                 | Min | Тур | Max | Unit |

|-------------------------------------------|------------------------|-----|-----|-----|------|

| RX_CLK clock period                       | t <sub>TRRX</sub>      | 7.5 | 8.0 | 8.5 | ns   |

| RX_CLK duty cycle                         | t <sub>TRRH/TRRX</sub> | 40  | 50  | 60  | %    |

| RX_CLK peak-to-peak jitter                | t <sub>TRRJ</sub>      | —   | _   | 250 | ps   |

| Rise time RX_CLK (20%-80%)                | t <sub>TRRR</sub>      | —   | _   | 1.0 | ns   |

| Fall time RX_CLK (80%–20%)                | t <sub>TRRF</sub>      | —   | _   | 1.0 | ns   |

| RCG[9:0] setup time to RX_CLK rising edge | t <sub>trrdvkh</sub>   | 2.0 | _   | —   | ns   |

| RCG[9:0] hold time to RX_CLK rising edge  | t <sub>trrdxkh</sub>   | 1.0 | _   | —   | ns   |

#### Enhanced Three-Speed Ethernet (eTSEC)

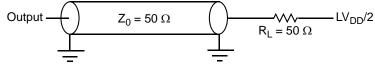

Figure 19 provides the AC test load for eTSEC.

Figure 19. eTSEC AC Test Load

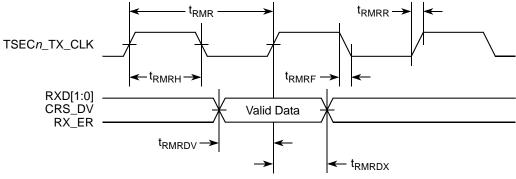

Figure 20 shows the RMII receive AC timing diagram.

Figure 20. RMII Receive AC Timing Diagram

# 9 Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals MDIO (management data input/output) and MDC (management data clock). The electrical characteristics for GMII, RGMII, RMII, TBI, and RTBI are specified in "Section 8, "Enhanced Three-Speed Ethernet (eTSEC)."

# 9.1 MII Management DC Electrical Characteristics

The MDC and MDIO are defined to operate at a supply voltage of 3.3 V. The DC electrical characteristics for MDIO and MDC are provided in this table.

| Parameter                                                            | Symbol           | Min  | Мах                    | Unit |

|----------------------------------------------------------------------|------------------|------|------------------------|------|

| Supply voltage (3.3 V)                                               | OV <sub>DD</sub> | 3.13 | 3.47                   | V    |

| Output high voltage ( $OV_{DD} = Min, I_{OH} = -1.0 mA$ )            | V <sub>OH</sub>  | 2.10 | OV <sub>DD</sub> + 0.3 | V    |

| Output low voltage (OV <sub>DD</sub> =Min, I <sub>OL</sub> = 1.0 mA) | V <sub>OL</sub>  | GND  | 0.50                   | V    |

| Input high voltage                                                   | V <sub>IH</sub>  | 2.0  | —                      | V    |

| Input low voltage                                                    | V <sub>IL</sub>  | _    | 0.90                   | V    |

| Input high current ( $OV_{DD} = Max, V_{IN}^1 = 2.1 V$ )             | I <sub>IH</sub>  | _    | 40                     | μA   |

| Input low current ( $OV_{DD} = Max$ , $V_{IN} = 0.5 V$ )             | IIL              | -600 | —                      | μΑ   |

Table 36. MII Management DC Electrical Characteristics

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

# 9.2 MII Management AC Electrical Specifications

This table provides the MII management AC timing specifications.

# Table 37. MII Management AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  is 3.3 V ± 5%.

| Parameter                  | Symbol <sup>1</sup> | Min                             | Тур | Мах                                | Unit | Notes   |

|----------------------------|---------------------|---------------------------------|-----|------------------------------------|------|---------|

| MDC frequency              | f <sub>MDC</sub>    | 0.72                            | 2.5 | 8.3                                | MHz  | 2, 3, 4 |

| MDC period                 | t <sub>MDC</sub>    | 120.5                           | _   | 1389                               | ns   | —       |

| MDC clock pulse width high | t <sub>MDCH</sub>   | 32                              | _   | —                                  | ns   | _       |

| MDC to MDIO valid          | t <sub>MDKHDV</sub> | $16 \times t_{CCB}$             | _   | —                                  | ns   | 5       |

| MDC to MDIO delay          | t <sub>MDKHDX</sub> | (16 × t <sub>CCB</sub> × 8) – 3 | _   | $(16 \times t_{CCB} \times 8) + 3$ | ns   | 5       |

| MDIO to MDC setup time     | t <sub>MDD∨KH</sub> | 5                               | _   | —                                  | ns   | _       |

| MDIO to MDC hold time      | t <sub>MDDXKH</sub> | 0                               | _   | —                                  | ns   | —       |

| MDC rise time              | t <sub>MDCR</sub>   | _                               |     | 10                                 | ns   | 4       |

| Parameter                                                             | Symbol <sup>1</sup>                 | Min | Max | Unit | Notes |

|-----------------------------------------------------------------------|-------------------------------------|-----|-----|------|-------|

| Local bus cycle time                                                  | t <sub>LBK</sub>                    | 7.5 | 12  | ns   | 2     |

| Local bus duty cycle                                                  | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43  | 57  | %    | —     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                  | t <sub>LBKSKEW</sub>                | —   | 150 | ps   | 7, 8  |

| Input setup to local bus clock (except LGTA/UPWAIT)                   | t <sub>LBIVKH1</sub>                | 1.9 | —   | ns   | 3, 4  |

| LGTA/LUPWAIT input setup to local bus clock                           | t <sub>LBIVKH2</sub>                | 1.8 | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LGTA/LUPWAIT)                 | t <sub>LBIXKH1</sub>                | 1.1 | —   | ns   | 3, 4  |

| LGTA/LUPWAIT input hold from local bus clock                          | t <sub>LBIXKH2</sub>                | 1.1 | —   | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) | t <sub>LBOTOT</sub>                 | 1.5 | —   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)             | t <sub>LBKHOV1</sub>                | —   | 2.1 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                             | t <sub>LBKHOV2</sub>                | —   | 2.3 | ns   | 3     |

| Local bus clock to address valid for LAD                              | t <sub>LBKHOV3</sub>                | —   | 2.4 | ns   | 3     |

| Local bus clock to LALE assertion                                     | t <sub>LBKHOV4</sub>                | —   | 2.4 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)            | t <sub>LBKHOX1</sub>                | 0.8 | —   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                          | t <sub>LBKHOX2</sub>                | 0.8 | —   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)    | t <sub>LBKHOZ1</sub>                | —   | 2.6 | ns   | 5     |

| Local bus clock to output high impedance for LAD/LDP                  | t <sub>LBKHOZ2</sub>                | _   | 2.6 | ns   | 5     |

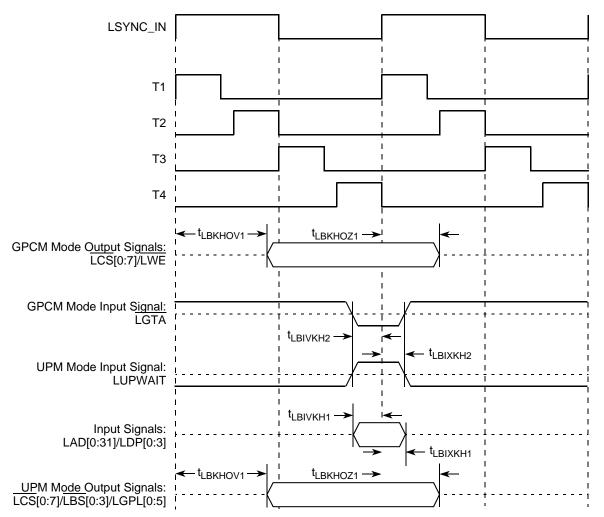

Table 41 describes the timing parameters of the local bus interface at  $BV_{DD} = 2.5$  V.

## Table 41. Local Bus Timing Parameters (BV<sub>DD</sub> = 2.5 V)—PLL Enabled

#### Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKH0X</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub></sub>

- 2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 3.3-V signaling levels.

- 4. Input timings are measured at the pin.

5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 8. Guaranteed by design.

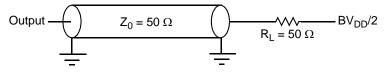

Figure 22 provides the AC test load for the local bus.

Figure 22. Local Bus AC Test Load

| Parameter                                                             | Symbol <sup>1</sup>  | Min  | Max  | Unit | Notes |

|-----------------------------------------------------------------------|----------------------|------|------|------|-------|

| LGTA/LUPWAIT input hold from local bus clock                          | t <sub>LBIXKL2</sub> | -1.3 |      | ns   | 4, 5  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) | t <sub>LBOTOT</sub>  | 1.5  |      | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)             | t <sub>LBKLOV1</sub> | _    | -0.3 | ns   |       |

| Local bus clock to data valid for LAD/LDP                             | t <sub>LBKLOV2</sub> | _    | -0.1 | ns   | 4     |

| Local bus clock to address valid for LAD                              | t <sub>LBKLOV3</sub> | _    | 0    | ns   | 4     |

| Local bus clock to LALE assertion                                     | t <sub>LBKLOV4</sub> | _    | 0    | ns   | 4     |

| Output hold from local bus clock (except LAD/LDP and LALE)            | t <sub>LBKLOX1</sub> | -3.7 |      | ns   | 4     |

| Output hold from local bus clock for LAD/LDP                          | t <sub>LBKLOX2</sub> | -3.7 |      | ns   | 4     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)    | t <sub>LBKLOZ1</sub> | _    | 0.2  | ns   | 7     |

| Local bus clock to output high impedance for LAD/LDP                  | t <sub>LBKLOZ2</sub> | _    | 0.2  | ns   | 7     |

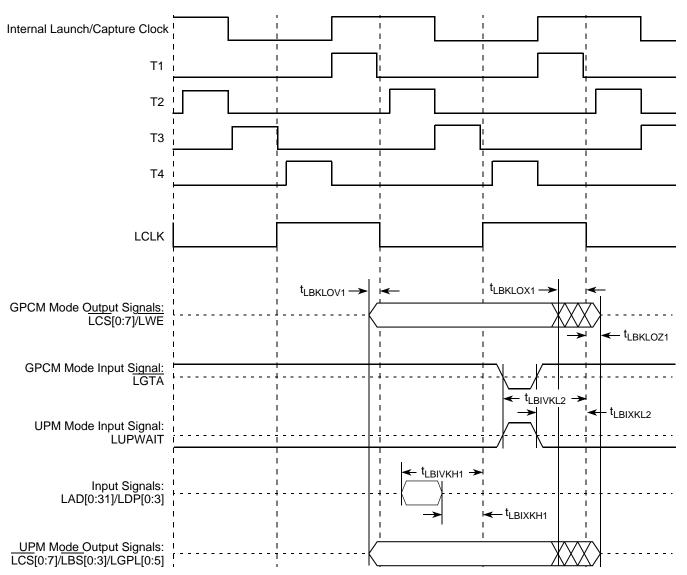

#### Table 42. Local Bus Timing Parameters—PLL Bypassed (continued)

#### Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKH0X</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

All timings are in reference to local bus clock for PLL bypass mode. Timings may be negative with respect to the local bus clock because the actual launch and capture of signals is done with the internal launch/capture clock, which precedes LCLK by t<sub>LBKHKT</sub>.

Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

4. All signals are measured from  $BV_{DD}/2$  of the rising edge of local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 3.3-V signaling levels.

5. Input timings are measured at the pin.

6. The value of t<sub>LBOTOT</sub> is the measurement of the minimum time between the negation of LALE and any change in LAD.

7. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 8. Guaranteed by characterization.

- 9. Guaranteed by design.

Figure 27. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 8 or 16 (PLL Enabled)

#### Local Bus

Figure 28. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 8 or 16 (PLL Bypass Mode)

#### Serial RapidIO

| Characteristic              | Symbol                             | Rai   | nge    | Unit   | Notes                                                                      |  |  |  |

|-----------------------------|------------------------------------|-------|--------|--------|----------------------------------------------------------------------------|--|--|--|

| Characteristic              | Characteristic Symbol Unit Min Max |       | NOICES |        |                                                                            |  |  |  |

| Output voltage              | V <sub>O</sub>                     | -0.40 | 2.30   | V      | Voltage relative to COMMON of either signal comprising a differential pair |  |  |  |

| Differential output voltage | V <sub>DIFFPP</sub>                | 800   | 1600   | mVp-p  | —                                                                          |  |  |  |

| Deterministic jitter        | J <sub>D</sub>                     | —     | 0.17   | UI p-p | —                                                                          |  |  |  |

| Total jitter                | J <sub>T</sub>                     | —     | 0.35   | UI p-p | —                                                                          |  |  |  |

| Multiple output skew        | S <sub>MO</sub>                    | —     | 1000   | ps     | Skew at the transmitter output between lanes of a multilane link           |  |  |  |

| Unit interval               | UI                                 | 400   | 400    | ps     | ±100 ppm                                                                   |  |  |  |

## Table 64. Long Run Transmitter AC Timing Specifications—3.125 GBaud

| Characteristic              | Symbol              | Ra    | nge  | Unit   | Notes                                                                         |

|-----------------------------|---------------------|-------|------|--------|-------------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Onic   | NULES                                                                         |

| Output voltage              | V <sub>O</sub>      | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal<br>comprising a differential pair |

| Differential output voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mVp-p  | —                                                                             |

| Deterministic jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                             |

| Total jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                             |

| Multiple output skew        | S <sub>MO</sub>     | —     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link              |

| Unit interval               | UI                  | 320   | 320  | ps     | ±100 ppm                                                                      |

For each baud rate at which an LP-serial transmitter is specified to operate, the output eye pattern of the transmitter shall fall entirely within the unshaded portion of the transmitter output compliance mask shown in Figure 52 with the parameters specified in Table 65 when measured at the output pins of the device and the device is driving a  $100-\Omega \pm 5\%$  differential resistive load. The output eye pattern of an LP-serial

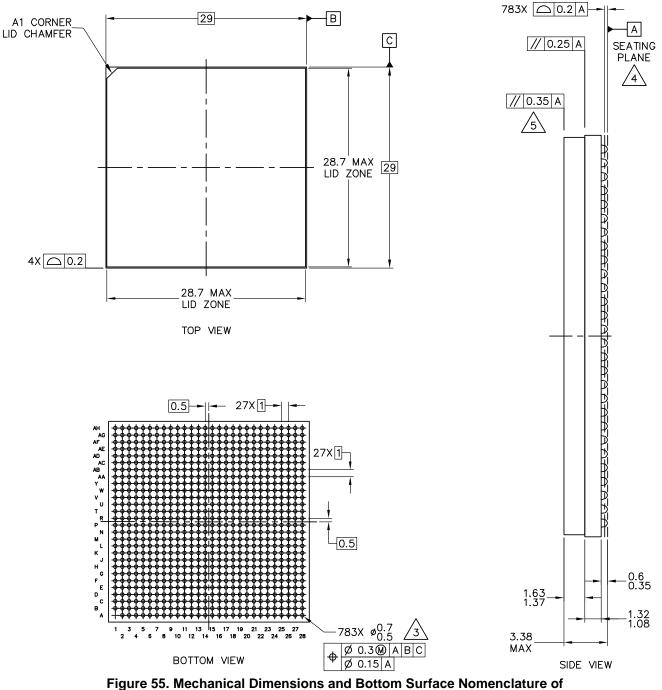

**Package Description**

# 19.2 Mechanical Dimensions of the HiCTE FC-CBGA and FC-PBGA with Full Lid

The following figures show the mechanical dimensions and bottom surface nomenclature for the MPC8548E HiCTE FC-CBGA and FC-PBGA packages.

the HiCTE FC-CBGA and FC-PBGA with Full Lid

Package Description

| Signal           | Package Pin Number                                                                                                                                                | Pin Type                                                          | Power<br>Supply  | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------|-------|

| LV <sub>DD</sub> | N8, R7, T9, U6                                                                                                                                                    | Power for<br>TSEC1 and<br>TSEC2<br>(2.5 V, 3.3 V)                 | LV <sub>DD</sub> |       |

| TV <sub>DD</sub> | W9, Y6                                                                                                                                                            | Power for<br>TSEC3 and<br>TSEC4<br>(2,5 V, 3.3 V)                 | TV <sub>DD</sub> | _     |

| GV <sub>DD</sub> | B3, B11, C7, C9, C14, C17, D4, D6, D10, D15,<br>E2, E8, E11, E18, F5, F12, F16, G3, G7, G9,<br>G11, H5, H12, H15, H17, J10, K3, K12, K16,<br>K18, L6, M4, M8, M13 | Power for<br>DDR1 and<br>DDR2 DRAM<br>I/O voltage<br>(1.8 V, 2.5) | GV <sub>DD</sub> |       |

| BV <sub>DD</sub> | C21, C24, C27, E20, E25, G19, G23, H26, J20                                                                                                                       | Power for local<br>bus (1.8 V,<br>2.5 V, 3.3 V)                   | BV <sub>DD</sub> |       |

| V <sub>DD</sub>  | M19, N12, N14, N16, N18, P11, P13, P15, P17,<br>P19, R12, R14, R16, R18, T11, T13, T15, T17,<br>T19, U12, U14, U16, U18, V17, V19                                 | Power for core<br>(1.1 V)                                         | V <sub>DD</sub>  |       |

| SV <sub>DD</sub> | L25, L27, M24, N28, P24, P26, R24, R27, T25,<br>V24, V26, W24, W27, Y25, AA28, AC27                                                                               | Core Power<br>for SerDes<br>transceivers<br>(1.1 V)               | SV <sub>DD</sub> | —     |

| XV <sub>DD</sub> | L20, L22, N23, P21, R22, T20, U23, V21, W22,<br>Y20                                                                                                               | Pad Power for<br>SerDes<br>transceivers<br>(1.1 V)                | XV <sub>DD</sub> |       |

| AVDD_LBIU        | J28                                                                                                                                                               | Power for local<br>bus PLL<br>(1.1 V)                             | _                | 26    |

| AVDD_PCI1        | AH21                                                                                                                                                              | Power for<br>PCI1 PLL<br>(1.1 V)                                  | _                | 26    |

| AVDD_PCI2        | AH22                                                                                                                                                              | Power for<br>PCI2 PLL<br>(1.1 V)                                  | _                | 26    |

| AVDD_CORE        | AH15                                                                                                                                                              | Power for<br>e500 PLL (1.1<br>V)                                  | _                | 26    |

| AVDD_PLAT        | AH19                                                                                                                                                              | PowerforCCB<br>PLL (1.1 V)                                        | —                | 26    |

| AVDD_SRDS        | U25                                                                                                                                                               | Power for<br>SRDSPLL<br>(1.1 V)                                   | _                | 26    |

| SENSEVDD         | M14                                                                                                                                                               | 0                                                                 | V <sub>DD</sub>  | 13    |

# Table 71. MPC8548E Pinout Listing (continued)

Package Description

| Table 72. MPC8547E Pinout Listing (continued | I) |

|----------------------------------------------|----|

|----------------------------------------------|----|

| Signal                 | Package Pin Number                     | Pin Type | Power<br>Supply  | Notes           |

|------------------------|----------------------------------------|----------|------------------|-----------------|

| Reserved               | U20, V22, W20, Y22                     | _        |                  | 15              |

| Reserved               | —                                      | —        | 15               |                 |

| SD_PLL_TPD             | U28                                    | 0        | XV <sub>DD</sub> | 24              |

| SD_REF_CLK             | T28                                    | I        | XV <sub>DD</sub> | —               |

| SD_REF_CLK             | T27                                    | I        | XV <sub>DD</sub> | —               |

| Reserved               | AC1, AC3                               | —        | _                | 2               |

| Reserved               | M26, V28                               | —        | —                | 32              |

| Reserved               | M25, V27                               | —        | —                | 34              |

| Reserved               | M20, M21, T22, T23                     | —        | —                | 38              |

| · · · · ·              | General-Purpose Output                 |          | l                | •               |

| GPOUT[24:31]           | K26, K25, H27, G28, H25, J26, K24, K23 | 0        | BV <sub>DD</sub> | —               |

| · · · ·                | System Control                         |          |                  | •               |

| HRESET                 | AG17                                   | I        | OV <sub>DD</sub> | —               |

| HRESET_REQ             | AG16                                   | 0        | OV <sub>DD</sub> | 29              |

| SRESET                 | AG20                                   | I        | OV <sub>DD</sub> | —               |

| CKSTP_IN               | AA9                                    | I        | OV <sub>DD</sub> | —               |

| CKSTP_OUT              | AA8                                    | 0        | OV <sub>DD</sub> | 2, 4            |

|                        | Debug                                  |          |                  |                 |

| TRIG_IN                | AB2                                    | I        | OV <sub>DD</sub> | —               |

| TRIG_OUT/READY/QUIESCE | AB1                                    | 0        | OV <sub>DD</sub> | 6, 9,<br>19, 29 |

| MSRCID[0:1]            | AE4, AG2                               | 0        | OV <sub>DD</sub> | 5, 6, 9         |

| MSRCID[2:4]            | AF3, AF1, AF2                          | 0        | OV <sub>DD</sub> | 6, 19,<br>29    |

| MDVAL                  | AE5                                    | 0        | OV <sub>DD</sub> | 6               |

| CLK_OUT                | AE21                                   | 0        | OV <sub>DD</sub> | 11              |

|                        | Clock                                  | •        |                  |                 |

| RTC                    | AF16                                   | I        | OV <sub>DD</sub> | —               |

| SYSCLK                 | AH17                                   | I        | OV <sub>DD</sub> | —               |

|                        | JTAG                                   | •        |                  |                 |

| ТСК                    | AG28                                   | I        | OV <sub>DD</sub> | —               |

| TDI                    | AH28                                   | I        | OV <sub>DD</sub> | 12              |

| TDO                    | AF28                                   | 0        | OV <sub>DD</sub> | —               |

| TMS                    | AH27                                   | I        | OV <sub>DD</sub> | 12              |

| TRST                   | AH23                                   | I        | OV <sub>DD</sub> | 12              |

# 20 Clocking

This section describes the PLL configuration of the device. Note that the platform clock is identical to the core complex bus (CCB) clock.

# 20.1 Clock Ranges

Table 75 through Table 77 provide the clocking specifications for the processor cores and Table 78, through Table 80 provide the clocking specifications for the memory bus.

|                               | Maximum Processor Core Frequency |      |          |      |          |      |      |       |  |

|-------------------------------|----------------------------------|------|----------|------|----------|------|------|-------|--|

| Characteristic                | 1000 MHz                         |      | 1200 MHz |      | 1333 MHz |      | Unit | Notes |  |

|                               | Min                              | Max  | Min      | Мах  | Min      | Max  |      |       |  |

| e500 core processor frequency |                                  | 1000 | 800      | 1200 | 800      | 1333 | MHz  | 1, 2  |  |

Table 75. Processor Core Clocking Specifications (MPC8548E and MPC8547E)

Notes:

Caution: The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

2.)The minimum e500 core frequency is based on the minimum platform frequency of 333 MHz.

## Table 76. Processor Core Clocking Specifications (MPC8545E)

|                               | Maximum Processor Core Frequency |     |          |      |          |      |      |       |  |

|-------------------------------|----------------------------------|-----|----------|------|----------|------|------|-------|--|

| Characteristic                | 800 MHz                          |     | 1000 MHz |      | 1200 MHz |      | Unit | Notes |  |

|                               | Min                              | Max | Min      | Max  | Min      | Max  |      |       |  |

| e500 core processor frequency | 800                              | 800 | 800      | 1000 | 800      | 1200 | MHz  | 1, 2  |  |

Notes:

1. **Caution:** The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

2.)The minimum e500 core frequency is based on the minimum platform frequency of 333 MHz.

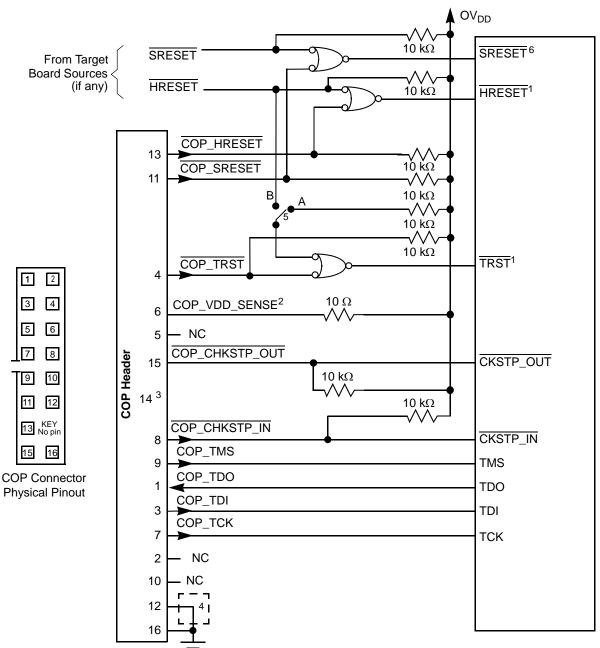

as shown in Figure 63. If this is not possible, the isolation resistor allows future access to  $\overline{\text{TRST}}$  in case a JTAG interface may need to be wired onto the system in future debug situations.

• No pull-up/pull-down is required for TDI, TMS, TDO, or TCK.

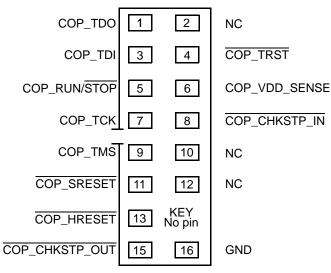

Figure 62. COP Connector Physical Pinout

#### System Design Information

#### Notes:

- 1. The COP port and target board must be able to independently assert HRESET and TRST to the processor in order to fully control the processor as shown here.

- 2. Populate this with a 10– $\Omega$  resistor for short-circuit/current-limiting protection.

- 3. The KEY location (pin 14) is not physically present on the COP header.

- 4. Although pin 12 is defined as a No-Connect, some debug tools may use pin 12 as an additional GND pin for improved signal integrity.

- This switch is included as a precaution for BSDL testing. The switch must be closed to position A during BSDL testing to avoid accidentally asserting the TRST line. If BSDL testing is not being performed, this switch must be closed to position B.

- 6. Asserting SRESET causes a machine check interrupt to the e500 core.

#### Figure 63. JTAG Interface Connection

# 24 Document Revision History

The following table provides a revision history for this hardware specification.

#### Rev. Date Substantive Change(s) Number • Updated Section 21.2, "Thermal for Version 2.1.1, 2.1.2, and 2.1.3 Silicon FC-PBGA with Full Lid and 9 02/2012 Version 3.1.x Silicon with Stamped Lid," with version 3.0 silicon information. Added Figure 56, "Mechanical Dimensions and Bottom Surface Nomenclature of the FC-PBGA with Stamped Lid." • Updated Table 87, "Part Numbering Nomenclature," with version 3.0 silicon information. Removed Note from Section 5.1. "Power-On Ramp Rate". • Changed the Table 10 title to "Power Supply Ramp Rate". • Removed table 11. • Updated the title of Section 21.2, "Thermal for Version 2.1.1, 2.1.2, and 2.1.3 Silicon FC-PBGA with Full Lid and Version 3.1.x Silicon with Stamped Lid" to include Thermal Version 2.1.3 and Version 3.1.x Silicon. Corrected the leaded Solder Ball composition in Table 70, "Package Parameters" • Updated Table 87, "Part Numbering Nomenclature," with Version 3.1.x silicon information. • Updated the Min and Max value of TDO in the valid times row of Table 44, "JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup>" from 4 and 25 to 2 and 10 respectively . 8 04/2011 Added Section 14.1, "GPOUT/GPIN Electrical Characteristics." • Updated Table 71, "MPC8548E Pinout Listing," Table 72, "MPC8547E Pinout Listing," Table 73, "MPC8545E Pinout Listing," and Table 74, "MPC8543E Pinout Listing," to reflect that the TDO signal is not driven during HRSET\* assertion. • Updated Table 87, "Part Numbering Nomenclature" with Ver. 2.1.3 silicon information. In Table 37, "MII Management AC Timing Specifications, modified the fifth row from "MDC to MDIO 7 09/2010 delay tMDKHDX (16 x tptb\_clk x 8) - 3 - (16 x tptb\_clk x 8) + 3" to "MDC to MDIO delay tMDKHDX $(16 \times tCCB \times 8) - 3 - (16 \times tCCB \times 8) + 3."$ Updated Figure 55, "Mechanical Dimensions and Bottom Surface Nomenclature of the HiCTE FC-CBGA and FC-PBGA with Full Lid and figure notes. 6 12/2009 • In Section 5.1, "Power-On Ramp Rate" added explanation that Power-On Ramp Rate is required to avoid falsely triggering ESD circuitry. In Table 13 changed required ramp rate from 545 V/s for MVREF and VDD/XVDD/SVDD to 3500 V/s for MVREF and 4000 V/s for VDD. • In Table 13 deleted ramp rate requirement for XVDD/SVDD. In Table 13 footnote 1 changed voltage range of concern from 0-400 mV to 20-500mV. In Table 13 added footnote 2 explaining that VDD voltage ramp rate is intended to control ramp rate of AVDD pins. 5 10/2009 • In Table 27, "GMII Receive AC Timing Specifications," changed duty cycle specification from 40/60 to 35/75 for RX CLK duty cycle. Updated tMDKHDX in Table 37, "MII Management AC Timing Specifications." • Added a reference to Revision 2.1.2. • Updated Table 55, "MII Management AC Timing Specifications." Added Section 5.1, "Power-On Ramp Rate."

## Table 88. Document Revision History

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4              | 04/2009 | <ul> <li>In Table 1, "Absolute Maximum Ratings <sup>1</sup>," and in Table 2, "Recommended Operating Conditions," moved text, "MII management voltage" from LV<sub>DD</sub>/TV<sub>DD</sub> to OV<sub>DD</sub>, added "Ethernet management" to OVDD row of input voltage section.</li> <li>In Table 5, "SYSCLK AC Timing Specifications," added notes 7 and 8 to SYSCLK frequency and cycle time.</li> <li>In Table 36, "MII Management DC Electrical Characteristics," changed all instances of LV<sub>DD</sub>/OV<sub>DD</sub> to OV<sub>DD</sub>.</li> <li>Modified Section 16, "High-Speed Serial Interfaces (HSSI)," to reflect that there is only one SerDes.</li> <li>Modified DDR clk rate min from 133 to 166 MHz.</li> <li>Modified note in Table 75, "Processor Core Clocking Specifications (MPC8548E and MPC8547E), "."</li> <li>In Table 56, "Differential Transmitter (TX) Output Specifications," modified equations in Comments column, and changed all instances of "LO" to "L0." Also added note 8.</li> <li>In Table 57, "Differential Receiver (RX) Input Specifications," modified equations in Comments column, and in note 3, changed "TRX-EYE-MEDIAN-to-MAX-JITTER," to "T<sub>RX-EYE-MEDIAN-to-MAX-JITTER</sub>."</li> <li>Modified Table 83, "Frequency Options of SYSCLK with Respect to Memory Bus Speeds."</li> <li>Added a note on Section 4.1, "System Clock Timing," to limit the SYSCLK to 100 MHz if the core frequency is less than 1200 MHz</li> <li>In Table 71, "MPC8543E Pinout ListingTable 72, "MPC8547E Pinout ListingTable 73, "MPC8545E Pinout ListingTable 74, "MPC8543E Pinout Listing," added note 5 to LA[28:31].</li> <li>Added note to Table 83, "Frequency Options of SYSCLK with Respect to Memory Bus Speeds."</li> </ul>                                                                                                 |

| 3              | 01/2009 | <ul> <li>[Section 4.6, "Platform Frequency Requirements for PCI-Express and Serial RapidIO." Changed minimum frequency equation to be 527 MHz for PCI x8.</li> <li>In Table 5, added note 7.</li> <li>Section 4.5, "Platform to FIFO Restrictions." Changed platform clock frequency to 4.2.</li> <li>Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1Gb Mbps)—GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics." Added MII after GMII and add 'or 2.5 V' after 3.3 V.</li> <li>In Table 23, modified table title to include GMII, MII, RMII, and TBI.</li> <li>In Table 24 and Table 25, changed clock period minimum to 5.3.</li> <li>In Table 26, Table 27, Table 28, Table 29, and Table 30, removed subtitle from table title.</li> <li>In Table 30 and Figure 15, changed all instances of PMA to TSEC<i>n</i>.</li> <li>In Table 34, Table 35, Figure 18, and Figure 20, changed all instances of REF_CLK to TSEC<i>n</i>_TX_CLK.</li> <li>In Table 36, changed all instances of OV<sub>DD</sub> to LV<sub>DD</sub>/TV<sub>DD</sub>.</li> <li>In Table 36, changed all instances of OV<sub>DD</sub> to LV<sub>DD</sub>/TV<sub>DD</sub>.</li> <li>In Table 37, "MII Management AC Timing Specifications," changed MDC minimum clock pulse width high from 32 to 48 ns.</li> <li>Added new section, Section 16, "High-Speed Serial Interfaces (HSSI)."</li> <li>Section 16.1, "DC Requirements for PCI Express SD_REF_CLK and SD_REF_CLK." Added new paragraph.</li> <li>Section 17.1, "DC Requirements for Serial RapidIO SD_REF_CLK and SD_REF_CLK." Added new paragraph.</li> <li>Added information to Figure 63, both in figure and in note.</li> <li>Section 22.3, "Decoupling Recommendations." Modified the recommendation.</li> <li>Table 87, "Part Numbering Nomenclature." In Silicon Version column added Ver. 2.1.2.</li> </ul> |

# Table 88. Document Revision History (continued)

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2              | 04/2008 | <ul> <li>Removed 1:1 support on Table 82, "e500 Core to CCB Clock Ratio."</li> <li>Removed MDM from Table 18, "DDR SDRAM Input AC Timing Specifications." MDM is an Output.</li> <li>Figure 57, "PLL Power Supply Filter Circuit with PLAT Pins" (AVDD_PLAT).</li> <li>Figure 58, "PLL Power Supply Filter Circuit with CORE Pins" (AVDD_CORE).</li> <li>Split Figure 59, "PLL Power Supply Filter Circuit with PCI/LBIU Pins," (formerly called just "PLL Power Supply Filter Circuit with PCI/LBIU Pins," (formerly called just "PLL Power Supply Filter Circuit with PCI/LBIU Pins," (formerly called just "PLL Power Supply Filter Circuit.") into three figures: the original (now specific for AVDD_PCI/AVDD_LBIU) and two new ones.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1              | 10/2007 | <ul> <li>Adjusted maximum SYSCLK frequency down in Table 5, "SYSCLK AC Timing Specifications" per device erratum GEN-13.</li> <li>Clarified notes to Table 6, "EC_GTX_CLK125 AC Timing Specifications."</li> <li>Added Section 4.4, "PCI/PCI-X Reference Clock Timing."</li> <li>Clarified descriptions and added PCI/PCI-X to Table 9, "PLL Lock Times."</li> <li>Removed support for 266 and 200 Mbps data rates per device erratum GEN-13 in Section 6, "DDR and DDR2 SDRAM."</li> <li>Clarified Note 4 of Table 19, "DDR SDRAM Output AC Timing Specifications."</li> <li>Clarified Note 4 of Table 22, "GMII, MII, RMII, and TBI DC Electrical Specifications."</li> <li>Clarified the reference clock used in Section 7.2, "DUART AC Electrical Characteristics."</li> <li>Corrected V<sub>IH</sub>(min) in Table 23, "GMII, MII, RMII, and TBI DC Electrical Characteristics."</li> <li>Corrected V<sub>IH</sub>(min) in Table 23, "GMII, MII, RMII, RGMII, RTBI, and FIFO DC Electrical Characteristics."</li> <li>Corrected V<sub>IH</sub>(min) in Table 36, "MII Management DC Electrical Characteristics."</li> <li>Corrected t<sub>MDC</sub>(min) in Table 37, "MII Management AC Timing Specifications."</li> <li>Updated parameters (BV<sub>DD</sub> = 3.3 V)—PLL Enabled" and Table 40, "Local Bus Timing Parameters (BV<sub>DD</sub> = 3.3 V)—PLL Enabled" and Table 40, "Local Bus Timing Parameters (BV<sub>DD</sub> = 3.3 V)—PLL Enabled" and Table 40, "Local Bus Timing Parameters (BV<sub>DD</sub> = 3.3 V)—PLL Enabled" and Table 40, "Local Bus Timing Parameters (BV<sub>DD</sub> = 3.3 V)—PLL Enabled"</li> <li>Updated parameter descriptions for t<sub>LBIVKH1</sub>, t<sub>LBIVKL2</sub>, t<sub>LBIXKH2</sub> in Table 42, "Local Bus Timing Parameters—PLL Bypassed." Note that t<sub>LBIVKL2</sub> and t<sub>LBIXKL2</sub> in Table 42, "Local Bus Timing Parameters—PLL Bypassed." Note that t<sub>LBIVKL2</sub> and t<sub>LBIXKL2</sub> in Table 42, "Local Bus Signals (PLL Bypass Mode)."</li> <li>Added LUPWAIT signal to Figure 23, "Local Bus Signals (PLL Enabled)" and Figure 24, "Local Bus Signals (PLL Bypass Mode)."</li> <li>Added LGTA signal to Figure 25, Figure 26, Figure 27 and Figure 28.</li> <li>Corrected LUPWAIT asser</li></ul> |

| 0              | 07/2007 | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

# Table 88. Document Revision History (continued)