# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 1.2GHz                                                                |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                                 |

| RAM Controllers                 | DDR, DDR2, SDRAM                                                      |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (4)                                                   |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                      |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | Cryptography, Random Number Generator                                 |

| Package / Case                  | 783-BBGA, FCBGA                                                       |

| Supplier Device Package         | 783-FCBGA (29x29)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8547ehxatg |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Dedicated single data rate SDRAM controller

- Parity support

- Default boot ROM chip select with configurable bus width (8, 16, or 32 bits)

- Four enhanced three-speed Ethernet controllers (eTSECs)

- Three-speed support (10/100/1000 Mbps)

- Four controllers designed to comply with IEEE Std. 802.3<sup>®</sup>, 802.3<sup>u</sup>, 802.3<sup>x</sup>, 802.3<sup>z</sup>, 802.3<sup>ac</sup>, and 802.3<sup>ab</sup>

- Support for various Ethernet physical interfaces:

- 1000 Mbps full-duplex IEEE 802.3 GMII, IEEE 802.3z TBI, RTBI, and RGMII

- 10/100 Mbps full and half-duplex IEEE 802.3 MII, IEEE 802.3 RGMII, and RMII

- Flexible configuration for multiple PHY interface configurations. See Section 8.1, "Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1Gb Mbps)—GMII/MII/TBI/RGMII/RTBI/RMII Electrical Characteristics," for more information.

- TCP/IP acceleration and QoS features available

- IP v4 and IP v6 header recognition on receive

- IP v4 header checksum verification and generation

- TCP and UDP checksum verification and generation

- Per-packet configurable acceleration

- Recognition of VLAN, stacked (queue in queue) VLAN, IEEE Std 802.2<sup>™</sup>, PPPoE session, MPLS stacks, and ESP/AH IP-security headers

- Supported in all FIFO modes

- Quality of service support:

- Transmission from up to eight physical queues

- Reception to up to eight physical queues

- Full- and half-duplex Ethernet support (1000 Mbps supports only full duplex):

- IEEE 802.3 full-duplex flow control (automatic PAUSE frame generation or software-programmed PAUSE frame generation and recognition)

- Programmable maximum frame length supports jumbo frames (up to 9.6 Kbytes) and IEEE Std. 802.1<sup>TM</sup> virtual local area network (VLAN) tags and priority

- VLAN insertion and deletion

- Per-frame VLAN control word or default VLAN for each eTSEC

- Extracted VLAN control word passed to software separately

- Retransmission following a collision

- CRC generation and verification of inbound/outbound frames

- Programmable Ethernet preamble insertion and extraction of up to 7 bytes

- MAC address recognition:

- Exact match on primary and virtual 48-bit unicast addresses

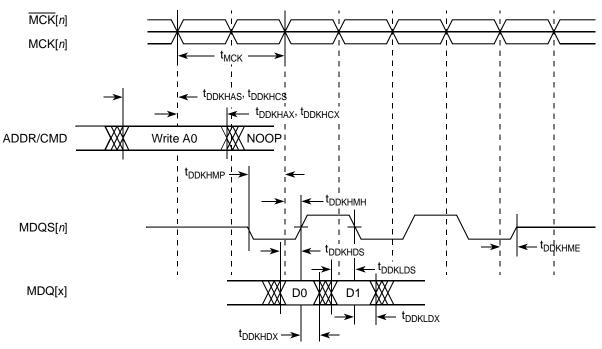

Figure 4 shows the DDR SDRAM output timing diagram.+

Figure 4. DDR SDRAM Output Timing Diagram

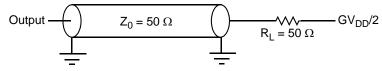

Figure 5 provides the AC test load for the DDR bus.

Figure 5. DDR AC Test Load

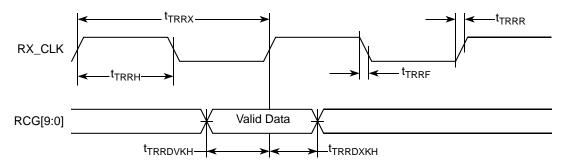

A timing diagram for TBI receive appears in Figure 16.

Figure 16. TBI Single-Clock Mode Receive AC Timing Diagram

### 8.2.6 RGMII and RTBI AC Timing Specifications

This table presents the RGMII and RTBI AC timing specifications.

| Parameter/Condition                                    | Symbol <sup>1</sup>                   | Min               | Тур | Max              | Unit |

|--------------------------------------------------------|---------------------------------------|-------------------|-----|------------------|------|

| Data to clock output skew (at transmitter)             | t <sub>SKRGT</sub> 5                  | -500 <sup>6</sup> | 0   | 500 <sup>6</sup> | ps   |

| Data to clock input skew (at receiver) <sup>2</sup>    | t <sub>SKRGT</sub>                    | 1.0               | _   | 2.8              | ns   |

| Clock period <sup>3</sup>                              | t <sub>RGT</sub> 5                    | 7.2               | 8.0 | 8.8              | ns   |

| Duty cycle for 10BASE-T and 100BASE-TX <sup>3, 4</sup> | t <sub>RGTH</sub> /t <sub>RGT</sub> 5 | 45                | 50  | 55               | %    |

| Rise time (20%–80%)                                    | t <sub>RGTR</sub> 5                   | _                 | _   | 0.75             | ns   |

| Fall time (20%–80%)                                    | t <sub>RGTF</sub> 5                   | _                 |     | 0.75             | ns   |

### Table 33. RGMII and RTBI AC Timing Specifications

Notes:

In general, the clock reference symbol representation for this section is based on the symbols RGT to represent RGMII and RTBI timing. For example, the subscript of t<sub>RGT</sub> represents the TBI (T) receive (RX) clock. Note also that the notation for rise (R) and fall (F) times follows the clock symbol that is being represented. For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (RGT).

- 2. This implies that PC board design requires clocks to be routed such that an additional trace delay of greater than 1.5 ns is added to the associated clock signal.

- 3. For 10 and 100 Mbps,  $t_{RGT}$  scales to 400 ns  $\pm$  40 ns and 40 ns  $\pm$  4 ns, respectively.

- 4. Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet's clock domains as long as the minimum duty cycle is not violated and stretching occurs for no more than three t<sub>RGT</sub> of the lowest speed transitioned between.

5. Guaranteed by characterization.

6. In rev 1.0 silicon, due to errata, t<sub>SKRGT</sub> is -650 ps (min) and 650 ps (max). See "eTSEC 10" in the device errata document.

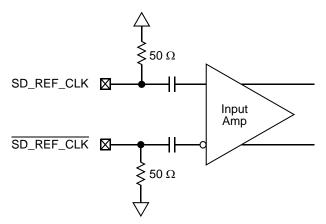

- The SD\_REF\_CLK and SD\_REF\_CLK are internally AC-coupled differential inputs as shown in Figure 39. Each differential clock input (SD\_REF\_CLK or SD\_REF\_CLK) has a 50-Ω termination to SGND\_SRDSn (xcorevss) followed by on-chip AC-coupling.

- The external reference clock driver must be able to drive this termination.

- The SerDes reference clock input can be either differential or single-ended. See the differential mode and single-ended mode description below for further detailed requirements.

- The maximum average current requirement that also determines the common mode voltage range:

- When the SerDes reference clock differential inputs are DC coupled externally with the clock driver chip, the maximum average current allowed for each input pin is 8 mA. In this case, the exact common mode input voltage is not critical as long as it is within the range allowed by the maximum average current of 8 mA (see the following bullet for more detail), since the input is AC-coupled on-chip.

- This current limitation sets the maximum common mode input voltage to be less than 0.4 V (0.4 V/50 = 8 mA) while the minimum common mode input level is 0.1 V above SGND\_SRDS*n* (xcorevss). For example, a clock with a 50/50 duty cycle can be produced by a clock driver with output driven by its current source from 0 to 16 mA (0–0.8 V), such that each phase of the differential input has a single-ended swing from 0 V to 800 mV with the common mode voltage at 400 mV.

- If the device driving the SD\_REF\_CLK and  $\overline{\text{SD}_{\text{REF}_{\text{CLK}}}}$  inputs cannot drive 50 Ω to SGND\_SRDS*n* (xcorevss) DC, or it exceeds the maximum input current limitations, then it must be AC-coupled off-chip.

- The input amplitude requirement:

- This requirement is described in detail in the following sections.

Figure 39. Receiver of SerDes Reference Clocks

### 16.2.2 DC Level Requirement for SerDes Reference Clocks

The DC level requirement for the SerDes reference clock inputs is different depending on the signaling mode used to connect the clock driver chip and SerDes reference clock inputs as described below:

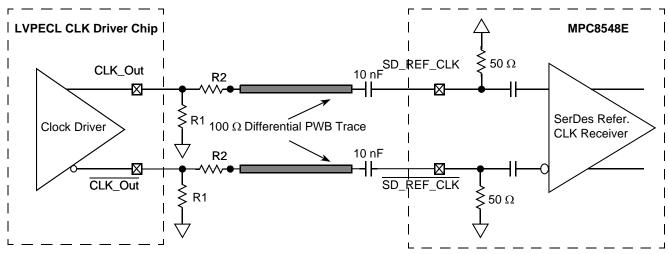

• Differential mode

to AC-coupling. Its value could be ranged from 140 to 240  $\Omega$  depending on the clock driver vendor's requirement. R2 is used together with the SerDes reference clock receiver's 50- $\Omega$  termination resistor to attenuate the LVPECL output's differential peak level such that it meets the SerDes reference clock's differential input amplitude requirement (between 200 and 800 mV differential peak). For example, if the LVPECL output's differential peak is 900 mV and the desired SerDes reference clock input amplitude is selected as 600 mV, the attenuation factor is 0.67, which requires R2 = 25  $\Omega$ . Consult a clock driver chip manufacturer to verify whether this connection scheme is compatible with a particular clock driver chip.

Figure 45. AC-Coupled Differential Connection with LVPECL Clock Driver (Reference Only)

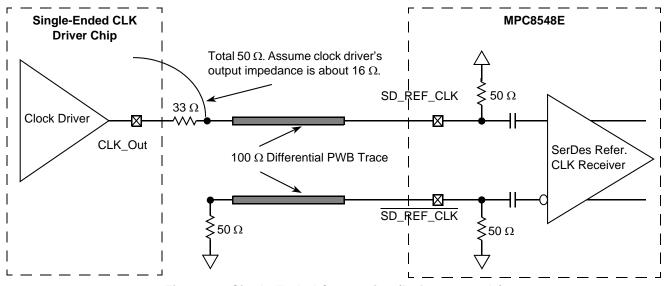

Figure 46 shows the SerDes reference clock connection reference circuits for a single-ended clock driver. It assumes the DC levels of the clock driver are compatible with the SerDes reference clock input's DC requirement.

Figure 46. Single-Ended Connection (Reference Only)

# 16.2.4 AC Requirements for SerDes Reference Clocks

The clock driver selected must provide a high quality reference clock with low phase noise and cycle-to-cycle jitter. Phase noise less than 100 kHz can be tracked by the PLL and data recovery loops and is less of a problem. Phase noise above 15 MHz is filtered by the PLL. The most problematic phase noise occurs in the 1–15 MHz range. The source impedance of the clock driver must be 50  $\Omega$  to match the transmission line and reduce reflections which are a source of noise to the system.

The detailed AC requirements of the SerDes reference clocks are defined by each interface protocol based on application usage. See the following sections for detailed information:

- Section 17.2, "AC Requirements for PCI Express SerDes Clocks"

- Section 18.2, "AC Requirements for Serial RapidIO SD\_REF\_CLK and SD\_REF\_CLK"

### 16.2.4.1 Spread Spectrum Clock

SD\_REF\_CLK/SD\_REF\_CLK are designed to work with a spread spectrum clock (+0% to -0.5% spreading at 30–33 kHz rate is allowed), assuming both ends have same reference clock. For better results, a source without significant unintended modulation must be used.

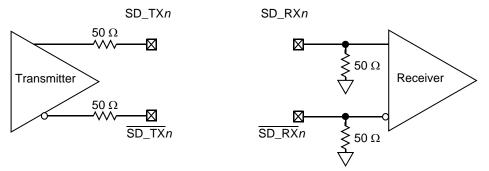

# 16.3 SerDes Transmitter and Receiver Reference Circuits

Figure 47 shows the reference circuits for SerDes data lane's transmitter and receiver.

Figure 47. SerDes Transmitter and Receiver Reference Circuits

The DC and AC specification of SerDes data lanes are defined in each interface protocol section below (PCI Express, Serial Rapid IO, or SGMII) in this document based on the application usage:

- Section 17, "PCI Express"

- Section 18, "Serial RapidIO"

Note that external an AC coupling capacitor is required for the above three serial transmission protocols with the capacitor value defined in the specification of each protocol section.

# 18.5 Explanatory Note on Transmitter and Receiver Specifications

AC electrical specifications are given for transmitter and receiver. Long- and short-run interfaces at three baud rates (a total of six cases) are described.

The parameters for the AC electrical specifications are guided by the XAUI electrical interface specified in Clause 47 of IEEE 802.3ae-2002.

XAUI has similar application goals to Serial RapidIO, as described in Section 8.1. The goal of this standard is that electrical designs for Serial RapidIO can reuse electrical designs for XAUI, suitably modified for applications at the baud intervals and reaches described herein.

# 18.6 Transmitter Specifications

LP-serial transmitter electrical and timing specifications are stated in the text and tables of this section.

The differential return loss, S11, of the transmitter in each case shall be better than:

- -10 dB for (baud frequency)/10 < Freq(f) < 625 MHz, and

- $-10 \text{ dB} + 10\log(f/625 \text{ MHz}) \text{ dB}$  for  $625 \text{ MHz} \le \text{Freq}(f) \le \text{baud}$  frequency

The reference impedance for the differential return loss measurements is  $100-\Omega$  resistive. Differential return loss includes contributions from on-chip circuitry, chip packaging, and any off-chip components related to the driver. The output impedance requirement applies to all valid output levels.

It is recommended that the 20%–80% rise/fall time of the transmitter, as measured at the transmitter output, in each case have a minimum value 60 ps.

It is recommended that the timing skew at the output of an LP-serial transmitter between the two signals that comprise a differential pair not exceed 25 ps at 1.25 GB, 20 ps at 2.50 GB, and 15 ps at 3.125 GB.

| Characteristic              | Symbol              | Ra    | nge  | Unit   | Notes                                                                         |  |

|-----------------------------|---------------------|-------|------|--------|-------------------------------------------------------------------------------|--|

| Characteristic              | Symbol              | Min   | Max  | Unit   | Notes                                                                         |  |

| Output voltage              | Vo                  | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal<br>comprising a differential pair |  |

| Differential output voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mV p-p | _                                                                             |  |

| Deterministic jitter        | J <sub>D</sub>      | _     | 0.17 | UI p-p | _                                                                             |  |

| Total jitter                | J <sub>T</sub>      | _     | 0.35 | UI p-p | _                                                                             |  |

| Multiple output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link              |  |

| Unit Interval               | UI                  | 800   | 800  | ps     | ±100 ppm                                                                      |  |

| Table 59. Short Run Transmitter | AC Timing Spe | cifications—1.25 GBaud |

|---------------------------------|---------------|------------------------|

|                                 | Ao mining ope |                        |

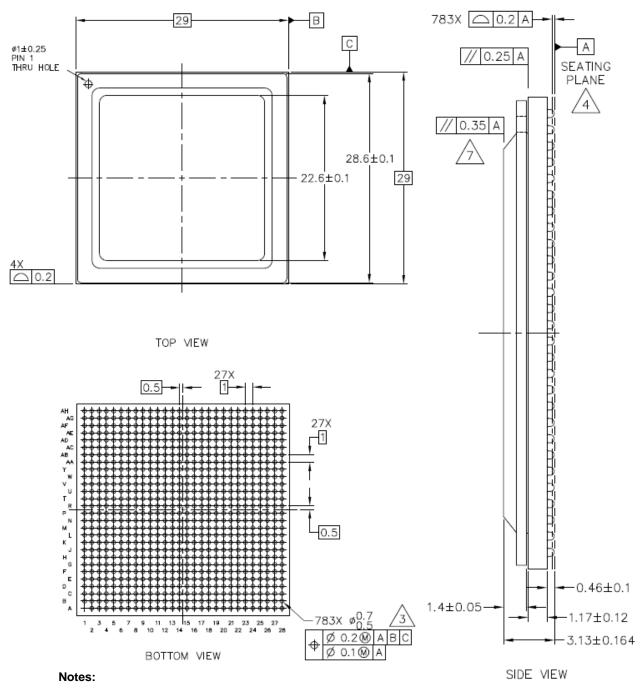

**Package Description**

- 1. All dimensions are in millimeters.

- 2. Dimensioning and tolerancing per ASME Y14.5M-1994.

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

- 5. Capacitors may not be present on all devices.

- 6. Caution must be taken not to short capacitors or exposed metal capacitor pads on package top.

- 7. Parallelism measurement shall exclude any effect of mark on top surface of package.

- 8. All dimensions are symmetric across the package center lines unless dimensioned otherwise.

#### Figure 56. Mechanical Dimensions and Bottom Surface Nomenclature of the FC-PBGA with Stamped Lid

| Signal                        | Package Pin Number                       | Pin Type | Power<br>Supply  | Notes          |

|-------------------------------|------------------------------------------|----------|------------------|----------------|

| Three                         | -Speed Ethernet Controller (Gigabit Ethe | ernet 2) |                  |                |

| TSEC2_RXD[7:0]                | P2, R2, N1, N2, P3, M2, M1, N3           | I        | LV <sub>DD</sub> | _              |

| TSEC2_TXD[7:0]                | N9, N10, P8, N7, R9, N5, R8, N6          | 0        | LV <sub>DD</sub> | 5, 9, 33       |

| TSEC2_COL                     | P1                                       | I        | LV <sub>DD</sub> |                |

| TSEC2_CRS                     | R6                                       | I/O      | LV <sub>DD</sub> | 20             |

| TSEC2_GTX_CLK                 | P6                                       | 0        | LV <sub>DD</sub> |                |

| TSEC2_RX_CLK                  | N4                                       | I        | LV <sub>DD</sub> | —              |

| TSEC2_RX_DV                   | P5                                       | I        | LV <sub>DD</sub> | —              |

| TSEC2_RX_ER                   | R1                                       | I        | LV <sub>DD</sub> | —              |

| TSEC2_TX_CLK                  | P10                                      | I        | LV <sub>DD</sub> | —              |

| TSEC2_TX_EN                   | P7                                       | 0        | LV <sub>DD</sub> | 30             |

| TSEC2_TX_ER                   | R10                                      | 0        | LV <sub>DD</sub> | 5, 9, 33       |

| Three                         | -Speed Ethernet Controller (Gigabit Ethe | ernet 3) |                  |                |

| TSEC3_TXD[3:0]                | V8, W10, Y10, W7                         | 0        | TV <sub>DD</sub> | 5, 9, 29       |

| TSEC3_RXD[3:0]                | Y1, W3, W5, W4                           | I        | TV <sub>DD</sub> | —              |

| TSEC3_GTX_CLK                 | W8                                       | 0        | TV <sub>DD</sub> | —              |

| TSEC3_RX_CLK                  | W2                                       | I        | TV <sub>DD</sub> | —              |

| TSEC3_RX_DV                   | W1                                       | I        | TV <sub>DD</sub> | —              |

| TSEC3_RX_ER                   | Y2                                       | I        | TV <sub>DD</sub> | —              |

| TSEC3_TX_CLK                  | V10                                      | I        | TV <sub>DD</sub> | —              |

| TSEC3_TX_EN                   | V9                                       | 0        | TV <sub>DD</sub> | 30             |

| Three                         | -Speed Ethernet Controller (Gigabit Ethe | ernet 4) |                  |                |

| TSEC4_TXD[3:0]/TSEC3_TXD[7:4] | AB8, Y7, AA7, Y8                         | 0        | TV <sub>DD</sub> | 1, 5, 9,<br>29 |

| TSEC4_RXD[3:0]/TSEC3_RXD[7:4] | AA1, Y3, AA2, AA4                        | I        | TV <sub>DD</sub> | 1              |

| TSEC4_GTX_CLK                 | AA5                                      | 0        | TV <sub>DD</sub> | —              |

| TSEC4_RX_CLK/TSEC3_COL        | Y5                                       | I        | TV <sub>DD</sub> | 1              |

| TSEC4_RX_DV/TSEC3_CRS         | AA3                                      | I/O      | TV <sub>DD</sub> | 1, 31          |

| TSEC4_TX_EN/TSEC3_TX_ER       | AB6                                      | 0        | TV <sub>DD</sub> | 1, 30          |

|                               | DUART                                    |          |                  |                |

| UART_CTS[0:1]                 | AB3, AC5                                 | I        | OV <sub>DD</sub> | —              |

| UART_RTS[0:1]                 | AC6, AD7                                 | 0        | OV <sub>DD</sub> | —              |

| UART_SIN[0:1]                 | AB5, AC7                                 | I        | OV <sub>DD</sub> | -              |

| UART_SOUT[0:1]                | AB7, AD8                                 | 0        | OV <sub>DD</sub> | 1 —            |

### Table 71. MPC8548E Pinout Listing (continued)

Package Description

| Signal                 | Package Pin Number                       | Pin Type | Power<br>Supply  | Notes           |

|------------------------|------------------------------------------|----------|------------------|-----------------|

|                        | I <sup>2</sup> C interface               |          |                  |                 |

| IIC1_SCL               | AG22                                     | I/O      | OV <sub>DD</sub> | 4, 27           |

| IIC1_SDA               | AG21                                     | I/O      | OV <sub>DD</sub> | 4, 27           |

| IIC2_SCL               | AG15                                     | I/O      | OV <sub>DD</sub> | 4, 27           |

| IIC2_SDA               | AG14                                     | I/O      | OV <sub>DD</sub> | 4, 27           |

|                        | SerDes                                   |          |                  |                 |

| SD_RX[0:7]             | M28, N26, P28, R26, W26, Y28, AA26, AB28 | I        | XV <sub>DD</sub> | —               |

| SD_RX[0:7]             | M27, N25, P27, R25, W25, Y27, AA25, AB27 | I        | XV <sub>DD</sub> | —               |

| SD_TX[0:7]             | M22, N20, P22, R20, U20, V22, W20, Y22   | 0        | XV <sub>DD</sub> | _               |

| SD_TX[0:7]             | M23, N21, P23, R21, U21, V23, W21, Y23   | 0        | XV <sub>DD</sub> | —               |

| SD_PLL_TPD             | U28                                      | 0        | XV <sub>DD</sub> | 24              |

| SD_REF_CLK             | T28                                      | I        | XV <sub>DD</sub> | 3               |

| SD_REF_CLK             | T27                                      | I        | XV <sub>DD</sub> | 3               |

| Reserved               | AC1, AC3                                 | _        | —                | 2               |

| Reserved               | M26, V28                                 | _        | —                | 32              |

| Reserved               | M25, V27                                 | _        | —                | 34              |

| Reserved               | M20, M21, T22, T23                       | —        | —                | 38              |

|                        | General-Purpose Output                   |          |                  | 1               |

| GPOUT[24:31]           | K26, K25, H27, G28, H25, J26, K24, K23   | 0        | BV <sub>DD</sub> | _               |

|                        | System Control                           |          |                  | 1               |

| HRESET                 | AG17                                     | I        | OV <sub>DD</sub> | _               |

| HRESET_REQ             | AG16                                     | 0        | OV <sub>DD</sub> | 29              |

| SRESET                 | AG20                                     | I        | OV <sub>DD</sub> | —               |

| CKSTP_IN               | AA9                                      | I        | OV <sub>DD</sub> | —               |

| CKSTP_OUT              | AA8                                      | 0        | OV <sub>DD</sub> | 2, 4            |

|                        | Debug                                    |          |                  | 1               |

| TRIG_IN                | AB2                                      | I        | OV <sub>DD</sub> | _               |

| TRIG_OUT/READY/QUIESCE | AB1                                      | 0        | OV <sub>DD</sub> | 6, 9,<br>19, 29 |

| MSRCID[0:1]            | AE4, AG2                                 | 0        | OV <sub>DD</sub> | 5, 6, 9         |

| MSRCID[2:4]            | AF3, AF1, AF2                            | 0        | OV <sub>DD</sub> | 6, 19,<br>29    |

| MDVAL                  | AE5                                      | 0        | OV <sub>DD</sub> | 6               |

| CLK_OUT                | AE21                                     | 0        | OV <sub>DD</sub> | 11              |

| Signal           | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin Type                                                            | Power<br>Supply  | Notes        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------|--------------|

|                  | DFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I I                                                                 |                  | 1            |

| L1_TSTCLK        | AC25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                                   | OV <sub>DD</sub> | 25           |

| L2_TSTCLK        | AE22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                                   | OV <sub>DD</sub> | 25           |

| LSSD_MODE        | AH20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                                   | OV <sub>DD</sub> | 25           |

| TEST_SEL         | AH14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | l                                                                   | OV <sub>DD</sub> | 25           |

|                  | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                     |                  |              |

| THERM0           | AG1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                                   | _                | 14           |

| THERM1           | AH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                                   | _                | 14           |

|                  | Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                     |                  |              |

| ASLEEP           | AH18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                   | OV <sub>DD</sub> | 9, 19,<br>29 |

|                  | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | I I                                                                 |                  | 1            |

| GND              | <ul> <li>A11, B7, B24, C1, C3, C5, C12, C15, C26, D8,<br/>D11, D16, D20, D22, E1, E5, E9, E12, E15, E17,<br/>F4, F26, G12, G15, G18, G21, G24, H2, H6, H8,<br/>H28, J4, J12, J15, J17, J27, K7, K9, K11, K27,<br/>L3, L5, L12, L16, N11, N13, N15, N17, N19, P4,<br/>P9, P12, P14, P16, P18, R11, R13, R15, R17,<br/>R19, T4, T12, T14, T16, T18, U8, U11, U13,<br/>U15, U17, U19, V4, V12, V18, W6, W19, Y4, Y9,<br/>Y11, Y19, AA6, AA14, AA17, AA22, AA23, AB4,<br/>AC2, AC11, AC19, AC26, AD5, AD9, AD22,<br/>AE3, AE14, AF6, AF10, AF13, AG8, AG27,<br/>K28, L24, L26, N24, N27, P25, R28, T24, T26,<br/>U24, V25, W28, Y24, Y26, AA24, AA27, AB25,<br/>AC28, L21, L23, N22, P20, R23, T21, U22, V20,<br/>W23, Y21, U27</li> </ul> |                                                                     | _                |              |

| OV <sub>DD</sub> | V16, W11, W14, Y18, AA13, AA21, AB11,<br>AB17, AB24, AC4, AC9, AC21, AD6, AD13,<br>AD17, AD19, AE10, AE8, AE24, AF4, AF12,<br>AF22, AF27, AG26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Power for PCI<br>and other<br>standards<br>(3.3 V)                  | OV <sub>DD</sub> | _            |

| LV <sub>DD</sub> | N8, R7, T9, U6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Power for<br>TSEC1 and<br>TSEC2<br>(2.5 V, 3.3 V)                   | LV <sub>DD</sub> | _            |

| TV <sub>DD</sub> | W9, Y6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Power for<br>TSEC3 and<br>TSEC4<br>(2,5 V, 3.3 V)                   | TV <sub>DD</sub> | _            |

| GV <sub>DD</sub> | B3, B11, C7, C9, C14, C17, D4, D6, D10, D15,<br>E2, E8, E11, E18, F5, F12, F16, G3, G7, G9,<br>G11, H5, H12, H15, H17, J10, K3, K12, K16,<br>K18, L6, M4, M8, M13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Power for<br>DDR1 and<br>DDR2 DRAM<br>I/O voltage<br>(1.8 V, 2.5 V) | GV <sub>DD</sub> |              |

Package Description

| Signal           | Package Pin Number                                                                                                                | Pin Type                                            | Power<br>Supply  | Notes |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------|-------|

| BV <sub>DD</sub> | C21, C24, C27, E20, E25, G19, G23, H26, J20                                                                                       | Power for local<br>bus (1.8 V,<br>2.5 V, 3.3 V)     | BV <sub>DD</sub> | _     |

| V <sub>DD</sub>  | M19, N12, N14, N16, N18, P11, P13, P15, P17,<br>P19, R12, R14, R16, R18, T11, T13, T15, T17,<br>T19, U12, U14, U16, U18, V17, V19 | Power for core<br>(1.1 V)                           | V <sub>DD</sub>  | _     |

| SV <sub>DD</sub> | L25, L27, M24, N28, P24, P26, R24, R27, T25,<br>V24, V26, W24, W27, Y25, AA28, AC27                                               | Core power for<br>SerDes<br>transceivers<br>(1.1 V) | SV <sub>DD</sub> | —     |

| XV <sub>DD</sub> | L20, L22, N23, P21, R22, T20, U23, V21, W22,<br>Y20                                                                               | Pad Power for<br>SerDes<br>transceivers<br>(1.1 V)  | XV <sub>DD</sub> | _     |

| AVDD_LBIU        | J28                                                                                                                               | Power for local<br>bus PLL<br>(1.1 V)               | _                | 26    |

| AVDD_PCI1        | AH21                                                                                                                              | Power for<br>PCI1 PLL<br>(1.1 V)                    | _                | 26    |

| AVDD_PCI2        | AH22                                                                                                                              | Power for<br>PCI2 PLL<br>(1.1 V)                    | _                | 26    |

| AVDD_CORE        | AH15                                                                                                                              | Power for<br>e500 PLL (1.1<br>V)                    | _                | 26    |

| AVDD_PLAT        | AH19                                                                                                                              | Powerfor CCB<br>PLL (1.1 V)                         |                  | 26    |

| AVDD_SRDS        | U25                                                                                                                               | Power for<br>SRDSPLL<br>(1.1 V)                     | _                | 26    |

| SENSEVDD         | M14                                                                                                                               | 0                                                   | V <sub>DD</sub>  | 13    |

| SENSEVSS         | M16                                                                                                                               | —                                                   |                  | 13    |

|                  | Analog Signals                                                                                                                    | <u>.</u>                                            | -                |       |

| MVREF            | A18                                                                                                                               | I<br>Reference<br>voltage signal<br>for DDR         | MVREF            | _     |

| SD_IMP_CAL_RX    | L28                                                                                                                               | I                                                   | 200 Ω to<br>GND  | —     |

| SD_IMP_CAL_TX    | AB26                                                                                                                              | I                                                   | 100 Ω to<br>GND  |       |

### Table 72. MPC8547E Pinout Listing (continued)

#### Table 72. MPC8547E Pinout Listing (continued)

| Signal     | Package Pin Number | Pin Type | Power<br>Supply | Notes |

|------------|--------------------|----------|-----------------|-------|

| SD_PLL_TPA | U26                | 0        | —               | 24    |

**Note:** All note references in this table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

Table 73 provides the pin-out listing for the MPC8545E 783 FC-PBGA package.

### NOTE

All note references in the following table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

| Signal                        | Package Pin Number                                                                                                                                                                                     | Pin Type | Power<br>Supply  | Notes    |  |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|--|

|                               | PCI1 and PCI2 (One 64-Bit or Two 32-Bit)                                                                                                                                                               |          |                  |          |  |

| PCI1_AD[63:32]/PCI2_AD[31:0]  | AB14, AC15, AA15, Y16, W16, AB16, AC16,<br>AA16, AE17, AA18, W18, AC17, AD16, AE16,<br>Y17, AC18, AB18, AA19, AB19, AB21, AA20,<br>AC20, AB20, AB22, AC22, AD21, AB23, AF23,<br>AD23, AE23, AC23, AC24 | I/O      | OV <sub>DD</sub> | 17       |  |

| PCI1_AD[31:0]                 | AH6, AE7, AF7, AG7, AH7, AF8, AH8, AE9,<br>AH9, AC10, AB10, AD10, AG10, AA10, AH10,<br>AA11, AB12, AE12, AG12, AH12, AB13, AA12,<br>AC13, AE13, Y14, W13, AG13, V14, AH13,<br>AC14, Y15, AB15          | I/O      | OV <sub>DD</sub> | 17       |  |

| PCI1_C_BE[7:4]/PCI2_C_BE[3:0] | AF15, AD14, AE15, AD15                                                                                                                                                                                 | I/O      | OV <sub>DD</sub> | 17       |  |

| PCI1_C_BE[3:0]                | AF9, AD11, Y12, Y13                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 17       |  |

| PCI1_PAR64/PCI2_PAR           | W15                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | —        |  |

| PCI1_GNT[4:1]                 | AG6, AE6, AF5, AH5                                                                                                                                                                                     | 0        | OV <sub>DD</sub> | 5, 9, 35 |  |

| PCI1_GNT0                     | AG5                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | —        |  |

| PCI1_IRDY                     | AF11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |  |

| PCI1_PAR                      | AD12                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | —        |  |

| PCI1_PERR                     | AC12                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |  |

| PCI1_SERR                     | V13                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2, 4     |  |

| PCI1_STOP                     | W12                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2        |  |

| PCI1_TRDY                     | AG11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |  |

| PCI1_REQ[4:1]                 | AH2, AG4, AG3, AH4                                                                                                                                                                                     | I        | OV <sub>DD</sub> | —        |  |

| PCI1_REQ0                     | AH3                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | —        |  |

| PCI1_CLK                      | AH26                                                                                                                                                                                                   | I        | OV <sub>DD</sub> | 39       |  |

| PCI1_DEVSEL                   | AH11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |  |

#### Table 73. MPC8545E Pinout Listing

| Signal        | Package Pin Number | Pin Type | Power<br>Supply | Notes |

|---------------|--------------------|----------|-----------------|-------|

| SD_IMP_CAL_RX | L28                | I        | 200 Ω to<br>GND | —     |

| SD_IMP_CAL_TX | AB26               | I        | 100 Ω to<br>GND | —     |

| SD_PLL_TPA    | U26                | 0        | _               | 24    |

#### Table 73. MPC8545E Pinout Listing (continued)

Note: All note references in this table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

Table 74 provides the pin-out listing for the MPC8543E 783 FC-PBGA package.

#### NOTE

All note references in the following table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

Table 74. MPC8543E Pinout Listing

| Signal         | Package Pin Number                                                                                                                                                                            | Pin Type | Power<br>Supply  | Notes    |  |  |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|--|--|--|--|--|

|                | PCI1 (One 32-Bit)                                                                                                                                                                             |          |                  |          |  |  |  |  |  |

| Reserved       | AB14, AC15, AA15, Y16, W16, AB16, AC16,<br>AA16, AE17, AA18, W18, AC17, AD16, AE16,<br>Y17, AC18,                                                                                             |          | _                | 110      |  |  |  |  |  |

| GPOUT[8:15]    | AB18, AA19, AB19, AB21, AA20, AC20, AB20,<br>AB22                                                                                                                                             | 0        | OV <sub>DD</sub> | —        |  |  |  |  |  |

| GPIN[8:15]     | AC22, AD21, AB23, AF23, AD23, AE23, AC23, AC24                                                                                                                                                | I        | OV <sub>DD</sub> | 111      |  |  |  |  |  |

| PCI1_AD[31:0]  | AH6, AE7, AF7, AG7, AH7, AF8, AH8, AE9,<br>AH9, AC10, AB10, AD10, AG10, AA10, AH10,<br>AA11, AB12, AE12, AG12, AH12, AB13, AA12,<br>AC13, AE13, Y14, W13, AG13, V14, AH13,<br>AC14, Y15, AB15 | I/O      | OV <sub>DD</sub> | 17       |  |  |  |  |  |

| Reserved       | AF15, AD14, AE15, AD15                                                                                                                                                                        | _        | -                | 110      |  |  |  |  |  |

| PCI1_C_BE[3:0] | AF9, AD11, Y12, Y13                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 17       |  |  |  |  |  |

| Reserved       | W15                                                                                                                                                                                           |          |                  | 110      |  |  |  |  |  |

| PCI1_GNT[4:1]  | AG6, AE6, AF5, AH5                                                                                                                                                                            | 0        | OV <sub>DD</sub> | 5, 9, 35 |  |  |  |  |  |

| PCI1_GNT0      | AG5                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | —        |  |  |  |  |  |

| PCI1_IRDY      | AF11                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | 2        |  |  |  |  |  |

| PCI1_PAR       | AD12                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | —        |  |  |  |  |  |

| PCI1_PERR      | AC12                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | 2        |  |  |  |  |  |

| PCI1_SERR      | V13                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2, 4     |  |  |  |  |  |

| PCI1_STOP      | W12                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |  |  |  |  |  |

Package Description

| Signal         | Package Pin Number                                                                                                                                                                                                                                                                                                            | Pin Type | Power<br>Supply  | Notes |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

| PCI1_TRDY      | AG11                                                                                                                                                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | 2     |

| PCI1_REQ[4:1]  | AH2, AG4, AG3, AH4                                                                                                                                                                                                                                                                                                            | I        | OV <sub>DD</sub> |       |

| PCI1_REQ0      | AH3                                                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | —     |

| PCI1_CLK       | AH26                                                                                                                                                                                                                                                                                                                          | I        | OV <sub>DD</sub> | 39    |

| PCI1_DEVSEL    | AH11                                                                                                                                                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | 2     |

| PCI1_FRAME     | AE11                                                                                                                                                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | 2     |

| PCI1_IDSEL     | AG9                                                                                                                                                                                                                                                                                                                           | I        | OV <sub>DD</sub> | _     |

| cfg_pci1_width | AF14                                                                                                                                                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | 112   |

| Reserved       | V15                                                                                                                                                                                                                                                                                                                           | —        | _                | 110   |

| Reserved       | AE28                                                                                                                                                                                                                                                                                                                          | —        | —                | 2     |

| Reserved       | AD26                                                                                                                                                                                                                                                                                                                          | —        | _                | 110   |

| Reserved       | AD25                                                                                                                                                                                                                                                                                                                          | —        | _                | 110   |

| Reserved       | AE26                                                                                                                                                                                                                                                                                                                          | —        | —                | 110   |

| cfg_pci1_clk   | AG24                                                                                                                                                                                                                                                                                                                          | I        | OV <sub>DD</sub> | 5     |

| Reserved       | AF25                                                                                                                                                                                                                                                                                                                          | —        | _                | 101   |

| Reserved       | AE25                                                                                                                                                                                                                                                                                                                          | _        | —                | 110   |

| Reserved       | AG25                                                                                                                                                                                                                                                                                                                          | —        | _                | 110   |

| Reserved       | AD24                                                                                                                                                                                                                                                                                                                          | —        | _                | 110   |

| Reserved       | AF24                                                                                                                                                                                                                                                                                                                          | —        | _                | 110   |

| Reserved       | AD27                                                                                                                                                                                                                                                                                                                          | —        | _                | 110   |

| Reserved       | AD28, AE27, W17, AF26                                                                                                                                                                                                                                                                                                         | —        | _                | 110   |

| Reserved       | AH25                                                                                                                                                                                                                                                                                                                          | —        | _                | 110   |

|                | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                                                    |          |                  |       |

| MDQ[0:63]      | MDQ[0:63]<br>L18, J18, K14, L13, L19, M18, L15, L14, A17,<br>B17, A13, B12, C18, B18, B13, A12, H18, F18,<br>J14, F15, K19, J19, H16, K15, D17, G16, K13,<br>D14, D18, F17, F14, E14, A7, A6, D5, A4, C8,<br>D7, B5, B4, A2, B1, D1, E4, A3, B2, D2, E3, F3,<br>G4, J5, K5, F6, G5, J6, K4, J1, K2, M5, M3, J3,<br>J2, L1, M6 |          | GV <sub>DD</sub> | _     |

| MECC[0:7]      | H13, F13, F11, C11, J13, G13, D12, M12                                                                                                                                                                                                                                                                                        | I/O      | GV <sub>DD</sub> |       |

| MDM[0:8]       | M17, C16, K17, E16, B6, C4, H4, K1, E13                                                                                                                                                                                                                                                                                       | 0        | $GV_DD$          |       |

| MDQS[0:8]      | M15, A16, G17, G14, A5, D3, H1, L2, C13                                                                                                                                                                                                                                                                                       | I/O      | GV <sub>DD</sub> |       |

| MDQS[0:8]      | L17, B16, J16, H14, C6, C2, H3, L4, D13                                                                                                                                                                                                                                                                                       | I/O      | GV <sub>DD</sub> | _     |

| MA[0:15]       | A8, F9, D9, B9, A9, L10, M10, H10, K10, G10,<br>B8, E10, B10, G6, A10, L11                                                                                                                                                                                                                                                    | 0        | GV <sub>DD</sub> | _     |

| MBA[0:2]       | F7, J7, M11                                                                                                                                                                                                                                                                                                                   | 0        | GV <sub>DD</sub> | —     |

### Table 74. MPC8543E Pinout Listing (continued)

| Signal                | Package Pin Number                    | Pin Type    | Power<br>Supply  | Notes    |

|-----------------------|---------------------------------------|-------------|------------------|----------|

| GPOUT[0:5]            | N9, N10, P8, N7, R9, N5               | 0           | LV <sub>DD</sub> | _        |

| cfg_dram_type0/GPOUT6 | R8                                    | 0           | LV <sub>DD</sub> | 5, 9     |

| GPOUT7                | N6                                    | 0           | LV <sub>DD</sub> | -        |

| Reserved              | P1                                    |             | _                | 104      |

| Reserved              | R6                                    |             | _                | 104      |

| Reserved              | P6                                    |             | _                | 15       |

| Reserved              | N4                                    | _           | _                | 105      |

| FIFO1_RXC2            | P5                                    | I           | LV <sub>DD</sub> | 104      |

| Reserved              | R1                                    | —           | _                | 104      |

| Reserved              | P10                                   | _           | _                | 105      |

| FIFO1_TXC2            | P7                                    | 0           | LV <sub>DD</sub> | 15       |

| cfg_dram_type1        | R10                                   | 0           | LV <sub>DD</sub> | 5, 9     |

| Three                 | ee-Speed Ethernet Controller (Gigabit | Ethernet 3) |                  |          |

| TSEC3_TXD[3:0]        | V8, W10, Y10, W7                      | 0           | TV <sub>DD</sub> | 5, 9, 2  |

| TSEC3_RXD[3:0]        | Y1, W3, W5, W4                        | I           | TV <sub>DD</sub> | _        |

| TSEC3_GTX_CLK         | W8                                    | 0           | TV <sub>DD</sub> | _        |

| TSEC3_RX_CLK          | W2                                    | I           | TV <sub>DD</sub> | <b>—</b> |

| TSEC3_RX_DV           | W1                                    | I           | TV <sub>DD</sub> | -        |

| TSEC3_RX_ER           | Y2                                    | I           | TV <sub>DD</sub> | _        |

| TSEC3_TX_CLK          | V10                                   | I           | TV <sub>DD</sub> | _        |

| TSEC3_TX_EN           | V9                                    | 0           | TV <sub>DD</sub> | 30       |

| TSEC3_TXD[7:4]        | AB8, Y7, AA7, Y8                      | 0           | TV <sub>DD</sub> | 5, 9, 2  |

| TSEC3_RXD[7:4]        | AA1, Y3, AA2, AA4                     | I           | TV <sub>DD</sub> | _        |

| Reserved              | AA5                                   | _           | _                | 15       |

| TSEC3_COL             | Y5                                    | I           | TV <sub>DD</sub> | - 1      |

| TSEC3_CRS             | AA3                                   | I/O         | TV <sub>DD</sub> | 31       |

| TSEC3_TX_ER           | AB6                                   | 0           | TV <sub>DD</sub> | -        |

|                       | DUART                                 |             |                  |          |

| UART_CTS[0:1]         | AB3, AC5                              | I           | OV <sub>DD</sub> | -        |

| UART_RTS[0:1]         | AC6, AD7                              | 0           | OV <sub>DD</sub> | 1 -      |

| UART_SIN[0:1]         | AB5, AC7                              |             | OV <sub>DD</sub> | <u> </u> |

| UART_SOUT[0:1]        | AB7, AD8                              | 0           | OV <sub>DD</sub> | <u> </u> |

|                       | I <sup>2</sup> C interface            | I           |                  | _1       |

| IIC1_SCL              | AG22                                  | I/O         | OV <sub>DD</sub> | 4, 27    |

|                       |                                       | I           |                  |          |

### Table 74. MPC8543E Pinout Listing (continued)

# 20.3 e500 Core PLL Ratio

This table describes the clock ratio between the e500 core complex bus (CCB) and the e500 core clock. This ratio is determined by the binary value of LBCTL, LALE, and LGPL2 at power up, as shown in this table.

| Binary Value of<br>LBCTL, LALE, LGPL2<br>Signals | e500 core:CCB Clock Ratio | Binary Value of<br>LBCTL, LALE, LGPL2<br>Signals | e500 core:CCB Clock Ratio |

|--------------------------------------------------|---------------------------|--------------------------------------------------|---------------------------|

| 000                                              | 4:1                       | 100                                              | 2:1                       |

| 001                                              | 9:2                       | 101                                              | 5:2                       |

| 010                                              | 010 Reserved              |                                                  | 3:1                       |

| 011                                              | 3:2                       | 111                                              | 7:2                       |

| Table 82. e500 | Core to CCB | <b>Clock Ratio</b> |

|----------------|-------------|--------------------|

|----------------|-------------|--------------------|

### 20.4 Frequency Options

Table 83This table shows the expected frequency values for the platform frequency when using a CCB clock to SYSCLK ratio in comparison to the memory bus clock speed.

| CCB to<br>SYSCLK Ratio |       | SYSCLK (MHz) |       |            |           |           |     |     |        |

|------------------------|-------|--------------|-------|------------|-----------|-----------|-----|-----|--------|

|                        | 16.66 | 25           | 33.33 | 41.66      | 66.66     | 83        | 100 | 111 | 133.33 |

|                        |       |              |       | Platform/C | CB Freque | ency (MHz | )   | •   |        |

| 2                      |       |              |       |            |           |           |     |     |        |

| 3                      |       |              |       |            |           |           |     | 333 | 400    |

| 4                      |       |              |       |            |           | 333       | 400 | 445 | 533    |

| 5                      |       |              |       |            | 333       | 415       | 500 |     |        |

| 6                      |       |              |       |            | 400       | 500       |     | -   |        |

| 8                      |       |              |       | 333        | 533       |           | -   |     |        |

| 9                      |       |              |       | 375        |           |           |     |     |        |

| 10                     |       |              | 333   | 417        |           |           |     |     |        |

| 12                     |       |              | 400   | 500        |           |           |     |     |        |

| 16                     |       | 400          | 533   |            |           |           |     |     |        |

| 20                     | 333   | 500          |       | -          |           |           |     |     |        |

Table 83. Frequency Options of SYSCLK with Respect to Memory Bus Speeds

**Note:** Due to errata Gen 13 the max sys clk frequency must not exceed 100 MHz if the core clk frequency is below 1200 MHz.

| Characteristic        | JEDEC Board | Symbol                | Value | Unit | Notes |

|-----------------------|-------------|-----------------------|-------|------|-------|

| Die junction-to-board | N/A         | $R_{	extsf{	heta}JB}$ | 5     | °C/W | 3     |

| Die junction-to-case  | N/A         | $R_{	ext{	heta}JC}$   | 0.8   | °C/W | 4     |

Table 85. Package Thermal Characteristics for FC-PBGA (continued)

Notes:

- 1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, airflow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-6 with the board (JESD51-7) horizontal.

- 3. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 4. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1). The cold plate temperature is used for the case temperature, measured value includes the thermal resistance of the interface layer.

# 21.3 Heat Sink Solution