# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 1.333GHz                                                              |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                                 |

| RAM Controllers                 | DDR, DDR2, SDRAM                                                      |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (4)                                                   |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                      |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | Cryptography, Random Number Generator                                 |

| Package / Case                  | 783-BBGA, FCBGA                                                       |

| Supplier Device Package         | 783-FCBGA (29x29)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8547ehxauj |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Performance monitor facility that is similar to, but separate from, the device performance monitor

The e500 defines features that are not implemented on this device. It also generally defines some features that this device implements more specifically. An understanding of these differences can be critical to ensure proper operations.

- 512-Kbyte L2 cache/SRAM

- Flexible configuration.

- Full ECC support on 64-bit boundary in both cache and SRAM modes

- Cache mode supports instruction caching, data caching, or both.

- External masters can force data to be allocated into the cache through programmed memory ranges or special transaction types (stashing).

- 1, 2, or 4 ways can be configured for stashing only.

- Eight-way set-associative cache organization (32-byte cache lines)

- Supports locking entire cache or selected lines. Individual line locks are set and cleared through Book E instructions or by externally mastered transactions.

- Global locking and Flash clearing done through writes to L2 configuration registers

- Instruction and data locks can be Flash cleared separately.

- SRAM features include the following:

- I/O devices access SRAM regions by marking transactions as snoopable (global).

- Regions can reside at any aligned location in the memory map.

- Byte-accessible ECC is protected using read-modify-write transaction accesses for smaller-than-cache-line accesses.

- Address translation and mapping unit (ATMU)

- Eight local access windows define mapping within local 36-bit address space.

- Inbound and outbound ATMUs map to larger external address spaces.

- Three inbound windows plus a configuration window on PCI/PCI-X and PCI Express

- Four inbound windows plus a default window on RapidIO<sup>™</sup>

- Four outbound windows plus default translation for PCI/PCI-X and PCI Express

- Eight outbound windows plus default translation for RapidIO with segmentation and sub-segmentation support

- DDR/DDR2 memory controller

- Programmable timing supporting DDR and DDR2 SDRAM

- 64-bit data interface

- Four banks of memory supported, each up to 4 Gbytes, to a maximum of 16 Gbytes

- DRAM chip configurations from 64 Mbits to 4 Gbits with ×8/×16 data ports

- Full ECC support

- Page mode support

- Up to 16 simultaneous open pages for DDR

#### DDR and DDR2 SDRAM

#### Table 19. DDR SDRAM Output AC Timing Specifications (continued)

At recommended operating conditions.

| Parameter         | Symbol <sup>1</sup> | Min  | Мах | Unit | Notes |

|-------------------|---------------------|------|-----|------|-------|

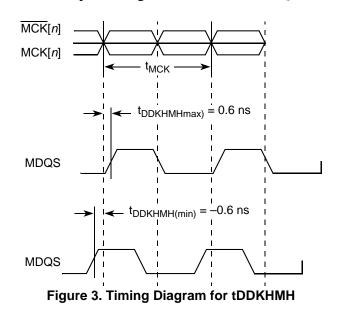

| MDQS epilogue end | t <sub>DDKHME</sub> | -0.6 | 0.6 | ns   | 6     |

Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

- 2. All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

- 3. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS.

- 4. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK[n] clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the MDQS override bits (called WR\_DATA\_DELAY) in the TIMING\_CFG\_2 register. This is typically set to the same delay as in DDR\_SDRAM\_CLK\_CNTL[CLK\_ADJUST]. The timing parameters listed in the table assume that these 2 parameters have been set to the same adjustment value. See the MPC8548E PowerQUICC III Integrated Processor Reference Manual for a description and understanding of the timing modifications enabled by use of these bits.

- Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe must be centered inside of the data eye at the pins of the microprocessor.

- 6. All outputs are referenced to the rising edge of MCK[*n*] at the pins of the microprocessor. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

#### NOTE

For the ADDR/CMD setup and hold specifications in Table 19, it is assumed that the clock control register is set to adjust the memory clocks by 1/2 applied cycle.

Figure 3 shows the DDR SDRAM output timing for the MCK to MDQS skew measurement (t<sub>DDKHMH</sub>).

DUART

# 7 DUART

This section describes the DC and AC electrical specifications for the DUART interface of the device.

# 7.1 DUART DC Electrical Characteristics

This table provides the DC electrical characteristics for the DUART interface.

# Table 20. DUART DC Electrical Characteristics

| Parameter                                                                 | Symbol          | Min  | Мах                    | Unit |

|---------------------------------------------------------------------------|-----------------|------|------------------------|------|

| High-level input voltage                                                  | V <sub>IH</sub> | 2    | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                   | V <sub>IL</sub> | -0.3 | 0.8                    | V    |

| Input current $(V_{IN}^{1} = 0 V \text{ or } V_{IN} = V_{DD})$            | I <sub>IN</sub> | —    | ±5                     | μA   |

| High-level output voltage ( $OV_{DD} = min, I_{OH} = -2 mA$ )             | V <sub>OH</sub> | 2.4  | —                      | V    |

| Low-level output voltage (OV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA) | V <sub>OL</sub> | —    | 0.4                    | V    |

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

# 7.2 DUART AC Electrical Specifications

This table provides the AC timing parameters for the DUART interface.

#### Table 21. DUART AC Timing Specifications

| Parameter         | Value                       | Unit | Notes   |

|-------------------|-----------------------------|------|---------|

| Minimum baud rate | f <sub>CCB</sub> /1,048,576 | baud | 1, 2    |

| Maximum baud rate | f <sub>CCB</sub> /16        | baud | 1, 2, 3 |

| Oversample rate   | 16                          |      | 1, 4    |

Notes:

1. Guaranteed by design.

2. f<sub>CCB</sub> refers to the internal platform clock.

3. Actual attainable baud rate is limited by the latency of interrupt processing.

4. The middle of a start bit is detected as the 8<sup>th</sup> sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each 16<sup>th</sup> sample.

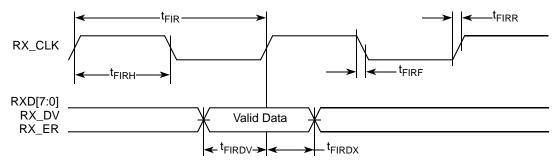

Figure 7. FIFO Receive AC Timing Diagram

# 8.2.2 GMII AC Timing Specifications

This section describes the GMII transmit and receive AC timing specifications.

# 8.2.2.1 GMII Transmit AC Timing Specifications

This table provides the GMII transmit AC timing specifications.

| Table 26. GMII Transmit AC Timing Specifications | Table 26 | <b>GMII</b> Transm | it AC Timing | Specifications |

|--------------------------------------------------|----------|--------------------|--------------|----------------|

|--------------------------------------------------|----------|--------------------|--------------|----------------|

| Parameter/Condition                               | Symbol <sup>1</sup>            | Min | Тур | Max | Unit |

|---------------------------------------------------|--------------------------------|-----|-----|-----|------|

| GMII data TXD[7:0], TX_ER, TX_EN setup time       | t <sub>GTKHDV</sub>            | 2.5 | —   | —   | ns   |

| GTX_CLK to GMII data TXD[7:0], TX_ER, TX_EN delay | <sup>t</sup> GTKHDX            | 0.5 | —   | 5.0 | ns   |

| GTX_CLK data clock rise time (20%–80%)            | t <sub>GTXR</sub> <sup>2</sup> | _   | —   | 1.0 | ns   |

| GTX_CLK data clock fall time (80%–20%)            | t <sub>GTXF</sub> <sup>2</sup> | _   | —   | 1.0 | ns   |

Notes:

The symbols used for timing specifications follow the pattern t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>GTKHDV</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) reaching the valid state (V) to state or setup time. Also, t<sub>GTKHDX</sub> symbolizes GMII transmit timing (GT) with respect to the high state (H) relative to the time date input signals (D) reaching the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GTX</sub> represents the GMII(G) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

2. Guaranteed by design.

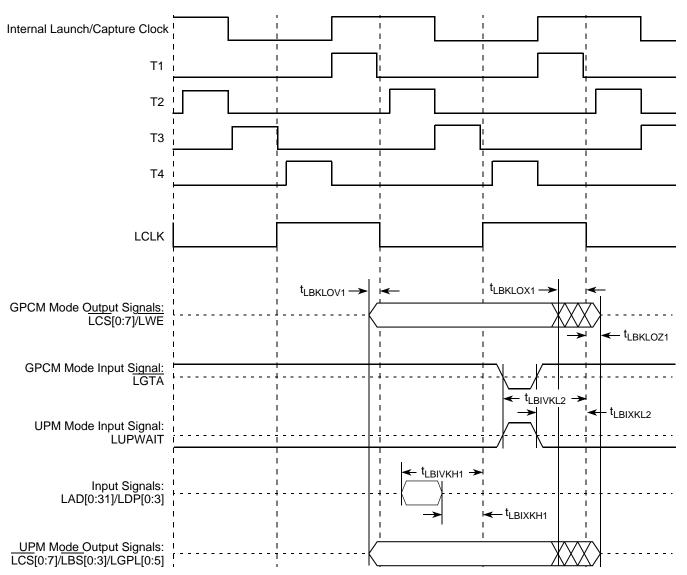

#### Local Bus

Figure 28. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 8 or 16 (PLL Bypass Mode)

| Parameter                                                                  | Symbol <sup>2</sup>                        | Min      | Мах      | Unit | Notes |

|----------------------------------------------------------------------------|--------------------------------------------|----------|----------|------|-------|

| Valid times:<br>Boundary-scan data<br>TDO                                  | t <sub>jtkldv</sub><br>t <sub>jtklov</sub> | 4<br>2   | 20<br>10 | ns   | 5     |

| Output hold times:<br>Boundary-scan data<br>TDO                            | t <sub>jtkldx</sub><br>t <sub>jtklox</sub> | 30<br>30 |          | ns   | 5     |

| JTAG external clock to output high impedance:<br>Boundary-scan data<br>TDO | t <sub>jtkldz</sub><br>t <sub>jtkloz</sub> | 3<br>3   | 19<br>9  | ns   | 5, 6  |

Table 44. JTAG AC Timing Specifications (Independent of SYSCLK)<sup>1</sup> (continued)

#### Notes:

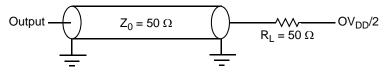

- All outputs are measured from the midpoint voltage of the falling/rising edge of t<sub>TCLK</sub> to the midpoint of the signal in question. The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Figure 29). Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

- 3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

- 5. Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

- 6. Guaranteed by design.

Figure 29 provides the AC test load for TDO and the boundary-scan outputs.

Figure 29. AC Test Load for the JTAG Interface

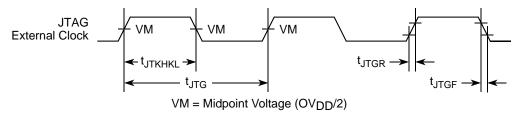

Figure 30 provides the JTAG clock input timing diagram.

Figure 30. JTAG Clock Input Timing Diagram

#### High-Speed Serial Interfaces (HSSI)

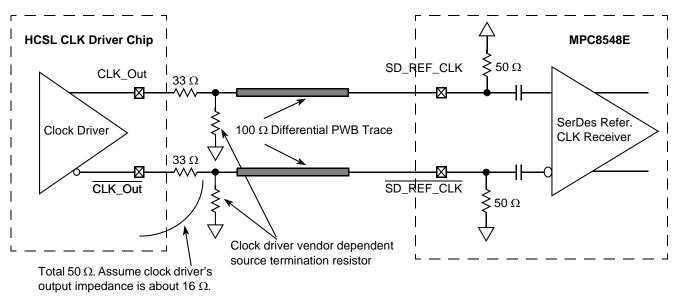

Figure 43 shows the SerDes reference clock connection reference circuits for HCSL type clock driver. It assumes that the DC levels of the clock driver chip is compatible with SerDes reference clock input's DC requirement.

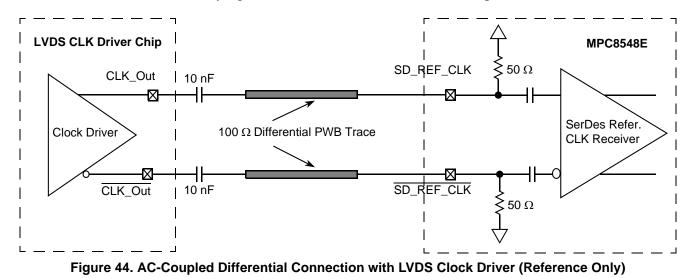

Figure 44 shows the SerDes reference clock connection reference circuits for LVDS type clock driver. Since LVDS clock driver's common mode voltage is higher than the SerDes reference clock input's allowed range (100–400 mV), AC-coupled connection scheme must be used. It assumes the LVDS output driver features 50- $\Omega$  termination resistor. It also assumes that the LVDS transmitter establishes its own common mode level without relying on the receiver or other external component.

Figure 45 shows the SerDes reference clock connection reference circuits for LVPECL type clock driver. Since LVPECL driver's DC levels (both common mode voltages and output swing) are incompatible with the SerDes reference clock input's DC requirement, AC-coupling must be used. Figure 45 assumes that the LVPECL clock driver's output impedance is 50  $\Omega$ . R1 is used to DC-bias the LVPECL outputs prior

#### Serial RapidIO

| Characteristic              | Symbol              | Ra    | nge  | Unit   | Notes                                                                      |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Unit   | Notes                                                                      |

| Output voltage              | Vo                  | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal comprising a differential pair |

| Differential output voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mV p-p | —                                                                          |

| Deterministic jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                          |

| Total jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                          |

| Multiple output skew        | S <sub>MO</sub>     | —     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |

| Unit interval               | UI                  | 400   | 400  | ps     | ±100 ppm                                                                   |

#### Table 61. Short Run Transmitter AC Timing Specifications—3.125 GBaud

| Characteristic              | Symbol              | Range |      | Unit   | Notes                                                                      |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Onic   | NOICS                                                                      |

| Output voltage              | Vo                  | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal comprising a differential pair |

| Differential output voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mVp-p  | -                                                                          |

| Deterministic jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | -                                                                          |

| Total jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                          |

| Multiple output skew        | S <sub>MO</sub>     | —     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |

| Unit interval               | UI                  | 320   | 320  | ps     | ±100 ppm                                                                   |

### Table 62. Long Run Transmitter AC Timing Specifications—1.25 GBaud

| Characteristic              | Symbol              | Range |      | Unit   | Notes                                                                      |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Onit   | NULES                                                                      |

| Output voltage              | V <sub>O</sub>      | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal comprising a differential pair |

| Differential output voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mVp-p  | —                                                                          |

| Deterministic jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                          |

| Total jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                          |

| Multiple output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |

| Unit interval               | UI                  | 800   | 800  | ps     | ±100 ppm                                                                   |

| Signal                        | Package Pin Number                       | Pin Type | Power<br>Supply  | Notes          |

|-------------------------------|------------------------------------------|----------|------------------|----------------|

| Three                         | -Speed Ethernet Controller (Gigabit Ethe | ernet 2) |                  |                |

| TSEC2_RXD[7:0]                | P2, R2, N1, N2, P3, M2, M1, N3           | I        | LV <sub>DD</sub> | _              |

| TSEC2_TXD[7:0]                | N9, N10, P8, N7, R9, N5, R8, N6          | 0        | LV <sub>DD</sub> | 5, 9, 33       |

| TSEC2_COL                     | TSEC2_COL P1                             |          |                  |                |

| TSEC2_CRS                     | R6                                       | I/O      | LV <sub>DD</sub> | 20             |

| TSEC2_GTX_CLK                 | P6                                       | 0        | LV <sub>DD</sub> |                |

| TSEC2_RX_CLK                  | N4                                       | I        | LV <sub>DD</sub> | —              |

| TSEC2_RX_DV                   | P5                                       | I        | LV <sub>DD</sub> | —              |

| TSEC2_RX_ER                   | R1                                       | I        | LV <sub>DD</sub> | —              |

| TSEC2_TX_CLK                  | P10                                      | I        | LV <sub>DD</sub> | —              |

| TSEC2_TX_EN                   | P7                                       | 0        | LV <sub>DD</sub> | 30             |

| TSEC2_TX_ER                   | R10                                      | 0        | LV <sub>DD</sub> | 5, 9, 33       |

| Three                         | -Speed Ethernet Controller (Gigabit Ethe | ernet 3) |                  |                |

| TSEC3_TXD[3:0]                | V8, W10, Y10, W7                         | 0        | TV <sub>DD</sub> | 5, 9, 29       |

| TSEC3_RXD[3:0]                | Y1, W3, W5, W4                           | I        | TV <sub>DD</sub> | —              |

| TSEC3_GTX_CLK                 | W8                                       | 0        | TV <sub>DD</sub> | —              |

| TSEC3_RX_CLK                  | W2                                       | I        | TV <sub>DD</sub> | —              |

| TSEC3_RX_DV                   | W1                                       | I        | TV <sub>DD</sub> | —              |

| TSEC3_RX_ER                   | Y2                                       | I        | TV <sub>DD</sub> | —              |

| TSEC3_TX_CLK                  | V10                                      | I        | TV <sub>DD</sub> | —              |

| TSEC3_TX_EN                   | V9                                       | 0        | TV <sub>DD</sub> | 30             |

| Three                         | -Speed Ethernet Controller (Gigabit Ethe | ernet 4) |                  |                |

| TSEC4_TXD[3:0]/TSEC3_TXD[7:4] | AB8, Y7, AA7, Y8                         | 0        | TV <sub>DD</sub> | 1, 5, 9,<br>29 |

| TSEC4_RXD[3:0]/TSEC3_RXD[7:4] | AA1, Y3, AA2, AA4                        | I        | TV <sub>DD</sub> | 1              |

| TSEC4_GTX_CLK                 | AA5                                      | 0        | TV <sub>DD</sub> | —              |

| TSEC4_RX_CLK/TSEC3_COL        | Y5                                       | I        | TV <sub>DD</sub> | 1              |

| TSEC4_RX_DV/TSEC3_CRS         | AA3                                      | I/O      | TV <sub>DD</sub> | 1, 31          |

| TSEC4_TX_EN/TSEC3_TX_ER       | AB6                                      | 0        | TV <sub>DD</sub> | 1, 30          |

|                               | DUART                                    |          |                  |                |

| UART_CTS[0:1]                 | AB3, AC5                                 | I        | OV <sub>DD</sub> | —              |

| UART_RTS[0:1]                 | AC6, AD7                                 | 0        | OV <sub>DD</sub> | —              |

| UART_SIN[0:1]                 | AB5, AC7                                 | I        | OV <sub>DD</sub> | -              |

| UART_SOUT[0:1]                | AB7, AD8                                 | 0        | OV <sub>DD</sub> | 1 —            |

# Table 71. MPC8548E Pinout Listing (continued)

# Table 71. MPC8548E Pinout Listing (continued)

| Signal                                                                                                             | Package Pin Number                                                                                                                                                                                                                                                                                     | Pin Type                                                      | Power<br>Supply                                                  | Notes                        |

|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------|------------------------------|

| 25.These are test signals for factory u                                                                            | ise only and must be pulled up (100 $\Omega$ –1 k $\Omega$ ) to                                                                                                                                                                                                                                        | OV <sub>DD</sub> for normal                                   | machine oper                                                     | ration.                      |

| 26.Independent supplies derived from                                                                               | n board V <sub>DD</sub> .                                                                                                                                                                                                                                                                              |                                                               |                                                                  |                              |

| 27.Recommend a pull-up resistor (~1                                                                                | $k\Omega$ ) be placed on this pin to $OV_{DD}$ .                                                                                                                                                                                                                                                       |                                                               |                                                                  |                              |

|                                                                                                                    | oul <u>led down du</u> ring power-on reset: TSEC3_TXD<br>Y/QUIESCE, MSRCID[2:4], ASLEEP.                                                                                                                                                                                                               | [3], TSEC4_TXD                                                | 93/TSEC3_TX                                                      | D7,                          |

| 30.This pin requires an external 4.7-ks driven.                                                                    | 2 pull-down resistor to prevent PHY from seeing a                                                                                                                                                                                                                                                      | valid transmit en                                             | able before it i                                                 | s active                     |

| 31.This pin is only an output in eTSE                                                                              | C3 FIFO mode when used as Rx flow control.                                                                                                                                                                                                                                                             |                                                               |                                                                  |                              |

| 32. These pins must be connected to 2                                                                              | XV <sub>DD</sub> .                                                                                                                                                                                                                                                                                     |                                                               |                                                                  |                              |

| 33. <u>TSEC2_</u> TXD1, TSEC2_TX_ER ar<br>HRESET assertion.                                                        | e multiplexed as cfg_dram_type[0:1]. They must                                                                                                                                                                                                                                                         | be valid at powe                                              | er-up, even bet                                                  | fore                         |

| 34.These pins must be pulled to grou                                                                               | nd through a 300- $\Omega$ (±10%) resistor.                                                                                                                                                                                                                                                            |                                                               |                                                                  |                              |

| down to select external arbiter if the<br>connect' or terminated through 2–1<br>connected to any other PCI device. | er the POR config pin that selects between inter<br>ere is any other PCI device connected on the PC<br>0 k $\Omega$ pull-up resistors with the default of internal<br>. The PCI block drives the PCI <i>n</i> _AD pins if it is con-<br>thether it is disabled via the DEVDISR register of<br>the bus. | l bus, or leave th<br>arbiter if the PC<br>onfigured to be th | e PCI <i>n_</i> AD pi<br><i>n_</i> AD pins are<br>e PCI arbiter– | ns as 'n<br>e not<br>–throug |

|                                                                                                                    | $2-\Omega$ precision 1% resistor and MDIC1 is connector automatic calibration of the DDR IOs.                                                                                                                                                                                                          | ed to GV <sub>DD</sub> throu                                  | gh an 18.2-Ω                                                     | precisio                     |

| 38.These pins must be left floating.                                                                               |                                                                                                                                                                                                                                                                                                        |                                                               |                                                                  |                              |

| 39. If PCI1 or PCI2 is configured as P<br>Otherwise the processor will not be                                      | CI asynchronous mode, a valid clock must be pr<br>oot up.                                                                                                                                                                                                                                              | ovided on pin PC                                              | CI1_CLK or PC                                                    | CI2_CL                       |

| 40.These pins must be connected to                                                                                 | GND.                                                                                                                                                                                                                                                                                                   |                                                               |                                                                  |                              |

| 101.This pin requires an external 4.7-                                                                             | $k\Omega$ resistor to GND.                                                                                                                                                                                                                                                                             |                                                               |                                                                  |                              |

| 102.For Rev. 2.x silicon, DMA_DACK<br>POR configuration are don't care.                                            | [0:1] must be 0b11 during POR configuration; for                                                                                                                                                                                                                                                       | r rev. 1.x silicon, t                                         | the pin values                                                   | during                       |

| 103.If these pins are not used as GPI<br>2–10 kΩ resistors.                                                        | Nn (general-purpose input), they must be pulled                                                                                                                                                                                                                                                        | low (to GND) or                                               | high (to LV <sub>DD</sub> )                                      | ) throug                     |

| 104.These must be pulled low to GNI                                                                                | D through 2–10 k $\Omega$ resistors if they are not used.                                                                                                                                                                                                                                              |                                                               |                                                                  |                              |

|                                                                                                                    | to $\text{LV}_{\text{DD}}$ through 2–10 k $\Omega$ resistors if they are no                                                                                                                                                                                                                            |                                                               |                                                                  |                              |

| 106.For rev. 2.x silicon, DMA_DACK[(<br>configuration are don't care.                                              | ):1] must be 0b10 during POR configuration; for re                                                                                                                                                                                                                                                     | ev. 1.x silicon, the                                          | pin values du                                                    | ring PO                      |

| 107.For rev. 2.x silicon, DMA_DACK[0 configuration are don't care.                                                 | ):1] must be 0b01 during POR configuration; for re                                                                                                                                                                                                                                                     | ev. 1.x silicon, the                                          | pin values du                                                    | ring PO                      |

| 108.For rev. 2.x silicon, DMA_DACK[C configuration are don't care.                                                 | 0:1] must be 0b11 during POR configuration; for re                                                                                                                                                                                                                                                     | ev. 1.x silicon, the                                          | pin values du                                                    | ring PO                      |

| 109.This is a test signal for factory us                                                                           | e only and must be pulled down (100 $\Omega$ – 1 k $\Omega$ )                                                                                                                                                                                                                                          | to GND for norm                                               | al machine op                                                    | eration.                     |

| 110.These pins must be pulled high to                                                                              | o OV <sub>DD</sub> through 2–10 k $\Omega$ resistors.                                                                                                                                                                                                                                                  |                                                               |                                                                  |                              |

| 111.If these pins are not used as GPII 2–10 k $\Omega$ resistors.                                                  | Nn (general-purpose input), they must be pulled                                                                                                                                                                                                                                                        | low (to GND) or I                                             | high (to OV <sub>DD</sub> )                                      | ) throug                     |

| 112.This pin must not be pulled down                                                                               | during POR configuration.                                                                                                                                                                                                                                                                              |                                                               |                                                                  |                              |

|                                                                                                                    |                                                                                                                                                                                                                                                                                                        |                                                               |                                                                  |                              |

# Table 73. MPC8545E Pinout Listing (continued)

| Signal                       | Package Pin Number                                                                                                                                                                                                                                                                                               | Pin Type | Power<br>Supply  | Notes    |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

| PCI1_FRAME                   | AE11                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_IDSEL                   | AG9                                                                                                                                                                                                                                                                                                              | I        | OV <sub>DD</sub> | —        |

| PCI1_REQ64/PCI2_FRAME        | AF14                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2, 5, 10 |

| PCI1_ACK64/PCI2_DEVSEL       | V15                                                                                                                                                                                                                                                                                                              | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_CLK                     | AE28                                                                                                                                                                                                                                                                                                             | l        | OV <sub>DD</sub> | 39       |

| PCI2_IRDY                    | AD26                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_PERR                    | AD25                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_GNT[4:1]                | AE26, AG24, AF25, AE25                                                                                                                                                                                                                                                                                           | 0        | OV <sub>DD</sub> | 5, 9, 35 |

| PCI2_GNT0                    | AG25                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | _        |

| PCI2_SERR                    | AD24                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2,4      |

| PCI2_STOP                    | AF24                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_TRDY                    | AD27                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_REQ[4:1]                | AD28, AE27, W17, AF26                                                                                                                                                                                                                                                                                            | l        | OV <sub>DD</sub> | —        |

| PCI2_REQ0                    | AH25                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | _        |

|                              | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                                       |          | •                | •        |

| MDQ[0:63]                    | L18, J18, K14, L13, L19, M18, L15, L14, A17,<br>B17, A13, B12, C18, B18, B13, A12, H18, F18,<br>J14, F15, K19, J19, H16, K15, D17, G16, K13,<br>D14, D18, F17, F14, E14, A7, A6, D5, A4, C8,<br>D7, B5, B4, A2, B1, D1, E4, A3, B2, D2, E3, F3,<br>G4, J5, K5, F6, G5, J6, K4, J1, K2, M5, M3, J3,<br>J2, L1, M6 | I/O      | GV <sub>DD</sub> | _        |

| MECC[0:7]                    | H13, F13, F11, C11, J13, G13, D12, M12                                                                                                                                                                                                                                                                           | I/O      | GV <sub>DD</sub> | _        |

| MDM[0:8]                     | M17, C16, K17, E16, B6, C4, H4, K1, E13                                                                                                                                                                                                                                                                          | 0        | GV <sub>DD</sub> | _        |

| MDQS[0:8]                    | M15, A16, G17, G14, A5, D3, H1, L2, C13                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> | _        |

| MDQS[0:8]                    | L17, B16, J16, H14, C6, C2, H3, L4, D13                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> | _        |

| MA[0:15]                     | A8, F9, D9, B9, A9, L10, M10, H10, K10, G10,<br>B8, E10, B10, G6, A10, L11                                                                                                                                                                                                                                       | 0        | GV <sub>DD</sub> | —        |

| MBA[0:2]                     | F7, J7, M11                                                                                                                                                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —        |

| MWE                          | E7                                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub> | _        |

| MCAS                         | H7                                                                                                                                                                                                                                                                                                               | 0        | GV <sub>DD</sub> | _        |

| MRAS                         | MRAS L8                                                                                                                                                                                                                                                                                                          |          | GV <sub>DD</sub> | _        |

| MCKE[0:3] F10, C10, J11, H11 |                                                                                                                                                                                                                                                                                                                  | 0        | GV <sub>DD</sub> | 11       |

| MCS[0:3]                     | MCS[0:3] K8, J8, G8, F8                                                                                                                                                                                                                                                                                          |          | GV <sub>DD</sub> | —        |

| MCK[0:5]                     | H9, B15, G2, M9, A14, F1                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub> | -        |

| MCK[0:5]                     | J9, A15, G1, L9, B14, F2                                                                                                                                                                                                                                                                                         | 0        | GV <sub>DD</sub> | —        |

| MODT[0:3]                    | E6, K6, L7, M7                                                                                                                                                                                                                                                                                                   | 0        | GV <sub>DD</sub> |          |

| Signal         | Package Pin Number                       | Pin Type   | Power<br>Supply  | Notes    |

|----------------|------------------------------------------|------------|------------------|----------|

| FIFO1_RXC2     | P5                                       | I          | LV <sub>DD</sub> | 104      |

| Reserved       | R1                                       | —          | _                | 104      |

| Reserved       | P10                                      | —          | —                | 105      |

| FIFO1_TXC2     | P7                                       | 0          | LV <sub>DD</sub> | 15       |

| cfg_dram_type1 | R10                                      | I          | LV <sub>DD</sub> | 5        |

| Thre           | ee-Speed Ethernet Controller (Gigabit Et | thernet 3) |                  |          |

| TSEC3_TXD[3:0] | V8, W10, Y10, W7                         | 0          | TV <sub>DD</sub> | 5, 9, 29 |

| TSEC3_RXD[3:0] | Y1, W3, W5, W4                           | I          | TV <sub>DD</sub> |          |

| TSEC3_GTX_CLK  | W8                                       | 0          | TV <sub>DD</sub> |          |

| TSEC3_RX_CLK   | W2                                       | I          | TV <sub>DD</sub> | —        |

| TSEC3_RX_DV    | W1                                       | I          | TV <sub>DD</sub> | _        |

| TSEC3_RX_ER    | Y2                                       | I          | TV <sub>DD</sub> | _        |

| TSEC3_TX_CLK   | V10                                      | I          | TV <sub>DD</sub> | _        |

| TSEC3_TX_EN    | V9                                       | 0          | TV <sub>DD</sub> | 30       |

| TSEC3_TXD[7:4] | AB8, Y7, AA7, Y8                         | 0          | TV <sub>DD</sub> | 5, 9, 29 |

| TSEC3_RXD[7:4] | AA1, Y3, AA2, AA4                        | I          | TV <sub>DD</sub> | _        |

| Reserved       | AA5                                      | —          | —                | 15       |

| TSEC3_COL      | Y5                                       | I          | TV <sub>DD</sub> | —        |

| TSEC3_CRS      | AA3                                      | I/O        | TV <sub>DD</sub> | 31       |

| TSEC3_TX_ER    | AB6                                      | 0          | TV <sub>DD</sub> | —        |

|                | DUART                                    |            | •                |          |

| UART_CTS[0:1]  | AB3, AC5                                 | I          | OV <sub>DD</sub> |          |

| UART_RTS[0:1]  | AC6, AD7                                 | 0          | OV <sub>DD</sub> |          |

| UART_SIN[0:1]  | AB5, AC7                                 | I          | OV <sub>DD</sub> |          |

| UART_SOUT[0:1] | AB7, AD8                                 | 0          | OV <sub>DD</sub> | _        |

| <b>I</b>       | I <sup>2</sup> C interface               |            |                  | 1        |

| IIC1_SCL       | AG22                                     | I/O        | OV <sub>DD</sub> | 4, 27    |

| IIC1_SDA       | AG21                                     | I/O        | OV <sub>DD</sub> | 4, 27    |

| IIC2_SCL       | AG15                                     | I/O        | OV <sub>DD</sub> | 4, 27    |

| IIC2_SDA       | AG14                                     | I/O        | OV <sub>DD</sub> | 4, 27    |

|                | SerDes                                   | 1          |                  |          |

| SD_RX[0:3]     | M28, N26, P28, R26                       | I          | XV <sub>DD</sub> | _        |

| SD_RX[0:3]     | M27, N25, P27, R25                       | I          | XV <sub>DD</sub> | —        |

| SD_TX[0:3]     | M22, N20, P22, R20                       | 0          | XV <sub>DD</sub> |          |

| Signal                 | Package Pin Number                     | Pin Type | Power<br>Supply  | Notes           |

|------------------------|----------------------------------------|----------|------------------|-----------------|

| SD_TX[0:3]             | M23, N21, P23, R21                     | 0        | XV <sub>DD</sub> | —               |

| Reserved               | W26, Y28, AA26, AB28                   | _        | _                | 40              |

| Reserved               | W25, Y27, AA25, AB27                   | —        | —                | 40              |

| Reserved               | U20, V22, W20, Y22                     | —        | —                | 15              |

| Reserved               | U21, V23, W21, Y23                     | —        | —                | 15              |

| SD_PLL_TPD             | U28                                    | 0        | XV <sub>DD</sub> | 24              |

| SD_REF_CLK             | T28                                    | I        | XV <sub>DD</sub> | —               |

| SD_REF_CLK             | T27                                    | I        | XV <sub>DD</sub> | —               |

| Reserved               | AC1, AC3                               | _        | —                | 2               |

| Reserved               | M26, V28                               | _        | —                | 32              |

| Reserved               | M25, V27                               | _        | —                | 34              |

| Reserved               | M20, M21, T22, T23                     | _        | —                | 38              |

|                        | General-Purpose Output                 |          |                  |                 |

| GPOUT[24:31]           | K26, K25, H27, G28, H25, J26, K24, K23 | 0        | BV <sub>DD</sub> | —               |

|                        | System Control                         |          |                  |                 |

| HRESET                 | AG17                                   | I        | OV <sub>DD</sub> | —               |

| HRESET_REQ             | AG16                                   | 0        | OV <sub>DD</sub> | 29              |

| SRESET                 | AG20                                   | I        | OV <sub>DD</sub> | —               |

| CKSTP_IN               | AA9                                    | I        | OV <sub>DD</sub> | —               |

| CKSTP_OUT              | AA8                                    | 0        | OV <sub>DD</sub> | 2, 4            |

|                        | Debug                                  |          | •                |                 |

| TRIG_IN                | AB2                                    | I        | OV <sub>DD</sub> | —               |

| TRIG_OUT/READY/QUIESCE | AB1                                    | 0        | OV <sub>DD</sub> | 6, 9,<br>19, 29 |

| MSRCID[0:1]            | AE4, AG2                               | 0        | OV <sub>DD</sub> | 5, 6, 9         |

| MSRCID[2:4]            | AF3, AF1, AF2                          | 0        | OV <sub>DD</sub> | 6, 19,<br>29    |

| MDVAL                  | AE5                                    | 0        | OV <sub>DD</sub> | 6               |

| CLK_OUT                | AE21                                   | 0        | OV <sub>DD</sub> | 11              |

|                        | Clock                                  |          |                  |                 |

| RTC                    | AF16                                   | I        | OV <sub>DD</sub> | —               |

| SYSCLK                 | AH17                                   | I        | OV <sub>DD</sub> | —               |

|                        | JTAG                                   | •        |                  |                 |

| ТСК                    | AG28                                   | I        | OV <sub>DD</sub> | —               |

| TDI                    | AH28                                   | I        | OV <sub>DD</sub> | 12              |

| Signal           | Package Pin Number                                                                                                                                                | Pin Type                                            | Power<br>Supply  | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------|-------|

| GV <sub>DD</sub> | B3, B11, C7, C9, C14, C17, D4, D6, D10, D15,<br>E2, E8, E11, E18, F5, F12, F16, G3, G7, G9,<br>G11, H5, H12, H15, H17, J10, K3, K12, K16,<br>K18, L6, M4, M8, M13 |                                                     | GV <sub>DD</sub> | _     |

| BV <sub>DD</sub> | C21, C24, C27, E20, E25, G19, G23, H26, J20                                                                                                                       | Power for local<br>bus (1.8 V,<br>2.5 V, 3.3 V)     | BV <sub>DD</sub> | -     |

| V <sub>DD</sub>  | M19, N12, N14, N16, N18, P11, P13, P15, P17,<br>P19, R12, R14, R16, R18, T11, T13, T15, T17,<br>T19, U12, U14, U16, U18, V17, V19                                 | Power for core<br>(1.1 V)                           | V <sub>DD</sub>  | -     |

| SV <sub>DD</sub> | L25, L27, M24, N28, P24, P26, R24, R27, T25,<br>V24, V26, W24, W27, Y25, AA28, AC27                                                                               | Core power for<br>SerDes<br>transceivers<br>(1.1 V) | SV <sub>DD</sub> | -     |

| XV <sub>DD</sub> | L20, L22, N23, P21, R22, T20, U23, V21, W22,<br>Y20                                                                                                               | Pad power for<br>SerDes<br>transceivers<br>(1.1 V)  | XV <sub>DD</sub> | -     |

| AVDD_LBIU        | J28                                                                                                                                                               | Power for local<br>bus PLL<br>(1.1 V)               | _                | 26    |

| AVDD_PCI1        | AH21                                                                                                                                                              | Power for<br>PCI1 PLL<br>(1.1 V)                    | —                | 26    |

| AVDD_PCI2        | AH22                                                                                                                                                              | Power for<br>PCI2 PLL<br>(1.1 V)                    | _                | 26    |

| AVDD_CORE        | AH15                                                                                                                                                              | Power for<br>e500 PLL (1.1<br>V)                    | _                | 26    |

| AVDD_PLAT        | AH19                                                                                                                                                              | Powerfor CCB<br>PLL (1.1 V)                         | —                | 26    |

| AVDD_SRDS        | D_SRDS U25                                                                                                                                                        |                                                     | _                | 26    |

| SENSEVDD         | M14                                                                                                                                                               | 0                                                   | V <sub>DD</sub>  | 13    |

| SENSEVSS         | M16                                                                                                                                                               | —                                                   | —                | 13    |

|                  | Analog Signals                                                                                                                                                    |                                                     |                  |       |

| MVREF            | A18                                                                                                                                                               | I<br>Reference<br>voltage signal<br>for DDR         | MVREF            |       |

# Table 73. MPC8545E Pinout Listing (continued)

| Signal                | Package Pin Number                    | Pin Type    | Power<br>Supply  | Notes    |

|-----------------------|---------------------------------------|-------------|------------------|----------|

| GPOUT[0:5]            | N9, N10, P8, N7, R9, N5               | 0           | LV <sub>DD</sub> |          |

| cfg_dram_type0/GPOUT6 | R8                                    | 0           | LV <sub>DD</sub> | 5, 9     |

| GPOUT7                | N6                                    | 0           | LV <sub>DD</sub> | -        |

| Reserved              | P1                                    | —           | _                | 104      |

| Reserved              | R6                                    | —           | _                | 104      |

| Reserved              | P6                                    | —           | —                | 15       |

| Reserved              | N4                                    | —           | _                | 105      |

| FIFO1_RXC2            | P5                                    | I           | LV <sub>DD</sub> | 104      |

| Reserved              | R1                                    | —           | _                | 104      |

| Reserved              | P10                                   | —           | _                | 105      |

| FIFO1_TXC2            | P7                                    | 0           | LV <sub>DD</sub> | 15       |

| cfg_dram_type1        | R10                                   | 0           | LV <sub>DD</sub> | 5, 9     |

| Thre                  | ee-Speed Ethernet Controller (Gigabit | Ethernet 3) |                  |          |

| TSEC3_TXD[3:0]        | V8, W10, Y10, W7                      | 0           | TV <sub>DD</sub> | 5, 9, 2  |

| TSEC3_RXD[3:0]        | Y1, W3, W5, W4                        | I           | TV <sub>DD</sub> | _        |

| TSEC3_GTX_CLK         | W8                                    | 0           | TV <sub>DD</sub> | _        |

| TSEC3_RX_CLK          | W2                                    | I           | TV <sub>DD</sub> | <b>—</b> |

| TSEC3_RX_DV           | W1                                    | I           | TV <sub>DD</sub> | _        |

| TSEC3_RX_ER           | Y2                                    | I           | TV <sub>DD</sub> | _        |

| TSEC3_TX_CLK          | V10                                   | I           | TV <sub>DD</sub> | _        |

| TSEC3_TX_EN           | V9                                    | 0           | TV <sub>DD</sub> | 30       |

| TSEC3_TXD[7:4]        | AB8, Y7, AA7, Y8                      | 0           | TV <sub>DD</sub> | 5, 9, 2  |

| TSEC3_RXD[7:4]        | AA1, Y3, AA2, AA4                     | I           | TV <sub>DD</sub> | _        |

| Reserved              | AA5                                   | _           | _                | 15       |

| TSEC3_COL             | Y5                                    | I           | TV <sub>DD</sub> | - 1      |

| TSEC3_CRS             | AA3                                   | I/O         | TV <sub>DD</sub> | 31       |

| TSEC3_TX_ER           | AB6                                   | 0           | TV <sub>DD</sub> | - 1      |

|                       | DUART                                 | 1           |                  |          |

| UART_CTS[0:1]         | AB3, AC5                              | I           | OV <sub>DD</sub> | -        |

| UART_RTS[0:1]         | AC6, AD7                              | 0           | OV <sub>DD</sub> | 1 -      |

| UART_SIN[0:1]         | AB5, AC7                              | I           | OV <sub>DD</sub> | <u> </u> |

| UART_SOUT[0:1]        | AB7, AD8                              | 0           | OV <sub>DD</sub> | <u> </u> |

|                       | I <sup>2</sup> C interface            | I           |                  | _1       |

| IIC1_SCL              | AG22                                  | I/O         | OV <sub>DD</sub> | 4, 27    |

|                       |                                       |             |                  | _1       |

# Table 74. MPC8543E Pinout Listing (continued)

| Signal           | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin Type                                              | Power<br>Supply  | Notes     |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------|-----------|

|                  | JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11                                                    |                  |           |

| ТСК              | AG28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | —         |

| TDI              | AH28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 12        |

| TDO              | AF28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                     | $OV_{DD}$        | —         |

| TMS              | AH27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 12        |

| TRST             | AH23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 12        |