#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

ĿХF

| Product Status                  | Obsolete                                                   |

|---------------------------------|------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                               |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                             |

| Speed                           | 1.2GHz                                                     |

| Co-Processors/DSP               | Signal Processing; SPE                                     |

| RAM Controllers                 | DDR, DDR2, SDRAM                                           |

| Graphics Acceleration           | No                                                         |

| Display & Interface Controllers | -                                                          |

| Ethernet                        | 10/100/1000Mbps (4)                                        |

| SATA                            | -                                                          |

| USB                             | -                                                          |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                           |

| Operating Temperature           | 0°C ~ 105°C (TA)                                           |

| Security Features               | -                                                          |

| Package / Case                  | 783-BBGA, FCBGA                                            |

| Supplier Device Package         | 783-FCBGA (29x29)                                          |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8547vtatgb |

|                                 |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Characteristic            | Symbol           | Max Value  | Unit | Notes |

|---------------------------|------------------|------------|------|-------|

| Storage temperature range | T <sub>STG</sub> | -55 to 150 | °C   | _     |

### Table 1. Absolute Maximum Ratings <sup>1</sup> (continued)

Notes:

- 1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- 2. The -0.3 to 2.75 V range is for DDR and -0.3 to 1.98 V range is for DDR2.

- 3. The 3.63 V maximum is only supported when the port is configured in GMII, MII, RMII, or TBI modes; otherwise the 2.75 V maximum applies. See Section 8.2, "FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications," for details on the recommended operating conditions per protocol.

- 4. (M,L,O)V<sub>IN</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

## 2.1.2 Recommended Operating Conditions

The following table provides the recommended operating conditions for this device. Note that the values in this table are the recommended and tested operating conditions. Proper device operation outside these conditions is not guaranteed.

|                    | Characteristic                                                                                                       | Symbol                               | Recommended<br>Value                               | Unit | Notes |

|--------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------|------|-------|

| Core supply volta  | age                                                                                                                  | V <sub>DD</sub>                      | 1.1 V ± 55 mV                                      | V    | —     |

| PLL supply voltage | ge                                                                                                                   | AV <sub>DD</sub>                     | 1.1 V ± 55 mV                                      | V    | 1     |

| Core power supp    | ly for SerDes transceivers                                                                                           | SV <sub>DD</sub>                     | 1.1 V ± 55 mV                                      | V    | —     |

| Pad power suppl    | y for SerDes transceivers                                                                                            | XV <sub>DD</sub>                     | 1.1 V ± 55 mV                                      | V    | —     |

| DDR and DDR2       | DRAM I/O voltage                                                                                                     | GV <sub>DD</sub>                     | 2.5 V ± 125 mV<br>1.8 V ± 90 mV                    | V    |       |

| Three-speed Eth    | ernet I/O voltage                                                                                                    | LV <sub>DD</sub>                     | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   | V    | 4     |

|                    |                                                                                                                      | TV <sub>DD</sub>                     | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   | _    | 4     |

|                    | RT, system control and power management, I <sup>2</sup> C, nagement, and JTAG I/O voltage                            | OV <sub>DD</sub>                     | 3.3 V ± 165 mV                                     | V    | 3     |

| Local bus I/O vol  | tage                                                                                                                 | BV <sub>DD</sub>                     | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   | V    |       |

| Input voltage      | DDR and DDR2 DRAM signals                                                                                            | MV <sub>IN</sub>                     | GND to GV <sub>DD</sub>                            | V    | 2     |

|                    | DDR and DDR2 DRAM reference                                                                                          | MV <sub>REF</sub>                    | GND to GV <sub>DD</sub> /2                         | V    | 2     |

|                    | Three-speed Ethernet signals                                                                                         | LV <sub>IN</sub><br>TV <sub>IN</sub> | GND to LV <sub>DD</sub><br>GND to TV <sub>DD</sub> | V    | 4     |

|                    | Local bus signals                                                                                                    | BV <sub>IN</sub>                     | GND to BV <sub>DD</sub>                            | V    | —     |

|                    | PCI, DUART, SYSCLK, system control and power management, I <sup>2</sup> C, Ethernet MII management, and JTAG signals | OV <sub>IN</sub>                     | GND to OV <sub>DD</sub>                            | V    | 3     |

**Table 2. Recommended Operating Conditions**

## 4.3 eTSEC Gigabit Reference Clock Timing

The following table provides the eTSEC gigabit reference clocks (EC\_GTX\_CLK125) AC timing specifications for the device.

| Parameter/Condition                                                  | Symbol            | Min      | Тур | Max         | Unit | Notes |

|----------------------------------------------------------------------|-------------------|----------|-----|-------------|------|-------|

| EC_GTX_CLK125 frequency                                              | f <sub>G125</sub> | _        | 125 | —           | MHz  | _     |

| EC_GTX_CLK125 cycle time                                             | t <sub>G125</sub> | —        | 8   | —           | ns   |       |

| EC_GTX_CLK125 rise and fall time<br>L/TVDD = 2.5 V<br>L/TVDD = 3.3 V |                   | —        | _   | 0.75<br>1.0 | ns   | 1     |

| EC_GTX_CLK125 duty cycle<br>GMII, TBI<br>1000Base-T for RGMII, RTBI  |                   | 45<br>47 | _   | 55<br>53    | %    | 2, 3  |

| Table 6. EC_ | GTX_CLK125 AC Tim | ning Specifications |

|--------------|-------------------|---------------------|

|--------------|-------------------|---------------------|

Notes:

1. Rise and fall times for EC\_GTX\_CLK125 are measured from 0.5 and 2.0 V for L/TV<sub>DD</sub> = 2.5 V, and from 0.6 and 2.7 V for L/TV<sub>DD</sub> = 3.3 V.

- 2. Timing is guaranteed by design and characterization.

- 3. EC\_GTX\_CLK125 is used to generate the GTX clock TSEC*n*\_GTX\_CLK for the eTSEC transmitter with 2% degradation. EC\_GTX\_CLK125 duty cycle can be loosened from 47/53% as long as the PHY device can tolerate the duty cycle generated by the TSEC*n*\_GTX\_CLK. See Section 8.2.6, "RGMII and RTBI AC Timing Specifications," for duty cycle for 10Base-T and 100Base-T reference clock.

## 4.4 PCI/PCI-X Reference Clock Timing

When the PCI/PCI-X controller is configured for asynchronous operation, the reference clock for the PCI/PCI-x controller is not the SYSCLK input, but instead the PCIn\_CLK. The following table provides the PCI/PCI-X reference clock AC timing specifications for the device.

| Table 7. PCIn_CLK AC Timing Specifications | Table 7. PCI <i>n</i> | CLK | AC Timing | Specifications |

|--------------------------------------------|-----------------------|-----|-----------|----------------|

|--------------------------------------------|-----------------------|-----|-----------|----------------|

At recommended operating conditions (see Table 2) with  $OV_{DD} = 3.3 \text{ V} \pm 165 \text{ mV}$ .

| Parameter/Condition         | Symbol                                    | Min | Тур | Мах | Unit | Notes |

|-----------------------------|-------------------------------------------|-----|-----|-----|------|-------|

| PCIn_CLK frequency          | f <sub>PCICLK</sub>                       | 16  | —   | 133 | MHz  | —     |

| PCIn_CLK cycle time         | t <sub>PCICLK</sub>                       | 7.5 | —   | 60  | ns   | —     |

| PCIn_CLK rise and fall time | t <sub>PCIKH</sub> , t <sub>PCIKL</sub>   | 0.6 | 1.0 | 2.1 | ns   | 1, 2  |

| PCIn_CLK duty cycle         | t <sub>PCIKHKL</sub> /t <sub>PCICLK</sub> | 40  | —   | 60  | %    | 2     |

Notes:

1. Rise and fall times for SYSCLK are measured at 0.6 and 2.7 V.

2. Timing is guaranteed by design and characterization.

### NOTE

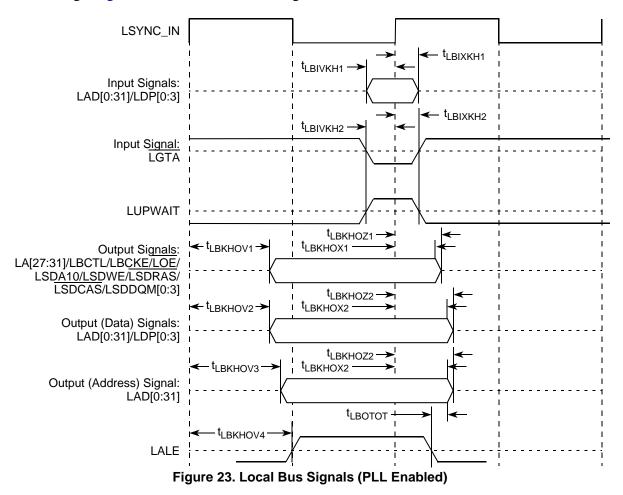

PLL bypass mode is required when LBIU frequency is at or below 83 MHz. When LBIU operates above 83 MHz, LBIU PLL is recommended to be enabled.

Figure 23 through Figure 28 show the local bus signals.

This table describes the timing parameters of the local bus interface at  $BV_{DD} = 3.3$  V with PLL disabled.

| Parameter                                             | Symbol <sup>1</sup>                 | Min  | Max | Unit | Notes |

|-------------------------------------------------------|-------------------------------------|------|-----|------|-------|

| Local bus cycle time                                  | t <sub>LBK</sub>                    | 12   | _   | ns   | 2     |

| Local bus duty cycle                                  | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43   | 57  | %    | _     |

| Internal launch/capture clock to LCLK delay           | t <sub>LBKHKT</sub>                 | 2.3  | 4.4 | ns   | 8     |

| Input setup to local bus clock (except LGTA/LUPWAIT)  | t <sub>LBIVKH1</sub>                | 6.2  | _   | ns   | 4, 5  |

| LGTA/LUPWAIT input setup to local bus clock           | t <sub>LBIVKL2</sub>                | 6.1  | _   | ns   | 4, 5  |

| Input hold from local bus clock (except LGTA/LUPWAIT) | t <sub>LBIXKH1</sub>                | -1.8 | _   | ns   | 4, 5  |

### Table 53. PCI-X AC Timing Specifications at 66 MHz (continued)

| Parameter                                        | Symbol              | Min | Max | Unit | Notes |

|--------------------------------------------------|---------------------|-----|-----|------|-------|

| HRESET to PCI-X initialization pattern hold time | t <sub>PCRHIX</sub> | 0   | 50  | ns   | 6, 11 |

Notes:

- 1. See the timing measurement conditions in the PCI-X 1.0a Specification.

- 2. Minimum times are measured at the package pin (not the test point). Maximum times are measured with the test point and load circuit.

- 3. Setup time for point-to-point signals applies to REQ and GNT only. All other signals are bused.

- 4. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 5. Setup time applies only when the device is not driving the pin. Devices cannot drive and receive signals at the same time.

- 6. Maximum value is also limited by delay to the first transaction (time for HRESET high to first configuration access, t<sub>PCRHFV</sub>). The PCI-X initialization pattern control signals after the rising edge of HRESET must be negated no later than two clocks before the first FRAME and must be floated no later than one clock before FRAME is asserted.

- 7. A PCI-X device is permitted to have the minimum values shown for t<sub>PCKHOV</sub> and t<sub>CYC</sub> only in PCI-X mode. In conventional mode, the device must meet the requirements specified in PCI 2.2 for the appropriate clock frequency.

- 8. Device must meet this specification independent of how many outputs switch simultaneously.

9. The timing parameter t<sub>PCRHFV</sub> is a minimum of 10 clocks rather than the minimum of 5 clocks in the PCI-X 1.0a Specification.

10.Guaranteed by characterization.

11.Guaranteed by design.

This table provides the PCI-X AC timing specifications at 133 MHz. Note that the maximum PCI-X frequency in synchronous mode is 110 MHz.

| Parameter                                         | Symbol              | Min | Max | Unit   | Notes         |

|---------------------------------------------------|---------------------|-----|-----|--------|---------------|

| SYSCLK to signal valid delay                      | <sup>t</sup> PCKHOV | _   | 3.8 | ns     | 1, 2, 3, 7, 8 |

| Output hold from SYSCLK                           | t <sub>PCKHOX</sub> | 0.7 | _   | ns     | 1, 11         |

| SYSCLK to output high impedance                   | t <sub>PCKHOZ</sub> |     | 7   | ns     | 1, 4, 8, 12   |

| Input setup time to SYSCLK                        | t <sub>PCIVKH</sub> | 1.2 | _   | ns     | 3, 5, 9, 11   |

| Input hold time from SYSCLK                       | t <sub>PCIXKH</sub> | 0.5 | -   | ns     | 11            |

| REQ64 to HRESET setup time                        | t <sub>PCRVRH</sub> | 10  | _   | clocks | 12            |

| HRESET to REQ64 hold time                         | t <sub>PCRHRX</sub> | 0   | 50  | ns     | 12            |

| HRESET high to first FRAME assertion              | t <sub>PCRHFV</sub> | 10  | _   | clocks | 10, 12        |

| PCI-X initialization pattern to HRESET setup time | <sup>t</sup> PCIVRH | 10  |     | clocks | 12            |

#### Table 54. PCI-X AC Timing Specifications at 133 MHz

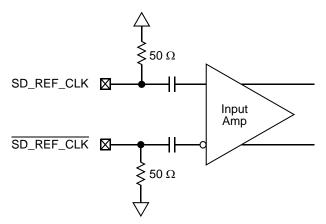

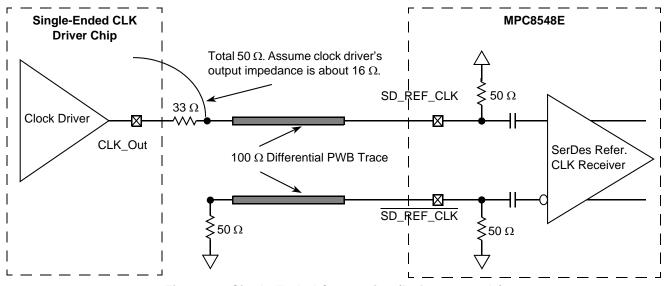

- The SD\_REF\_CLK and SD\_REF\_CLK are internally AC-coupled differential inputs as shown in Figure 39. Each differential clock input (SD\_REF\_CLK or SD\_REF\_CLK) has a 50-Ω termination to SGND\_SRDSn (xcorevss) followed by on-chip AC-coupling.

- The external reference clock driver must be able to drive this termination.

- The SerDes reference clock input can be either differential or single-ended. See the differential mode and single-ended mode description below for further detailed requirements.

- The maximum average current requirement that also determines the common mode voltage range:

- When the SerDes reference clock differential inputs are DC coupled externally with the clock driver chip, the maximum average current allowed for each input pin is 8 mA. In this case, the exact common mode input voltage is not critical as long as it is within the range allowed by the maximum average current of 8 mA (see the following bullet for more detail), since the input is AC-coupled on-chip.

- This current limitation sets the maximum common mode input voltage to be less than 0.4 V (0.4 V/50 = 8 mA) while the minimum common mode input level is 0.1 V above SGND\_SRDS*n* (xcorevss). For example, a clock with a 50/50 duty cycle can be produced by a clock driver with output driven by its current source from 0 to 16 mA (0–0.8 V), such that each phase of the differential input has a single-ended swing from 0 V to 800 mV with the common mode voltage at 400 mV.

- If the device driving the SD\_REF\_CLK and  $\overline{\text{SD}_{\text{REF}_{\text{CLK}}}}$  inputs cannot drive 50 Ω to SGND\_SRDS*n* (xcorevss) DC, or it exceeds the maximum input current limitations, then it must be AC-coupled off-chip.

- The input amplitude requirement:

- This requirement is described in detail in the following sections.

Figure 39. Receiver of SerDes Reference Clocks

## 16.2.2 DC Level Requirement for SerDes Reference Clocks

The DC level requirement for the SerDes reference clock inputs is different depending on the signaling mode used to connect the clock driver chip and SerDes reference clock inputs as described below:

• Differential mode

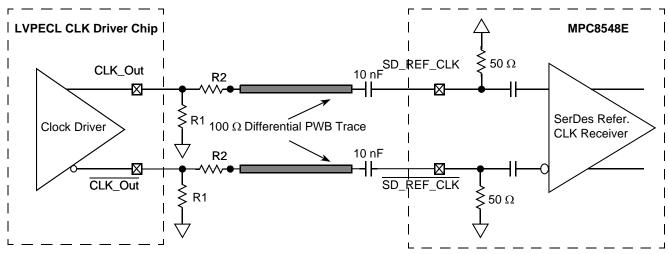

to AC-coupling. Its value could be ranged from 140 to 240  $\Omega$  depending on the clock driver vendor's requirement. R2 is used together with the SerDes reference clock receiver's 50- $\Omega$  termination resistor to attenuate the LVPECL output's differential peak level such that it meets the SerDes reference clock's differential input amplitude requirement (between 200 and 800 mV differential peak). For example, if the LVPECL output's differential peak is 900 mV and the desired SerDes reference clock input amplitude is selected as 600 mV, the attenuation factor is 0.67, which requires R2 = 25  $\Omega$ . Consult a clock driver chip manufacturer to verify whether this connection scheme is compatible with a particular clock driver chip.

Figure 45. AC-Coupled Differential Connection with LVPECL Clock Driver (Reference Only)

Figure 46 shows the SerDes reference clock connection reference circuits for a single-ended clock driver. It assumes the DC levels of the clock driver are compatible with the SerDes reference clock input's DC requirement.

Figure 46. Single-Ended Connection (Reference Only)

PCI Express

| Symbol                                      | Parameter                                                                      | Min   | Nom | Мах | Unit | Comments                                                                                                                                                                                             |

|---------------------------------------------|--------------------------------------------------------------------------------|-------|-----|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>RX-CM-ACp</sub>                      | AC peak<br>common mode<br>input voltage                                        |       | _   | 150 | mV   | $V_{\text{RX-CM-ACp}} =  V_{\text{RXD+}} - V_{\text{RXD-}} /2 + V_{\text{RX-CM-DC}}$ $V_{\text{RX-CM-DC}} = DC_{(\text{avg})} \text{ of }  V_{\text{RX-D+}} + V_{\text{RX-D-}}  \div 2.$ See Note 2. |

| RL <sub>RX-DIFF</sub>                       | Differential return loss                                                       | 15    |     | _   | dB   | Measured over 50 MHz to 1.25 GHz with the D+<br>and D– lines biased at +300 mV and –300 mV,<br>respectively. See Note 4.                                                                             |

| RL <sub>RX-CM</sub>                         | Common mode<br>return loss                                                     | 6     |     | —   | dB   | Measured over 50 MHz to 1.25 GHz with the D+<br>and D– lines biased at 0 V. See Note 4.                                                                                                              |

| Z <sub>RX-DIFF-DC</sub>                     | DC differential input impedance                                                | 80    | 100 | 120 | Ω    | RX DC differential mode impedance. See Note 5.                                                                                                                                                       |

| Z <sub>RX-DC</sub>                          | DC input<br>impedance                                                          | 40    | 50  | 60  | Ω    | Required RX D+ as well as D– DC impedance (50 $\pm$ 20% tolerance). See Notes 2 and 5.                                                                                                               |

| Z <sub>RX-HIGH-IMP-DC</sub>                 | Powered down<br>DC input<br>impedance                                          | 200 k | _   | —   | Ω    | Required RX D+ as well as D– DC impedance<br>when the receiver terminations do not have<br>power. See Note 6.                                                                                        |

| V <sub>RX-IDLE-DET-DIFFp-p</sub>            | Electrical idle<br>detect threshold                                            | 65    | _   | 175 | mV   | $V_{RX-IDLE-DET-DIFF_{P-P}} = 2 \times  V_{RX-D+} - V_{RX-D-} .$<br>Measured at the package pins of the receiver                                                                                     |

| T <sub>RX-IDLE-DET-DIFF-</sub><br>ENTERTIME | Unexpected<br>electrical idle<br>enter detect<br>threshold<br>integration time |       | _   | 10  | ms   | An unexpected electrical idle ( $V_{RX-DIFFp-p} < V_{RX-IDLE-DET-DIFFp-p}$ ) must be recognized no longer than $T_{RX-IDLE-DET-DIFF-ENTERING}$ to signal an unexpected idle condition.               |

## Table 57. Differential Receiver (RX) Input Specifications (continued)

#### PCI Express

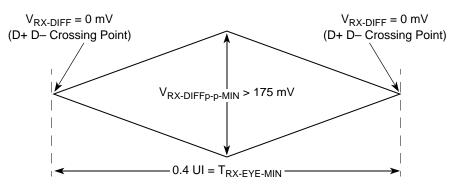

The eye diagram must be valid for any 250 consecutive UIs.

A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. The eye diagram is created using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI.

## NOTE

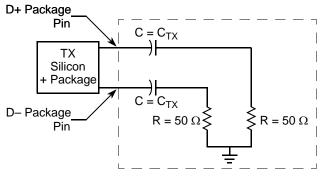

The reference impedance for return loss measurements is 50. to ground for both the D+ and D– line (that is, as measured by a vector network analyzer with 50- $\Omega$  probes—see Figure 50). Note that the series capacitors, CTX, are optional for the return loss measurement.

Figure 49. Minimum Receiver Eye Timing and Voltage Compliance Specification

## 17.5.1 Compliance Test and Measurement Load

The AC timing and voltage parameters must be verified at the measurement point, as specified within 0.2 inches of the package pins, into a test/measurement load shown in Figure 50.

## NOTE

The allowance of the measurement point to be within 0.2 inches of the package pins is meant to acknowledge that package/board routing may benefit from D+ and D- not being exactly matched in length at the package pin boundary.

Figure 50. Compliance Test/Measurement Load

#### Serial RapidIO

| Characteristic              | Symbol              | Range |      | Unit   | Notes                                                                      |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Unit   | Notes                                                                      |

| Output voltage              | Vo                  | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal comprising a differential pair |

| Differential output voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mV p-p | —                                                                          |

| Deterministic jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                          |

| Total jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                          |

| Multiple output skew        | S <sub>MO</sub>     | —     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |

| Unit interval               | UI                  | 400   | 400  | ps     | ±100 ppm                                                                   |

### Table 61. Short Run Transmitter AC Timing Specifications—3.125 GBaud

| Characteristic              | Symbol              | Range |      | Unit   | Notes                                                                      |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Onic   | NOICS                                                                      |

| Output voltage              | Vo                  | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal comprising a differential pair |

| Differential output voltage | V <sub>DIFFPP</sub> | 500   | 1000 | mVp-p  | -                                                                          |

| Deterministic jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | -                                                                          |

| Total jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                          |

| Multiple output skew        | S <sub>MO</sub>     | —     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |

| Unit interval               | UI                  | 320   | 320  | ps     | ±100 ppm                                                                   |

### Table 62. Long Run Transmitter AC Timing Specifications—1.25 GBaud

| Characteristic              | Symbol              | Range |      | Unit   | Notes                                                                      |

|-----------------------------|---------------------|-------|------|--------|----------------------------------------------------------------------------|

| Characteristic              | Symbol              | Min   | Max  | Onit   | NULES                                                                      |

| Output voltage              | V <sub>O</sub>      | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal comprising a differential pair |

| Differential output voltage | V <sub>DIFFPP</sub> | 800   | 1600 | mVp-p  | —                                                                          |

| Deterministic jitter        | J <sub>D</sub>      | —     | 0.17 | UI p-p | —                                                                          |

| Total jitter                | J <sub>T</sub>      | —     | 0.35 | UI p-p | —                                                                          |

| Multiple output skew        | S <sub>MO</sub>     | _     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |

| Unit interval               | UI                  | 800   | 800  | ps     | ±100 ppm                                                                   |

### Serial RapidIO

802.3ae-2002 is specified as the test pattern for use in eye pattern and jitter measurements. Annex 48B of IEEE Std. 802.3ae-2002 is recommended as a reference for additional information on jitter test methods.

## 18.9.1 Eye Template Measurements

For the purpose of eye template measurements, the effects of a single-pole high pass filter with a 3 dB point at (baud frequency)/1667 is applied to the jitter. The data pattern for template measurements is the continuous jitter test pattern (CJPAT) defined in Annex 48A of IEEE 802.3ae. All lanes of the LP-serial link shall be active in both the transmit and receive directions, and opposite ends of the links shall use asynchronous clocks. Four lane implementations shall use CJPAT as defined in Annex 48A. Single lane implementations shall use the CJPAT sequence specified in Annex 48A for transmission on lane 0. The amount of data represented in the eye shall be adequate to ensure that the bit error ratio is less than  $10^{-12}$ . The eye pattern shall be measured with AC coupling and the compliance template centered at 0 V differential. The left and right edges of the template shall be aligned with the mean zero crossing points of the measured data eye. The load for this test shall be  $100-\Omega$  resistive  $\pm 5\%$  differential to 2.5 GHz.

## 18.9.2 Jitter Test Measurements

For the purpose of jitter measurement, the effects of a single-pole high pass filter with a 3 dB point at (baud frequency)/1667 is applied to the jitter. The data pattern for jitter measurements is the Continuous Jitter test pattern (CJPAT) pattern defined in Annex 48A of IEEE 802.3ae. All lanes of the LP-serial link shall be active in both the transmit and receive directions, and opposite ends of the links shall use asynchronous clocks. Four lane implementations shall use CJPAT as defined in Annex 48A. Single lane implementations shall use the CJPAT sequence specified in Annex 48A for transmission on lane 0. Jitter shall be measured with AC coupling and at 0 V differential. Jitter measurement for the transmitter (or for calibration of a jitter tolerance setup) shall be performed with a test procedure resulting in a BER curve such as that described in Annex 48B of IEEE 802.3ae.

## 18.9.3 Transmit Jitter

Transmit jitter is measured at the driver output when terminated into a load of 100  $\Omega$  resistive ± 5% differential to 2.5 GHz.

## 18.9.4 Jitter Tolerance

Jitter tolerance is measured at the receiver using a jitter tolerance test signal. This signal is obtained by first producing the sum of deterministic and random jitter defined in Section 18.7, "Receiver Specifications," and then adjusting the signal amplitude until the data eye contacts the 6 points of the minimum eye opening of the receive template shown in Figure 54 and Table 69. Note that for this to occur, the test signal must have vertical waveform symmetry about the average value and have horizontal symmetry (including jitter) about the mean zero crossing. Eye template measurement requirements are as defined above. Random jitter is calibrated using a high pass filter with a low frequency corner at 20 MHz and a 20 dB/decade roll-off below this. The required sinusoidal jitter specified in Section 18.7, "Receiver Specifications," is then added to the signal and the test load is replaced by the receiver being tested.

#### **Package Description**

#### Notes:

- 1. All dimensions are in millimeters.

- 2. Dimensioning and tolerancing per ASME Y14.5M-1994.

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

- 5. Parallelism measurement shall exclude any effect of mark on top surface of package.

- 6. All dimensions are symmetric across the package center lines unless dimensioned otherwise.

### Table 71. MPC8548E Pinout Listing (continued)

| Signal                   | Package Pin Number                                                                                                                                                      | Pin Type | Power<br>Supply  | Notes   |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|---------|

| MWE                      | E7                                                                                                                                                                      | 0        | GV <sub>DD</sub> |         |

| MCAS                     | H7                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —       |

| MRAS                     | L8                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —       |

| MCKE[0:3]                | F10, C10, J11, H11                                                                                                                                                      | 0        | GV <sub>DD</sub> | 11      |

| MCS[0:3]                 | K8, J8, G8, F8                                                                                                                                                          | 0        | GV <sub>DD</sub> | —       |

| MCK[0:5]                 | H9, B15, G2, M9, A14, F1                                                                                                                                                | 0        | GV <sub>DD</sub> | —       |

| MCK[0:5]                 | J9, A15, G1, L9, B14, F2                                                                                                                                                | 0        | GV <sub>DD</sub> | —       |

| MODT[0:3]                | E6, K6, L7, M7                                                                                                                                                          | 0        | GV <sub>DD</sub> | —       |

| MDIC[0:1]                | A19, B19                                                                                                                                                                | I/O      | GV <sub>DD</sub> | 36      |

|                          | Local Bus Controller Interface                                                                                                                                          |          | •                | -       |

| LAD[0:31]                | E27, B20, H19, F25, A20, C19, E28, J23, A25,<br>K22, B28, D27, D19, J22, K20, D28, D25, B25,<br>E22, F22, F21, C25, C22, B23, F20, A23, A22,<br>E19, A21, D21, F19, B21 | I/O      | BV <sub>DD</sub> | _       |

| LDP[0:3]                 | K21, C28, B26, B22                                                                                                                                                      | I/O      | BV <sub>DD</sub> | —       |

| LA[27]                   | H21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LA[28:31]                | H20, A27, D26, A28                                                                                                                                                      | 0        | BV <sub>DD</sub> | 5, 7, 9 |

| LCS[0:4]                 | J25, C20, J24, G26, A26                                                                                                                                                 | 0        | BV <sub>DD</sub> |         |

| LCS5/DMA_DREQ2           | D23                                                                                                                                                                     | I/O      | BV <sub>DD</sub> | 1       |

| LCS6/DMA_DACK2           | G20                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 1       |

| LCS7/DMA_DDONE2          | E21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 1       |

| LWE0/LBS0/LSDDQM[0]      | G25                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE1/LBS1/LSDDQM[1]      | C23                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE2/LBS2/LSDDQM[2]      | J21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE3/LBS3/LSDDQM[3]      | A24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LALE                     | H24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| LBCTL                    | G27                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| LGPL0/LSDA10             | F23                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LGPL1/LSDWE              | G22                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LGPL2/LOE/LSDRAS         | B27                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| LGPL3/LSDCAS             | F24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LGPL4/LGTA/LUPWAIT/LPBSE | H23                                                                                                                                                                     | I/O      | BV <sub>DD</sub> | —       |

| LGPL5                    | E26                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LCKE                     | E24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | -       |

| LCLK[0:2]                | E23, D24, H22                                                                                                                                                           | 0        | BV <sub>DD</sub> | —       |

| Signal           | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Pin Type                                                            | Power<br>Supply  | Notes        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------|--------------|

|                  | DFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I I                                                                 |                  |              |

| L1_TSTCLK        | AC25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I                                                                   | OV <sub>DD</sub> | 25           |

| L2_TSTCLK        | AE22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I                                                                   | OV <sub>DD</sub> | 25           |

| LSSD_MODE        | AH20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I                                                                   | $OV_{DD}$        | 25           |

| TEST_SEL         | AH14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I                                                                   | $OV_{DD}$        | 25           |

|                  | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                     |                  | •            |

| THERM0           | AG1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —                                                                   | _                | 14           |

| THERM1           | AH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —                                                                   | _                | 14           |

|                  | Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                     |                  | •            |

| ASLEEP           | AH18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                                   | OV <sub>DD</sub> | 9, 19,<br>29 |

|                  | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | I I                                                                 |                  |              |

| GND              | A11, B7, B24, C1, C3, C5, C12, C15, C26, D8,<br>D11, D16, D20, D22, E1, E5, E9, E12, E15, E17,<br>F4, F26, G12, G15, G18, G21, G24, H2, H6, H8,<br>H28, J4, J12, J15, J17, J27, K7, K9, K11, K27,<br>L3, L5, L12, L16, N11, N13, N15, N17, N19, P4,<br>P9, P12, P14, P16, P18, R11, R13, R15, R17,<br>R19, T4, T12, T14, T16, T18, U8, U11, U13,<br>U15, U17, U19, V4, V12, V18, W6, W19, Y4, Y9,<br>Y11, Y19, AA6, AA14, AA17, AA22, AA23, AB4,<br>AC2, AC11, AC19, AC26, AD5, AD9, AD22,<br>AE3, AE14, AF6, AF10, AF13, AG8, AG27,<br>K28, L24, L26, N24, N27, P25, R28, T24, T26,<br>U24, V25, W28, Y24, Y26, AA24, AA27, AB25,<br>AC28, L21, L23, N22, P20, R23, T21, U22, V20,<br>W23, Y21, U27 | _                                                                   | _                |              |

| OV <sub>DD</sub> | V16, W11, W14, Y18, AA13, AA21, AB11,<br>AB17, AB24, AC4, AC9, AC21, AD6, AD13,<br>AD17, AD19, AE10, AE8, AE24, AF4, AF12,<br>AF22, AF27, AG26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for PCI<br>and other<br>standards<br>(3.3 V)                  | OV <sub>DD</sub> | _            |

| LV <sub>DD</sub> | N8, R7, T9, U6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Power for<br>TSEC1 and<br>TSEC2<br>(2.5 V, 3.3 V)                   | LV <sub>DD</sub> | _            |

| TV <sub>DD</sub> | W9, Y6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Power for<br>TSEC3 and<br>TSEC4<br>(2,5 V, 3.3 V)                   | TV <sub>DD</sub> | —            |

| GV <sub>DD</sub> | B3, B11, C7, C9, C14, C17, D4, D6, D10, D15,<br>E2, E8, E11, E18, F5, F12, F16, G3, G7, G9,<br>G11, H5, H12, H15, H17, J10, K3, K12, K16,<br>K18, L6, M4, M8, M13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Power for<br>DDR1 and<br>DDR2 DRAM<br>I/O voltage<br>(1.8 V, 2.5 V) | GV <sub>DD</sub> | —            |

### Table 72. MPC8547E Pinout Listing (continued)

| Signal     | Package Pin Number | Pin Type | Power<br>Supply | Notes |

|------------|--------------------|----------|-----------------|-------|

| SD_PLL_TPA | U26                | 0        | —               | 24    |

**Note:** All note references in this table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

Table 73 provides the pin-out listing for the MPC8545E 783 FC-PBGA package.

### NOTE

All note references in the following table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

|                               | •                                                                                                                                                                                                      |     |                  |          |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------|----------|

| Signal                        | Signal Package Pin Number                                                                                                                                                                              |     |                  |          |

|                               | PCI1 and PCI2 (One 64-Bit or Two 32-Bit)                                                                                                                                                               |     |                  |          |

| PCI1_AD[63:32]/PCI2_AD[31:0]  | AB14, AC15, AA15, Y16, W16, AB16, AC16,<br>AA16, AE17, AA18, W18, AC17, AD16, AE16,<br>Y17, AC18, AB18, AA19, AB19, AB21, AA20,<br>AC20, AB20, AB22, AC22, AD21, AB23, AF23,<br>AD23, AE23, AC23, AC24 | I/O | OV <sub>DD</sub> | 17       |

| PCI1_AD[31:0]                 | AH6, AE7, AF7, AG7, AH7, AF8, AH8, AE9,<br>AH9, AC10, AB10, AD10, AG10, AA10, AH10,<br>AA11, AB12, AE12, AG12, AH12, AB13, AA12,<br>AC13, AE13, Y14, W13, AG13, V14, AH13,<br>AC14, Y15, AB15          | I/O | OV <sub>DD</sub> | 17       |

| PCI1_C_BE[7:4]/PCI2_C_BE[3:0] | AF15, AD14, AE15, AD15                                                                                                                                                                                 | I/O | OV <sub>DD</sub> | 17       |

| PCI1_C_BE[3:0]                | AF9, AD11, Y12, Y13                                                                                                                                                                                    | I/O | OV <sub>DD</sub> | 17       |

| PCI1_PAR64/PCI2_PAR           | W15                                                                                                                                                                                                    | I/O | OV <sub>DD</sub> | —        |

| PCI1_GNT[4:1]                 | AG6, AE6, AF5, AH5                                                                                                                                                                                     | 0   | OV <sub>DD</sub> | 5, 9, 35 |

| PCI1_GNT0                     | AG5                                                                                                                                                                                                    | I/O | OV <sub>DD</sub> | —        |

| PCI1_IRDY                     | AF11                                                                                                                                                                                                   | I/O | OV <sub>DD</sub> | 2        |

| PCI1_PAR                      | AD12                                                                                                                                                                                                   | I/O | OV <sub>DD</sub> | —        |

| PCI1_PERR                     | AC12                                                                                                                                                                                                   | I/O | OV <sub>DD</sub> | 2        |

| PCI1_SERR                     | V13                                                                                                                                                                                                    | I/O | OV <sub>DD</sub> | 2, 4     |

| PCI1_STOP                     | W12                                                                                                                                                                                                    | I/O | OV <sub>DD</sub> | 2        |

| PCI1_TRDY                     | AG11                                                                                                                                                                                                   | I/O | OV <sub>DD</sub> | 2        |

| PCI1_REQ[4:1]                 | AH2, AG4, AG3, AH4                                                                                                                                                                                     | I   | OV <sub>DD</sub> | —        |

| PCI1_REQ0                     | AH3                                                                                                                                                                                                    | I/O | OV <sub>DD</sub> | —        |

| PCI1_CLK                      | AH26                                                                                                                                                                                                   | I   | OV <sub>DD</sub> | 39       |

| PCI1_DEVSEL                   | AH11                                                                                                                                                                                                   | I/O | OV <sub>DD</sub> | 2        |

### Table 73. MPC8545E Pinout Listing

| Signal                 | Package Pin Number                       | Pin Type | Power<br>Supply  | Notes           |

|------------------------|------------------------------------------|----------|------------------|-----------------|

| IIC1_SDA               | AG21                                     | I/O      | OV <sub>DD</sub> | 4, 27           |

| IIC2_SCL               | AG15                                     | I/O      | OV <sub>DD</sub> | 4, 27           |

| IIC2_SDA               | AG14                                     | I/O      | OV <sub>DD</sub> | 4, 27           |

|                        | SerDes                                   | 1        |                  |                 |

| SD_RX[0:7]             | M28, N26, P28, R26, W26, Y28, AA26, AB28 | Ι        | XV <sub>DD</sub> | —               |

| SD_RX[0:7]             | M27, N25, P27, R25, W25, Y27, AA25, AB27 | I        | XV <sub>DD</sub> | _               |

| SD_TX[0:7]             | M22, N20, P22, R20, U20, V22, W20, Y22   | 0        | XV <sub>DD</sub> | —               |

| SD_TX[0:7]             | M23, N21, P23, R21, U21, V23, W21, Y23   | 0        | XV <sub>DD</sub> | _               |

| SD_PLL_TPD             | U28                                      | 0        | XV <sub>DD</sub> | 24              |

| SD_REF_CLK             | T28                                      | Ι        | XV <sub>DD</sub> | —               |

| SD_REF_CLK             | T27                                      | I        | XV <sub>DD</sub> | _               |

| Reserved               | AC1, AC3                                 | —        | _                | 2               |

| Reserved               | M26, V28                                 | _        | —                | 32              |

| Reserved               | M25, V27                                 | _        | _                | 34              |

| Reserved               | M20, M21, T22, T23                       | —        | _                | 38              |

|                        | General-Purpose Output                   |          |                  | •               |

| GPOUT[24:31]           | K26, K25, H27, G28, H25, J26, K24, K23   | 0        | BV <sub>DD</sub> | —               |

|                        | System Control                           |          |                  |                 |

| HRESET                 | AG17                                     | Ι        | OV <sub>DD</sub> | —               |

| HRESET_REQ             | AG16                                     | 0        | $OV_DD$          | 29              |

| SRESET                 | AG20                                     | I        | OV <sub>DD</sub> | —               |

| CKSTP_IN               | AA9                                      | Ι        | $OV_{DD}$        | —               |

| CKSTP_OUT              | AA8                                      | 0        | $OV_{DD}$        | 2, 4            |

|                        | Debug                                    |          |                  | •               |

| TRIG_IN                | AB2                                      | Ι        | OV <sub>DD</sub> | —               |

| TRIG_OUT/READY/QUIESCE | AB1                                      | 0        | OV <sub>DD</sub> | 6, 9, 19,<br>29 |

| MSRCID[0:1]            | AE4, AG2                                 | 0        | OV <sub>DD</sub> | 5, 6, 9         |

| MSRCID[2:4]            | AF3, AF1, AF2                            | 0        | OV <sub>DD</sub> | 6, 19, 29       |

| MDVAL                  | AE5                                      | 0        | $OV_{DD}$        | 6               |

| CLK_OUT                | AE21                                     | 0        | OV <sub>DD</sub> | 11              |

|                        | Clock                                    |          |                  |                 |

| RTC                    | AF16                                     | Ι        | $OV_{DD}$        | —               |

| SYSCLK                 | AH17                                     | I        | OV <sub>DD</sub> |                 |

# 20 Clocking

This section describes the PLL configuration of the device. Note that the platform clock is identical to the core complex bus (CCB) clock.

## 20.1 Clock Ranges

Table 75 through Table 77 provide the clocking specifications for the processor cores and Table 78, through Table 80 provide the clocking specifications for the memory bus.

| Characteristic                | Maximum Processor Core Frequency |      |          |      |          |      |      |       |

|-------------------------------|----------------------------------|------|----------|------|----------|------|------|-------|

|                               | 1000 MHz                         |      | 1200 MHz |      | 1333 MHz |      | Unit | Notes |

|                               | Min                              | Max  | Min      | Max  | Min      | Max  |      |       |

| e500 core processor frequency | 800                              | 1000 | 800      | 1200 | 800      | 1333 | MHz  | 1, 2  |

Table 75. Processor Core Clocking Specifications (MPC8548E and MPC8547E)

Notes:

Caution: The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

2.) The minimum e500 core frequency is based on the minimum platform frequency of 333 MHz.

### Table 76. Processor Core Clocking Specifications (MPC8545E)

|                               | Maximum Processor Core Frequency |     |          |      |     |      |       |      |

|-------------------------------|----------------------------------|-----|----------|------|-----|------|-------|------|

| Characteristic                | 800 MHz 1000 M                   |     | MHz 1200 |      | MHz | Unit | Notes |      |

|                               | Min                              | Max | Min      | Max  | Min | Max  |       |      |

| e500 core processor frequency | 800                              | 800 | 800      | 1000 | 800 | 1200 | MHz   | 1, 2 |

Notes:

1. **Caution:** The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

2.)The minimum e500 core frequency is based on the minimum platform frequency of 333 MHz.

## 20.3 e500 Core PLL Ratio

This table describes the clock ratio between the e500 core complex bus (CCB) and the e500 core clock. This ratio is determined by the binary value of LBCTL, LALE, and LGPL2 at power up, as shown in this table.

| Binary Value of<br>LBCTL, LALE, LGPL2<br>Signals | e500 core:CCB Clock Ratio | 00 core:CCB Clock Ratio<br>Binary Value of<br>LBCTL, LALE, LGPL2<br>Signals |     |

|--------------------------------------------------|---------------------------|-----------------------------------------------------------------------------|-----|

| 000                                              | 4:1                       | 100                                                                         | 2:1 |

| 001                                              | 9:2                       | 101                                                                         | 5:2 |

| 010                                              | Reserved                  | 110                                                                         | 3:1 |

| 011                                              | 3:2                       | 111                                                                         | 7:2 |

| Table 82. e500 | Core to CCB | <b>Clock Ratio</b> |

|----------------|-------------|--------------------|

|----------------|-------------|--------------------|

## 20.4 Frequency Options

Table 83This table shows the expected frequency values for the platform frequency when using a CCB clock to SYSCLK ratio in comparison to the memory bus clock speed.

| CCB to<br>SYSCLK Ratio | SYSCLK (MHz)                 |     |       |       |       |     |     |     |        |  |

|------------------------|------------------------------|-----|-------|-------|-------|-----|-----|-----|--------|--|

|                        | 16.66                        | 25  | 33.33 | 41.66 | 66.66 | 83  | 100 | 111 | 133.33 |  |

|                        | Platform/CCB Frequency (MHz) |     |       |       |       |     |     |     |        |  |

| 2                      |                              |     |       |       |       |     |     |     |        |  |

| 3                      |                              |     |       |       |       |     |     | 333 | 400    |  |

| 4                      |                              |     |       |       |       | 333 | 400 | 445 | 533    |  |

| 5                      |                              |     |       |       | 333   | 415 | 500 |     |        |  |

| 6                      |                              |     |       |       | 400   | 500 |     | -   |        |  |

| 8                      |                              |     |       | 333   | 533   |     | -   |     |        |  |

| 9                      |                              |     |       | 375   |       |     |     |     |        |  |

| 10                     |                              |     | 333   | 417   |       |     |     |     |        |  |

| 12                     |                              |     | 400   | 500   |       |     |     |     |        |  |

| 16                     |                              | 400 | 533   |       |       |     |     |     |        |  |

| 20                     | 333                          | 500 |       | -     |       |     |     |     |        |  |

Table 83. Frequency Options of SYSCLK with Respect to Memory Bus Speeds

**Note:** Due to errata Gen 13 the max sys clk frequency must not exceed 100 MHz if the core clk frequency is below 1200 MHz.

System Design Information

## 22.10 Guidelines for High-Speed Interface Termination

This section provides the guidelines for high-speed interface termination when the SerDes interface is entirely unused and when it is partly unused.

## 22.10.1 SerDes Interface Entirely Unused

If the high-speed SerDes interface is not used at all, the unused pin must be terminated as described in this section.

The following pins must be left unconnected (float):

- SD\_TX[7:0]

- <u>SD\_TX</u>[7:0]

- Reserved pins T22, T23, M20, M21

The following pins must be connected to GND:

- SD\_RX[7:0]

- <u>SD\_RX</u>[7:0]

- SD\_REF\_CLK

- SD\_REF\_CLK

### NOTE

It is recommended to power down the unused lane through SRDSCR1[0:7] register (offset =  $0xE_0F08$ ) (This prevents the oscillations and holds the receiver output in a fixed state.) that maps to SERDES lane 0 to lane 7 accordingly.

Pins V28 and M26 must be tied to  $XV_{DD}$ . Pins V27 and M25 must be tied to GND through a 300- $\Omega$  resistor.

In Rev 2.0 silicon, POR configuration pin cfg\_srds\_en on TSEC4\_TXD[2]/TSEC3\_TXD[6] can be used to power down SerDes block.

## 22.10.2 SerDes Interface Partly Unused

If only part of the high-speed SerDes interface pins are used, the remaining high-speed serial I/O pins must be terminated as described in this section.

The following pins must be left unconnected (float) if not used:

- SD\_TX[7:0]

- <u>SD\_TX</u>[7:0]

- Reserved pins: T22, T23, M20, M21

The following pins must be connected to GND if not used:

- SD\_RX[7:0]

- $\overline{\text{SD}_{RX}}[7:0]$

- SD\_REF\_CLK

# 23 Ordering Information

Ordering information for the parts fully covered by this specification document is provided in Section 23.1, "Part Numbers Fully Addressed by this Document."

## 23.1 Part Numbers Fully Addressed by this Document

This table provides the Freescale part numbering nomenclature for the device. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the processor frequency, the part-numbering scheme also includes an application modifier that may specify special application conditions. Each part number also contains a revision code that refers to the die mask revision number.

| MPC             | nnnnn              | t                                       | рр                                                               | ff                                                            | С                                          | r                                                                                                                                                                              |

|-----------------|--------------------|-----------------------------------------|------------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Product<br>Code | Part<br>Identifier | Temperature                             | Package <sup>1, 2, 3</sup>                                       | Processor<br>Frequency <sup>4</sup>                           | Core<br>Frequency                          | Silicon Version                                                                                                                                                                |

| MPC             | 8548E<br>8548      | Blank = 0 to 105°C<br>C = −40° to 105°C | HX = CBGA<br>VU = Pb-free CBGA<br>PX = PBGA<br>VT = Pb-free PBGA | AV = 1500 <sup>3</sup><br>AU = 1333<br>AT = 1200<br>AQ = 1000 | J = 533<br>H = 500 <sup>5</sup><br>G = 400 | Blank = Ver. 2.0<br>(SVR = 0x80390020)<br>A = Ver. 2.1.1<br>B = Ver. 2.1.2<br>C = Ver. 2.1.3<br>(SVR = 0x80390021)<br>D = Ver. 3.1.x<br>(SVR = 0x80390031)<br>Blank = Ver. 2.0 |

|                 |                    |                                         |                                                                  |                                                               |                                            | (SVR = 0x80310020)<br>A = Ver. 2.1.1<br>B = Ver. 2.1.2<br>C = Ver. 2.1.3<br>(SVR = 0x80310021)<br>D = Ver. 3.1.x<br>(SVR = 0x80310031)                                         |

|                 | 8547E              |                                         |                                                                  | AU = 1333<br>AT = 1200<br>AQ = 1000                           | J = 533<br>G = 400                         | Blank = Ver. 2.0 (SVR = 0x80390120) A = Ver. 2.1.1 B = Ver. 2.1.2 C = Ver. 2.1.3 (SVR = 0x80390121) D = Ver. 3.1.x (SVR = 0x80390131)                                          |

|                 | 8547               |                                         |                                                                  |                                                               |                                            | Blank = Ver. 2.0 (SVR = 0x80390120)<br>A = Ver. 2.1.1<br>B = Ver. 2.1.2<br>C = Ver. 2.1.3<br>(SVR = 0x80310121)<br>D = Ver. 3.1.x<br>(SVR = 0x80310131)                        |

### Table 87. Part Numbering Nomenclature

...

## 23.2 Part Marking

Parts are marked as the example shown in Figure 64.

#### Notes:

TWLYYWW is final test traceability code. MMMMM is 5 digit mask number. CCCCC is the country of assembly. This space is left blank if parts are assembled in the United States. YWWLAZ is assembly traceability code.

#### Figure 64. Part Marking for CBGA and PBGA Device