#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 1.0GHz                                                                 |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                                  |

| RAM Controllers                 | DDR, DDR2, SDRAM                                                       |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (4)                                                    |

| SATA                            | -                                                                      |

| USB                             | · ·                                                                    |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                     |

| Security Features               | Cryptography, Random Number Generator                                  |

| Package / Case                  | 783-BBGA, FCBGA                                                        |

| Supplier Device Package         | 783-FCBGA (29x29)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8548echxaqg |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Overview

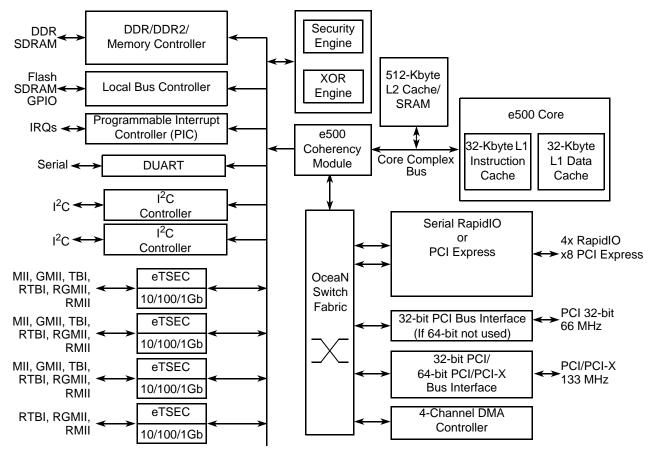

Figure 1. Device Block Diagram

## 1.1 Key Features

The following list provides an overview of the device feature set:

- High-performance 32-bit core built on Power Architecture® technology.

- 32-Kbyte L1 instruction cache and 32-Kbyte L1 data cache with parity protection. Caches can be locked entirely or on a per-line basis, with separate locking for instructions and data.

- Signal-processing engine (SPE) APU (auxiliary processing unit). Provides an extensive instruction set for vector (64-bit) integer and fractional operations. These instructions use both the upper and lower words of the 64-bit GPRs as they are defined by the SPE APU.

- Double-precision floating-point APU. Provides an instruction set for double-precision (64-bit) floating-point instructions that use the 64-bit GPRs.

- 36-bit real addressing

- Embedded vector and scalar single-precision floating-point APUs. Provide an instruction set for single-precision (32-bit) floating-point instructions.

- Memory management unit (MMU). Especially designed for embedded applications. Supports 4-Kbyte to 4-Gbyte page sizes.

- Enhanced hardware and software debug support

Performance monitor facility that is similar to, but separate from, the device performance monitor

The e500 defines features that are not implemented on this device. It also generally defines some features that this device implements more specifically. An understanding of these differences can be critical to ensure proper operations.

- 512-Kbyte L2 cache/SRAM

- Flexible configuration.

- Full ECC support on 64-bit boundary in both cache and SRAM modes

- Cache mode supports instruction caching, data caching, or both.

- External masters can force data to be allocated into the cache through programmed memory ranges or special transaction types (stashing).

- 1, 2, or 4 ways can be configured for stashing only.

- Eight-way set-associative cache organization (32-byte cache lines)

- Supports locking entire cache or selected lines. Individual line locks are set and cleared through Book E instructions or by externally mastered transactions.

- Global locking and Flash clearing done through writes to L2 configuration registers

- Instruction and data locks can be Flash cleared separately.

- SRAM features include the following:

- I/O devices access SRAM regions by marking transactions as snoopable (global).

- Regions can reside at any aligned location in the memory map.

- Byte-accessible ECC is protected using read-modify-write transaction accesses for smaller-than-cache-line accesses.

- Address translation and mapping unit (ATMU)

- Eight local access windows define mapping within local 36-bit address space.

- Inbound and outbound ATMUs map to larger external address spaces.

- Three inbound windows plus a configuration window on PCI/PCI-X and PCI Express

- Four inbound windows plus a default window on RapidIO<sup>™</sup>

- Four outbound windows plus default translation for PCI/PCI-X and PCI Express

- Eight outbound windows plus default translation for RapidIO with segmentation and sub-segmentation support

- DDR/DDR2 memory controller

- Programmable timing supporting DDR and DDR2 SDRAM

- 64-bit data interface

- Four banks of memory supported, each up to 4 Gbytes, to a maximum of 16 Gbytes

- DRAM chip configurations from 64 Mbits to 4 Gbits with ×8/×16 data ports

- Full ECC support

- Page mode support

- Up to 16 simultaneous open pages for DDR

#### Overview

- AESU-Advanced Encryption Standard unit

- Implements the Rijndael symmetric key cipher

- ECB, CBC, CTR, and CCM modes

- 128-, 192-, and 256-bit key lengths

- AFEU—ARC four execution unit

- Implements a stream cipher compatible with the RC4 algorithm

- 40- to 128-bit programmable key

- MDEU—message digest execution unit

- SHA with 160- or 256-bit message digest

- MD5 with 128-bit message digest

- HMAC with either algorithm

- KEU—Kasumi execution unit

- Implements F8 algorithm for encryption and F9 algorithm for integrity checking

- Also supports A5/3 and GEA-3 algorithms

- RNG—random number generator

- XOR engine for parity checking in RAID storage applications

- Dual I<sup>2</sup>C controllers

- Two-wire interface

- Multiple master support

- Master or slave  $I^2C$  mode support

- On-chip digital filtering rejects spikes on the bus

- Boot sequencer

- Optionally loads configuration data from serial ROM at reset via the  $I^2C$  interface

- Can be used to initialize configuration registers and/or memory

- Supports extended I<sup>2</sup>C addressing mode

- Data integrity checked with preamble signature and CRC

- DUART

- Two 4-wire interfaces (SIN, SOUT,  $\overline{\text{RTS}}$ ,  $\overline{\text{CTS}}$ )

- Programming model compatible with the original 16450 UART and the PC16550D

- Local bus controller (LBC)

- Multiplexed 32-bit address and data bus operating at up to 133 MHz

- Eight chip selects support eight external slaves

- Up to eight-beat burst transfers

- The 32-, 16-, and 8-bit port sizes are controlled by an on-chip memory controller.

- Three protocol engines available on a per chip select basis:

- General-purpose chip select machine (GPCM)

- Three user programmable machines (UPMs)

- VRRP and HSRP support for seamless router fail-over

- Up to 16 exact-match MAC addresses supported

- Broadcast address (accept/reject)

- Hash table match on up to 512 multicast addresses

- Promiscuous mode

- Buffer descriptors backward compatible with MPC8260 and MPC860T 10/100 Ethernet programming models

- RMON statistics support

- 10-Kbyte internal transmit and 2-Kbyte receive FIFOs

- MII management interface for control and status

- Ability to force allocation of header information and buffer descriptors into L2 cache

- OCeaN switch fabric

- Full crossbar packet switch

- Reorders packets from a source based on priorities

- Reorders packets to bypass blocked packets

- Implements starvation avoidance algorithms

- Supports packets with payloads of up to 256 bytes

- Integrated DMA controller

- Four-channel controller

- All channels accessible by both the local and remote masters

- Extended DMA functions (advanced chaining and striding capability)

- Support for scatter and gather transfers

- Misaligned transfer capability

- Interrupt on completed segment, link, list, and error

- Supports transfers to or from any local memory or I/O port

- Selectable hardware-enforced coherency (snoop/no snoop)

- Ability to start and flow control each DMA channel from external 3-pin interface

- Ability to launch DMA from single write transaction

- Two PCI/PCI-X controllers

- PCI 2.2 and PCI-X 1.0 compatible

- One 32-/64-bit PCI/PCI-X port with support for speeds of up to 133 MHz (maximum PCI-X frequency in synchronous mode is 110 MHz)

- One 32-bit PCI port with support for speeds from 16 to 66 MHz (available when the other port is in 32-bit mode)

- Host and agent mode support

- 64-bit dual address cycle (DAC) support

- PCI-X supports multiple split transactions

- Supports PCI-to-memory and memory-to-PCI streaming

| Characteristic            | Symbol           | Max Value  | Unit | Notes |  |

|---------------------------|------------------|------------|------|-------|--|

| Storage temperature range | T <sub>STG</sub> | -55 to 150 | °C   | _     |  |

### Table 1. Absolute Maximum Ratings <sup>1</sup> (continued)

Notes:

- 1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- 2. The -0.3 to 2.75 V range is for DDR and -0.3 to 1.98 V range is for DDR2.

- 3. The 3.63 V maximum is only supported when the port is configured in GMII, MII, RMII, or TBI modes; otherwise the 2.75 V maximum applies. See Section 8.2, "FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications," for details on the recommended operating conditions per protocol.

- 4. (M,L,O)V<sub>IN</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

## 2.1.2 Recommended Operating Conditions

The following table provides the recommended operating conditions for this device. Note that the values in this table are the recommended and tested operating conditions. Proper device operation outside these conditions is not guaranteed.

|                                                                                                                        | Characteristic                                                                                                       | Symbol                               | Recommended<br>Value                               | Unit | Notes |

|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------|------|-------|

| Core supply volta                                                                                                      | age                                                                                                                  | V <sub>DD</sub>                      | 1.1 V ± 55 mV                                      | V    | —     |

| PLL supply voltage                                                                                                     | ge                                                                                                                   | AV <sub>DD</sub>                     | 1.1 V ± 55 mV                                      | V    | 1     |

| Core power supply for SerDes transceivers                                                                              |                                                                                                                      | SV <sub>DD</sub>                     | 1.1 V ± 55 mV                                      | V    | —     |

| Pad power suppl                                                                                                        | Pad power supply for SerDes transceivers                                                                             |                                      | 1.1 V ± 55 mV                                      | V    | —     |

| DDR and DDR2                                                                                                           | DRAM I/O voltage                                                                                                     | GV <sub>DD</sub>                     | 2.5 V ± 125 mV<br>1.8 V ± 90 mV                    | V    |       |

| Three-speed Eth                                                                                                        | ernet I/O voltage                                                                                                    | LV <sub>DD</sub>                     | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   | V    | 4     |

|                                                                                                                        |                                                                                                                      | TV <sub>DD</sub>                     | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   | _    | 4     |

| PCI/PCI-X, DUART, system control and power management, I <sup>2</sup> C, Ethernet MII management, and JTAG I/O voltage |                                                                                                                      | OV <sub>DD</sub>                     | 3.3 V ± 165 mV                                     | V    | 3     |

| Ethernet MII management, and JTAG I/O voltage                                                                          |                                                                                                                      | BV <sub>DD</sub>                     | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   | V    |       |

| Input voltage                                                                                                          | DDR and DDR2 DRAM signals                                                                                            | MV <sub>IN</sub>                     | GND to GV <sub>DD</sub>                            | V    | 2     |

|                                                                                                                        | DDR and DDR2 DRAM reference                                                                                          | MV <sub>REF</sub>                    | GND to GV <sub>DD</sub> /2                         | V    | 2     |

|                                                                                                                        | Three-speed Ethernet signals                                                                                         | LV <sub>IN</sub><br>TV <sub>IN</sub> | GND to LV <sub>DD</sub><br>GND to TV <sub>DD</sub> | V    | 4     |

|                                                                                                                        | Local bus signals                                                                                                    | BV <sub>IN</sub>                     | GND to BV <sub>DD</sub>                            | V    | —     |

|                                                                                                                        | PCI, DUART, SYSCLK, system control and power management, I <sup>2</sup> C, Ethernet MII management, and JTAG signals | OV <sub>IN</sub>                     | GND to OV <sub>DD</sub>                            | V    | 3     |

**Table 2. Recommended Operating Conditions**

# 6 DDR and DDR2 SDRAM

This section describes the DC and AC electrical specifications for the DDR SDRAM interface of the device. Note that  $GV_{DD}(typ) = 2.5 \text{ V}$  for DDR SDRAM, and  $GV_{DD}(typ) = 1.8 \text{ V}$  for DDR2 SDRAM.

## 6.1 DDR SDRAM DC Electrical Characteristics

The following table provides the recommended operating conditions for the DDR2 SDRAM controller of the device when  $GV_{DD}(typ) = 1.8 \text{ V}.$

| Parameter/Condition                              | Symbol            | Min                       | Мах                       | Unit | Notes |

|--------------------------------------------------|-------------------|---------------------------|---------------------------|------|-------|

| I/O supply voltage                               | GV <sub>DD</sub>  | 1.71                      | 1.89                      | V    | 1     |

| I/O reference voltage                            | MV <sub>REF</sub> | $0.49 \times GV_{DD}$     | $0.51 \times GV_{DD}$     | V    | 2     |

| I/O termination voltage                          | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04  | MV <sub>REF</sub> + 0.04  | V    | 3     |

| Input high voltage                               | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.125 | GV <sub>DD</sub> + 0.3    | V    | —     |

| Input low voltage                                | V <sub>IL</sub>   | -0.3                      | MV <sub>REF</sub> – 0.125 | V    | —     |

| Output leakage current                           | I <sub>OZ</sub>   | -50                       | 50                        | μA   | 4     |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>OH</sub>   | -13.4                     | —                         | mA   | _     |

| Output low current (V <sub>OUT</sub> = 0.280 V)  | I <sub>OL</sub>   | 13.4                      | —                         | mA   |       |

Table 11. DDR2 SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V

### Notes:

1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $V_{DD}$  at all times.

2.  $MV_{REF}$  is expected to be equal to 0.5 ×  $GV_{DD}$ , and to track  $GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}$  may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail must track variations in the DC level of MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled,  $0 V \le V_{OUT} \le GV_{DD}$ .

This table provides the DDR2 I/O capacitance when  $GV_{DD}(typ) = 1.8$  V.

## Table 12. DDR2 SDRAM Capacitance for GV<sub>DD</sub>(typ)=1.8 V

| Parameter/Condition                          | Symbol           | Min | Мах | Unit | Notes |

|----------------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS, DQS | C <sub>DIO</sub> |     | 0.5 | pF   | 1     |

Note:

1. This parameter is sampled.  $GV_{DD} = 1.8 \text{ V} \pm 0.090 \text{ V}$ , f = 1 MHz, T<sub>A</sub> = 25°C,  $V_{OUT} = GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

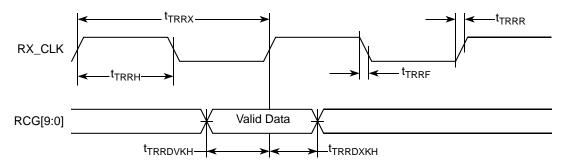

A timing diagram for TBI receive appears in Figure 16.

Figure 16. TBI Single-Clock Mode Receive AC Timing Diagram

## 8.2.6 RGMII and RTBI AC Timing Specifications

This table presents the RGMII and RTBI AC timing specifications.

| Parameter/Condition                                    | Symbol <sup>1</sup>                   | Min               | Тур | Max              | Unit |

|--------------------------------------------------------|---------------------------------------|-------------------|-----|------------------|------|

| Data to clock output skew (at transmitter)             | t <sub>SKRGT</sub> 5                  | -500 <sup>6</sup> | 0   | 500 <sup>6</sup> | ps   |

| Data to clock input skew (at receiver) <sup>2</sup>    | t <sub>SKRGT</sub>                    | 1.0               | _   | 2.8              | ns   |

| Clock period <sup>3</sup>                              | t <sub>RGT</sub> 5                    | 7.2               | 8.0 | 8.8              | ns   |

| Duty cycle for 10BASE-T and 100BASE-TX <sup>3, 4</sup> | t <sub>RGTH</sub> /t <sub>RGT</sub> 5 | 45                | 50  | 55               | %    |

| Rise time (20%–80%)                                    | t <sub>RGTR</sub> 5                   | _                 | _   | 0.75             | ns   |

| Fall time (20%–80%)                                    | t <sub>RGTF</sub> 5                   | _                 |     | 0.75             | ns   |

## Table 33. RGMII and RTBI AC Timing Specifications

Notes:

In general, the clock reference symbol representation for this section is based on the symbols RGT to represent RGMII and RTBI timing. For example, the subscript of t<sub>RGT</sub> represents the TBI (T) receive (RX) clock. Note also that the notation for rise (R) and fall (F) times follows the clock symbol that is being represented. For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (RGT).

- 2. This implies that PC board design requires clocks to be routed such that an additional trace delay of greater than 1.5 ns is added to the associated clock signal.

- 3. For 10 and 100 Mbps,  $t_{RGT}$  scales to 400 ns  $\pm$  40 ns and 40 ns  $\pm$  4 ns, respectively.

- 4. Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet's clock domains as long as the minimum duty cycle is not violated and stretching occurs for no more than three t<sub>RGT</sub> of the lowest speed transitioned between.

5. Guaranteed by characterization.

6. In rev 1.0 silicon, due to errata, t<sub>SKRGT</sub> is -650 ps (min) and 650 ps (max). See "eTSEC 10" in the device errata document.

#### Enhanced Three-Speed Ethernet (eTSEC)

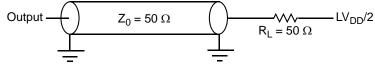

Figure 19 provides the AC test load for eTSEC.

Figure 19. eTSEC AC Test Load

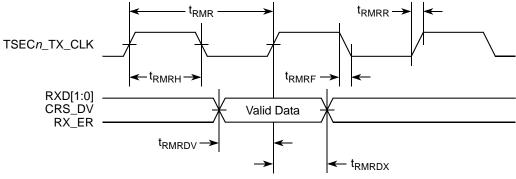

Figure 20 shows the RMII receive AC timing diagram.

Figure 20. RMII Receive AC Timing Diagram

#### **Ethernet Management Interface Electrical Characteristics**

#### Table 37. MII Management AC Timing Specifications (continued)

At recommended operating conditions with  $\text{OV}_{\text{DD}}$  is 3.3 V ± 5%.

| Parameter     | Symbol <sup>1</sup> | Min | Тур | Мах | Unit | Notes |

|---------------|---------------------|-----|-----|-----|------|-------|

| MDC fall time | t <sub>MDHF</sub>   |     |     | 10  | ns   | 4     |

#### Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MDKHDX</sub> symbolizes management data timing (MD) for the time t<sub>MDC</sub> from clock reference (K) high (H) until data outputs (D) are invalid (X) or data hold time. Also, t<sub>MDDVKH</sub> symbolizes management data timing (MD) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MDC</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

- 2. This parameter is dependent on the eTSEC system clock speed, which is half of the Platform Frequency (f<sub>CCB</sub>). The actual ECn\_MDC output clock frequency for a specific eTSEC port can be programmed by configuring the MgmtClk bit field of device's MIIMCFG register, based on the platform (CCB) clock running for the device. The formula is: Platform Frequency (CCB) ÷ (2 × Frequency Divider determined by MIICFG[MgmtClk] encoding selection). For example, if MIICFG[MgmtClk] = 000 and the platform (CCB) is currently running at 533 MHz, f<sub>MDC</sub> = 533) ÷ (2 × 4 × 8) = 533) ÷ 64 = 8.3 MHz. That is, for a system running at a particular platform frequency (f<sub>CCB</sub>), the ECn\_MDC output clock frequency can be programmed between maximum f<sub>MDC</sub> = f<sub>CCB</sub> ÷ 64 and minimum f<sub>MDC</sub> = f<sub>CCB</sub> ÷ 448. See 14.5.3.6.6, "MII Management Configuration Register (MIIMCFG)," in the MPC8548E PowerQUICC™ III Integrated Processor Family Reference Manual for more detail.

- 3. The maximum ECn\_MDC output clock frequency is defined based on the maximum platform frequency for device (533 MHz) divided by 64, while the minimum ECn\_MDC output clock frequency is defined based on the minimum platform frequency for device (333 MHz) divided by 448, following the formula described in Note 2 above.

- 4. Guaranteed by design.

- 5. t<sub>CCB</sub> is the platform (CCB) clock period.

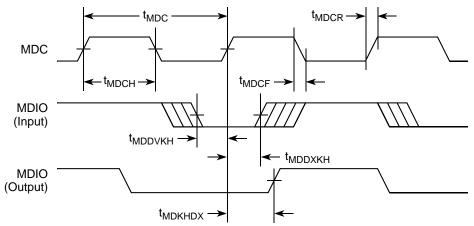

Figure 21 shows the MII management AC timing diagram.

Figure 21. MII Management Interface Timing Diagram

#### High-Speed Serial Interfaces (HSSI)

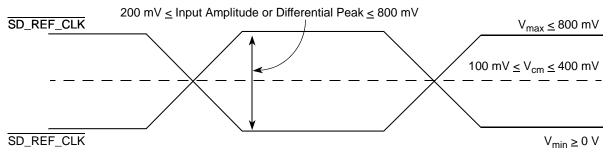

- The input amplitude of the differential clock must be between 400 and 1600 mV differential peak-peak (or between 200 and 800 mV differential peak). In other words, each signal wire of the differential pair must have a single-ended swing less than 800 mV and greater than 200 mV. This requirement is the same for both external DC- or AC-coupled connection.

- For external DC-coupled connection, as described in Section 16.2.1, "SerDes Reference Clock Receiver Characteristics," the maximum average current requirements sets the requirement for average voltage (common mode voltage) to be between 100 and 400 mV. Figure 40 shows the SerDes reference clock input requirement for DC-coupled connection scheme.

- For external AC-coupled connection, there is no common mode voltage requirement for the clock driver. Since the external AC-coupling capacitor blocks the DC level, the clock driver and the SerDes reference clock receiver operate in different command mode voltages. The SerDes reference clock receiver in this connection scheme has its common mode voltage set to SGND\_SRDSn. Each signal wire of the differential inputs is allowed to swing below and above the command mode voltage (SGND\_SRDSn). Figure 41 shows the SerDes reference clock input requirement for AC-coupled connection scheme.

- Single-ended mode

- The reference clock can also be single-ended. The SD\_REF\_CLK input amplitude (single-ended swing) must be between 400 and 800 mV peak-to-peak (from  $V_{min}$  to  $V_{max}$ ) with SD\_REF\_CLK either left unconnected or tied to ground.

- The SD\_REF\_CLK input average voltage must be between 200 and 400 mV. Figure 42 shows the SerDes reference clock input requirement for single-ended signaling mode.

- To meet the input amplitude requirement, the reference clock inputs might need to be DC- or AC-coupled externally. For the best noise performance, the reference of the clock could be DCor AC-coupled into the unused phase (SD\_REF\_CLK) through the same source impedance as the clock input (SD\_REF\_CLK) in use.

Figure 40. Differential Reference Clock Input DC Requirements (External DC-Coupled)

| Characteristic                                     | Symbol          | Range |                   | Unit   | Notes                                                        |

|----------------------------------------------------|-----------------|-------|-------------------|--------|--------------------------------------------------------------|

| Characteristic                                     | Symbol          | Min   | Max               | Onit   | NOICES                                                       |

| Differential input voltage                         | V <sub>IN</sub> | 200   | 1600              | mVp-p  | Measured at receiver                                         |

| Deterministic jitter tolerance                     | J <sub>D</sub>  | 0.37  | —                 | UI p-p | Measured at receiver                                         |

| Combined deterministic and random jitter tolerance | J <sub>DR</sub> | 0.55  | —                 | UI p-p | Measured at receiver                                         |

| Total jitter tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65  | _                 | UI p-p | Measured at receiver                                         |

| Multiple input skew                                | S <sub>MI</sub> | _     | 22                | ns     | Skew at the receiver input between lanes of a multilane link |

| Bit error rate                                     | BER             | _     | 10 <sup>-12</sup> |        | —                                                            |

| Unit interval                                      | UI              | 320   | 320               | ps     | ±100 ppm                                                     |

| Table 68. Receiver | <b>AC Timing</b> | Specifications- | -3.125 GBaud |

|--------------------|------------------|-----------------|--------------|

|--------------------|------------------|-----------------|--------------|

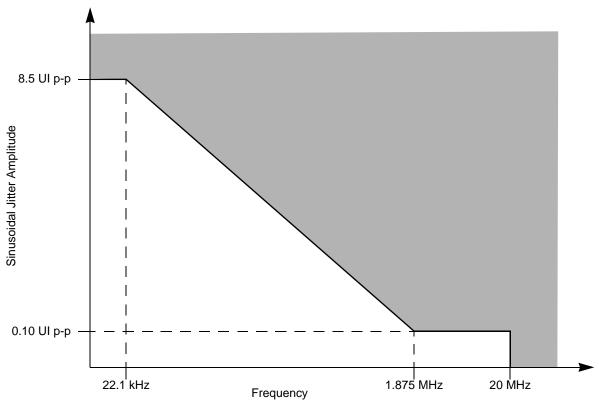

### Note:

1. Total jitter is composed of three components, deterministic jitter, random jitter and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 53. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk and other variable system effects.

Figure 53. Single Frequency Sinusoidal Jitter Limits

| Signal                 | Package Pin Number                                                                                                                                                                                                                                                                                               | Pin Type | Power<br>Supply  | Notes    |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

| PCI1_REQ[4:1]          | AH2, AG4, AG3, AH4                                                                                                                                                                                                                                                                                               | I        | OV <sub>DD</sub> |          |

|                        |                                                                                                                                                                                                                                                                                                                  |          |                  | _        |

|                        |                                                                                                                                                                                                                                                                                                                  |          |                  | —        |

|                        |                                                                                                                                                                                                                                                                                                                  |          |                  | —        |

|                        |                                                                                                                                                                                                                                                                                                                  |          |                  | —        |

| PCI1_REQ0              | AH3                                                                                                                                                                                                                                                                                                              | I/O      | OV <sub>DD</sub> | —        |

| PCI1_CLK               | AH26                                                                                                                                                                                                                                                                                                             | I        | OV <sub>DD</sub> | 39       |

| PCI1_DEVSEL            | AH11                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_FRAME             | AE11                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_IDSEL             | AG9                                                                                                                                                                                                                                                                                                              | I        | OV <sub>DD</sub> | —        |

| PCI1_REQ64/PCI2_FRAME  | AF14                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2, 5, 10 |

| PCI1_ACK64/PCI2_DEVSEL | V15                                                                                                                                                                                                                                                                                                              | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_CLK               | AE28                                                                                                                                                                                                                                                                                                             | I        | OV <sub>DD</sub> | 39       |

| PCI2_IRDY              | AD26                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_PERR              | AD25                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_GNT[4:1]          | AE26, AG24, AF25, AE25                                                                                                                                                                                                                                                                                           | 0        | OV <sub>DD</sub> | 5, 9, 35 |

| PCI2_GNT0              | AG25                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | —        |

| PCI2_SERR              | AD24                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2, 4     |

| PCI2_STOP              | AF24                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_TRDY              | AD27                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_REQ[4:1]          | AD28, AE27, W17, AF26                                                                                                                                                                                                                                                                                            | I        | OV <sub>DD</sub> | —        |

| PCI2_REQ0              | AH25                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | —        |

|                        | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                                       |          | 1                | -        |

| MDQ[0:63]              | L18, J18, K14, L13, L19, M18, L15, L14, A17,<br>B17, A13, B12, C18, B18, B13, A12, H18, F18,<br>J14, F15, K19, J19, H16, K15, D17, G16, K13,<br>D14, D18, F17, F14, E14, A7, A6, D5, A4, C8,<br>D7, B5, B4, A2, B1, D1, E4, A3, B2, D2, E3, F3,<br>G4, J5, K5, F6, G5, J6, K4, J1, K2, M5, M3, J3,<br>J2, L1, M6 | I/O      | GV <sub>DD</sub> | —        |

| MECC[0:7]              | H13, F13, F11, C11, J13, G13, D12, M12                                                                                                                                                                                                                                                                           | I/O      | GV <sub>DD</sub> | —        |

| MDM[0:8]               | M17, C16, K17, E16, B6, C4, H4, K1, E13                                                                                                                                                                                                                                                                          | 0        | GV <sub>DD</sub> | —        |

| MDQS[0:8]              | M15, A16, G17, G14, A5, D3, H1, L2, C13                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> |          |

| MDQS[0:8]              | L17, B16, J16, H14, C6, C2, H3, L4, D13                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> | —        |

| MA[0:15]               | A8, F9, D9, B9, A9, L10, M10, H10, K10, G10,<br>B8, E10, B10, G6, A10, L11                                                                                                                                                                                                                                       | 0        | GV <sub>DD</sub> | —        |

| MBA[0:2]               | F7, J7, M11                                                                                                                                                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —        |

## Table 71. MPC8548E Pinout Listing (continued)

| Signal           | Package Pin Number                                                                                                                                                | Pin Type                                                          | Power<br>Supply  | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------|-------|

| LV <sub>DD</sub> | N8, R7, T9, U6                                                                                                                                                    | Power for<br>TSEC1 and<br>TSEC2<br>(2.5 V, 3.3 V)                 | LV <sub>DD</sub> | _     |

| TV <sub>DD</sub> | W9, Y6                                                                                                                                                            | Power for<br>TSEC3 and<br>TSEC4<br>(2,5 V, 3.3 V)                 | TV <sub>DD</sub> | _     |

| GV <sub>DD</sub> | B3, B11, C7, C9, C14, C17, D4, D6, D10, D15,<br>E2, E8, E11, E18, F5, F12, F16, G3, G7, G9,<br>G11, H5, H12, H15, H17, J10, K3, K12, K16,<br>K18, L6, M4, M8, M13 | Power for<br>DDR1 and<br>DDR2 DRAM<br>I/O voltage<br>(1.8 V, 2.5) | GV <sub>DD</sub> |       |

| BV <sub>DD</sub> | C21, C24, C27, E20, E25, G19, G23, H26, J20                                                                                                                       | Power for local<br>bus (1.8 V,<br>2.5 V, 3.3 V)                   | BV <sub>DD</sub> |       |

| V <sub>DD</sub>  | M19, N12, N14, N16, N18, P11, P13, P15, P17,<br>P19, R12, R14, R16, R18, T11, T13, T15, T17,<br>T19, U12, U14, U16, U18, V17, V19                                 | Power for core<br>(1.1 V)                                         | V <sub>DD</sub>  |       |

| SV <sub>DD</sub> | L25, L27, M24, N28, P24, P26, R24, R27, T25,<br>V24, V26, W24, W27, Y25, AA28, AC27                                                                               | Core Power<br>for SerDes<br>transceivers<br>(1.1 V)               | SV <sub>DD</sub> | —     |

| XV <sub>DD</sub> | L20, L22, N23, P21, R22, T20, U23, V21, W22,<br>Y20                                                                                                               | Pad Power for<br>SerDes<br>transceivers<br>(1.1 V)                | XV <sub>DD</sub> |       |

| AVDD_LBIU        | J28                                                                                                                                                               | Power for local<br>bus PLL<br>(1.1 V)                             | _                | 26    |

| AVDD_PCI1        | AH21                                                                                                                                                              | Power for<br>PCI1 PLL<br>(1.1 V)                                  | _                | 26    |

| AVDD_PCI2        | AH22                                                                                                                                                              | Power for<br>PCI2 PLL<br>(1.1 V)                                  | _                | 26    |

| AVDD_CORE        | AH15                                                                                                                                                              | Power for<br>e500 PLL (1.1<br>V)                                  | _                | 26    |

| AVDD_PLAT        | AH19                                                                                                                                                              | Powerfor CCB<br>PLL (1.1 V)                                       | —                | 26    |

| AVDD_SRDS        | U25                                                                                                                                                               | Power for<br>SRDSPLL<br>(1.1 V)                                   | _                | 26    |

| SENSEVDD         | M14                                                                                                                                                               | 0                                                                 | V <sub>DD</sub>  | 13    |

## Table 71. MPC8548E Pinout Listing (continued)

| Table 72. MPC8547E Pinout Listing (continued | I) |

|----------------------------------------------|----|

|----------------------------------------------|----|

| Signal                 | Package Pin Number                     | Pin Type | Power<br>Supply  | Notes           |

|------------------------|----------------------------------------|----------|------------------|-----------------|

| Reserved               | U20, V22, W20, Y22                     | _        |                  | 15              |

| Reserved               | U21, V23, W21, Y23                     | —        | —                | 15              |

| SD_PLL_TPD             | U28                                    | 0        | XV <sub>DD</sub> | 24              |

| SD_REF_CLK             | T28                                    | I        | XV <sub>DD</sub> | —               |

| SD_REF_CLK             | T27                                    | I        | XV <sub>DD</sub> | —               |

| Reserved               | AC1, AC3                               | —        | _                | 2               |

| Reserved               | M26, V28                               | —        | —                | 32              |

| Reserved               | M25, V27                               | —        | —                | 34              |

| Reserved               | M20, M21, T22, T23                     | —        | —                | 38              |

| · · · · ·              | General-Purpose Output                 |          | l                | •               |

| GPOUT[24:31]           | K26, K25, H27, G28, H25, J26, K24, K23 | 0        | BV <sub>DD</sub> | —               |

| · · · ·                | System Control                         |          |                  | •               |

| HRESET                 | AG17                                   | I        | OV <sub>DD</sub> | —               |

| HRESET_REQ             | AG16                                   | 0        | OV <sub>DD</sub> | 29              |

| SRESET                 | AG20                                   | I        | OV <sub>DD</sub> | —               |

| CKSTP_IN               | AA9                                    | I        | OV <sub>DD</sub> | —               |

| CKSTP_OUT              | AA8                                    | 0        | OV <sub>DD</sub> | 2, 4            |

|                        | Debug                                  |          |                  |                 |

| TRIG_IN                | AB2                                    | I        | OV <sub>DD</sub> | —               |

| TRIG_OUT/READY/QUIESCE | AB1                                    | 0        | OV <sub>DD</sub> | 6, 9,<br>19, 29 |

| MSRCID[0:1]            | AE4, AG2                               | 0        | OV <sub>DD</sub> | 5, 6, 9         |

| MSRCID[2:4]            | AF3, AF1, AF2                          | 0        | OV <sub>DD</sub> | 6, 19,<br>29    |

| MDVAL                  | AE5                                    | 0        | OV <sub>DD</sub> | 6               |

| CLK_OUT                | AE21                                   | 0        | OV <sub>DD</sub> | 11              |

|                        | Clock                                  | •        |                  |                 |

| RTC                    | AF16                                   | I        | OV <sub>DD</sub> | —               |

| SYSCLK                 | AH17                                   | I        | OV <sub>DD</sub> | —               |

|                        | JTAG                                   | •        |                  |                 |

| ТСК                    | AG28                                   | I        | OV <sub>DD</sub> | —               |

| TDI                    | AH28                                   | I        | OV <sub>DD</sub> | 12              |

| TDO                    | AF28                                   | 0        | OV <sub>DD</sub> | —               |

| TMS                    | AH27                                   | I        | OV <sub>DD</sub> | 12              |

| TRST                   | AH23                                   | I        | OV <sub>DD</sub> | 12              |

### Table 72. MPC8547E Pinout Listing (continued)

| Signal     | Package Pin Number | Pin Type | Power<br>Supply | Notes |

|------------|--------------------|----------|-----------------|-------|

| SD_PLL_TPA | U26                | 0        | —               | 24    |

**Note:** All note references in this table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

Table 73 provides the pin-out listing for the MPC8545E 783 FC-PBGA package.

## NOTE

All note references in the following table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

| Signal                        | Package Pin Number                                                                                                                                                                                     | Pin Type         | Power<br>Supply  | Notes    |  |  |  |  |  |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|----------|--|--|--|--|--|

|                               | PCI1 and PCI2 (One 64-Bit or Two 32-Bit)                                                                                                                                                               |                  |                  |          |  |  |  |  |  |

| PCI1_AD[63:32]/PCI2_AD[31:0]  | AB14, AC15, AA15, Y16, W16, AB16, AC16,<br>AA16, AE17, AA18, W18, AC17, AD16, AE16,<br>Y17, AC18, AB18, AA19, AB19, AB21, AA20,<br>AC20, AB20, AB22, AC22, AD21, AB23, AF23,<br>AD23, AE23, AC23, AC24 | I/O              | OV <sub>DD</sub> | 17       |  |  |  |  |  |

| PCI1_AD[31:0]                 | AH6, AE7, AF7, AG7, AH7, AF8, AH8, AE9,<br>AH9, AC10, AB10, AD10, AG10, AA10, AH10,<br>AA11, AB12, AE12, AG12, AH12, AB13, AA12,<br>AC13, AE13, Y14, W13, AG13, V14, AH13,<br>AC14, Y15, AB15          | OV <sub>DD</sub> | 17               |          |  |  |  |  |  |

| PCI1_C_BE[7:4]/PCI2_C_BE[3:0] | AF15, AD14, AE15, AD15                                                                                                                                                                                 | I/O              | OV <sub>DD</sub> | 17       |  |  |  |  |  |

| PCI1_C_BE[3:0]                | AF9, AD11, Y12, Y13                                                                                                                                                                                    | I/O              | OV <sub>DD</sub> | 17       |  |  |  |  |  |

| PCI1_PAR64/PCI2_PAR           | W15                                                                                                                                                                                                    | I/O              | OV <sub>DD</sub> | —        |  |  |  |  |  |

| PCI1_GNT[4:1]                 | AG6, AE6, AF5, AH5                                                                                                                                                                                     | 0                | OV <sub>DD</sub> | 5, 9, 35 |  |  |  |  |  |

| PCI1_GNT0                     | AG5                                                                                                                                                                                                    | I/O              | OV <sub>DD</sub> | —        |  |  |  |  |  |

| PCI1_IRDY                     | AF11                                                                                                                                                                                                   | I/O              | OV <sub>DD</sub> | 2        |  |  |  |  |  |

| PCI1_PAR                      | AD12                                                                                                                                                                                                   | I/O              | OV <sub>DD</sub> | —        |  |  |  |  |  |

| PCI1_PERR                     | AC12                                                                                                                                                                                                   | I/O              | OV <sub>DD</sub> | 2        |  |  |  |  |  |

| PCI1_SERR                     | V13                                                                                                                                                                                                    | I/O              | OV <sub>DD</sub> | 2, 4     |  |  |  |  |  |

| PCI1_STOP                     | W12                                                                                                                                                                                                    | I/O              | OV <sub>DD</sub> | 2        |  |  |  |  |  |

| PCI1_TRDY                     | AG11                                                                                                                                                                                                   | I/O              | OV <sub>DD</sub> | 2        |  |  |  |  |  |

| PCI1_REQ[4:1]                 | AH2, AG4, AG3, AH4                                                                                                                                                                                     | I                | OV <sub>DD</sub> | —        |  |  |  |  |  |

| PCI1_REQ0                     | AH3                                                                                                                                                                                                    | I/O              | OV <sub>DD</sub> | —        |  |  |  |  |  |

| PCI1_CLK                      | AH26                                                                                                                                                                                                   | I                | OV <sub>DD</sub> | 39       |  |  |  |  |  |

| PCI1_DEVSEL                   | AH11                                                                                                                                                                                                   | I/O              | OV <sub>DD</sub> | 2        |  |  |  |  |  |

### Table 73. MPC8545E Pinout Listing

| Signal                 | Package Pin Number                     | Package Pin Number Pin Type Power<br>Supply |                  |                 |  |

|------------------------|----------------------------------------|---------------------------------------------|------------------|-----------------|--|

| SD_TX[0:3]             | M23, N21, P23, R21                     | 0                                           | XV <sub>DD</sub> | —               |  |

| Reserved               | W26, Y28, AA26, AB28                   | _                                           | _                | 40              |  |

| Reserved               | W25, Y27, AA25, AB27                   | —                                           | —                | 40              |  |

| Reserved               | U20, V22, W20, Y22                     | —                                           | —                | 15              |  |

| Reserved               | U21, V23, W21, Y23                     | —                                           | —                | 15              |  |

| SD_PLL_TPD             | U28 O XV <sub>DD</sub>                 |                                             | XV <sub>DD</sub> | 24              |  |

| SD_REF_CLK             | T28                                    | I                                           | XV <sub>DD</sub> | —               |  |

| SD_REF_CLK             | T27                                    | I                                           | XV <sub>DD</sub> | —               |  |

| Reserved               | AC1, AC3                               | —                                           | —                | 2               |  |

| Reserved               | M26, V28                               | —                                           | —                | 32              |  |

| Reserved               | M25, V27                               | —                                           | —                | 34              |  |

| Reserved               | M20, M21, T22, T23                     | —                                           | —                | 38              |  |

|                        | General-Purpose Output                 |                                             | I                |                 |  |

| GPOUT[24:31]           | K26, K25, H27, G28, H25, J26, K24, K23 | 0                                           | BV <sub>DD</sub> | —               |  |

|                        | System Control                         |                                             |                  |                 |  |

| HRESET                 | AG17                                   | I                                           | OV <sub>DD</sub> | —               |  |

| HRESET_REQ             | AG16                                   | 0                                           | OV <sub>DD</sub> | 29              |  |

| SRESET                 | AG20                                   | I                                           | OV <sub>DD</sub> | —               |  |

| CKSTP_IN               | AA9                                    | I                                           | OV <sub>DD</sub> | —               |  |

| CKSTP_OUT              | AA8                                    | 0                                           | OV <sub>DD</sub> | 2, 4            |  |

|                        | Debug                                  |                                             | •                |                 |  |

| TRIG_IN                | AB2                                    | I                                           | OV <sub>DD</sub> | —               |  |

| TRIG_OUT/READY/QUIESCE | AB1                                    | 0                                           | OV <sub>DD</sub> | 6, 9,<br>19, 29 |  |

| MSRCID[0:1]            | AE4, AG2                               | 0                                           | OV <sub>DD</sub> | 5, 6, 9         |  |

| MSRCID[2:4]            | AF3, AF1, AF2                          | 0                                           | OV <sub>DD</sub> | 6, 19,<br>29    |  |

| MDVAL                  | AE5                                    | 0                                           | OV <sub>DD</sub> | 6               |  |

| CLK_OUT                | AE21                                   | 0                                           | OV <sub>DD</sub> | 11              |  |

|                        | Clock                                  |                                             |                  |                 |  |

| RTC                    | AF16                                   | I                                           | OV <sub>DD</sub> | —               |  |

| SYSCLK                 | AH17                                   | I                                           | OV <sub>DD</sub> | —               |  |

|                        | JTAG                                   | •                                           |                  |                 |  |

| ТСК                    | AG28                                   | I                                           | OV <sub>DD</sub> | —               |  |

| TDI                    | AH28                                   | I                                           | OV <sub>DD</sub> | 12              |  |

| Signal           | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin Type                                              | Power<br>Supply  | Notes     |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------|-----------|

|                  | JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11                                                    |                  |           |

| ТСК              | AG28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | —         |

| TDI              | AH28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 12        |

| TDO              | AF28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                     | $OV_{DD}$        | —         |

| TMS              | AH27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 12        |

| TRST             | AH23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 12        |

|                  | DFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                       |                  |           |

| L1_TSTCLK        | AC25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 25        |

| L2_TSTCLK        | AE22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 25        |

| LSSD_MODE        | AH20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 25        |

| TEST_SEL         | AH14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 109       |

|                  | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |                  |           |

| THERM0           | AG1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                     | _                | 14        |

| THERM1           | AH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                     | _                | 14        |

|                  | Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                       |                  |           |