#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

### Details

| Product Status                  | Obsolete                                                                |

|---------------------------------|-------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                            |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                          |

| Speed                           | 1.333GHz                                                                |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                                   |

| RAM Controllers                 | DDR, DDR2, SDRAM                                                        |

| Graphics Acceleration           | No                                                                      |

| Display & Interface Controllers | ·                                                                       |

| Ethernet                        | 10/100/1000Mbps (4)                                                     |

| SATA                            | -                                                                       |

| USB                             | ·                                                                       |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                        |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                      |

| Security Features               | Cryptography, Random Number Generator                                   |

| Package / Case                  | 783-BBGA, FCBGA                                                         |

| Supplier Device Package         | 783-FCBGA (29x29)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8548ecvtaujc |

|                                 |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- VRRP and HSRP support for seamless router fail-over

- Up to 16 exact-match MAC addresses supported

- Broadcast address (accept/reject)

- Hash table match on up to 512 multicast addresses

- Promiscuous mode

- Buffer descriptors backward compatible with MPC8260 and MPC860T 10/100 Ethernet programming models

- RMON statistics support

- 10-Kbyte internal transmit and 2-Kbyte receive FIFOs

- MII management interface for control and status

- Ability to force allocation of header information and buffer descriptors into L2 cache

- OCeaN switch fabric

- Full crossbar packet switch

- Reorders packets from a source based on priorities

- Reorders packets to bypass blocked packets

- Implements starvation avoidance algorithms

- Supports packets with payloads of up to 256 bytes

- Integrated DMA controller

- Four-channel controller

- All channels accessible by both the local and remote masters

- Extended DMA functions (advanced chaining and striding capability)

- Support for scatter and gather transfers

- Misaligned transfer capability

- Interrupt on completed segment, link, list, and error

- Supports transfers to or from any local memory or I/O port

- Selectable hardware-enforced coherency (snoop/no snoop)

- Ability to start and flow control each DMA channel from external 3-pin interface

- Ability to launch DMA from single write transaction

- Two PCI/PCI-X controllers

- PCI 2.2 and PCI-X 1.0 compatible

- One 32-/64-bit PCI/PCI-X port with support for speeds of up to 133 MHz (maximum PCI-X frequency in synchronous mode is 110 MHz)

- One 32-bit PCI port with support for speeds from 16 to 66 MHz (available when the other port is in 32-bit mode)

- Host and agent mode support

- 64-bit dual address cycle (DAC) support

- PCI-X supports multiple split transactions

- Supports PCI-to-memory and memory-to-PCI streaming

# 2.1.3 Output Driver Characteristics

The following table provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

| Driver Type                           | Programmable<br>Output Impedance<br>(Ω) | Supply<br>Voltage                                    | Notes |

|---------------------------------------|-----------------------------------------|------------------------------------------------------|-------|

| Local bus interface utilities signals | 25<br>25                                | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V | 1     |

|                                       | 45(default)<br>45(default)              | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V |       |

| PCI signals                           | 25                                      | OV <sub>DD</sub> = 3.3 V                             | 2     |

|                                       | 45(default)                             |                                                      |       |

| DDR signal                            | 18<br>36 (half strength mode)           | GV <sub>DD</sub> = 2.5 V                             | 3     |

| DDR2 signal                           | 18<br>36 (half strength mode)           | GV <sub>DD</sub> = 1.8 V                             | 3     |

| TSEC/10/100 signals                   | 45                                      | L/TV <sub>DD</sub> = 2.5/3.3 V                       | —     |

| DUART, system control, JTAG           | 45                                      | OV <sub>DD</sub> = 3.3 V                             | —     |

| 12C                                   | 150                                     | OV <sub>DD</sub> = 3.3 V                             |       |

Table 3. Output Drive Capability

Notes:

1. The drive strength of the local bus interface is determined by the configuration of the appropriate bits in PORIMPSCR.

2. The drive strength of the PCI interface is determined by the setting of the PCI\_GNT1 signal at reset.

3. The drive strength of the DDR interface in half-strength mode is at  $T_i = 105^{\circ}C$  and at  $GV_{DD}$  (min).

# 2.2 Power Sequencing

The device requires its power rails to be applied in a specific sequence in order to ensure proper device operation. These requirements are as follows for power-up:

- 1. V<sub>DD</sub>, AV<sub>DD</sub>, BV<sub>DD</sub>, LV<sub>DD</sub>, OV<sub>DD</sub>, SV<sub>DD</sub>, TV<sub>DD</sub>, XV<sub>DD</sub>

- 2.  $GV_{DD}$

All supplies must be at their stable values within 50 ms.

## NOTE

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90% of their value before the voltage rails on the current step reach 10% of theirs.

# NOTE

In order to guarantee MCKE low during power-up, the above sequencing for  $GV_{DD}$  is required. If there is no concern about any of the DDR signals being in an indeterminate state during power-up, then the sequencing for  $GV_{DD}$  is not required.

# 5 **RESET** Initialization

This section describes the AC electrical specifications for the RESET initialization timing requirements of the device. The following table provides the RESET initialization AC timing specifications for the DDR SDRAM component(s).

| Parameter/Condition                                                                                     | Min | Max | Unit    | Notes |

|---------------------------------------------------------------------------------------------------------|-----|-----|---------|-------|

| Required assertion time of HRESET                                                                       | 100 |     | μS      | —     |

| Minimum assertion time for SRESET                                                                       | 3   |     | SYSCLKs | 1     |

| PLL input setup time with stable SYSCLK before HRESET negation                                          | 100 |     | μS      | —     |

| Input setup time for POR configs (other than PLL config) with respect to negation of HRESET             | 4   | —   | SYSCLKs | 1     |

| Input hold time for all POR configs (including PLL config) with respect to negation of HRESET           | 2   | _   | SYSCLKs | 1     |

| Maximum valid-to-high impedance time for actively driven POR configs with respect to negation of HRESET | —   | 5   | SYSCLKs | 1     |

| Table 8. RESET Initialization | Timing | Specifications |

|-------------------------------|--------|----------------|

|-------------------------------|--------|----------------|

### Note:

1. SYSCLK is the primary clock input for the device.

The following table provides the PLL lock times.

## Table 9. PLL Lock Times

| Parameter/Condition              | Min | Мах | Unit |

|----------------------------------|-----|-----|------|

| Core and platform PLL lock times | —   | 100 | μs   |

| Local bus PLL lock time          | —   | 50  | μs   |

| PCI/PCI-X bus PLL lock time      | —   | 50  | μs   |

# 5.1 Power-On Ramp Rate

This section describes the AC electrical specifications for the power-on ramp rate requirements.

Controlling the maximum power-on ramp rate is required to avoid falsely triggering the ESD circuitry. The following table provides the power supply ramp rate specifications.

| Table 10. | Power | Supply | Ramp Rate |

|-----------|-------|--------|-----------|

|-----------|-------|--------|-----------|

| Parameter                    | Min | Мах  | Unit | Notes |

|------------------------------|-----|------|------|-------|

| Required ramp rate for MVREF | _   | 3500 | V/s  | 1     |

| Required ramp rate for VDD   |     | 4000 | V/s  | 1, 2  |

Note:

1. Maximum ramp rate from 200 to 500 mV is most critical as this range may falsely trigger the ESD circuitry.

2. VDD itself is not vulnerable to false ESD triggering; however, as per Section 22.2, "PLL Power Supply Filtering," the recommended AVDD\_CORE, AVDD\_PLAT, AVDD\_LBIU, AVDD\_PCI1 and AVDD\_PCI2 filters are all connected to VDD. Their ramp rates must be equal to or less than the VDD ramp rate.

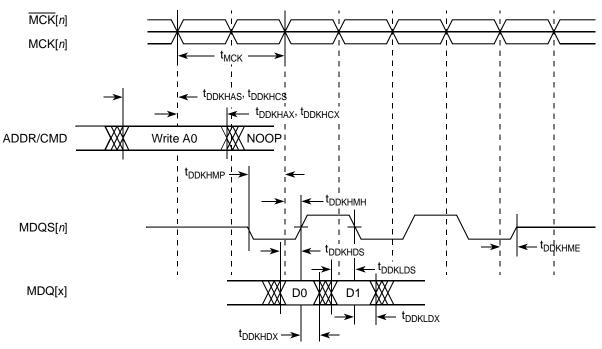

Figure 4 shows the DDR SDRAM output timing diagram.+

Figure 4. DDR SDRAM Output Timing Diagram

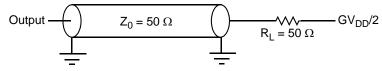

Figure 5 provides the AC test load for the DDR bus.

Figure 5. DDR AC Test Load

| Parameters                                                                      | Symbol                             | Min    | Мах                                      | Unit | Notes   |

|---------------------------------------------------------------------------------|------------------------------------|--------|------------------------------------------|------|---------|

| Supply voltage 2.5 V                                                            | LV <sub>DD</sub> /TV <sub>DD</sub> | 2.37   | 2.63                                     | V    | 1, 2    |

| Output high voltage ( $LV_{DD}/TV_{DD} = Min$ ,<br>$I_{OH} = -1.0 \text{ mA}$ ) | V <sub>OH</sub>                    | 2.00   | LV <sub>DD</sub> /TV <sub>DD</sub> + 0.3 | V    | _       |

| Output low voltage ( $LV_{DD}/TV_{DD} = Min$ ,<br>I <sub>OL</sub> = 1.0 mA)     | V <sub>OL</sub>                    | GND0.3 | 0.40                                     | V    | _       |

| Input high voltage                                                              | V <sub>IH</sub>                    | 1.70   | $LV_{DD}/TV_{DD} + 0.3$                  | V    | —       |

| Input low voltage                                                               | V <sub>IL</sub>                    | -0.3   | 0.90                                     | V    | —       |

| Input high current ( $V_{IN} = LV_{DD}$ , $V_{IN} = TV_{DD}$ )                  | Ι <sub>ΙΗ</sub>                    | —      | 10                                       | μA   | 1, 2, 3 |

| Input low current (V <sub>IN</sub> = GND)                                       | ١ <sub>١L</sub>                    | -15    | —                                        | μA   | 3       |

Table 23. GMII, MII, RMII, TBI, RGMII, RTBI, and FIFO DC Electrical Characteristics

Notes:

1.  $LV_{DD}$  supports eTSECs 1 and 2.

2.  $\mathsf{TV}_{\mathsf{DD}}$  supports eTSECs 3 and 4.

3. Note that the symbol  $V_{IN}$ , in this case, represents the  $LV_{IN}$  and  $TV_{IN}$  symbols referenced in Table 1 and Table 2.

# 8.2 FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications

The AC timing specifications for FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI are presented in this section.

# 8.2.1 FIFO AC Specifications

The basis for the AC specifications for the eTSEC's FIFO modes is the double data rate RGMII and RTBI specifications, since they have similar performances and are described in a source-synchronous fashion like FIFO modes. However, the FIFO interface provides deliberate skew between the transmitted data and source clock in GMII fashion.

When the eTSEC is configured for FIFO modes, all clocks are supplied from external sources to the relevant eTSEC interface. That is, the transmit clock must be applied to the eTSEC*n*'s TSEC*n*\_TX\_CLK, while the receive clock must be applied to pin TSEC*n*\_RX\_CLK. The eTSEC internally uses the transmit clock to synchronously generate transmit data and outputs an echoed copy of the transmit clock back out onto the TSEC*n*\_GTX\_CLK pin (while transmit data appears on TSEC*n*\_TXD[7:0], for example). It is intended that external receivers capture eTSEC transmit data using the clock on TSEC*n*\_GTX\_CLK as a source- synchronous timing reference. Typically, the clock edge that launched the data can be used, since the clock is delayed by the eTSEC to allow acceptable set-up margin at the receiver. Note that there is relationship between the maximum FIFO speed and the platform speed. For more information see Section 4.5, "Platform to FIFO Restrictions."

### PCI/PCI-X

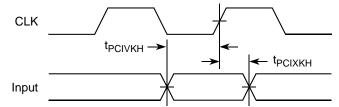

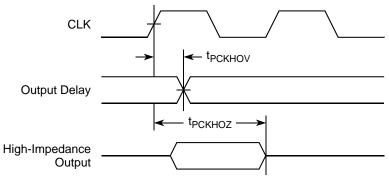

Figure 36 shows the PCI/PCI-X input AC timing conditions.

Figure 36. PCI/PCI-X Input AC Timing Measurement Conditions

Figure 37 shows the PCI/PCI-X output AC timing conditions.

Table 53 provides the PCI-X AC timing specifications at 66 MHz.

| Table 53. PCI-X AC Timing | <b>Specifications at 66 MHz</b> |

|---------------------------|---------------------------------|

|---------------------------|---------------------------------|

| Parameter                                         | Symbol              | Min | Max | Unit   | Notes         |

|---------------------------------------------------|---------------------|-----|-----|--------|---------------|

| SYSCLK to signal valid delay                      | <sup>t</sup> PCKHOV | —   | 3.8 | ns     | 1, 2, 3, 7, 8 |

| Output hold from SYSCLK                           | t <sub>РСКНОХ</sub> | 0.7 | —   | ns     | 1, 10         |

| SYSCLK to output high impedance                   | t <sub>PCKHOZ</sub> | —   | 7   | ns     | 1, 4, 8, 11   |

| Input setup time to SYSCLK                        | t <sub>PCIVKH</sub> | 1.7 | —   | ns     | 3, 5          |

| Input hold time from SYSCLK                       | t <sub>PCIXKH</sub> | 0.5 | —   | ns     | 10            |

| REQ64 to HRESET setup time                        | t <sub>PCRVRH</sub> | 10  | —   | clocks | 11            |

| HRESET to REQ64 hold time                         | t <sub>PCRHRX</sub> | 0   | 50  | ns     | 11            |

| HRESET high to first FRAME assertion              | t <sub>PCRHFV</sub> | 10  | —   | clocks | 9, 11         |

| PCI-X initialization pattern to HRESET setup time | <sup>t</sup> PCIVRH | 10  | —   | clocks | 11            |

# 16 High-Speed Serial Interfaces (HSSI)

The device features one Serializer/Deserializer (SerDes) interface to be used for high-speed serial interconnect applications. The SerDes interface can be used for PCI Express and/or serial RapidIO data transfers.

This section describes the common portion of SerDes DC electrical specifications, which is the DC requirement for SerDes reference clocks. The SerDes data lane's transmitter and receiver reference circuits are also shown.

# 16.1 Signal Terms Definition

The SerDes utilizes differential signaling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals.

Figure 38 shows how the signals are defined. For illustration purpose, only one SerDes lane is used for the description. The figure shows a waveform for either a transmitter output (SD\_TX and  $\overline{SD}_TX$ ) or a receiver input (SD\_RX and  $\overline{SD}_RX$ ). Each signal swings between A volts and B volts where A > B.

Using this waveform, the definitions are as follows. To simplify the illustration, the following definitions assume that the SerDes transmitter and receiver operate in a fully symmetrical differential signaling environment.

• Single-ended swing

The transmitter output signals and the receiver input signals SD\_TX,  $\overline{SD}_TX$ ,  $\overline{SD}_RX$  and  $\overline{SD}_RX$  each have a peak-to-peak swing of A – B volts. This is also referred as each signal wire's single-ended swing.

- Differential output voltage,  $V_{OD}$  (or differential output swing): The differential output voltage (or swing) of the transmitter,  $V_{OD}$ , is defined as the difference of the two complimentary output voltages:  $V_{SD_TX} - V_{\overline{SD_TX}}$ . The  $V_{OD}$  value can be either positive or negative.

- Differential input voltage, V<sub>ID</sub> (or differential input swing): The differential input voltage (or swing) of the receiver, V<sub>ID</sub>, is defined as the difference of the two complimentary input voltages: V<sub>SD\_RX</sub> – V<sub>SD\_RX</sub>. The V<sub>ID</sub> value can be either positive or negative.

- Differential peak voltage,  $V_{DIFFp}$ The peak value of the differential transmitter output signal or the differential receiver input signal is defined as differential peak voltage,  $V_{DIFFp} = |A - B|$  volts.

- Differential peak-to-peak,  $V_{DIFFp-p}$ Because the differential output signal of the transmitter and the differential input signal of the receiver each range from A – B to –(A – B) volts, the peak-to-peak value of the differential transmitter output signal or the differential receiver input signal is defined as differential peak-to-peak voltage,  $V_{DIFFp-p} = 2 \times V_{DIFFp} = 2 \times |(A - B)|$  volts, which is twice of differential swing in amplitude, or twice of the differential peak. For example, the output differential peak-to-peak voltage can also be calculated as  $V_{TX-DIFFp-p} = 2 \times |V_{OD}|$ .

- Common mode voltage,  $V_{cm}$ The common mode voltage is equal to one half of the sum of the voltages between each conductor

### High-Speed Serial Interfaces (HSSI)

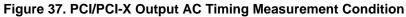

Figure 43 shows the SerDes reference clock connection reference circuits for HCSL type clock driver. It assumes that the DC levels of the clock driver chip is compatible with SerDes reference clock input's DC requirement.

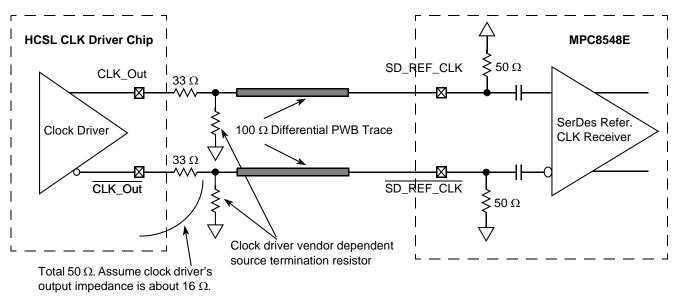

Figure 44 shows the SerDes reference clock connection reference circuits for LVDS type clock driver. Since LVDS clock driver's common mode voltage is higher than the SerDes reference clock input's allowed range (100–400 mV), AC-coupled connection scheme must be used. It assumes the LVDS output driver features 50- $\Omega$  termination resistor. It also assumes that the LVDS transmitter establishes its own common mode level without relying on the receiver or other external component.

Figure 45 shows the SerDes reference clock connection reference circuits for LVPECL type clock driver. Since LVPECL driver's DC levels (both common mode voltages and output swing) are incompatible with the SerDes reference clock input's DC requirement, AC-coupling must be used. Figure 45 assumes that the LVPECL clock driver's output impedance is 50  $\Omega$ . R1 is used to DC-bias the LVPECL outputs prior

# 16.2.4 AC Requirements for SerDes Reference Clocks

The clock driver selected must provide a high quality reference clock with low phase noise and cycle-to-cycle jitter. Phase noise less than 100 kHz can be tracked by the PLL and data recovery loops and is less of a problem. Phase noise above 15 MHz is filtered by the PLL. The most problematic phase noise occurs in the 1–15 MHz range. The source impedance of the clock driver must be 50  $\Omega$  to match the transmission line and reduce reflections which are a source of noise to the system.

The detailed AC requirements of the SerDes reference clocks are defined by each interface protocol based on application usage. See the following sections for detailed information:

- Section 17.2, "AC Requirements for PCI Express SerDes Clocks"

- Section 18.2, "AC Requirements for Serial RapidIO SD\_REF\_CLK and SD\_REF\_CLK"

# 16.2.4.1 Spread Spectrum Clock

SD\_REF\_CLK/SD\_REF\_CLK are designed to work with a spread spectrum clock (+0% to -0.5% spreading at 30–33 kHz rate is allowed), assuming both ends have same reference clock. For better results, a source without significant unintended modulation must be used.

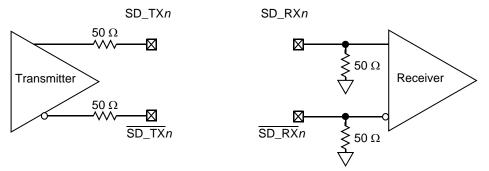

# 16.3 SerDes Transmitter and Receiver Reference Circuits

Figure 47 shows the reference circuits for SerDes data lane's transmitter and receiver.

Figure 47. SerDes Transmitter and Receiver Reference Circuits

The DC and AC specification of SerDes data lanes are defined in each interface protocol section below (PCI Express, Serial Rapid IO, or SGMII) in this document based on the application usage:

- Section 17, "PCI Express"

- Section 18, "Serial RapidIO"

Note that external an AC coupling capacitor is required for the above three serial transmission protocols with the capacitor value defined in the specification of each protocol section.

**Package Description**

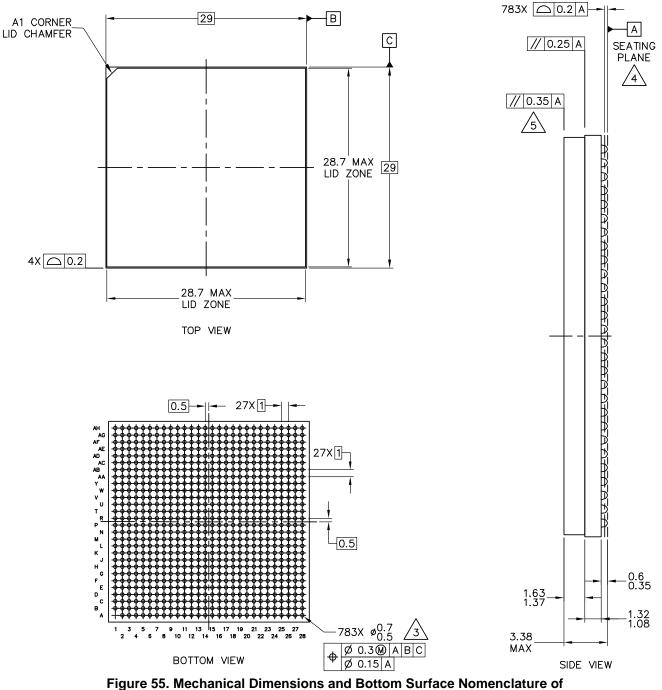

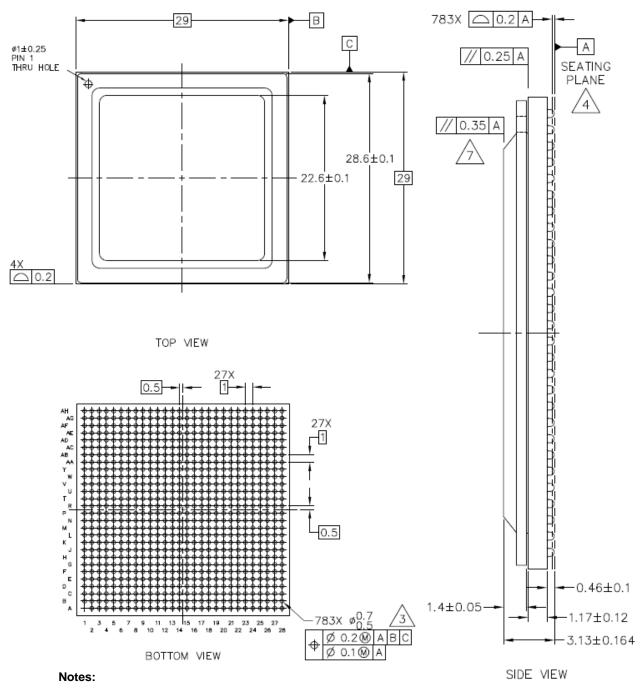

# 19.2 Mechanical Dimensions of the HiCTE FC-CBGA and FC-PBGA with Full Lid

The following figures show the mechanical dimensions and bottom surface nomenclature for the MPC8548E HiCTE FC-CBGA and FC-PBGA packages.

the HiCTE FC-CBGA and FC-PBGA with Full Lid

**Package Description**

- 1. All dimensions are in millimeters.

- 2. Dimensioning and tolerancing per ASME Y14.5M-1994.

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

- 5. Capacitors may not be present on all devices.

- 6. Caution must be taken not to short capacitors or exposed metal capacitor pads on package top.

- 7. Parallelism measurement shall exclude any effect of mark on top surface of package.

- 8. All dimensions are symmetric across the package center lines unless dimensioned otherwise.

## Figure 56. Mechanical Dimensions and Bottom Surface Nomenclature of the FC-PBGA with Stamped Lid

# **19.3 Pinout Listings**

# NOTE

The DMA\_DACK[0:1] and TEST\_SEL/TEST\_SEL pins must be set to a proper state during POR configuration. See the pinlist table of the individual device for more details.

For MPC8548/47/45, GPIOs are still available on PCI1\_AD[63:32]/PC2\_AD[31:0] pins if they are not used for PCI functionality.

For MPC8545/43, eTSEC does not support 16 bit FIFO mode.

Table 71 provides the pinout listing for the MPC8548E 783 FC-PBGA package.

| Signal                        | Package Pin Number                                                                                                                                                                                     | Pin Type | Power<br>Supply  | Notes    |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

|                               | PCI1 and PCI2 (One 64-Bit or Two 32-Bit)                                                                                                                                                               |          |                  | •        |

| PCI1_AD[63:32]/PCI2_AD[31:0]  | AB14, AC15, AA15, Y16, W16, AB16, AC16,<br>AA16, AE17, AA18, W18, AC17, AD16, AE16,<br>Y17, AC18, AB18, AA19, AB19, AB21, AA20,<br>AC20, AB20, AB22, AC22, AD21, AB23, AF23,<br>AD23, AE23, AC23, AC24 | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_AD[31:0]                 | AH6, AE7, AF7, AG7, AH7, AF8, AH8, AE9,<br>AH9, AC10, AB10, AD10, AG10, AA10, AH10,<br>AA11, AB12, AE12, AG12, AH12, AB13, AA12,<br>AC13, AE13, Y14, W13, AG13, V14, AH13,<br>AC14, Y15, AB15          | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_C_BE[7:4]/PCI2_C_BE[3:0] | AF15, AD14, AE15, AD15                                                                                                                                                                                 | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_C_BE[3:0]                | AF9, AD11, Y12, Y13                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_PAR64/PCI2_PAR           | W15                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> |          |

| PCI1_GNT[4:1]                 | AG6, AE6, AF5, AH5                                                                                                                                                                                     | 0        | OV <sub>DD</sub> | 5, 9, 35 |

| PCI1_GNT0                     | AG5                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | —        |

| PCI1_IRDY                     | AF11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_PAR                      | AD12                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | —        |

| PCI1_PERR                     | AC12                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_SERR                     | V13                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2, 4     |

| PCI1_STOP                     | W12                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_TRDY                     | AG11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |

### Table 71. MPC8548E Pinout Listing

## Table 71. MPC8548E Pinout Listing (continued)

| Signal                   | Package Pin Number                                                                                                                                                      | Pin Type | Power<br>Supply  | Notes   |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|---------|

| MWE                      | E7                                                                                                                                                                      | 0        | GV <sub>DD</sub> |         |

| MCAS                     | H7                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —       |

| MRAS                     | L8                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —       |

| MCKE[0:3]                | F10, C10, J11, H11                                                                                                                                                      | 0        | GV <sub>DD</sub> | 11      |

| MCS[0:3]                 | K8, J8, G8, F8                                                                                                                                                          | 0        | GV <sub>DD</sub> | —       |

| MCK[0:5]                 | H9, B15, G2, M9, A14, F1                                                                                                                                                | 0        | GV <sub>DD</sub> | —       |

| MCK[0:5]                 | J9, A15, G1, L9, B14, F2                                                                                                                                                | 0        | GV <sub>DD</sub> | —       |

| MODT[0:3]                | E6, K6, L7, M7                                                                                                                                                          | 0        | GV <sub>DD</sub> | —       |

| MDIC[0:1]                | A19, B19                                                                                                                                                                | I/O      | GV <sub>DD</sub> | 36      |

|                          | Local Bus Controller Interface                                                                                                                                          |          | •                | -       |

| LAD[0:31]                | E27, B20, H19, F25, A20, C19, E28, J23, A25,<br>K22, B28, D27, D19, J22, K20, D28, D25, B25,<br>E22, F22, F21, C25, C22, B23, F20, A23, A22,<br>E19, A21, D21, F19, B21 | I/O      | BV <sub>DD</sub> | _       |

| LDP[0:3]                 | K21, C28, B26, B22                                                                                                                                                      | I/O      | BV <sub>DD</sub> | —       |

| LA[27]                   | H21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LA[28:31]                | H20, A27, D26, A28                                                                                                                                                      | 0        | BV <sub>DD</sub> | 5, 7, 9 |

| LCS[0:4]                 | J25, C20, J24, G26, A26                                                                                                                                                 | 0        | BV <sub>DD</sub> |         |

| LCS5/DMA_DREQ2           | D23                                                                                                                                                                     | I/O      | BV <sub>DD</sub> | 1       |

| LCS6/DMA_DACK2           | G20                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 1       |

| LCS7/DMA_DDONE2          | E21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 1       |

| LWE0/LBS0/LSDDQM[0]      | G25                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE1/LBS1/LSDDQM[1]      | C23                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE2/LBS2/LSDDQM[2]      | J21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE3/LBS3/LSDDQM[3]      | A24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LALE                     | H24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| LBCTL                    | G27                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| LGPL0/LSDA10             | F23                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LGPL1/LSDWE              | G22                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LGPL2/LOE/LSDRAS         | B27                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| LGPL3/LSDCAS             | F24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LGPL4/LGTA/LUPWAIT/LPBSE | H23                                                                                                                                                                     | I/O      | BV <sub>DD</sub> | —       |

| LGPL5                    | E26                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LCKE                     | E24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | -       |

| LCLK[0:2]                | E23, D24, H22                                                                                                                                                           | 0        | BV <sub>DD</sub> | —       |

| Signal           | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin Type                                                            | Power<br>Supply  | Notes        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------|--------------|

|                  | DFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I                                                                   |                  | 1            |

| L1_TSTCLK        | AC25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                                   | OV <sub>DD</sub> | 25           |

| L2_TSTCLK        | AE22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                                   | OV <sub>DD</sub> | 25           |

| LSSD_MODE        | AH20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                                   | $OV_{DD}$        | 25           |

| TEST_SEL         | AH14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                                   | $OV_{DD}$        | 25           |

|                  | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                     |                  |              |

| THERMO           | AG1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                                   | _                | 14           |

| THERM1           | AH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                                   | _                | 14           |

|                  | Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                     |                  |              |

| ASLEEP           | AH18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                   | OV <sub>DD</sub> | 9, 19,<br>29 |

|                  | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | I                                                                   |                  |              |

| GND              | <ul> <li>A11, B7, B24, C1, C3, C5, C12, C15, C26, D8,<br/>D11, D16, D20, D22, E1, E5, E9, E12, E15, E17,<br/>F4, F26, G12, G15, G18, G21, G24, H2, H6, H8,<br/>H28, J4, J12, J15, J17, J27, K7, K9, K11, K27,<br/>L3, L5, L12, L16, N11, N13, N15, N17, N19, P4,<br/>P9, P12, P14, P16, P18, R11, R13, R15, R17,<br/>R19, T4, T12, T14, T16, T18, U8, U11, U13,<br/>U15, U17, U19, V4, V12, V18, W6, W19, Y4, Y9,<br/>Y11, Y19, AA6, AA14, AA17, AA22, AA23, AB4,<br/>AC2, AC11, AC19, AC26, AD5, AD9, AD22,<br/>AE3, AE14, AF6, AF10, AF13, AG8, AG27,<br/>K28, L24, L26, N24, N27, P25, R28, T24, T26,<br/>U24, V25, W28, Y24, Y26, AA24, AA27, AB25,<br/>AC28, L21, L23, N22, P20, R23, T21, U22, V20,<br/>W23, Y21, U27</li> </ul> | _                                                                   | _                | -            |

| OV <sub>DD</sub> | V16, W11, W14, Y18, AA13, AA21, AB11,<br>AB17, AB24, AC4, AC9, AC21, AD6, AD13,<br>AD17, AD19, AE10, AE8, AE24, AF4, AF12,<br>AF22, AF27, AG26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Power for PCI<br>and other<br>standards<br>(3.3 V)                  | OV <sub>DD</sub> | _            |

| LV <sub>DD</sub> | N8, R7, T9, U6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Power for<br>TSEC1 and<br>TSEC2<br>(2.5 V, 3.3 V)                   | LV <sub>DD</sub> | _            |

| TV <sub>DD</sub> | W9, Y6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Power for<br>TSEC3 and<br>TSEC4<br>(2,5 V, 3.3 V)                   | TV <sub>DD</sub> | —            |

| GV <sub>DD</sub> | B3, B11, C7, C9, C14, C17, D4, D6, D10, D15,<br>E2, E8, E11, E18, F5, F12, F16, G3, G7, G9,<br>G11, H5, H12, H15, H17, J10, K3, K12, K16,<br>K18, L6, M4, M8, M13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Power for<br>DDR1 and<br>DDR2 DRAM<br>I/O voltage<br>(1.8 V, 2.5 V) | GV <sub>DD</sub> | -            |

Package Description

| Signal           | Package Pin Number                                                                                                                                                | Pin Type                                                            | Power<br>Supply  | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------|-------|

| GV <sub>DD</sub> | B3, B11, C7, C9, C14, C17, D4, D6, D10, D15,<br>E2, E8, E11, E18, F5, F12, F16, G3, G7, G9,<br>G11, H5, H12, H15, H17, J10, K3, K12, K16,<br>K18, L6, M4, M8, M13 | Power for<br>DDR1 and<br>DDR2 DRAM<br>I/O voltage<br>(1.8 V, 2.5 V) | GV <sub>DD</sub> | _     |

| BV <sub>DD</sub> | C21, C24, C27, E20, E25, G19, G23, H26, J20                                                                                                                       | Power for local<br>bus (1.8 V,<br>2.5 V, 3.3 V)                     | BV <sub>DD</sub> | _     |

| V <sub>DD</sub>  | M19, N12, N14, N16, N18, P11, P13, P15, P17,<br>P19, R12, R14, R16, R18, T11, T13, T15, T17,<br>T19, U12, U14, U16, U18, V17, V19                                 | Power for core<br>(1.1 V)                                           | V <sub>DD</sub>  | -     |

| SV <sub>DD</sub> | L25, L27, M24, N28, P24, P26, R24, R27, T25,<br>V24, V26, W24, W27, Y25, AA28, AC27                                                                               | Core power for<br>SerDes<br>transceivers<br>(1.1 V)                 | SV <sub>DD</sub> | _     |

| XV <sub>DD</sub> | L20, L22, N23, P21, R22, T20, U23, V21, W22,<br>Y20                                                                                                               | Pad power for<br>SerDes<br>transceivers<br>(1.1 V)                  | XV <sub>DD</sub> | —     |

| AVDD_LBIU        | J28                                                                                                                                                               | Power for local<br>bus PLL<br>(1.1 V)                               | _                | 26    |

| AVDD_PCI1        | AH21                                                                                                                                                              | Power for<br>PCI1 PLL<br>(1.1 V)                                    | —                | 26    |

| AVDD_PCI2        | AH22                                                                                                                                                              | Power for<br>PCI2 PLL<br>(1.1 V)                                    | _                | 26    |

| AVDD_CORE        | AH15                                                                                                                                                              | Power for<br>e500 PLL (1.1<br>V)                                    | _                | 26    |

| AVDD_PLAT        | AH19                                                                                                                                                              | Powerfor CCB<br>PLL (1.1 V)                                         | —                | 26    |

| AVDD_SRDS        | U25                                                                                                                                                               | Power for<br>SRDSPLL (1.1<br>V)                                     | _                | 26    |

| SENSEVDD         | M14                                                                                                                                                               | 0                                                                   | V <sub>DD</sub>  | 13    |

| SENSEVSS         | M16                                                                                                                                                               | —                                                                   | —                | 13    |

|                  | Analog Signals                                                                                                                                                    |                                                                     |                  | •     |

| MVREF            | A18                                                                                                                                                               | I<br>Reference<br>voltage signal<br>for DDR                         | MVREF            |       |

## Table 73. MPC8545E Pinout Listing (continued)

## Table 74. MPC8543E Pinout Listing (continued)

| Signal                   | Package Pin Number                                                                                                                                                      | Pin Type | Power<br>Supply  | Notes   |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|---------|

| MWE                      | E7                                                                                                                                                                      | 0        | GV <sub>DD</sub> |         |

| MCAS                     | H7                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —       |

| MRAS                     | L8                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —       |

| MCKE[0:3]                | F10, C10, J11, H11                                                                                                                                                      | 0        | GV <sub>DD</sub> | 11      |

| MCS[0:3]                 | K8, J8, G8, F8                                                                                                                                                          | 0        | GV <sub>DD</sub> | — —     |

| MCK[0:5]                 | H9, B15, G2, M9, A14, F1                                                                                                                                                | 0        | GV <sub>DD</sub> | —       |

| MCK[0:5]                 | J9, A15, G1, L9, B14, F2                                                                                                                                                | 0        | GV <sub>DD</sub> | —       |

| MODT[0:3]                | E6, K6, L7, M7                                                                                                                                                          | 0        | $GV_DD$          | —       |

| MDIC[0:1]                | A19, B19                                                                                                                                                                | I/O      | $GV_DD$          | 36      |

|                          | Local Bus Controller Interface                                                                                                                                          |          |                  |         |

| LAD[0:31]                | E27, B20, H19, F25, A20, C19, E28, J23, A25,<br>K22, B28, D27, D19, J22, K20, D28, D25, B25,<br>E22, F22, F21, C25, C22, B23, F20, A23, A22,<br>E19, A21, D21, F19, B21 | I/O      | BV <sub>DD</sub> | _       |

| LDP[0:3]                 | K21, C28, B26, B22                                                                                                                                                      | I/O      | BV <sub>DD</sub> | —       |

| LA[27]                   | H21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LA[28:31]                | H20, A27, D26, A28                                                                                                                                                      | 0        | BV <sub>DD</sub> | 5, 7, 9 |

| LCS[0:4]                 | J25, C20, J24, G26, A26                                                                                                                                                 | 0        | BV <sub>DD</sub> | —       |

| LCS5/DMA_DREQ2           | D23                                                                                                                                                                     | I/O      | BV <sub>DD</sub> | 1       |

| LCS6/DMA_DACK2           | G20                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 1       |

| LCS7/DMA_DDONE2          | E21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 1       |

| LWE0/LBS0/LSDDQM[0]      | G25                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE1/LBS1/LSDDQM[1]      | C23                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE2/LBS2/LSDDQM[2]      | J21                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE3/LBS3/LSDDQM[3]      | A24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LALE                     | H24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| LBCTL                    | G27                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| LGPL0/LSDA10             | F23                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LGPL1/LSDWE              | G22                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LGPL2/LOE/LSDRAS         | B27                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| LGPL3/LSDCAS             | F24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LGPL4/LGTA/LUPWAIT/LPBSE | H23                                                                                                                                                                     | I/O      | BV <sub>DD</sub> | —       |

| LGPL5                    | E26                                                                                                                                                                     | 0        | BV <sub>DD</sub> | 5, 9    |

| LCKE                     | E24                                                                                                                                                                     | 0        | BV <sub>DD</sub> | —       |

| LCLK[0:2]                | E23, D24, H22                                                                                                                                                           | 0        | BV <sub>DD</sub> | —       |

Package Description

| Signal           | Package Pin Number                                                                                                                                                | Pin Type                                                              | Power<br>Supply  | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------|-------|

| TV <sub>DD</sub> | W9, Y6                                                                                                                                                            | Power for<br>TSEC3 and<br>TSEC4<br>(2,5 V, 3.3 V)                     | TV <sub>DD</sub> | _     |

| GV <sub>DD</sub> | B3, B11, C7, C9, C14, C17, D4, D6, D10, D15,<br>E2, E8, E11, E18, F5, F12, F16, G3, G7, G9,<br>G11, H5, H12, H15, H17, J10, K3, K12, K16,<br>K18, L6, M4, M8, M13 | Power for<br>DDR1 and<br>DDR2<br>DRAM I/O<br>voltage<br>(1.8 V,2.5 V) | GV <sub>DD</sub> | _     |

| BV <sub>DD</sub> | C21, C24, C27, E20, E25, G19, G23, H26, J20                                                                                                                       | Power for<br>local bus<br>(1.8 V, 2.5 V,<br>3.3 V)                    | BV <sub>DD</sub> | _     |

| V <sub>DD</sub>  | M19, N12, N14, N16, N18, P11, P13, P15, P17,<br>P19, R12, R14, R16, R18, T11, T13, T15, T17,<br>T19, U12, U14, U16, U18, V17, V19                                 | Power for core (1.1 V)                                                | V <sub>DD</sub>  | _     |

| SV <sub>DD</sub> | L25, L27, M24, N28, P24, P26, R24, R27, T25,<br>V24, V26, W24, W27, Y25, AA28, AC27                                                                               | Core power<br>for SerDes<br>transceivers<br>(1.1 V)                   | SV <sub>DD</sub> | _     |

| XV <sub>DD</sub> | L20, L22, N23, P21, R22, T20, U23, V21, W22,<br>Y20                                                                                                               | Pad power<br>for SerDes<br>transceivers<br>(1.1 V)                    | XV <sub>DD</sub> | _     |

| AVDD_LBIU        | J28                                                                                                                                                               | Power for<br>local bus<br>PLL<br>(1.1 V)                              | _                | 26    |

| AVDD_PCI1        | AH21                                                                                                                                                              | Power for<br>PCI1 PLL<br>(1.1 V)                                      | _                | 26    |

| AVDD_PCI2        | AH22                                                                                                                                                              | Power for<br>PCI2 PLL<br>(1.1 V)                                      | _                | 26    |

| AVDD_CORE        | AH15                                                                                                                                                              | Power for<br>e500 PLL<br>(1.1 V)                                      | _                | 26    |

| AVDD_PLAT        | AH19                                                                                                                                                              | Power for<br>CCB PLL<br>(1.1 V)                                       | _                | 26    |

| AVDD_SRDS        | U25                                                                                                                                                               | Power for<br>SRDSPLL<br>(1.1 V)                                       | _                | 26    |

| SENSEVDD         | M14                                                                                                                                                               | 0                                                                     | V <sub>DD</sub>  | 13    |

## Table 74. MPC8543E Pinout Listing (continued)

### System Design Information

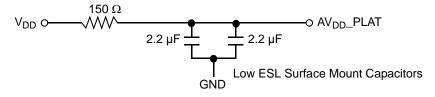

level must always be equivalent to  $V_{DD}$ , and preferably these voltages are derived directly from  $V_{DD}$  through a low frequency filter scheme such as the following.

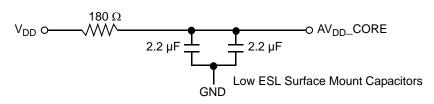

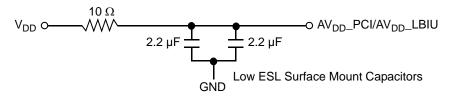

There are a number of ways to reliably provide power to the PLLs, but the recommended solution is to provide independent filter circuits per PLL power supply as illustrated in Figure 57, one to each of the  $AV_{DD}$  pins. By providing independent filters to each PLL the opportunity to cause noise injection from one PLL to the other is reduced.

This circuit is intended to filter noise in the PLLs resonant frequency range from a 500 kHz to 10 MHz range. It must be built with surface mount capacitors with minimum Effective Series Inductance (ESL). Consistent with the recommendations of Dr. Howard Johnson in *High Speed Digital Design: A Handbook of Black Magic* (Prentice Hall, 1993), multiple small capacitors of equal value are recommended over a single large value capacitor.

Each circuit must be placed as close as possible to the specific  $AV_{DD}$  pin being supplied to minimize noise coupled from nearby circuits. It must be routed directly from the capacitors to the  $AV_{DD}$  pin, which is on the periphery of the footprint, without the inductance of vias.

Figure 57 through Figure 59 shows the PLL power supply filter circuits.

Figure 57. PLL Power Supply Filter Circuit with PLAT Pins

Figure 58. PLL Power Supply Filter Circuit with CORE Pins

Figure 59. PLL Power Supply Filter Circuit with PCI/LBIU Pins

The AV<sub>DD</sub>\_SRDS signal provides power for the analog portions of the SerDes PLL. To ensure stability of the internal clock, the power supplied to the PLL is filtered using a circuit similar to the one shown in following figure. For maximum effectiveness, the filter circuit is placed as closely as possible to the AV<sub>DD</sub>\_SRDS ball to ensure it filters out as much noise as possible. The ground connection must be near the AV<sub>DD</sub>\_SRDS ball. The 0.003- $\mu$ F capacitor is closest to the ball, followed by the two 2.2  $\mu$ F capacitors, and finally the 1  $\Omega$  resistor to the board supply plane. The capacitors are connected from AV<sub>DD</sub>\_SRDS to

- First, the board must have at least 10 × 10-nF SMT ceramic chip capacitors as close as possible to the supply balls of the device. Where the board has blind vias, these capacitors must be placed directly below the chip supply and ground connections. Where the board does not have blind vias, these capacitors must be placed in a ring around the device as close to the supply and ground connections as possible.

- Second, there must be a  $1-\mu F$  ceramic chip capacitor from each SerDes supply (SV<sub>DD</sub> and XV<sub>DD</sub>) to the board ground plane on each side of the device. This must be done for all SerDes supplies.

- Third, between the device and any SerDes voltage regulator there must be a 10- $\mu$ F, low equivalent series resistance (ESR) SMT tantalum chip capacitor and a 100- $\mu$ F, low ESR SMT tantalum chip capacitor. This must be done for all SerDes supplies.

# 22.5 Connection Recommendations

To ensure reliable operation, it is highly recommended to connect unused inputs to an appropriate signal level. All unused active low inputs must be tied to  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$ , as required. All unused active high inputs must be connected to GND. All NC (no-connect) signals must remain unconnected. Power and ground connections must be made to all external  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$ , and GND pins of the device.

# 22.6 Pull-Up and Pull-Down Resistor Requirements

The device requires weak pull-up resistors (2–10 k $\Omega$  is recommended) on open drain type pins including I<sup>2</sup>C pins and PIC (interrupt) pins.

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 63. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions as most have asynchronous behavior and spurious assertion gives unpredictable results.

The following pins must not be pulled down during power-on reset: TSEC3\_TXD[3], HRESET\_REQ, TRIG\_OUT/READY/QUIESCE, MSRCID[2:4], ASLEEP. The DMA\_DACK[0:1], and TEST\_SEL/TEST\_SEL pins must be set to a proper state during POR configuration. See the pinlist table of the individual device for more details

See the PCI 2.2 specification for all pull ups required for PCI.

# 22.7 Output Buffer DC Impedance

The device drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ).

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $OV_{DD}$  or GND. Then, the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 61). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open) and  $R_P$  is trimmed until the voltage at the pad equals  $OV_{DD}/2$ .  $R_P$  then becomes the resistance of the pull-up devices.  $R_P$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_P + R_N)/2$ .

# 23.2 Part Marking

Parts are marked as the example shown in Figure 64.

### Notes:

TWLYYWW is final test traceability code. MMMMM is 5 digit mask number. CCCCC is the country of assembly. This space is left blank if parts are assembled in the United States. YWWLAZ is assembly traceability code.

### Figure 64. Part Marking for CBGA and PBGA Device