#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 1.0GHz                                                                 |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                                  |

| RAM Controllers                 | DDR, DDR2, SDRAM                                                       |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (4)                                                    |

| SATA                            | -                                                                      |

| USB                             | ·                                                                      |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                     |

| Security Features               | Cryptography, Random Number Generator                                  |

| Package / Case                  | 783-BBGA, FCBGA                                                        |

| Supplier Device Package         | 783-FCBGA (29x29)                                                      |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8548ecvuaqg |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Overview

- Memory prefetching of PCI read accesses

- Supports posting of processor-to-PCI and PCI-to-memory writes

- PCI 3.3-V compatible

- Selectable hardware-enforced coherency

- Serial RapidIO<sup>™</sup> interface unit

- Supports RapidIO<sup>™</sup> Interconnect Specification, Revision 1.2

- Both  $1 \times$  and  $4 \times$  LP-serial link interfaces

- Long- and short-haul electricals with selectable pre-compensation

- Transmission rates of 1.25, 2.5, and 3.125 Gbaud (data rates of 1.0, 2.0, and 2.5 Gbps) per lane

- Auto detection of 1- and 4-mode operation during port initialization

- Link initialization and synchronization

- Large and small size transport information field support selectable at initialization time

- 34-bit addressing

- Up to 256 bytes data payload

- All transaction flows and priorities

- Atomic set/clr/inc/dec for read-modify-write operations

- Generation of IO\_READ\_HOME and FLUSH with data for accessing cache-coherent data at a remote memory system

- Receiver-controlled flow control

- Error detection, recovery, and time-out for packets and control symbols as required by the RapidIO specification

- Register and register bit extensions as described in part VIII (Error Management) of the RapidIO specification

- Hardware recovery only

- Register support is not required for software-mediated error recovery.

- Accept-all mode of operation for fail-over support

- Support for RapidIO error injection

- Internal LP-serial and application interface-level loopback modes

- Memory and PHY BIST for at-speed production test

- RapidIO-compatible message unit

- 4 Kbytes of payload per message

- Up to sixteen 256-byte segments per message

- Two inbound data message structures within the inbox

- Capable of receiving three letters at any mailbox

- Two outbound data message structures within the outbox

- Capable of sending three letters simultaneously

- Single segment multicast to up to 32 devIDs

- Chaining and direct modes in the outbox

# 2.1.3 Output Driver Characteristics

The following table provides information on the characteristics of the output driver strengths. The values are preliminary estimates.

| Driver Type                           | Programmable<br>Output Impedance<br>(Ω) | Supply<br>Voltage                                    | Notes |

|---------------------------------------|-----------------------------------------|------------------------------------------------------|-------|

| Local bus interface utilities signals | 25<br>25                                | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V | 1     |

|                                       | 45(default)<br>45(default)              | BV <sub>DD</sub> = 3.3 V<br>BV <sub>DD</sub> = 2.5 V |       |

| PCI signals                           | 25                                      | OV <sub>DD</sub> = 3.3 V                             | 2     |

|                                       | 45(default)                             |                                                      |       |

| DDR signal                            | 18<br>36 (half strength mode)           | GV <sub>DD</sub> = 2.5 V                             | 3     |

| DDR2 signal                           | 18<br>36 (half strength mode)           | GV <sub>DD</sub> = 1.8 V                             | 3     |

| TSEC/10/100 signals                   | 45                                      | L/TV <sub>DD</sub> = 2.5/3.3 V                       | —     |

| DUART, system control, JTAG           | 45                                      | OV <sub>DD</sub> = 3.3 V                             | —     |

| 12C                                   | 150                                     | OV <sub>DD</sub> = 3.3 V                             |       |

Table 3. Output Drive Capability

Notes:

1. The drive strength of the local bus interface is determined by the configuration of the appropriate bits in PORIMPSCR.

2. The drive strength of the PCI interface is determined by the setting of the PCI\_GNT1 signal at reset.

3. The drive strength of the DDR interface in half-strength mode is at  $T_i = 105^{\circ}C$  and at  $GV_{DD}$  (min).

# 2.2 Power Sequencing

The device requires its power rails to be applied in a specific sequence in order to ensure proper device operation. These requirements are as follows for power-up:

- 1. V<sub>DD</sub>, AV<sub>DD</sub>, BV<sub>DD</sub>, LV<sub>DD</sub>, OV<sub>DD</sub>, SV<sub>DD</sub>, TV<sub>DD</sub>, XV<sub>DD</sub>

- 2.  $GV_{DD}$

All supplies must be at their stable values within 50 ms.

### NOTE

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90% of their value before the voltage rails on the current step reach 10% of theirs.

## NOTE

In order to guarantee MCKE low during power-up, the above sequencing for  $GV_{DD}$  is required. If there is no concern about any of the DDR signals being in an indeterminate state during power-up, then the sequencing for  $GV_{DD}$  is not required.

### NOTE

From a system standpoint, if any of the I/O power supplies ramp prior to the  $V_{DD}$  core supply, the I/Os associated with that I/O supply may drive a logic one or zero during power-up, and extra current may be drawn by the device.

# 4 Input Clocks

This section discusses the timing for the input clocks.

# 4.1 System Clock Timing

The following table provides the system clock (SYSCLK) AC timing specifications for the device.

### Table 5. SYSCLK AC Timing Specifications

At recommended operating conditions (see Table 2) with  $OV_{DD} = 3.3 \text{ V} \pm 165 \text{ mV}$ .

| Parameter/Condition       | Symbol                            | Min | Тур | Мах  | Unit | Notes      |

|---------------------------|-----------------------------------|-----|-----|------|------|------------|

| SYSCLK frequency          | f <sub>SYSCLK</sub>               | 16  | —   | 133  | MHz  | 1, 6, 7, 8 |

| SYSCLK cycle time         | t <sub>SYSCLK</sub>               | 7.5 | —   | 60   | ns   | 6, 7, 8    |

| SYSCLK rise and fall time | t <sub>KH</sub> , t <sub>KL</sub> | 0.6 | 1.0 | 1.2  | ns   | 2          |

| SYSCLK duty cycle         | t <sub>KHK</sub> ∕tsysclk         | 40  | —   | 60   | %    | 3          |

| SYSCLK jitter             | _                                 | _   | —   | ±150 | ps   | 4, 5       |

Notes:

- Caution: The CCB clock to SYSCLK ratio and e500 core to CCB clock ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB clock frequency do not exceed their respective maximum or minimum operating frequencies. See Section 20.2, "CCB/SYSCLK PLL Ratio," and Section 20.3, "e500 Core PLL Ratio," for ratio settings.

- 2. Rise and fall times for SYSCLK are measured at 0.6 and 2.7 V.

- 3. Timing is guaranteed by design and characterization.

- 4. This represents the total input jitter—short term and long term—and is guaranteed by design.

- 5. The SYSCLK driver's closed loop jitter bandwidth must be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track SYSCLK drivers with the specified jitter.

- 6. This parameter has been adjusted slower according to the workaround for device erratum GEN 13.

- 7. For spread spectrum clocking. Guidelines are + 0% to -1% down spread at modulation rate between 20 and 60 kHz on SYSCLK.

- 8. System with operating core frequency less than 1200 MHz must limit SYSCLK frequency to 100 MHz maximum.

# 4.2 Real Time Clock Timing

The RTC input is sampled by the platform clock (CCB clock). The output of the sampling latch is then used as an input to the counters of the PIC and the TimeBase unit of the e500. There is no jitter specification. The minimum pulse width of the RTC signal must be greater than 2x the period of the CCB clock. That is, minimum clock high time is  $2 \times t_{CCB}$ , and minimum clock low time is  $2 \times t_{CCB}$ . There is no minimum RTC frequency; RTC may be grounded if not needed.

# 4.5 Platform to FIFO Restrictions

Note the following FIFO maximum speed restrictions based on platform speed.

For FIFO GMII mode:

FIFO TX/RX clock frequency ≤ platform clock frequency/4.2

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency must be no more than 127 MHz.

For FIFO encoded mode:

FIFO TX/RX clock frequency  $\leq$  platform clock frequency/4.2

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency must be no more than 167 MHz.

# 4.6 Platform Frequency Requirements for PCI-Express and Serial RapidIO

The CCB clock frequency must be considered for proper operation of the high-speed PCI-Express and Serial RapidIO interfaces as described below.

For proper PCI Express operation, the CCB clock frequency must be greater than:

See *MPC8548ERM*, *Rev.* 2, *PowerQUICC III Integrated Processor Family Reference Manual*, Section 18.1.3.2, "Link Width," for PCI Express interface width details.

For proper serial RapidIO operation, the CCB clock frequency must be greater than:

$2 \times (0.80) \times (Serial RapidIO interface frequency) \times (Serial RapidIO link width)$

64

See *MPC8548ERM*, *Rev.* 2, *PowerQUICC III Integrated Processor Family Reference Manual*, Section 17.4, "1x/4x LP-Serial Signal Descriptions," for serial RapidIO interface width and frequency details.

# 4.7 Other Input Clocks

For information on the input clocks of other functional blocks of the platform see the specific section of this document.

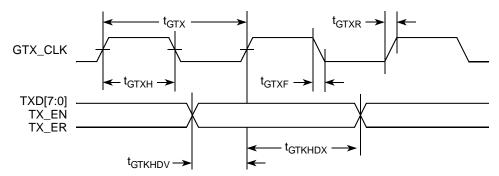

Figure 8 shows the GMII transmit AC timing diagram.

Figure 8. GMII Transmit AC Timing Diagram

## 8.2.2.2 GMII Receive AC Timing Specifications

This table provides the GMII receive AC timing specifications.

| Table 27. GMII Receive AC | Timing Specifications |

|---------------------------|-----------------------|

|---------------------------|-----------------------|

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|---------------------------------------------|-------------------------------------|-----|-----|-----|------|

| RX_CLK clock period                         | t <sub>GRX</sub>                    | —   | 8.0 | —   | ns   |

| RX_CLK duty cycle                           | t <sub>GRXH</sub> /t <sub>GRX</sub> | 35  | _   | 75  | ns   |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>GRDVKH</sub>                 | 2.0 | _   | —   | ns   |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>GRDXKH</sub>                 | 0   | _   | —   | ns   |

| RX_CLK clock rise (20%-80%)                 | t <sub>GRXR</sub> 2                 | —   | _   | 1.0 | ns   |

| RX_CLK clock fall time (80%-20%)            | t <sub>GRXF</sub> 2                 |     |     | 1.0 | ns   |

#### Notes:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>GRDVKH</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GRX</sub> represents the GMII (G) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

2. Guaranteed by design.

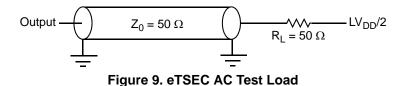

Figure 9 provides the AC test load for eTSEC.

# 9 Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals MDIO (management data input/output) and MDC (management data clock). The electrical characteristics for GMII, RGMII, RMII, TBI, and RTBI are specified in "Section 8, "Enhanced Three-Speed Ethernet (eTSEC)."

# 9.1 MII Management DC Electrical Characteristics

The MDC and MDIO are defined to operate at a supply voltage of 3.3 V. The DC electrical characteristics for MDIO and MDC are provided in this table.

| Parameter                                                            | Symbol           | Min  | Мах                    | Unit |

|----------------------------------------------------------------------|------------------|------|------------------------|------|

| Supply voltage (3.3 V)                                               | OV <sub>DD</sub> | 3.13 | 3.47                   | V    |

| Output high voltage ( $OV_{DD} = Min, I_{OH} = -1.0 mA$ )            | V <sub>OH</sub>  | 2.10 | OV <sub>DD</sub> + 0.3 | V    |

| Output low voltage (OV <sub>DD</sub> =Min, I <sub>OL</sub> = 1.0 mA) | V <sub>OL</sub>  | GND  | 0.50                   | V    |

| Input high voltage                                                   | V <sub>IH</sub>  | 2.0  | —                      | V    |

| Input low voltage                                                    | V <sub>IL</sub>  | _    | 0.90                   | V    |

| Input high current ( $OV_{DD} = Max, V_{IN}^1 = 2.1 V$ )             | I <sub>IH</sub>  | _    | 40                     | μA   |

| Input low current ( $OV_{DD} = Max$ , $V_{IN} = 0.5 V$ )             | IIL              | -600 | —                      | μΑ   |

Table 36. MII Management DC Electrical Characteristics

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

# 9.2 MII Management AC Electrical Specifications

This table provides the MII management AC timing specifications.

### Table 37. MII Management AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  is 3.3 V ± 5%.

| Parameter                  | Symbol <sup>1</sup> | Min                             | Тур | Мах                                | Unit | Notes   |

|----------------------------|---------------------|---------------------------------|-----|------------------------------------|------|---------|

| MDC frequency              | f <sub>MDC</sub>    | 0.72                            | 2.5 | 8.3                                | MHz  | 2, 3, 4 |

| MDC period                 | t <sub>MDC</sub>    | 120.5                           | _   | 1389                               | ns   | —       |

| MDC clock pulse width high | t <sub>MDCH</sub>   | 32                              | _   | —                                  | ns   | _       |

| MDC to MDIO valid          | t <sub>MDKHDV</sub> | $16 \times t_{CCB}$             | _   | —                                  | ns   | 5       |

| MDC to MDIO delay          | t <sub>MDKHDX</sub> | (16 × t <sub>CCB</sub> × 8) – 3 | _   | $(16 \times t_{CCB} \times 8) + 3$ | ns   | 5       |

| MDIO to MDC setup time     | t <sub>MDD∨KH</sub> | 5                               | _   | —                                  | ns   | _       |

| MDIO to MDC hold time      | t <sub>MDDXKH</sub> | 0                               | _   | —                                  | ns   | —       |

| MDC rise time              | t <sub>MDCR</sub>   | _                               |     | 10                                 | ns   | 4       |

| Parameter                                                             | Symbol <sup>1</sup>                 | Min | Max | Unit | Notes |

|-----------------------------------------------------------------------|-------------------------------------|-----|-----|------|-------|

| Local bus cycle time                                                  | t <sub>LBK</sub>                    | 7.5 | 12  | ns   | 2     |

| Local bus duty cycle                                                  | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43  | 57  | %    | —     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                  | t <sub>LBKSKEW</sub>                | —   | 150 | ps   | 7, 8  |

| Input setup to local bus clock (except LGTA/UPWAIT)                   | t <sub>LBIVKH1</sub>                | 1.9 | —   | ns   | 3, 4  |

| LGTA/LUPWAIT input setup to local bus clock                           | t <sub>LBIVKH2</sub>                | 1.8 | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LGTA/LUPWAIT)                 | t <sub>LBIXKH1</sub>                | 1.1 | —   | ns   | 3, 4  |

| LGTA/LUPWAIT input hold from local bus clock                          | t <sub>LBIXKH2</sub>                | 1.1 | —   | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) | t <sub>LBOTOT</sub>                 | 1.5 | —   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)             | t <sub>LBKHOV1</sub>                | —   | 2.1 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                             | t <sub>LBKHOV2</sub>                | —   | 2.3 | ns   | 3     |

| Local bus clock to address valid for LAD                              | t <sub>LBKHOV3</sub>                | —   | 2.4 | ns   | 3     |

| Local bus clock to LALE assertion                                     | t <sub>LBKHOV4</sub>                | —   | 2.4 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)            | t <sub>LBKHOX1</sub>                | 0.8 | —   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                          | t <sub>LBKHOX2</sub>                | 0.8 | —   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)    | t <sub>LBKHOZ1</sub>                | —   | 2.6 | ns   | 5     |

| Local bus clock to output high impedance for LAD/LDP                  | t <sub>LBKHOZ2</sub>                | _   | 2.6 | ns   | 5     |

Table 41 describes the timing parameters of the local bus interface at  $BV_{DD} = 2.5$  V.

### Table 41. Local Bus Timing Parameters (BV<sub>DD</sub> = 2.5 V)—PLL Enabled

#### Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKH0X</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub></sub>

- 2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 3.3-V signaling levels.

- 4. Input timings are measured at the pin.

5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 8. Guaranteed by design.

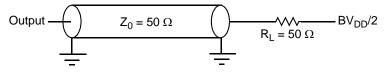

Figure 22 provides the AC test load for the local bus.

Figure 22. Local Bus AC Test Load

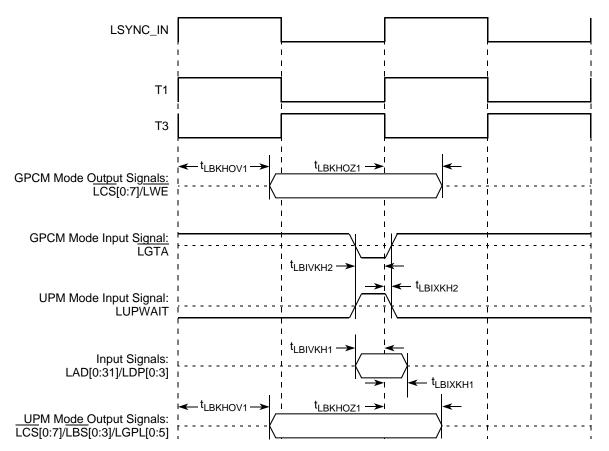

Figure 25. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 (PLL Enabled)

#### Local Bus

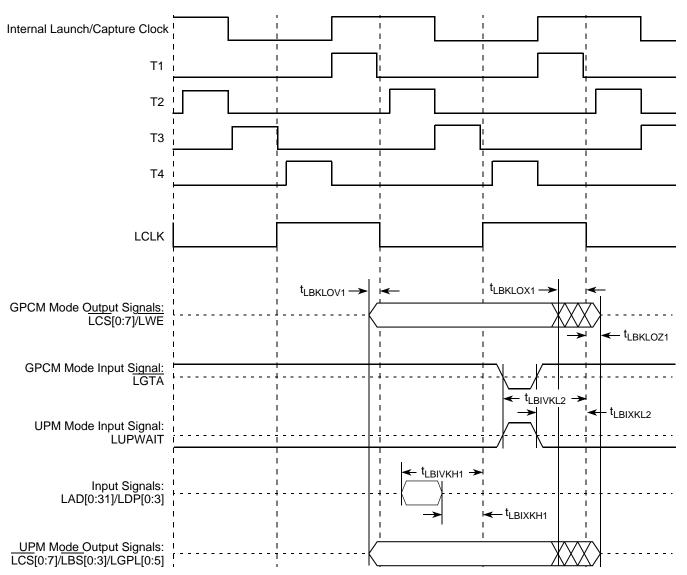

Figure 28. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 8 or 16 (PLL Bypass Mode)

#### High-Speed Serial Interfaces (HSSI)

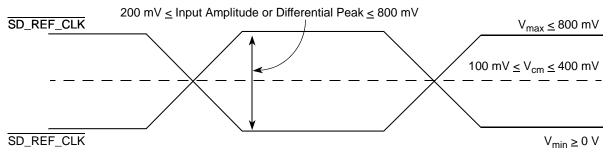

- The input amplitude of the differential clock must be between 400 and 1600 mV differential peak-peak (or between 200 and 800 mV differential peak). In other words, each signal wire of the differential pair must have a single-ended swing less than 800 mV and greater than 200 mV. This requirement is the same for both external DC- or AC-coupled connection.

- For external DC-coupled connection, as described in Section 16.2.1, "SerDes Reference Clock Receiver Characteristics," the maximum average current requirements sets the requirement for average voltage (common mode voltage) to be between 100 and 400 mV. Figure 40 shows the SerDes reference clock input requirement for DC-coupled connection scheme.

- For external AC-coupled connection, there is no common mode voltage requirement for the clock driver. Since the external AC-coupling capacitor blocks the DC level, the clock driver and the SerDes reference clock receiver operate in different command mode voltages. The SerDes reference clock receiver in this connection scheme has its common mode voltage set to SGND\_SRDSn. Each signal wire of the differential inputs is allowed to swing below and above the command mode voltage (SGND\_SRDSn). Figure 41 shows the SerDes reference clock input requirement for AC-coupled connection scheme.

- Single-ended mode

- The reference clock can also be single-ended. The SD\_REF\_CLK input amplitude (single-ended swing) must be between 400 and 800 mV peak-to-peak (from  $V_{min}$  to  $V_{max}$ ) with SD\_REF\_CLK either left unconnected or tied to ground.

- The SD\_REF\_CLK input average voltage must be between 200 and 400 mV. Figure 42 shows the SerDes reference clock input requirement for single-ended signaling mode.

- To meet the input amplitude requirement, the reference clock inputs might need to be DC- or AC-coupled externally. For the best noise performance, the reference of the clock could be DCor AC-coupled into the unused phase (SD\_REF\_CLK) through the same source impedance as the clock input (SD\_REF\_CLK) in use.

Figure 40. Differential Reference Clock Input DC Requirements (External DC-Coupled)

#### High-Speed Serial Interfaces (HSSI)

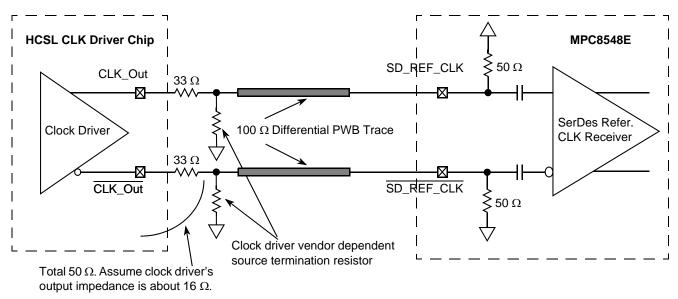

Figure 43 shows the SerDes reference clock connection reference circuits for HCSL type clock driver. It assumes that the DC levels of the clock driver chip is compatible with SerDes reference clock input's DC requirement.

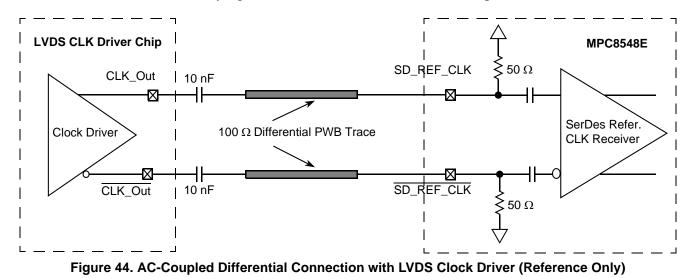

Figure 44 shows the SerDes reference clock connection reference circuits for LVDS type clock driver. Since LVDS clock driver's common mode voltage is higher than the SerDes reference clock input's allowed range (100–400 mV), AC-coupled connection scheme must be used. It assumes the LVDS output driver features 50- $\Omega$  termination resistor. It also assumes that the LVDS transmitter establishes its own common mode level without relying on the receiver or other external component.

Figure 45 shows the SerDes reference clock connection reference circuits for LVPECL type clock driver. Since LVPECL driver's DC levels (both common mode voltages and output swing) are incompatible with the SerDes reference clock input's DC requirement, AC-coupling must be used. Figure 45 assumes that the LVPECL clock driver's output impedance is 50  $\Omega$ . R1 is used to DC-bias the LVPECL outputs prior

#### PCI Express

The eye diagram must be valid for any 250 consecutive UIs.

A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. The eye diagram is created using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI.

### NOTE

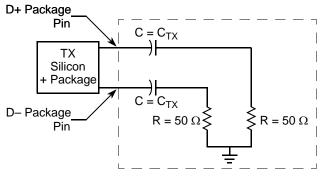

The reference impedance for return loss measurements is 50. to ground for both the D+ and D– line (that is, as measured by a vector network analyzer with 50- $\Omega$  probes—see Figure 50). Note that the series capacitors, CTX, are optional for the return loss measurement.

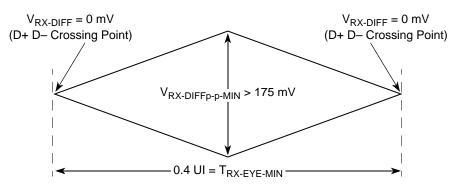

Figure 49. Minimum Receiver Eye Timing and Voltage Compliance Specification

# 17.5.1 Compliance Test and Measurement Load

The AC timing and voltage parameters must be verified at the measurement point, as specified within 0.2 inches of the package pins, into a test/measurement load shown in Figure 50.

### NOTE

The allowance of the measurement point to be within 0.2 inches of the package pins is meant to acknowledge that package/board routing may benefit from D+ and D- not being exactly matched in length at the package pin boundary.

Figure 50. Compliance Test/Measurement Load

### Serial RapidIO

802.3ae-2002 is specified as the test pattern for use in eye pattern and jitter measurements. Annex 48B of IEEE Std. 802.3ae-2002 is recommended as a reference for additional information on jitter test methods.

# 18.9.1 Eye Template Measurements

For the purpose of eye template measurements, the effects of a single-pole high pass filter with a 3 dB point at (baud frequency)/1667 is applied to the jitter. The data pattern for template measurements is the continuous jitter test pattern (CJPAT) defined in Annex 48A of IEEE 802.3ae. All lanes of the LP-serial link shall be active in both the transmit and receive directions, and opposite ends of the links shall use asynchronous clocks. Four lane implementations shall use CJPAT as defined in Annex 48A. Single lane implementations shall use the CJPAT sequence specified in Annex 48A for transmission on lane 0. The amount of data represented in the eye shall be adequate to ensure that the bit error ratio is less than  $10^{-12}$ . The eye pattern shall be measured with AC coupling and the compliance template centered at 0 V differential. The left and right edges of the template shall be aligned with the mean zero crossing points of the measured data eye. The load for this test shall be  $100-\Omega$  resistive  $\pm 5\%$  differential to 2.5 GHz.

# 18.9.2 Jitter Test Measurements

For the purpose of jitter measurement, the effects of a single-pole high pass filter with a 3 dB point at (baud frequency)/1667 is applied to the jitter. The data pattern for jitter measurements is the Continuous Jitter test pattern (CJPAT) pattern defined in Annex 48A of IEEE 802.3ae. All lanes of the LP-serial link shall be active in both the transmit and receive directions, and opposite ends of the links shall use asynchronous clocks. Four lane implementations shall use CJPAT as defined in Annex 48A. Single lane implementations shall use the CJPAT sequence specified in Annex 48A for transmission on lane 0. Jitter shall be measured with AC coupling and at 0 V differential. Jitter measurement for the transmitter (or for calibration of a jitter tolerance setup) shall be performed with a test procedure resulting in a BER curve such as that described in Annex 48B of IEEE 802.3ae.

# 18.9.3 Transmit Jitter

Transmit jitter is measured at the driver output when terminated into a load of 100  $\Omega$  resistive ± 5% differential to 2.5 GHz.

# 18.9.4 Jitter Tolerance

Jitter tolerance is measured at the receiver using a jitter tolerance test signal. This signal is obtained by first producing the sum of deterministic and random jitter defined in Section 18.7, "Receiver Specifications," and then adjusting the signal amplitude until the data eye contacts the 6 points of the minimum eye opening of the receive template shown in Figure 54 and Table 69. Note that for this to occur, the test signal must have vertical waveform symmetry about the average value and have horizontal symmetry (including jitter) about the mean zero crossing. Eye template measurement requirements are as defined above. Random jitter is calibrated using a high pass filter with a low frequency corner at 20 MHz and a 20 dB/decade roll-off below this. The required sinusoidal jitter specified in Section 18.7, "Receiver Specifications," is then added to the signal and the test load is replaced by the receiver being tested.

**Package Description**

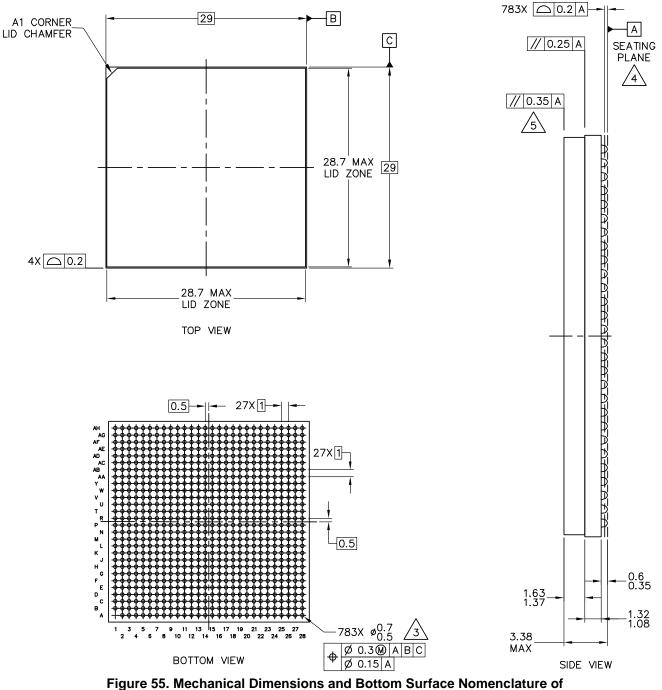

# 19.2 Mechanical Dimensions of the HiCTE FC-CBGA and FC-PBGA with Full Lid

The following figures show the mechanical dimensions and bottom surface nomenclature for the MPC8548E HiCTE FC-CBGA and FC-PBGA packages.

the HiCTE FC-CBGA and FC-PBGA with Full Lid

| Signal                        | Package Pin Number                       | Pin Type | Power<br>Supply  | Notes          |

|-------------------------------|------------------------------------------|----------|------------------|----------------|

| Three                         | -Speed Ethernet Controller (Gigabit Ethe | ernet 2) |                  |                |

| TSEC2_RXD[7:0]                | P2, R2, N1, N2, P3, M2, M1, N3           | I        | LV <sub>DD</sub> | _              |

| TSEC2_TXD[7:0]                | N9, N10, P8, N7, R9, N5, R8, N6          | 0        | LV <sub>DD</sub> | 5, 9, 33       |

| TSEC2_COL                     | P1                                       | I        | LV <sub>DD</sub> |                |

| TSEC2_CRS                     | R6                                       | I/O      | LV <sub>DD</sub> | 20             |

| TSEC2_GTX_CLK                 | P6                                       | 0        | LV <sub>DD</sub> |                |

| TSEC2_RX_CLK                  | N4                                       | I        | LV <sub>DD</sub> | —              |

| TSEC2_RX_DV                   | P5                                       | I        | LV <sub>DD</sub> | —              |

| TSEC2_RX_ER                   | R1                                       | I        | LV <sub>DD</sub> | —              |

| TSEC2_TX_CLK                  | P10                                      | I        | LV <sub>DD</sub> | —              |

| TSEC2_TX_EN                   | P7                                       | 0        | LV <sub>DD</sub> | 30             |

| TSEC2_TX_ER                   | R10                                      | 0        | LV <sub>DD</sub> | 5, 9, 33       |

| Three                         | -Speed Ethernet Controller (Gigabit Ethe | ernet 3) |                  |                |

| TSEC3_TXD[3:0]                | V8, W10, Y10, W7                         | 0        | TV <sub>DD</sub> | 5, 9, 29       |

| TSEC3_RXD[3:0]                | Y1, W3, W5, W4                           | I        | TV <sub>DD</sub> | —              |

| TSEC3_GTX_CLK                 | W8                                       | 0        | TV <sub>DD</sub> | —              |

| TSEC3_RX_CLK                  | W2                                       | I        | TV <sub>DD</sub> | —              |

| TSEC3_RX_DV                   | W1                                       | I        | TV <sub>DD</sub> | —              |

| TSEC3_RX_ER                   | Y2                                       | I        | TV <sub>DD</sub> | —              |

| TSEC3_TX_CLK                  | V10                                      | I        | TV <sub>DD</sub> | —              |

| TSEC3_TX_EN                   | V9                                       | 0        | TV <sub>DD</sub> | 30             |

| Three                         | -Speed Ethernet Controller (Gigabit Ethe | ernet 4) |                  |                |

| TSEC4_TXD[3:0]/TSEC3_TXD[7:4] | AB8, Y7, AA7, Y8                         | 0        | TV <sub>DD</sub> | 1, 5, 9,<br>29 |

| TSEC4_RXD[3:0]/TSEC3_RXD[7:4] | AA1, Y3, AA2, AA4                        | I        | TV <sub>DD</sub> | 1              |

| TSEC4_GTX_CLK                 | AA5                                      | 0        | TV <sub>DD</sub> | —              |

| TSEC4_RX_CLK/TSEC3_COL        | Y5                                       | I        | TV <sub>DD</sub> | 1              |

| TSEC4_RX_DV/TSEC3_CRS         | AA3                                      | I/O      | TV <sub>DD</sub> | 1, 31          |

| TSEC4_TX_EN/TSEC3_TX_ER       | AB6                                      | 0        | TV <sub>DD</sub> | 1, 30          |

|                               | DUART                                    |          |                  |                |

| UART_CTS[0:1]                 | AB3, AC5                                 | I        | OV <sub>DD</sub> | —              |

| UART_RTS[0:1]                 | AC6, AD7                                 | 0        | OV <sub>DD</sub> | —              |

| UART_SIN[0:1]                 | AB5, AC7                                 | I        | OV <sub>DD</sub> | -              |

| UART_SOUT[0:1]                | AB7, AD8                                 | 0        | OV <sub>DD</sub> | 1 —            |

### Table 71. MPC8548E Pinout Listing (continued)

| Signal        | Package Pin Number | Pin Type | Power<br>Supply | Notes |

|---------------|--------------------|----------|-----------------|-------|

| SD_IMP_CAL_RX | L28                | I        | 200 Ω to<br>GND | —     |

| SD_IMP_CAL_TX | AB26               | I        | 100 Ω to<br>GND | —     |

| SD_PLL_TPA    | U26                | 0        | —               | 24    |

### Table 73. MPC8545E Pinout Listing (continued)

Note: All note references in this table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

Table 74 provides the pin-out listing for the MPC8543E 783 FC-PBGA package.

### NOTE

All note references in the following table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

Table 74. MPC8543E Pinout Listing

| Signal         | Package Pin Number                                                                                                                                                                            | Pin Type | Power<br>Supply  | Notes    |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|--|--|--|

|                | PCI1 (One 32-Bit)                                                                                                                                                                             |          |                  |          |  |  |  |

| Reserved       | AB14, AC15, AA15, Y16, W16, AB16, AC16,<br>AA16, AE17, AA18, W18, AC17, AD16, AE16,<br>Y17, AC18,                                                                                             |          | _                | 110      |  |  |  |

| GPOUT[8:15]    | AB18, AA19, AB19, AB21, AA20, AC20, AB20,<br>AB22                                                                                                                                             | 0        | OV <sub>DD</sub> | —        |  |  |  |

| GPIN[8:15]     | AC22, AD21, AB23, AF23, AD23, AE23, AC23, AC24                                                                                                                                                | I        | OV <sub>DD</sub> | 111      |  |  |  |

| PCI1_AD[31:0]  | AH6, AE7, AF7, AG7, AH7, AF8, AH8, AE9,<br>AH9, AC10, AB10, AD10, AG10, AA10, AH10,<br>AA11, AB12, AE12, AG12, AH12, AB13, AA12,<br>AC13, AE13, Y14, W13, AG13, V14, AH13,<br>AC14, Y15, AB15 | I/O      | OV <sub>DD</sub> | 17       |  |  |  |

| Reserved       | AF15, AD14, AE15, AD15                                                                                                                                                                        | _        | -                | 110      |  |  |  |

| PCI1_C_BE[3:0] | AF9, AD11, Y12, Y13                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 17       |  |  |  |

| Reserved       | W15                                                                                                                                                                                           |          |                  | 110      |  |  |  |

| PCI1_GNT[4:1]  | AG6, AE6, AF5, AH5                                                                                                                                                                            | 0        | OV <sub>DD</sub> | 5, 9, 35 |  |  |  |

| PCI1_GNT0      | AG5                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | —        |  |  |  |

| PCI1_IRDY      | AF11                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| PCI1_PAR       | AD12                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | —        |  |  |  |

| PCI1_PERR      | AC12                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| PCI1_SERR      | V13                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2, 4     |  |  |  |

| PCI1_STOP      | W12                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| Signal           | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin Type                                              | Power<br>Supply  | Notes     |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------|-----------|

|                  | JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11                                                    |                  |           |

| ТСК              | AG28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | —         |

| TDI              | AH28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 12        |

| TDO              | AF28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                     | $OV_{DD}$        | —         |

| TMS              | AH27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 12        |

| TRST             | AH23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 12        |

|                  | DFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                       |                  |           |

| L1_TSTCLK        | AC25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 25        |

| L2_TSTCLK        | AE22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 25        |

| LSSD_MODE        | AH20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 25        |

| TEST_SEL         | AH14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 109       |

|                  | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |                  |           |

| THERM0           | AG1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                     | _                | 14        |

| THERM1           | AH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                     | _                | 14        |

|                  | Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                       |                  |           |

| ASLEEP           | AH18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                     | $OV_{DD}$        | 9, 19, 29 |

|                  | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                       |                  |           |

| GND              | <ul> <li>A11, B7, B24, C1, C3, C5, C12, C15, C26, D8,<br/>D11, D16, D20, D22, E1, E5, E9, E12, E15, E17,<br/>F4, F26, G12, G15, G18, G21, G24, H2, H6, H8,<br/>H28, J4, J12, J15, J17, J27, K7, K9, K11, K27,<br/>L3, L5, L12, L16, N11, N13, N15, N17, N19, P4,<br/>P9, P12, P14, P16, P18, R11, R13, R15, R17,<br/>R19, T4, T12, T14, T16, T18, U8, U11, U13,<br/>U15, U17, U19, V4, V12, V18, W6, W19, Y4, Y9,<br/>Y11, Y19, AA6, AA14, AA17, AA22, AA23, AB4,<br/>AC2, AC11, AC19, AC26, AD5, AD9, AD22,<br/>AE3, AE14, AF6, AF10, AF13, AG8, AG27,<br/>K28, L24, L26, N24, N27, P25, R28, T24, T26,<br/>U24, V25, W28, Y24, Y26, AA24, AA27, AB25,<br/>AC28, L21, L23, N22, P20, R23, T21, U22, V20,<br/>W23, Y21, U27</li> </ul> | _                                                     |                  | _         |

| OV <sub>DD</sub> | V16, W11, W14, Y18, AA13, AA21, AB11,<br>AB17, AB24, AC4, AC9, AC21, AD6, AD13,<br>AD17, AD19, AE10, AE8, AE24, AF4, AF12,<br>AF22, AF27, AG26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Power for<br>PCI and<br>other<br>standards<br>(3.3 V) | OV <sub>DD</sub> | _         |

| LV <sub>DD</sub> | N8, R7, T9, U6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Power for<br>TSEC1 and<br>TSEC2<br>(2.5 V, 3.3 V)     | LV <sub>DD</sub> | _         |

Package Description

| Signal           | Package Pin Number                                                                                                                                                | Pin Type                                                              | Power<br>Supply  | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------|-------|

| TV <sub>DD</sub> | W9, Y6                                                                                                                                                            | Power for<br>TSEC3 and<br>TSEC4<br>(2,5 V, 3.3 V)                     | TV <sub>DD</sub> | _     |

| GV <sub>DD</sub> | B3, B11, C7, C9, C14, C17, D4, D6, D10, D15,<br>E2, E8, E11, E18, F5, F12, F16, G3, G7, G9,<br>G11, H5, H12, H15, H17, J10, K3, K12, K16,<br>K18, L6, M4, M8, M13 | Power for<br>DDR1 and<br>DDR2<br>DRAM I/O<br>voltage<br>(1.8 V,2.5 V) | GV <sub>DD</sub> | _     |

| BV <sub>DD</sub> | C21, C24, C27, E20, E25, G19, G23, H26, J20                                                                                                                       | Power for<br>local bus<br>(1.8 V, 2.5 V,<br>3.3 V)                    | BV <sub>DD</sub> | _     |

| V <sub>DD</sub>  | M19, N12, N14, N16, N18, P11, P13, P15, P17,<br>P19, R12, R14, R16, R18, T11, T13, T15, T17,<br>T19, U12, U14, U16, U18, V17, V19                                 | Power for core (1.1 V)                                                | V <sub>DD</sub>  | _     |

| SV <sub>DD</sub> | L25, L27, M24, N28, P24, P26, R24, R27, T25,<br>V24, V26, W24, W27, Y25, AA28, AC27                                                                               | Core power<br>for SerDes<br>transceivers<br>(1.1 V)                   | SV <sub>DD</sub> | _     |

| XV <sub>DD</sub> | L20, L22, N23, P21, R22, T20, U23, V21, W22,<br>Y20                                                                                                               | Pad power<br>for SerDes<br>transceivers<br>(1.1 V)                    | XV <sub>DD</sub> | _     |

| AVDD_LBIU        | J28                                                                                                                                                               | Power for<br>local bus<br>PLL<br>(1.1 V)                              | _                | 26    |

| AVDD_PCI1        | AH21                                                                                                                                                              | Power for<br>PCI1 PLL<br>(1.1 V)                                      | _                | 26    |

| AVDD_PCI2        | AH22                                                                                                                                                              | Power for<br>PCI2 PLL<br>(1.1 V)                                      | _                | 26    |

| AVDD_CORE        | AH15                                                                                                                                                              | Power for<br>e500 PLL<br>(1.1 V)                                      |                  | 26    |

| AVDD_PLAT        | AH19                                                                                                                                                              | Power for<br>CCB PLL<br>(1.1 V)                                       | _                | 26    |

| AVDD_SRDS        | U25                                                                                                                                                               | Power for<br>SRDSPLL<br>(1.1 V)                                       | _                | 26    |

| SENSEVDD         | M14                                                                                                                                                               | 0                                                                     | V <sub>DD</sub>  | 13    |

### Table 74. MPC8543E Pinout Listing (continued)

#### System Design Information

The platform PLL ratio and e500 PLL ratio configuration pins are not equipped with these default pull-up devices.

# 22.9 JTAG Configuration Signals

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 63. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions as most have asynchronous behavior and spurious assertion gives unpredictable results.

Boundary-scan testing is enabled through the JTAG interface signals. The TRST signal is optional in the IEEE 1149.1 specification, but it is provided on all processors built on Power Architecture technology. The device requires TRST to be asserted during power-on reset flow to ensure that the JTAG boundary logic does not interfere with normal chip operation. While the TAP controller can be forced to the reset state using only the TCK and TMS signals, generally systems assert TRST during the power-on reset flow. Simply tying TRST to HRESET is not practical because the JTAG interface is also used for accessing the common on-chip processor (COP), which implements the debug interface to the chip.

The COP function of these processors allow a remote computer system (typically, a PC with dedicated hardware and debugging software) to access and control the internal operations of the processor. The COP interface connects primarily through the JTAG port of the processor, with some additional status monitoring signals. The COP port requires the ability to independently assert HRESET or TRST in order to fully control the processor. If the target system has independent reset sources, such as voltage monitors, watchdog timers, power supply failures, or push-button switches, then the COP reset signals must be merged into these signals with logic.

The arrangement shown in Figure 63 allows the COP port to independently assert  $\overline{\text{HRESET}}$  or  $\overline{\text{TRST}}$ , while ensuring that the target can drive  $\overline{\text{HRESET}}$  as well.

The COP interface has a standard header, shown in Figure 62, for connection to the target system, and is based on the 0.025" square-post, 0.100" centered header assembly (often called a Berg header). The connector typically has pin 14 removed as a connector key.

The COP header adds many benefits such as breakpoints, watchpoints, register and memory examination/modification, and other standard debugger features. An inexpensive option can be to leave the COP header unpopulated until needed.

There is no standardized way to number the COP header; so emulator vendors have issued many different pin numbering schemes. Some COP headers are numbered top-to-bottom then left-to-right, while others use left-to-right then top-to-bottom. Still others number the pins counter-clockwise from pin 1 (as with an IC). Regardless of the numbering scheme, the signal placement recommended in Figure 62 is common to all known emulators.

# 22.9.1 Termination of Unused Signals

Freescale recommends the following connections, when the JTAG interface and COP header are not used:

• TRST must be tied to HRESET through a 0 k $\Omega$  isolation resistor so that it is asserted when the system reset signal (HRESET) is asserted, ensuring that the JTAG scan chain is initialized during the power-on reset flow. Freescale recommends that the COP header be designed into the system