Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

## **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                             |

|---------------------------------|-------------------------------------------------------------|

| Product Status                  | Obsolete                                                    |

| Core Processor                  | PowerPC e500                                                |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 1.0GHz                                                      |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                       |

| RAM Controllers                 | DDR, DDR2, SDRAM                                            |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | -                                                           |

| Ethernet                        | 10/100/1000Mbps (4)                                         |

| SATA                            | -                                                           |

| USB                             | -                                                           |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                            |

| Operating Temperature           | 0°C ~ 105°C (TA)                                            |

| Security Features               | Cryptography, Random Number Generator                       |

| Package / Case                  | 783-BBGA, FCBGA                                             |

| Supplier Device Package         | 783-FCBGA (29x29)                                           |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8548epxaqgb |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Single inbound doorbell message structure

- Facility to accept port-write messages

- PCI Express interface

- PCI Express 1.0a compatible

- Supports x8,x4,x2, and x1 link widths

- Auto-detection of number of connected lanes

- Selectable operation as root complex or endpoint

- Both 32- and 64-bit addressing

- 256-byte maximum payload size

- Virtual channel 0 only

- Traffic class 0 only

- Full 64-bit decode with 32-bit wide windows

- Pin multiplexing for the high-speed I/O interfaces supports one of the following configurations:

- 8 PCI Express

- 4 PCI Express and 4 serial RapidIO

- Power management

- Supports power saving modes: doze, nap, and sleep

- Employs dynamic power management, which automatically minimizes power consumption of blocks when they are idle

- System performance monitor

- Supports eight 32-bit counters that count the occurrence of selected events

- Ability to count up to 512 counter-specific events

- Supports 64 reference events that can be counted on any of the eight counters

- Supports duration and quantity threshold counting

- Burstiness feature that permits counting of burst events with a programmable time between bursts

- Triggering and chaining capability

- Ability to generate an interrupt on overflow

- System access port

- Uses JTAG interface and a TAP controller to access entire system memory map

- Supports 32-bit accesses to configuration registers

- Supports cache-line burst accesses to main memory

- Supports large block (4-Kbyte) uploads and downloads

- Supports continuous bit streaming of entire block for fast upload and download

- JTAG boundary scan, designed to comply with IEEE Std. 1149.1<sup>TM</sup>

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

Table 1. Absolute Maximum Ratings <sup>1</sup> (continued)

| Characteristic            | Symbol           | Max Value  | Unit | Notes |

|---------------------------|------------------|------------|------|-------|

| Storage temperature range | T <sub>STG</sub> | -55 to 150 | °C   | _     |

- 1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- 2. The -0.3 to 2.75 V range is for DDR and -0.3 to 1.98 V range is for DDR2.

- 3. The 3.63 V maximum is only supported when the port is configured in GMII, MII, RMII, or TBI modes; otherwise the 2.75 V maximum applies. See Section 8.2, "FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications," for details on the recommended operating conditions per protocol.

- 4. (M,L,O)V<sub>IN</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

# 2.1.2 Recommended Operating Conditions

The following table provides the recommended operating conditions for this device. Note that the values in this table are the recommended and tested operating conditions. Proper device operation outside these conditions is not guaranteed.

**Table 2. Recommended Operating Conditions**

|                                  | Characteristic                                                                                                       | Symbol                               | Recommended<br>Value                               | Unit | Notes |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------|------|-------|

| Core supply volt                 | age                                                                                                                  | V <sub>DD</sub>                      | 1.1 V ± 55 mV                                      | V    | _     |

| PLL supply volta                 | ge                                                                                                                   | AV <sub>DD</sub>                     | 1.1 V ± 55 mV                                      | V    | 1     |

| Core power supp                  | oly for SerDes transceivers                                                                                          | SV <sub>DD</sub>                     | 1.1 V ± 55 mV                                      | V    | _     |

| Pad power supp                   | ly for SerDes transceivers                                                                                           | $XV_{DD}$                            | 1.1 V ± 55 mV                                      | V    | _     |

| DDR and DDR2 DRAM I/O voltage    |                                                                                                                      | GV <sub>DD</sub>                     | 2.5 V ± 125 mV<br>1.8 V ± 90 mV                    | V    | _     |

| Three-speed Ethernet I/O voltage |                                                                                                                      | LV <sub>DD</sub>                     | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   | V    | 4     |

|                                  |                                                                                                                      | $TV_DD$                              | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   | _    | 4     |

|                                  | RT, system control and power management, I <sup>2</sup> C, nagement, and JTAG I/O voltage                            | OV <sub>DD</sub>                     | 3.3 V ± 165 mV                                     | V    | 3     |

| Local bus I/O vo                 | ltage                                                                                                                | BV <sub>DD</sub>                     | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   | V    | _     |

| Input voltage                    | DDR and DDR2 DRAM signals                                                                                            | MV <sub>IN</sub>                     | GND to GV <sub>DD</sub>                            | V    | 2     |

|                                  | DDR and DDR2 DRAM reference                                                                                          | MV <sub>REF</sub>                    | GND to GV <sub>DD</sub> /2                         | V    | 2     |

|                                  | Three-speed Ethernet signals                                                                                         | LV <sub>IN</sub><br>TV <sub>IN</sub> | GND to LV <sub>DD</sub><br>GND to TV <sub>DD</sub> | V    | 4     |

|                                  | Local bus signals                                                                                                    | BV <sub>IN</sub>                     | GND to BV <sub>DD</sub>                            | V    | _     |

|                                  | PCI, DUART, SYSCLK, system control and power management, I <sup>2</sup> C, Ethernet MII management, and JTAG signals | OV <sub>IN</sub>                     | GND to OV <sub>DD</sub>                            | V    | 3     |

**Input Clocks**

## 4.5 Platform to FIFO Restrictions

Note the following FIFO maximum speed restrictions based on platform speed.

For FIFO GMII mode:

FIFO TX/RX clock frequency ≤ platform clock frequency/4.2

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency must be no more than 127 MHz.

For FIFO encoded mode:

FIFO TX/RX clock frequency ≤ platform clock frequency/4.2

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency must be no more than 167 MHz.

# 4.6 Platform Frequency Requirements for PCI-Express and Serial RapidIO

The CCB clock frequency must be considered for proper operation of the high-speed PCI-Express and Serial RapidIO interfaces as described below.

For proper PCI Express operation, the CCB clock frequency must be greater than:

527 MHz × (PCI-Express link width)

8

See MPC8548ERM, Rev. 2, PowerQUICC III Integrated Processor Family Reference Manual, Section 18.1.3.2, "Link Width," for PCI Express interface width details.

For proper serial RapidIO operation, the CCB clock frequency must be greater than:

2 × (0.80) × (Serial RapidIO interface frequency) × (Serial RapidIO link width)

See MPC8548ERM, Rev. 2, PowerQUICC III Integrated Processor Family Reference Manual, Section 17.4, "1x/4x LP-Serial Signal Descriptions," for serial RapidIO interface width and frequency details.

# 4.7 Other Input Clocks

For information on the input clocks of other functional blocks of the platform see the specific section of this document.

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

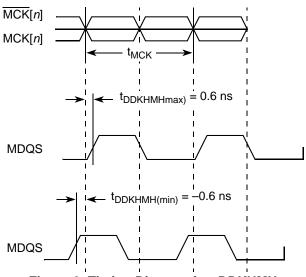

#### Table 19. DDR SDRAM Output AC Timing Specifications (continued)

At recommended operating conditions.

| Parameter         | Symbol <sup>1</sup> | Min  | Max | Unit | Notes |

|-------------------|---------------------|------|-----|------|-------|

| MDQS epilogue end | t <sub>DDKHME</sub> | -0.6 | 0.6 | ns   | 6     |

#### Notes:

- 1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

- 2. All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

- 3. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS.

- 4. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK[n] clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the MDQS override bits (called WR\_DATA\_DELAY) in the TIMING\_CFG\_2 register. This is typically set to the same delay as in DDR\_SDRAM\_CLK\_CNTL[CLK\_ADJUST]. The timing parameters listed in the table assume that these 2 parameters have been set to the same adjustment value. See the MPC8548E PowerQUICC III Integrated Processor Reference Manual for a description and understanding of the timing modifications enabled by use of these bits.

- 5. Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe must be centered inside of the data eye at the pins of the microprocessor.

- 6. All outputs are referenced to the rising edge of MCK[n] at the pins of the microprocessor. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

#### NOTE

For the ADDR/CMD setup and hold specifications in Table 19, it is assumed that the clock control register is set to adjust the memory clocks by 1/2 applied cycle.

Figure 3 shows the DDR SDRAM output timing for the MCK to MDQS skew measurement (t<sub>DDKHMH</sub>).

Figure 3. Timing Diagram for tDDKHMH

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

Table 23. GMII, MII, RMII, TBI, RGMII, RTBI, and FIFO DC Electrical Characteristics

| Parameters                                                                                    | Symbol                             | Min      | Max                     | Unit | Notes   |

|-----------------------------------------------------------------------------------------------|------------------------------------|----------|-------------------------|------|---------|

| Supply voltage 2.5 V                                                                          | LV <sub>DD</sub> /TV <sub>DD</sub> | 2.37     | 2.63                    | V    | 1, 2    |

| Output high voltage (LV <sub>DD</sub> /TV <sub>DD</sub> = Min, $I_{OH} = -1.0 \text{ mA}$ )   | V <sub>OH</sub>                    | 2.00     | $LV_{DD}/TV_{DD} + 0.3$ | V    | _       |

| Output low voltage (LV <sub>DD</sub> /TV <sub>DD</sub> = Min, $I_{OL}$ = 1.0 mA)              | V <sub>OL</sub>                    | GND -0.3 | 0.40                    | V    | _       |

| Input high voltage                                                                            | V <sub>IH</sub>                    | 1.70     | $LV_{DD}/TV_{DD} + 0.3$ | V    | _       |

| Input low voltage                                                                             | V <sub>IL</sub>                    | -0.3     | 0.90                    | V    | _       |

| Input high current (V <sub>IN</sub> = LV <sub>DD</sub> , V <sub>IN</sub> = TV <sub>DD</sub> ) | I <sub>IH</sub>                    | _        | 10                      | μΑ   | 1, 2, 3 |

| Input low current (V <sub>IN</sub> = GND)                                                     | I <sub>IL</sub>                    | -15      | _                       | μΑ   | 3       |

- 1. LV<sub>DD</sub> supports eTSECs 1 and 2.

- 2. TV<sub>DD</sub> supports eTSECs 3 and 4.

- 3. Note that the symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> and TV<sub>IN</sub> symbols referenced in Table 1 and Table 2.

# 8.2 FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications

The AC timing specifications for FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI are presented in this section.

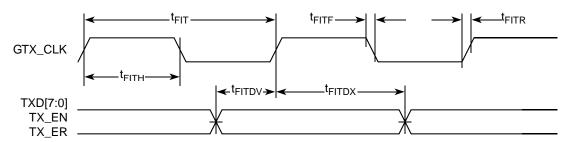

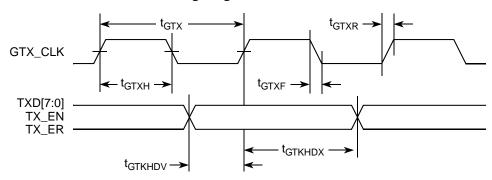

# 8.2.1 FIFO AC Specifications

The basis for the AC specifications for the eTSEC's FIFO modes is the double data rate RGMII and RTBI specifications, since they have similar performances and are described in a source-synchronous fashion like FIFO modes. However, the FIFO interface provides deliberate skew between the transmitted data and source clock in GMII fashion.

When the eTSEC is configured for FIFO modes, all clocks are supplied from external sources to the relevant eTSEC interface. That is, the transmit clock must be applied to the eTSECn's TSECn\_TX\_CLK, while the receive clock must be applied to pin TSECn\_RX\_CLK. The eTSEC internally uses the transmit clock to synchronously generate transmit data and outputs an echoed copy of the transmit clock back out onto the TSECn\_GTX\_CLK pin (while transmit data appears on TSECn\_TXD[7:0], for example). It is intended that external receivers capture eTSEC transmit data using the clock on TSECn\_GTX\_CLK as a source- synchronous timing reference. Typically, the clock edge that launched the data can be used, since the clock is delayed by the eTSEC to allow acceptable set-up margin at the receiver. Note that there is relationship between the maximum FIFO speed and the platform speed. For more information see Section 4.5, "Platform to FIFO Restrictions."

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

A summary of the FIFO AC specifications appears in Table 24 and Table 25.

**Table 24. FIFO Mode Transmit AC Timing Specification**

| Parameter/Condition                                    | Symbol                              | Min | Тур | Max  | Unit |

|--------------------------------------------------------|-------------------------------------|-----|-----|------|------|

| TX_CLK, GTX_CLK clock period                           | t <sub>FIT</sub>                    | 5.3 | 8.0 | 100  | ns   |

| TX_CLK, GTX_CLK duty cycle                             | t <sub>FITH</sub> /t <sub>FIT</sub> | 45  | 50  | 55   | %    |

| TX_CLK, GTX_CLK peak-to-peak jitter                    | t <sub>FITJ</sub>                   | _   | _   | 250  | ps   |

| Rise time TX_CLK (20%–80%)                             | t <sub>FITR</sub>                   | _   | _   | 0.75 | ns   |

| Fall time TX_CLK (80%–20%)                             | t <sub>FITF</sub>                   | _   | _   | 0.75 | ns   |

| FIFO data TXD[7:0], TX_ER, TX_EN setup time to GTX_CLK | t <sub>FITDV</sub>                  | 2.0 | _   | _    | ns   |

| GTX_CLK to FIFO data TXD[7:0], TX_ER, TX_EN hold time  | t <sub>FITDX</sub>                  | 0.5 | _   | 3.0  | ns   |

**Table 25. FIFO Mode Receive AC Timing Specification**

| Parameter/Condition                         | Symbol                              | Min | Тур | Max  | Unit |

|---------------------------------------------|-------------------------------------|-----|-----|------|------|

| RX_CLK clock period                         | t <sub>FIR</sub>                    | 5.3 | 8.0 | 100  | ns   |

| RX_CLK duty cycle                           | t <sub>FIRH</sub> /t <sub>FIR</sub> | 45  | 50  | 55   | %    |

| RX_CLK peak-to-peak jitter                  | t <sub>FIRJ</sub>                   | _   | _   | 250  | ps   |

| Rise time RX_CLK (20%–80%)                  | t <sub>FIRR</sub>                   | _   | _   | 0.75 | ns   |

| Fall time RX_CLK (80%–20%)                  | t <sub>FIRF</sub>                   | _   | _   | 0.75 | ns   |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>FIRDV</sub>                  | 1.5 | _   | _    | ns   |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>FIRDX</sub>                  | 0.5 | _   | _    | ns   |

#### Note:

Timing diagrams for FIFO appear in Figure 6 and Figure 7.

Figure 6. FIFO Transmit AC Timing Diagram

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

<sup>1.</sup> The minimum cycle period of the TX\_CLK and RX\_CLK is dependent on the maximum platform frequency of the speed bins the part belongs to as well as the FIFO mode under operation. See Section 4.5, "Platform to FIFO Restrictions."

Figure 8 shows the GMII transmit AC timing diagram.

Figure 8. GMII Transmit AC Timing Diagram

## 8.2.2.2 GMII Receive AC Timing Specifications

This table provides the GMII receive AC timing specifications.

Parameter/Condition Symbol<sup>1</sup> Min Typ Max Unit RX\_CLK clock period 8.0 t<sub>GRX</sub> ns RX\_CLK duty cycle 35 75 t<sub>GRXH</sub>/t<sub>GRX</sub> ns RXD[7:0], RX\_DV, RX\_ER setup time to RX\_CLK 2.0 ns t<sub>GRDVKH</sub> RXD[7:0], RX\_DV, RX\_ER hold time to RX\_CLK 0 ns t<sub>GRDXKH</sub>  $t_{GRXR}^2$ RX\_CLK clock rise (20%-80%) 1.0 ns  $t_{\text{GRXF}}^2$ RX\_CLK clock fall time (80%-20%) 1.0 ns

**Table 27. GMII Receive AC Timing Specifications**

#### Notes:

- 1. The symbols used for timing specifications follow the pattern of  $t_{(first\ two\ letters\ of\ functional\ block)(signal)(state)}$  for inputs and  $t_{(first\ two\ letters\ of\ functional\ block)(reference)(state)}$  for outputs. For example,  $t_{GRDVKH}$  symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the  $t_{RX}$  clock reference (K) going to the high state (H) or setup time. Also,  $t_{GRDXKL}$  symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the  $t_{GRX}$  clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of  $t_{GRX}$  represents the GMII (G) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 2. Guaranteed by design.

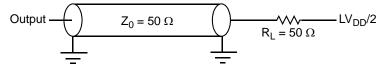

Figure 9 provides the AC test load for eTSEC.

Figure 9. eTSEC AC Test Load

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

Table 34. RMII Transmit AC Timing Specifications (continued)

| Parameter/Condition                             | Symbol <sup>1</sup> | Min | Тур | Max  | Unit |

|-------------------------------------------------|---------------------|-----|-----|------|------|

| TSECn_TX_CLK to RMII data TXD[1:0], TX_EN delay | t <sub>RMTDX</sub>  | 1.0 | _   | 10.0 | ns   |

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

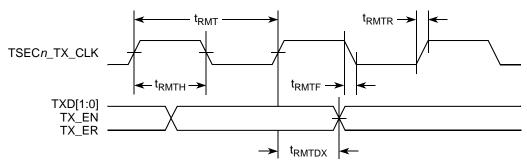

Figure 18 shows the RMII transmit AC timing diagram.

Figure 18. RMII Transmit AC Timing Diagram

## 8.2.7.2 RMII Receive AC Timing Specifications

**Table 35. RMII Receive AC Timing Specifications**

| Parameter/Condition                                       | Symbol <sup>1</sup> | Min  | Тур  | Max  | Unit |

|-----------------------------------------------------------|---------------------|------|------|------|------|

| TSECn_TX_CLK clock period                                 | t <sub>RMR</sub>    | 15.0 | 20.0 | 25.0 | ns   |

| TSECn_TX_CLK duty cycle                                   | t <sub>RMRH</sub>   | 35   | 50   | 65   | %    |

| TSECn_TX_CLK peak-to-peak jitter                          | t <sub>RMRJ</sub>   | _    | _    | 250  | ps   |

| Rise time TSECn_TX_CLK(20%–80%)                           | t <sub>RMRR</sub>   | 1.0  | _    | 2.0  | ns   |

| Fall time TSECn_TX_CLK (80%–20%)                          | t <sub>RMRF</sub>   | 1.0  | _    | 2.0  | ns   |

| RXD[1:0], CRS_DV, RX_ER setup time to REF_CLK rising edge | t <sub>RMRDV</sub>  | 4.0  | _    | _    | ns   |

| RXD[1:0], CRS_DV, RX_ER hold time to REF_CLK rising edge  | t <sub>RMRDX</sub>  | 2.0  | _    | _    | ns   |

#### Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

Table 42. Local Bus Timing Parameters—PLL Bypassed (continued)

| Parameter                                                             | Symbol <sup>1</sup>  | Min  | Max  | Unit | Notes |

|-----------------------------------------------------------------------|----------------------|------|------|------|-------|

| LGTA/LUPWAIT input hold from local bus clock                          | t <sub>LBIXKL2</sub> | -1.3 | _    | ns   | 4, 5  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) | t <sub>LBOTOT</sub>  | 1.5  | _    | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)             | t <sub>LBKLOV1</sub> | _    | -0.3 | ns   | _     |

| Local bus clock to data valid for LAD/LDP                             | t <sub>LBKLOV2</sub> | _    | -0.1 | ns   | 4     |

| Local bus clock to address valid for LAD                              | t <sub>LBKLOV3</sub> | 1    | 0    | ns   | 4     |

| Local bus clock to LALE assertion                                     | t <sub>LBKLOV4</sub> | 1    | 0    | ns   | 4     |

| Output hold from local bus clock (except LAD/LDP and LALE)            | t <sub>LBKLOX1</sub> | -3.7 | _    | ns   | 4     |

| Output hold from local bus clock for LAD/LDP                          | t <sub>LBKLOX2</sub> | -3.7 | 1    | ns   | 4     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)    | t <sub>LBKLOZ1</sub> | _    | 0.2  | ns   | 7     |

| Local bus clock to output high impedance for LAD/LDP                  | t <sub>LBKLOZ2</sub> | _    | 0.2  | ns   | 7     |

- 1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

- 2. All timings are in reference to local bus clock for PLL bypass mode. Timings may be negative with respect to the local bus clock because the actual launch and capture of signals is done with the internal launch/capture clock, which precedes LCLK by t<sub>LBKHKT</sub>.

- 3. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 4. All signals are measured from BV<sub>DD</sub>/2 of the rising edge of local bus clock for PLL bypass mode to 0.4 × BV<sub>DD</sub> of the signal in question for 3.3-V signaling levels.

- 5. Input timings are measured at the pin.

- 6. The value of t<sub>LBOTOT</sub> is the measurement of the minimum time between the negation of LALE and any change in LAD.

- 7. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 8. Guaranteed by characterization.

- 9. Guaranteed by design.

| Table 44. JTAG AC Timing | Specifications | (Independent of SYSCL | .K) <sup>1</sup> (continued) |

|--------------------------|----------------|-----------------------|------------------------------|

|--------------------------|----------------|-----------------------|------------------------------|

| Parameter                                                             | Symbol <sup>2</sup>                        | Min      | Max      | Unit | Notes |

|-----------------------------------------------------------------------|--------------------------------------------|----------|----------|------|-------|

| Valid times:  Boundary-scan data TDO                                  | t <sub>JTKLDV</sub><br>t <sub>JTKLOV</sub> | 4<br>2   | 20<br>10 | ns   | 5     |

| Output hold times:  Boundary-scan data TDO                            | t <sub>JTKLDX</sub><br>t <sub>JTKLOX</sub> | 30<br>30 |          | ns   | 5     |

| JTAG external clock to output high impedance:  Boundary-scan data TDO | t <sub>JTKLDZ</sub><br>t <sub>JTKLOZ</sub> | 3 3      | 19<br>9  | ns   | 5, 6  |

- All outputs are measured from the midpoint voltage of the falling/rising edge of t<sub>TCLK</sub> to the midpoint of the signal in question.

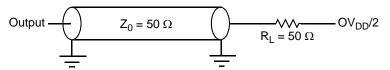

The output timings are measured at the pins. All output timings assume a purely resistive 50-Ω load (see Figure 29).

Time-of-flight delays must be added for trace lengths, vias, and connectors in the system.

- 2. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>JTDVKH</sub> symbolizes JTAG device timing (JT) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>JTDXKH</sub> symbolizes JTAG timing (JT) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>JTG</sub> clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 3. TRST is an asynchronous level sensitive signal. The setup time is for test purposes only.

- 4. Non-JTAG signal input timing with respect to t<sub>TCLK</sub>.

- 5. Non-JTAG signal output timing with respect to t<sub>TCLK</sub>.

- 6. Guaranteed by design.

Figure 29 provides the AC test load for TDO and the boundary-scan outputs.

Figure 29. AC Test Load for the JTAG Interface

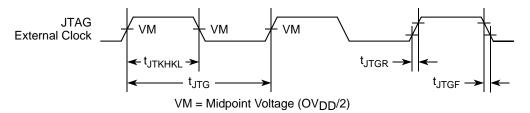

Figure 30 provides the JTAG clock input timing diagram.

Figure 30. JTAG Clock Input Timing Diagram

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

#### **PCI Express**

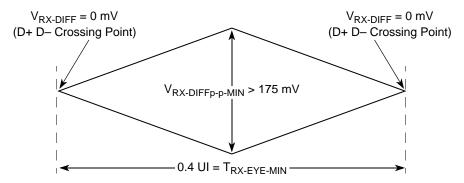

The eye diagram must be valid for any 250 consecutive UIs.

A recovered TX UI is calculated over 3500 consecutive unit intervals of sample data. The eye diagram is created using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the TX UI.

#### NOTE

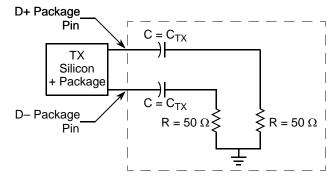

The reference impedance for return loss measurements is 50. to ground for both the D+ and D- line (that is, as measured by a vector network analyzer with  $50-\Omega$  probes—see Figure 50). Note that the series capacitors, CTX, are optional for the return loss measurement.

Figure 49. Minimum Receiver Eye Timing and Voltage Compliance Specification

# 17.5.1 Compliance Test and Measurement Load

The AC timing and voltage parameters must be verified at the measurement point, as specified within 0.2 inches of the package pins, into a test/measurement load shown in Figure 50.

#### NOTE

The allowance of the measurement point to be within 0.2 inches of the package pins is meant to acknowledge that package/board routing may benefit from D+ and D- not being exactly matched in length at the package pin boundary.

Figure 50. Compliance Test/Measurement Load

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

# 18.5 Explanatory Note on Transmitter and Receiver Specifications

AC electrical specifications are given for transmitter and receiver. Long- and short-run interfaces at three baud rates (a total of six cases) are described.

The parameters for the AC electrical specifications are guided by the XAUI electrical interface specified in Clause 47 of IEEE 802.3ae-2002.

XAUI has similar application goals to Serial RapidIO, as described in Section 8.1. The goal of this standard is that electrical designs for Serial RapidIO can reuse electrical designs for XAUI, suitably modified for applications at the baud intervals and reaches described herein.

# 18.6 Transmitter Specifications

LP-serial transmitter electrical and timing specifications are stated in the text and tables of this section.

The differential return loss, S11, of the transmitter in each case shall be better than:

- -10 dB for (baud frequency)/10 < Freq(f) < 625 MHz, and

- $-10 \text{ dB} + 10 \log(f/625 \text{ MHz}) \text{ dB for } 625 \text{ MHz} \leq \text{Freq}(f) \leq \text{baud frequency}$

The reference impedance for the differential return loss measurements is  $100-\Omega$  resistive. Differential return loss includes contributions from on-chip circuitry, chip packaging, and any off-chip components related to the driver. The output impedance requirement applies to all valid output levels.

It is recommended that the 20%-80% rise/fall time of the transmitter, as measured at the transmitter output, in each case have a minimum value 60 ps.

It is recommended that the timing skew at the output of an LP-serial transmitter between the two signals that comprise a differential pair not exceed 25 ps at 1.25 GB, 20 ps at 2.50 GB, and 15 ps at 3.125 GB.

| Characteristic              | Symbol          | Range |      | Unit   | Notes                                                                      |

|-----------------------------|-----------------|-------|------|--------|----------------------------------------------------------------------------|

|                             |                 | Max   |      | Notes  |                                                                            |

| Output voltage              | Vo              | -0.40 | 2.30 | V      | Voltage relative to COMMON of either signal comprising a differential pair |

| Differential output voltage | $V_{DIFFPP}$    | 500   | 1000 | mV p-p | _                                                                          |

| Deterministic jitter        | $J_D$           | _     | 0.17 | UI p-p | _                                                                          |

| Total jitter                | J <sub>T</sub>  | _     | 0.35 | UI p-p | _                                                                          |

| Multiple output skew        | S <sub>MO</sub> | _     | 1000 | ps     | Skew at the transmitter output between lanes of a multilane link           |

| Unit Interval               | UI              | 800   | 800  | ps     | ±100 ppm                                                                   |

Table 59. Short Run Transmitter AC Timing Specifications—1.25 GBaud

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

## **Package Description**

Table 71. MPC8548E Pinout Listing (continued)

| Signal                 | Package Pin Number                                                                                                                                                                                                                                                                             | Pin Type | Power<br>Supply  | Notes    |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

| PCI1_REQ[4:1]          | AH2, AG4, AG3, AH4                                                                                                                                                                                                                                                                             | I        | OV <sub>DD</sub> | _        |

|                        |                                                                                                                                                                                                                                                                                                |          |                  | _        |

|                        |                                                                                                                                                                                                                                                                                                |          |                  | _        |

|                        |                                                                                                                                                                                                                                                                                                |          |                  | _        |

|                        |                                                                                                                                                                                                                                                                                                |          |                  | _        |

| PCI1_REQ0              | AH3                                                                                                                                                                                                                                                                                            | I/O      | $OV_{DD}$        | _        |

| PCI1_CLK               | AH26                                                                                                                                                                                                                                                                                           | ı        | $OV_{DD}$        | 39       |

| PCI1_DEVSEL            | AH11                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_FRAME             | AE11                                                                                                                                                                                                                                                                                           | I/O      | $OV_{DD}$        | 2        |

| PCI1_IDSEL             | AG9                                                                                                                                                                                                                                                                                            | I        | OV <sub>DD</sub> | _        |

| PCI1_REQ64/PCI2_FRAME  | AF14                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2, 5, 10 |

| PCI1_ACK64/PCI2_DEVSEL | V15                                                                                                                                                                                                                                                                                            | I/O      | $OV_{DD}$        | 2        |

| PCI2_CLK               | AE28                                                                                                                                                                                                                                                                                           | I        | OV <sub>DD</sub> | 39       |

| PCI2_IRDY              | AD26                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_PERR              | AD25                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_GNT[4:1]          | AE26, AG24, AF25, AE25                                                                                                                                                                                                                                                                         | 0        | OV <sub>DD</sub> | 5, 9, 35 |

| PCI2_GNT0              | AG25                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | _        |

| PCI2_SERR              | AD24                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2, 4     |

| PCI2_STOP              | AF24                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_TRDY              | AD27                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_REQ[4:1]          | AD28, AE27, W17, AF26                                                                                                                                                                                                                                                                          | l        | OV <sub>DD</sub> | _        |

| PCI2_REQ0              | AH25                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | _        |

|                        | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                     |          |                  |          |

| MDQ[0:63]              | L18, J18, K14, L13, L19, M18, L15, L14, A17, B17, A13, B12, C18, B18, B13, A12, H18, F18, J14, F15, K19, J19, H16, K15, D17, G16, K13, D14, D18, F17, F14, E14, A7, A6, D5, A4, C8, D7, B5, B4, A2, B1, D1, E4, A3, B2, D2, E3, F3, G4, J5, K5, F6, G5, J6, K4, J1, K2, M5, M3, J3, J2, L1, M6 | I/O      | GV <sub>DD</sub> | _        |

| MECC[0:7]              | H13, F13, F11, C11, J13, G13, D12, M12                                                                                                                                                                                                                                                         | I/O      | GV <sub>DD</sub> | _        |

| MDM[0:8]               | M17, C16, K17, E16, B6, C4, H4, K1, E13                                                                                                                                                                                                                                                        | 0        | GV <sub>DD</sub> | _        |

| MDQS[0:8]              | M15, A16, G17, G14, A5, D3, H1, L2, C13                                                                                                                                                                                                                                                        | I/O      | GV <sub>DD</sub> | _        |

| MDQS[0:8]              | L17, B16, J16, H14, C6, C2, H3, L4, D13                                                                                                                                                                                                                                                        | I/O      | GV <sub>DD</sub> | _        |

| MA[0:15]               | A8, F9, D9, B9, A9, L10, M10, H10, K10, G10,<br>B8, E10, B10, G6, A10, L11                                                                                                                                                                                                                     | 0        | GV <sub>DD</sub> | _        |

| MBA[0:2]               | F7, J7, M11                                                                                                                                                                                                                                                                                    | 0        | GV <sub>DD</sub> | _        |

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

Table 71. MPC8548E Pinout Listing (continued)

| Signal        | Package Pin Number | Pin Type                                    | Power<br>Supply | Notes |

|---------------|--------------------|---------------------------------------------|-----------------|-------|

| SENSEVSS      | M16                | _                                           | _               | 13    |

|               | Analog Signals     |                                             |                 |       |

| MVREF         | A18                | I<br>Reference<br>voltage signal<br>for DDR | MVREF           | _     |

| SD_IMP_CAL_RX | L28                | I                                           | 200Ω to<br>GND  | _     |

| SD_IMP_CAL_TX | AB26               | I                                           | 100Ω to<br>GND  | _     |

| SD_PLL_TPA    | U26                | 0                                           | _               | 24    |

- 1. All multiplexed signals are listed only once and do not re-occur. For example, LCS5/DMA\_REQ2 is listed only once in the local bus controller section, and is not mentioned in the DMA section even though the pin also functions as DMA\_REQ2.

- 2. Recommend a weak pull-up resistor (2–10  $k\Omega$ ) be placed on this pin to OV<sub>DD</sub>.

- 3. A valid clock must be provided at POR if TSEC4\_TXD[2] is set = 1.

- 4. This pin is an open drain signal.

- 5. This pin is a reset configuration pin. It has a weak internal pull-up P-FET which is enabled only when the processor is in the reset state. This pull-up is designed such that it can be overpowered by an external 4.7-kΩ pull-down resistor. However, if the signal is intended to be high after reset, and if there is any device on the net which might pull down the value of the net at reset, then a pullup or active driver is needed.

- 6. Treat these pins as no connects (NC) unless using debug address functionality.

- 7. The value of LA[28:31] during reset sets the CCB clock to SYSCLK PLL ratio. These pins require 4.7-kΩ pull-up or pull-down resistors. See Section 20.2, "CCB/SYSCLK PLL Ratio."

- 8. The value of LALE, LGPL2, and LBCTL at reset set the e500 core clock to CCB clock PLL ratio. These pins require 4.7-kΩ pull-up or pull-down resistors. See the Section 20.3, "e500 Core PLL Ratio."

- 9. Functionally, this pin is an output, but structurally it is an I/O because it either samples configuration input during reset or because it has other manufacturing test functions. This pin therefore is described as an I/O for boundary scan.

- 10. This pin functionally requires a pull-up resistor, but during reset it is a configuration input that controls 32- vs. 64-bit PCI operation. Therefore, it must be actively driven low during reset by reset logic if the device is to be configured to be a 64-bit PCI device. See the *PCI Specification*.

- 11. This output is actively driven during reset rather than being three-stated during reset.

- 12. These JTAG pins have weak internal pull-up P-FETs that are always enabled.

- 13. These pins are connected to the V<sub>DD</sub>/GND planes internally and may be used by the core power supply to improve tracking and regulation.

- 14.Internal thermally sensitive resistor.

- 15.No connections must be made to these pins if they are not used.

- 16. These pins are not connected for any use.

- 17.PCI specifications recommend that a weak pull-up resistor (2–10 k $\Omega$ ) be placed on the higher order pins to OV<sub>DD</sub> when using 64-bit buffer mode (pins PCI\_AD[63:32] and PCI1\_C\_BE[7:4]).

- 19. If this pin is connected to a device that pulls down during reset, an external pull-up is required to drive this pin to a safe state during reset.

- 20. This pin is only an output in FIFO mode when used as Rx flow control.

- 24.Do not connect.

## **Package Description**

Table 73. MPC8545E Pinout Listing (continued)

| Signal                | Package Pin Number                              | Pin Type | Power<br>Supply  | Notes    |

|-----------------------|-------------------------------------------------|----------|------------------|----------|

| UDE AH16              |                                                 | I        | OV <sub>DD</sub> | _        |

| MCP                   | AG19                                            | I        | OV <sub>DD</sub> | _        |

| IRQ[0:7]              | AG23, AF18, AE18, AF20, AG18, AF17, AH24, AE20  | I        | OV <sub>DD</sub> | _        |

| IRQ[8]                | AF19                                            | I        | OV <sub>DD</sub> | _        |

| IRQ[9]/DMA_DREQ3      | AF21                                            | I        | OV <sub>DD</sub> | 1        |

| IRQ[10]/DMA_DACK3     | AE19                                            | I/O      | OV <sub>DD</sub> | 1        |

| IRQ[11]/DMA_DDONE3    | AD20                                            | I/O      | OV <sub>DD</sub> | 1        |

| IRQ_OUT               | AD18                                            | 0        | OV <sub>DD</sub> | 2, 4     |

|                       | Ethernet Management Interface                   |          | 1                | •        |

| EC_MDC                | AB9                                             | 0        | OV <sub>DD</sub> | 5, 9     |

| EC_MDIO               | AC8                                             | I/O      | OV <sub>DD</sub> | _        |

|                       | Gigabit Reference Clock                         |          |                  |          |

| EC_GTX_CLK125         | V11                                             | I        | LV <sub>DD</sub> | _        |

|                       | Three-Speed Ethernet Controller (Gigabit Ethern | et 1)    |                  |          |

| TSEC1_RXD[7:0]        | R5, U1, R3, U2, V3, V1, T3, T2                  | I        | LV <sub>DD</sub> | T —      |

| TSEC1_TXD[7:0]        | T10, V7, U10, U5, U4, V6, T5, T8                | 0        | LV <sub>DD</sub> | 5, 9     |

| TSEC1_COL             | R4                                              | I        | LV <sub>DD</sub> | _        |

| TSEC1_CRS             | V5                                              | I/O      | LV <sub>DD</sub> | 20       |

| TSEC1_GTX_CLK         | U7                                              | 0        | LV <sub>DD</sub> | _        |

| TSEC1_RX_CLK          | U3                                              | I        | LV <sub>DD</sub> | _        |

| TSEC1_RX_DV           | V2                                              | I        | LV <sub>DD</sub> | <u> </u> |

| TSEC1_RX_ER           | T1                                              | I        | LV <sub>DD</sub> | T —      |

| TSEC1_TX_CLK          | Т6                                              | I        | LV <sub>DD</sub> | _        |

| TSEC1_TX_EN           | U9                                              | 0        | LV <sub>DD</sub> | 30       |

| TSEC1_TX_ER           | Т7                                              | 0        | LV <sub>DD</sub> | _        |

| GPIN[0:7]             | P2, R2, N1, N2, P3, M2, M1, N3                  | I        | LV <sub>DD</sub> | 103      |

| GPOUT[0:5]            | N9, N10, P8, N7, R9, N5                         | 0        | LV <sub>DD</sub> | _        |

| cfg_dram_type0/GPOUT6 | R8                                              | 0        | LV <sub>DD</sub> | 5, 9     |

| GPOUT7                | N6                                              | 0        | LV <sub>DD</sub> | _        |

| Reserved              | Reserved P1                                     |          | _                | 104      |

| Reserved              | R6                                              | _        | <u> </u>         | 104      |

| Reserved              | P6                                              | _        | <u> </u>         | 15       |

| Reserved              | N4                                              | _        | _                | 105      |

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

Table 73. MPC8545E Pinout Listing (continued)

| Signal         | Package Pin Number                      | Pin Type                         | Power<br>Supply        | Notes    |

|----------------|-----------------------------------------|----------------------------------|------------------------|----------|

| FIFO1_RXC2     | P5                                      | 1                                | LV <sub>DD</sub>       | 104      |

| Reserved       | R1                                      | _                                | — 104                  |          |

| Reserved       | P10                                     | _                                | _                      | 105      |

| FIFO1_TXC2     | P7                                      | 0                                | LV <sub>DD</sub>       | 15       |

| cfg_dram_type1 | R10                                     | 1                                | LV <sub>DD</sub>       | 5        |

| Thre           | ee-Speed Ethernet Controller (Gigabit E | thernet 3)                       |                        | •        |

| TSEC3_TXD[3:0] | V8, W10, Y10, W7                        | 0                                | TV <sub>DD</sub>       | 5, 9, 29 |

| TSEC3_RXD[3:0] | Y1, W3, W5, W4                          | 1                                | TV <sub>DD</sub>       | _        |

| TSEC3_GTX_CLK  | W8                                      | 0                                | TV <sub>DD</sub>       | _        |

| TSEC3_RX_CLK   | W2                                      | 1                                | TV <sub>DD</sub>       | _        |

| TSEC3_RX_DV    | W1                                      | 1                                | TV <sub>DD</sub>       | _        |

| TSEC3_RX_ER    | Y2                                      | 1                                | TV <sub>DD</sub>       | _        |

| TSEC3_TX_CLK   | V10                                     | 1                                | TV <sub>DD</sub>       | _        |

| TSEC3_TX_EN    | V9                                      | 0                                | TV <sub>DD</sub>       | 30       |

| TSEC3_TXD[7:4] | AB8, Y7, AA7, Y8                        | , Y7, AA7, Y8 O TV <sub>DD</sub> |                        | 5, 9, 29 |

| TSEC3_RXD[7:4] | AA1, Y3, AA2, AA4                       | 1                                | TV <sub>DD</sub>       | _        |

| Reserved       | AA5                                     | _                                | <u> </u>               |          |

| TSEC3_COL      | Y5                                      | I                                | TV <sub>DD</sub> —     |          |

| TSEC3_CRS      | AA3                                     | I/O                              | TV <sub>DD</sub> 31    |          |

| TSEC3_TX_ER    | AB6                                     | 0                                | TV <sub>DD</sub>       | _        |

|                | DUART                                   |                                  |                        |          |

| UART_CTS[0:1]  | AB3, AC5                                | I                                | OV <sub>DD</sub>       | _        |

| UART_RTS[0:1]  | AC6, AD7                                | 0                                | OV <sub>DD</sub>       | _        |

| UART_SIN[0:1]  | AB5, AC7                                | I                                | OV <sub>DD</sub> —     |          |

| UART_SOUT[0:1] | AB7, AD8                                | 0                                | OV <sub>DD</sub>       | _        |

|                | I <sup>2</sup> C interface              |                                  |                        |          |

| IIC1_SCL       | AG22                                    | I/O                              | OV <sub>DD</sub>       | 4, 27    |

| IIC1_SDA       | AG21                                    | I/O                              | OV <sub>DD</sub> 4, 27 |          |

| IIC2_SCL       | AG15                                    | I/O                              | OV <sub>DD</sub>       | 4, 27    |

| IIC2_SDA       | AG14                                    | I/O                              | OV <sub>DD</sub>       | 4, 27    |

|                | SerDes                                  |                                  |                        |          |

| SD_RX[0:3]     | M28, N26, P28, R26                      | I                                | $XV_{DD}$              |          |

| SD_RX[0:3]     | M27, N25, P27, R25                      | I                                | $XV_{DD}$              |          |

| SD_TX[0:3]     | M22, N20, P22, R20                      | 0                                | $XV_{DD}$              | _        |

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

Table 74. MPC8543E Pinout Listing (continued)

| Signal                   | Package Pin Number                                                                                                                                             | Pin Type | Power<br>Supply  | Notes   |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|---------|

| MWE                      | E7                                                                                                                                                             | 0        | GV <sub>DD</sub> | _       |

| MCAS                     | H7                                                                                                                                                             | 0        | GV <sub>DD</sub> | _       |

| MRAS                     | L8                                                                                                                                                             | 0        | GV <sub>DD</sub> | _       |

| MCKE[0:3]                | F10, C10, J11, H11                                                                                                                                             | 0        | GV <sub>DD</sub> | 11      |

| MCS[0:3]                 | K8, J8, G8, F8                                                                                                                                                 | 0        | GV <sub>DD</sub> | _       |

| MCK[0:5]                 | H9, B15, G2, M9, A14, F1                                                                                                                                       | 0        | GV <sub>DD</sub> | _       |

| MCK[0:5]                 | J9, A15, G1, L9, B14, F2                                                                                                                                       | 0        | GV <sub>DD</sub> | _       |

| MODT[0:3]                | E6, K6, L7, M7                                                                                                                                                 | 0        | GV <sub>DD</sub> | _       |

| MDIC[0:1]                | A19, B19                                                                                                                                                       | I/O      | GV <sub>DD</sub> | 36      |

|                          | Local Bus Controller Interface                                                                                                                                 |          |                  | 1       |

| LAD[0:31]                | E27, B20, H19, F25, A20, C19, E28, J23, A25, K22, B28, D27, D19, J22, K20, D28, D25, B25, E22, F22, F21, C25, C22, B23, F20, A23, A22, E19, A21, D21, F19, B21 | I/O      | BV <sub>DD</sub> | _       |

| LDP[0:3]                 | K21, C28, B26, B22                                                                                                                                             | I/O      | BV <sub>DD</sub> | _       |

| LA[27]                   | H21                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 9    |

| LA[28:31]                | H20, A27, D26, A28                                                                                                                                             | 0        | BV <sub>DD</sub> | 5, 7, 9 |

| LCS[0:4]                 | J25, C20, J24, G26, A26                                                                                                                                        | 0        | BV <sub>DD</sub> | _       |

| LCS5/DMA_DREQ2           | D23                                                                                                                                                            | I/O      | BV <sub>DD</sub> | 1       |

| LCS6/DMA_DACK2           | G20                                                                                                                                                            | 0        | BV <sub>DD</sub> | 1       |

| LCS7/DMA_DDONE2          | E21                                                                                                                                                            | 0        | BV <sub>DD</sub> | 1       |

| LWE0/LBS0/LSDDQM[0]      | G25                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE1/LBS1/LSDDQM[1]      | C23                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 9    |

| LWE2/LBS2/LSDDQM[2]      | J21                                                                                                                                                            | 0        | $BV_DD$          | 5, 9    |

| LWE3/LBS3/LSDDQM[3]      | A24                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 9    |

| LALE                     | H24                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| LBCTL                    | G27                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| LGPL0/LSDA10             | F23                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 9    |

| LGPL1/LSDWE              | G22                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 9    |

| LGPL2/LOE/LSDRAS         | B27                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 8, 9 |

| LGPL3/LSDCAS             | F24                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 9    |

| LGPL4/LGTA/LUPWAIT/LPBSE | H23                                                                                                                                                            | I/O      | BV <sub>DD</sub> |         |

| LGPL5                    | E26                                                                                                                                                            | 0        | BV <sub>DD</sub> | 5, 9    |

| LCKE                     | E24                                                                                                                                                            | 0        | BV <sub>DD</sub> | _       |

| LCLK[0:2]                | E23, D24, H22                                                                                                                                                  | 0        | BV <sub>DD</sub> |         |

## **Package Description**

Table 74. MPC8543E Pinout Listing (continued)

| Signal           | Package Pin Number                                                                                                                                       | Pin Type                                                              | Power<br>Supply  | Notes |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------|-------|

| TV <sub>DD</sub> | W9, Y6                                                                                                                                                   | Power for<br>TSEC3 and<br>TSEC4<br>(2,5 V, 3.3 V)                     | TV <sub>DD</sub> | _     |

| GV <sub>DD</sub> | B3, B11, C7, C9, C14, C17, D4, D6, D10, D15, E2, E8, E11, E18, F5, F12, F16, G3, G7, G9, G11, H5, H12, H15, H17, J10, K3, K12, K16, K18, L6, M4, M8, M13 | Power for<br>DDR1 and<br>DDR2<br>DRAM I/O<br>voltage<br>(1.8 V,2.5 V) | GV <sub>DD</sub> | _     |

| BV <sub>DD</sub> | C21, C24, C27, E20, E25, G19, G23, H26, J20                                                                                                              | Power for<br>local bus<br>(1.8 V, 2.5 V,<br>3.3 V)                    | BV <sub>DD</sub> | _     |

| V <sub>DD</sub>  | M19, N12, N14, N16, N18, P11, P13, P15, P17, P19, R12, R14, R16, R18, T11, T13, T15, T17, T19, U12, U14, U16, U18, V17, V19                              | Power for core (1.1 V)                                                | V <sub>DD</sub>  |       |

| SV <sub>DD</sub> | L25, L27, M24, N28, P24, P26, R24, R27, T25, V24, V26, W24, W27, Y25, AA28, AC27                                                                         | Core power<br>for SerDes<br>transceivers<br>(1.1 V)                   | SV <sub>DD</sub> | _     |

| XV <sub>DD</sub> | L20, L22, N23, P21, R22, T20, U23, V21, W22,<br>Y20                                                                                                      | Pad power<br>for SerDes<br>transceivers<br>(1.1 V)                    | XV <sub>DD</sub> | _     |

| AVDD_LBIU        | J28                                                                                                                                                      | Power for local bus PLL (1.1 V)                                       | _                | 26    |

| AVDD_PCI1        | AH21                                                                                                                                                     | Power for<br>PCI1 PLL<br>(1.1 V)                                      | _                | 26    |

| AVDD_PCI2        | AH22                                                                                                                                                     | Power for<br>PCI2 PLL<br>(1.1 V)                                      | _                | 26    |

| AVDD_CORE        | AH15                                                                                                                                                     | Power for<br>e500 PLL<br>(1.1 V)                                      | _                | 26    |

| AVDD_PLAT        | AH19                                                                                                                                                     | Power for<br>CCB PLL<br>(1.1 V)                                       | _                | 26    |

| AVDD_SRDS        | U25                                                                                                                                                      | Power for<br>SRDSPLL<br>(1.1 V)                                       | _                | 26    |

| SENSEVDD         | M14                                                                                                                                                      | 0                                                                     | $V_{DD}$         | 13    |

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

#### **System Design Information**

- First, the board must have at least 10 × 10-nF SMT ceramic chip capacitors as close as possible to

the supply balls of the device. Where the board has blind vias, these capacitors must be placed

directly below the chip supply and ground connections. Where the board does not have blind vias,

these capacitors must be placed in a ring around the device as close to the supply and ground

connections as possible.

- Second, there must be a 1-μF ceramic chip capacitor from each SerDes supply (SV<sub>DD</sub> and XV<sub>DD</sub>) to the board ground plane on each side of the device. This must be done for all SerDes supplies.

- Third, between the device and any SerDes voltage regulator there must be a 10-μF, low equivalent series resistance (ESR) SMT tantalum chip capacitor and a 100-μF, low ESR SMT tantalum chip capacitor. This must be done for all SerDes supplies.

## 22.5 Connection Recommendations

To ensure reliable operation, it is highly recommended to connect unused inputs to an appropriate signal level. All unused active low inputs must be tied to  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $OV_{DD}$ , and  $LV_{DD}$ , as required. All unused active high inputs must be connected to GND. All NC (no-connect) signals must remain unconnected. Power and ground connections must be made to all external  $V_{DD}$ ,  $TV_{DD}$ ,  $BV_{DD}$ ,  $OV_{DD}$ ,  $OV_{DD}$ ,  $OV_{DD}$ ,  $OV_{DD}$ ,  $OV_{DD}$ , and  $OV_{DD}$ ,  $OV_{DD}$

# 22.6 Pull-Up and Pull-Down Resistor Requirements

The device requires weak pull-up resistors (2–10 k $\Omega$  is recommended) on open drain type pins including I<sup>2</sup>C pins and PIC (interrupt) pins.

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 63. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions as most have asynchronous behavior and spurious assertion gives unpredictable results.

The following pins must not be pulled down during power-on reset: TSEC3\_TXD[3], HRESET\_REQ, TRIG\_OUT/READY/QUIESCE, MSRCID[2:4], ASLEEP. The DMA\_DACK[0:1], and TEST\_SEL/TEST\_SEL pins must be set to a proper state during POR configuration. See the pinlist table of the individual device for more details

See the PCI 2.2 specification for all pull ups required for PCI.

# 22.7 Output Buffer DC Impedance

The device drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ).

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $OV_{DD}$  or GND. Then, the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 61). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open) and  $R_P$  is trimmed until the voltage at the pad equals  $OV_{DD}/2$ .  $R_P$  then becomes the resistance of the pull-up devices.  $R_P$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_P + R_N)/2$ .

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

# 24 Document Revision History

The following table provides a revision history for this hardware specification.

**Table 88. Document Revision History**