#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

∃•XF

| Product Status                  | Obsolete                                                    |

|---------------------------------|-------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                              |

| Speed                           | 1.0GHz                                                      |

| Co-Processors/DSP               | Signal Processing; SPE, Security; SEC                       |

| RAM Controllers                 | DDR, DDR2, SDRAM                                            |

| Graphics Acceleration           | No                                                          |

| Display & Interface Controllers | -                                                           |

| Ethernet                        | 10/100/1000Mbps (4)                                         |

| SATA                            | -                                                           |

| USB                             | -                                                           |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                            |

| Operating Temperature           | 0°C ~ 105°C (TA)                                            |

| Security Features               | Cryptography, Random Number Generator                       |

| Package / Case                  | 783-BBGA, FCBGA                                             |

| Supplier Device Package         | 783-FCPBGA (29x29)                                          |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8548epxaqgd |

|                                 |                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the device. This device is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

# 2.1 **Overall DC Electrical Characteristics**

This section covers the ratings, conditions, and other characteristics.

# 2.1.1 Absolute Maximum Ratings

The following table provides the absolute maximum ratings.

| 1 |

|---|

|   |

| Characteristic                                                                                                         |                                                                                                                       | Symbol                                      | Max Value                                                            | Unit | Notes |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------|------|-------|

| Core supply v                                                                                                          | oltage                                                                                                                | V <sub>DD</sub>                             | -0.3 to 1.21                                                         | V    | _     |

| PLL supply voltage                                                                                                     |                                                                                                                       | AV <sub>DD</sub>                            | -0.3 to 1.21                                                         | V    | _     |

| Core power supply for SerDes transceivers                                                                              |                                                                                                                       | SV <sub>DD</sub>                            | -0.3 to 1.21                                                         | V    | _     |

| Pad power supply for SerDes transceivers                                                                               |                                                                                                                       | XV <sub>DD</sub>                            | -0.3 to 1.21                                                         | V    | —     |

| DDR and DDR2 DRAM I/O voltage                                                                                          |                                                                                                                       | GV <sub>DD</sub>                            | -0.3 to 2.75<br>-0.3 to 1.98                                         | V    | 2     |

| Three-speed Ethernet I/O voltage                                                                                       |                                                                                                                       | LV <sub>DD</sub> (for eTSEC1<br>and eTSEC2) | -0.3 to 3.63<br>-0.3 to 2.75                                         | V    |       |

|                                                                                                                        |                                                                                                                       | TV <sub>DD</sub> (for eTSEC3<br>and eTSEC4) | -0.3 to 3.63<br>-0.3 to 2.75                                         |      | 3     |

| PCI/PCI-X, DUART, system control and power management, I <sup>2</sup> C, Ethernet MII management, and JTAG I/O voltage |                                                                                                                       | OV <sub>DD</sub>                            | -0.3 to 3.63                                                         | V    |       |

| Local bus I/O                                                                                                          | voltage                                                                                                               | BV <sub>DD</sub>                            | -0.3 to 3.63<br>-0.3 to 2.75                                         | V    | —     |

| Input voltage                                                                                                          | DDR/DDR2 DRAM signals                                                                                                 | MV <sub>IN</sub>                            | –0.3 to (GV <sub>DD</sub> + 0.3)                                     | V    | 4     |

|                                                                                                                        | DDR/DDR2 DRAM reference                                                                                               | MV <sub>REF</sub>                           | -0.3 to<br>(GV <sub>DD</sub> /2 + 0.3)                               | V    | _     |

|                                                                                                                        | Three-speed Ethernet I/O signals                                                                                      | LV <sub>IN</sub><br>TV <sub>IN</sub>        | -0.3 to (LV <sub>DD</sub> + 0.3)<br>-0.3 to (TV <sub>DD</sub> + 0.3) | V    | 4     |

|                                                                                                                        | Local bus signals                                                                                                     | BV <sub>IN</sub>                            | -0.3 to (BV <sub>DD</sub> + 0.3)                                     | _    | —     |

|                                                                                                                        | DUART, SYSCLK, system control and power<br>management, I <sup>2</sup> C, Ethernet MII management,<br>and JTAG signals | OV <sub>IN</sub>                            | -0.3 to (OV <sub>DD</sub> + 0.3)                                     | V    | 4     |

|                                                                                                                        | PCI/PCI-X                                                                                                             | OV <sub>IN</sub>                            | -0.3 to (OV <sub>DD</sub> + 0.3)                                     | V    | 4     |

| Characteristic            | Symbol           | Max Value  | Unit | Notes |

|---------------------------|------------------|------------|------|-------|

| Storage temperature range | T <sub>STG</sub> | -55 to 150 | °C   | _     |

### Table 1. Absolute Maximum Ratings <sup>1</sup> (continued)

Notes:

- 1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- 2. The -0.3 to 2.75 V range is for DDR and -0.3 to 1.98 V range is for DDR2.

- 3. The 3.63 V maximum is only supported when the port is configured in GMII, MII, RMII, or TBI modes; otherwise the 2.75 V maximum applies. See Section 8.2, "FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications," for details on the recommended operating conditions per protocol.

- 4. (M,L,O)V<sub>IN</sub> may overshoot/undershoot to a voltage and for a maximum duration as shown in Figure 2.

## 2.1.2 Recommended Operating Conditions

The following table provides the recommended operating conditions for this device. Note that the values in this table are the recommended and tested operating conditions. Proper device operation outside these conditions is not guaranteed.

|                                          | Characteristic                                                                                                       | Symbol                               | Recommended<br>Value                               | Unit | Notes |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------------|------|-------|

| Core supply volta                        | age                                                                                                                  | V <sub>DD</sub>                      | 1.1 V ± 55 mV                                      | V    | —     |

| PLL supply voltage                       | ge                                                                                                                   | AV <sub>DD</sub>                     | 1.1 V ± 55 mV                                      | V    | 1     |

| Core power supp                          | ly for SerDes transceivers                                                                                           | SV <sub>DD</sub>                     | 1.1 V ± 55 mV                                      | V    | —     |

| Pad power supply for SerDes transceivers |                                                                                                                      | XV <sub>DD</sub>                     | 1.1 V ± 55 mV                                      | V    | —     |

| DDR and DDR2 DRAM I/O voltage            |                                                                                                                      | GV <sub>DD</sub>                     | 2.5 V ± 125 mV<br>1.8 V ± 90 mV                    | V    |       |

| Three-speed Eth                          | ernet I/O voltage                                                                                                    | LV <sub>DD</sub>                     | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   | V    | 4     |

|                                          |                                                                                                                      | TV <sub>DD</sub>                     | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   | _    | 4     |

|                                          | RT, system control and power management, I <sup>2</sup> C, nagement, and JTAG I/O voltage                            | OV <sub>DD</sub>                     | 3.3 V ± 165 mV                                     | V    | 3     |

| Local bus I/O vol                        | tage                                                                                                                 | BV <sub>DD</sub>                     | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                   | V    |       |

| Input voltage                            | DDR and DDR2 DRAM signals                                                                                            | MV <sub>IN</sub>                     | GND to GV <sub>DD</sub>                            | V    | 2     |

|                                          | DDR and DDR2 DRAM reference                                                                                          | MV <sub>REF</sub>                    | GND to GV <sub>DD</sub> /2                         | V    | 2     |

|                                          | Three-speed Ethernet signals                                                                                         | LV <sub>IN</sub><br>TV <sub>IN</sub> | GND to LV <sub>DD</sub><br>GND to TV <sub>DD</sub> | V    | 4     |

|                                          | Local bus signals                                                                                                    | BV <sub>IN</sub>                     | GND to BV <sub>DD</sub>                            | V    | —     |

|                                          | PCI, DUART, SYSCLK, system control and power management, I <sup>2</sup> C, Ethernet MII management, and JTAG signals | OV <sub>IN</sub>                     | GND to OV <sub>DD</sub>                            | V    | 3     |

**Table 2. Recommended Operating Conditions**

# 6 DDR and DDR2 SDRAM

This section describes the DC and AC electrical specifications for the DDR SDRAM interface of the device. Note that  $GV_{DD}(typ) = 2.5 \text{ V}$  for DDR SDRAM, and  $GV_{DD}(typ) = 1.8 \text{ V}$  for DDR2 SDRAM.

# 6.1 DDR SDRAM DC Electrical Characteristics

The following table provides the recommended operating conditions for the DDR2 SDRAM controller of the device when  $GV_{DD}(typ) = 1.8 \text{ V}.$

| Parameter/Condition                              | Symbol            | Min                       | Мах                       | Unit | Notes |

|--------------------------------------------------|-------------------|---------------------------|---------------------------|------|-------|

| I/O supply voltage                               | GV <sub>DD</sub>  | 1.71                      | 1.89                      | V    | 1     |

| I/O reference voltage                            | MV <sub>REF</sub> | $0.49 \times GV_{DD}$     | $0.51 \times GV_{DD}$     | V    | 2     |

| I/O termination voltage                          | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04  | MV <sub>REF</sub> + 0.04  | V    | 3     |

| Input high voltage                               | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.125 | GV <sub>DD</sub> + 0.3    | V    | —     |

| Input low voltage                                | V <sub>IL</sub>   | -0.3                      | MV <sub>REF</sub> – 0.125 | V    | —     |

| Output leakage current                           | I <sub>OZ</sub>   | -50                       | 50                        | μA   | 4     |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>OH</sub>   | -13.4                     | —                         | mA   | _     |

| Output low current (V <sub>OUT</sub> = 0.280 V)  | I <sub>OL</sub>   | 13.4                      | —                         | mA   |       |

Table 11. DDR2 SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V

### Notes:

1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $V_{DD}$  at all times.

2.  $MV_{REF}$  is expected to be equal to 0.5 ×  $GV_{DD}$ , and to track  $GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}$  may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail must track variations in the DC level of MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled,  $0 V \le V_{OUT} \le GV_{DD}$ .

This table provides the DDR2 I/O capacitance when  $GV_{DD}(typ) = 1.8$  V.

### Table 12. DDR2 SDRAM Capacitance for GV<sub>DD</sub>(typ)=1.8 V

| Parameter/Condition                          | Symbol           | Min | Мах | Unit | Notes |

|----------------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS, DQS | C <sub>DIO</sub> |     | 0.5 | pF   | 1     |

Note:

1. This parameter is sampled.  $GV_{DD} = 1.8 \text{ V} \pm 0.090 \text{ V}$ , f = 1 MHz, T<sub>A</sub> = 25°C,  $V_{OUT} = GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

Table 13 provides the recommended operating conditions for the DDR SDRAM controller when  $GV_{DD}(typ) = 2.5 \text{ V}.$

| Parameter/Condition                             | Symbol            | Min                      | Max                      | Unit | Notes |

|-------------------------------------------------|-------------------|--------------------------|--------------------------|------|-------|

| I/O supply voltage                              | GV <sub>DD</sub>  | 2.375                    | 2.625                    | V    | 1     |

| I/O reference voltage                           | MV <sub>REF</sub> | $0.49 \times GV_{DD}$    | $0.51 	imes GV_{DD}$     | V    | 2     |

| I/O termination voltage                         | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04 | MV <sub>REF</sub> + 0.04 | V    | 3     |

| Input high voltage                              | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.15 | GV <sub>DD</sub> + 0.3   | V    | —     |

| Input low voltage                               | V <sub>IL</sub>   | -0.3                     | MV <sub>REF</sub> – 0.15 | V    | —     |

| Output leakage current                          | I <sub>OZ</sub>   | -50                      | 50                       | μΑ   | 4     |

| Output high current (V <sub>OUT</sub> = 1.95 V) | I <sub>OH</sub>   | -16.2                    | —                        | mA   | —     |

| Output low current (V <sub>OUT</sub> = 0.35 V)  | I <sub>OL</sub>   | 16.2                     | —                        | mA   | —     |

| Table 13. DDR SDRAM DC Electrical | Characteristics for GV <sub>DD</sub> (typ) = 2.5 V |

|-----------------------------------|----------------------------------------------------|

|                                   |                                                    |

#### Notes:

1.  ${\rm GV}_{\rm DD}$  is expected to be within 50 mV of the DRAM  ${\rm V}_{\rm DD}$  at all times.

2. MV<sub>REF</sub> is expected to be equal to 0.5 × GV<sub>DD</sub>, and to track GV<sub>DD</sub> DC variations as measured at the receiver. Peak-to-peak noise on MV<sub>REF</sub> may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail must track variations in the DC level of MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  GV<sub>DD</sub>.

Table 14 provides the DDR I/O capacitance when  $GV_{DD}(typ) = 2.5$  V.

### Table 14. DDR SDRAM Capacitance for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition                     | Symbol           | Min | Max | Unit | Notes |

|-----------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS | C <sub>DIO</sub> |     | 0.5 | pF   | 1     |

#### Note:

1. This parameter is sampled.  $GV_{DD} = 2.5 \text{ V} \pm 0.125 \text{ V}$ , f = 1 MHz, T<sub>A</sub> = 25°C,  $V_{OUT} = GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

This table provides the current draw characteristics for MV<sub>REF</sub>.

### Table 15. Current Draw Characteristics for MV<sub>REF</sub>

| Parameter/Condition                | Symbol             | Min | Max | Unit | Notes |

|------------------------------------|--------------------|-----|-----|------|-------|

| Current draw for MV <sub>REF</sub> | I <sub>MVREF</sub> |     | 500 | μA   | 1     |

#### Note:

1. The voltage regulator for  $MV_{REF}$  must be able to supply up to 500  $\mu$ A current.

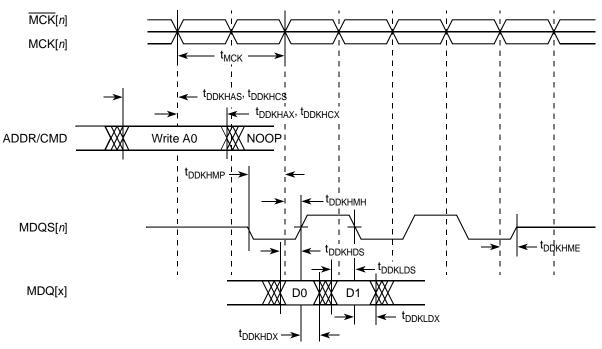

Figure 4 shows the DDR SDRAM output timing diagram.+

Figure 4. DDR SDRAM Output Timing Diagram

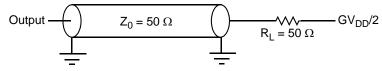

Figure 5 provides the AC test load for the DDR bus.

Figure 5. DDR AC Test Load

#### Enhanced Three-Speed Ethernet (eTSEC)

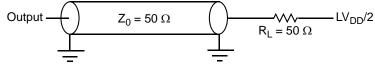

Figure 19 provides the AC test load for eTSEC.

Figure 19. eTSEC AC Test Load

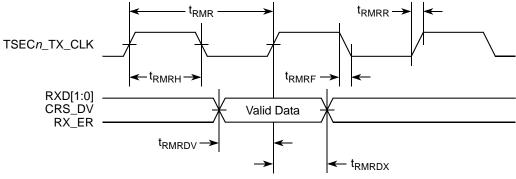

Figure 20 shows the RMII receive AC timing diagram.

Figure 20. RMII Receive AC Timing Diagram

### Table 53. PCI-X AC Timing Specifications at 66 MHz (continued)

| Parameter                                        | Symbol              | Min | Max | Unit | Notes |

|--------------------------------------------------|---------------------|-----|-----|------|-------|

| HRESET to PCI-X initialization pattern hold time | t <sub>PCRHIX</sub> | 0   | 50  | ns   | 6, 11 |

Notes:

- 1. See the timing measurement conditions in the PCI-X 1.0a Specification.

- 2. Minimum times are measured at the package pin (not the test point). Maximum times are measured with the test point and load circuit.

- 3. Setup time for point-to-point signals applies to REQ and GNT only. All other signals are bused.

- 4. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 5. Setup time applies only when the device is not driving the pin. Devices cannot drive and receive signals at the same time.

- 6. Maximum value is also limited by delay to the first transaction (time for HRESET high to first configuration access, t<sub>PCRHFV</sub>). The PCI-X initialization pattern control signals after the rising edge of HRESET must be negated no later than two clocks before the first FRAME and must be floated no later than one clock before FRAME is asserted.

- 7. A PCI-X device is permitted to have the minimum values shown for t<sub>PCKHOV</sub> and t<sub>CYC</sub> only in PCI-X mode. In conventional mode, the device must meet the requirements specified in PCI 2.2 for the appropriate clock frequency.

- 8. Device must meet this specification independent of how many outputs switch simultaneously.

9. The timing parameter t<sub>PCRHFV</sub> is a minimum of 10 clocks rather than the minimum of 5 clocks in the PCI-X 1.0a Specification.

10.Guaranteed by characterization.

11.Guaranteed by design.

This table provides the PCI-X AC timing specifications at 133 MHz. Note that the maximum PCI-X frequency in synchronous mode is 110 MHz.

| Parameter                                         | Symbol              | Min | Max | Unit   | Notes         |

|---------------------------------------------------|---------------------|-----|-----|--------|---------------|

| SYSCLK to signal valid delay                      | <sup>t</sup> PCKHOV | _   | 3.8 | ns     | 1, 2, 3, 7, 8 |

| Output hold from SYSCLK                           | t <sub>PCKHOX</sub> | 0.7 | _   | ns     | 1, 11         |

| SYSCLK to output high impedance                   | t <sub>PCKHOZ</sub> |     | 7   | ns     | 1, 4, 8, 12   |

| Input setup time to SYSCLK                        | t <sub>PCIVKH</sub> | 1.2 | _   | ns     | 3, 5, 9, 11   |

| Input hold time from SYSCLK                       | t <sub>PCIXKH</sub> | 0.5 | -   | ns     | 11            |

| REQ64 to HRESET setup time                        | t <sub>PCRVRH</sub> | 10  | _   | clocks | 12            |

| HRESET to REQ64 hold time                         | t <sub>PCRHRX</sub> | 0   | 50  | ns     | 12            |

| HRESET high to first FRAME assertion              | t <sub>PCRHFV</sub> | 10  | _   | clocks | 10, 12        |

| PCI-X initialization pattern to HRESET setup time | <sup>t</sup> PCIVRH | 10  |     | clocks | 12            |

#### Table 54. PCI-X AC Timing Specifications at 133 MHz

#### PCI/PCI-X

### Table 54. PCI-X AC Timing Specifications at 133 MHz (continued)

| Parameter                                        | Symbol              | Min | Max | Unit | Notes |

|--------------------------------------------------|---------------------|-----|-----|------|-------|

| HRESET to PCI-X initialization pattern hold time | t <sub>PCRHIX</sub> | 0   | 50  | ns   | 6, 12 |

Notes:

1. See the timing measurement conditions in the PCI-X 1.0a Specification.

- 2. Minimum times are measured at the package pin (not the test point). Maximum times are measured with the test point and load circuit.

- 3. Setup time for point-to-point signals applies to REQ and GNT only. All other signals are bused.

- 4. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 5. Setup time applies only when the device is not driving the pin. Devices cannot drive and receive signals at the same time.

- 6. Maximum value is also limited by delay to the first transaction (time for HRESET high to first configuration access, t<sub>PCRHFV</sub>). The PCI-X initialization pattern control signals after the rising edge of HRESET must be negated no later than two clocks before the first FRAME and must be floated no later than one clock before FRAME is asserted.

- 7. A PCI-X device is permitted to have the minimum values shown for t<sub>PCKHOV</sub> and t<sub>CYC</sub> only in PCI-X mode. In conventional mode, the device must meet the requirements specified in PCI 2.2 for the appropriate clock frequency.

8. Device must meet this specification independent of how many outputs switch simultaneously.

9. The timing parameter t<sub>PCIVKH</sub> is a minimum of 1.4 ns rather than the minimum of 1.2 ns in the PCI-X 1.0a Specification.

- 10. The timing parameter t<sub>PCRHFV</sub> is a minimum of 10 clocks rather than the minimum of 5 clocks in the *PCI-X 1.0a Specification.*

- 11. Guaranteed by characterization.

12. Guaranteed by design.

# 17 PCI Express

This section describes the DC and AC electrical specifications for the PCI Express bus of the MPC8548E.

# 17.1 <u>DC Requirements</u> for PCI Express SD\_REF\_CLK and SD\_REF\_CLK

For more information, see Section 16.2, "SerDes Reference Clocks."

# **17.2 AC Requirements for PCI Express SerDes Clocks**

Table 55 lists the AC requirements for the PCI Express SerDes clocks.

| Table 55. SD_I | REF_CLK and SD | D_REF_CLK AC Re | quirements |

|----------------|----------------|-----------------|------------|

|----------------|----------------|-----------------|------------|

| Symbol             | Parameter Description                                                                     | Min | Тур | Max | Unit | Notes |

|--------------------|-------------------------------------------------------------------------------------------|-----|-----|-----|------|-------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                         |     | 10  | —   | ns   | 1     |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles. | _   | —   | 100 | ps   | —     |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location.              | -50 |     | 50  | ps   | —     |

Note:

1. Typical based on PCI Express Specification 2.0.

# 17.3 Clocking Dependencies

The ports on the two ends of a link must transmit data at a rate that is within 600 parts per million (ppm) of each other at all times. This is specified to allow bit rate clock sources with a  $\pm$ 300 ppm tolerance.

# 17.4 Physical Layer Specifications

The following is a summary of the specifications for the physical layer of PCI Express on this device. For further details as well as the specifications of the transport and data link layer see *PCI Express Base Specification. Rev. 1.0a.*

# 17.4.1 Differential Transmitter (TX) Output

Table 56 defines the specifications for the differential output at all transmitters (TXs). The parameters are specified at the component pins.

#### **PCI Express**

Figure 48. Minimum Transmitter Timing and Voltage Output Compliance Specifications

# 17.4.3 Differential Receiver (RX) Input Specifications

Table 57 defines the specifications for the differential input at all receivers (RXs). The parameters are specified at the component pins.

| Symbol                                       | Parameter                                                                                   | Min    | Nom | Max    | Unit | Comments                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------|---------------------------------------------------------------------------------------------|--------|-----|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI                                           | Unit interval                                                                               | 399.88 | 400 | 400.12 | ps   | Each UI is 400 ps $\pm$ 300 ppm. UI does not account<br>for spread spectrum clock dictated variations.<br>See Note 1.                                                                                                                                                                                                                                                                        |

| V <sub>RX-DIFFp-p</sub>                      | Differential<br>peak-to-peak<br>input voltage                                               | 0.175  | —   | 1.200  | V    | $V_{RX-DIFFp-p} = 2 \times  V_{RX-D+} - V_{RX-D-} $ . See Note 2.                                                                                                                                                                                                                                                                                                                            |

| T <sub>RX-EYE</sub>                          | Minimum<br>receiver eye<br>width                                                            | 0.4    | _   | _      | UI   | The maximum interconnect media and transmitter jitter that can be tolerated by the receiver can be derived as $T_{RX-MAX-JITTER} = 1 - T_{RX-EYE} = 0.6$ UI. See Notes 2 and 3.                                                                                                                                                                                                              |

| T <sub>RX-EYE-MEDIAN-to-</sub><br>MAX-JITTER | Maximum time<br>between the<br>jitter median and<br>maximum<br>deviation from<br>the median | —      |     | 0.3    | UI   | Jitter is defined as the measurement variation of<br>the crossing points ( $V_{RX-DIFFp-p} = 0$ V) in relation<br>to a recovered TX UI. A recovered TX UI is<br>calculated over 3500 consecutive unit intervals of<br>sample data. Jitter is measured using all edges of<br>the 250 consecutive UI in the center of the<br>3500 UI used for calculating the TX UI.<br>See Notes 2, 3, and 7. |

Table 57. Differential Receiver (RX) Input Specifications

# **19.3 Pinout Listings**

### NOTE

The DMA\_DACK[0:1] and TEST\_SEL/TEST\_SEL pins must be set to a proper state during POR configuration. See the pinlist table of the individual device for more details.

For MPC8548/47/45, GPIOs are still available on PCI1\_AD[63:32]/PC2\_AD[31:0] pins if they are not used for PCI functionality.

For MPC8545/43, eTSEC does not support 16 bit FIFO mode.

Table 71 provides the pinout listing for the MPC8548E 783 FC-PBGA package.

| Signal                        | Package Pin Number                                                                                                                                                                                     | Pin Type | Power<br>Supply  | Notes    |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

|                               | PCI1 and PCI2 (One 64-Bit or Two 32-Bit)                                                                                                                                                               |          |                  |          |

| PCI1_AD[63:32]/PCI2_AD[31:0]  | AB14, AC15, AA15, Y16, W16, AB16, AC16,<br>AA16, AE17, AA18, W18, AC17, AD16, AE16,<br>Y17, AC18, AB18, AA19, AB19, AB21, AA20,<br>AC20, AB20, AB22, AC22, AD21, AB23, AF23,<br>AD23, AE23, AC23, AC24 | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_AD[31:0]                 | AH6, AE7, AF7, AG7, AH7, AF8, AH8, AE9,<br>AH9, AC10, AB10, AD10, AG10, AA10, AH10,<br>AA11, AB12, AE12, AG12, AH12, AB13, AA12,<br>AC13, AE13, Y14, W13, AG13, V14, AH13,<br>AC14, Y15, AB15          | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_C_BE[7:4]/PCI2_C_BE[3:0] | AF15, AD14, AE15, AD15                                                                                                                                                                                 | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_C_BE[3:0]                | AF9, AD11, Y12, Y13                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_PAR64/PCI2_PAR           | W15                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> |          |

| PCI1_GNT[4:1]                 | AG6, AE6, AF5, AH5                                                                                                                                                                                     | 0        | OV <sub>DD</sub> | 5, 9, 35 |

| PCI1_GNT0                     | AG5                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | —        |

| PCI1_IRDY                     | AF11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_PAR                      | AD12                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | —        |

| PCI1_PERR                     | AC12                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_SERR                     | V13                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2, 4     |

| PCI1_STOP                     | W12                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_TRDY                     | AG11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |

### Table 71. MPC8548E Pinout Listing

Package Description

| Signal             | Package Pin Number                                | Pin Type | Power<br>Supply  | Notes        |

|--------------------|---------------------------------------------------|----------|------------------|--------------|

| LSYNC_IN           | F27                                               | I        | BV <sub>DD</sub> | _            |

| LSYNC_OUT          | F28                                               | 0        | BV <sub>DD</sub> | —            |

|                    | DMA                                               |          |                  | 1            |

| DMA_DACK[0:1]      | AD3, AE1                                          | 0        | OV <sub>DD</sub> | 5, 9,<br>102 |

| DMA_DREQ[0:1]      | AD4, AE2                                          | I        | OV <sub>DD</sub> | _            |

| DMA_DDONE[0:1]     | AD2, AD1                                          | 0        | OV <sub>DD</sub> | —            |

|                    | Programmable Interrupt Controller                 |          | •                |              |

| UDE                | AH16                                              | I        | OV <sub>DD</sub> | —            |

| MCP                | AG19                                              | I        | OV <sub>DD</sub> | —            |

| IRQ[0:7]           | AG23, AF18, AE18, AF20, AG18, AF17, AH24, AE20    | I        | OV <sub>DD</sub> | -            |

| IRQ[8]             | AF19                                              | I        | OV <sub>DD</sub> | —            |

| IRQ[9]/DMA_DREQ3   | AF21                                              | I        | OV <sub>DD</sub> | 1            |

| IRQ[10]/DMA_DACK3  | AE19                                              | I/O      | OV <sub>DD</sub> | 1            |

| IRQ[11]/DMA_DDONE3 | AD20                                              | I/O      | OV <sub>DD</sub> | 1            |

| IRQ_OUT            | AD18                                              | 0        | OV <sub>DD</sub> | 2, 4         |

|                    | Ethernet Management Interface                     |          | •                |              |

| EC_MDC             | AB9                                               | 0        | OV <sub>DD</sub> | 5, 9         |

| EC_MDIO            | AC8                                               | I/O      | OV <sub>DD</sub> | —            |

|                    | Gigabit Reference Clock                           |          |                  | 1            |

| EC_GTX_CLK125      | V11                                               | I        | LV <sub>DD</sub> | _            |

|                    | Three-Speed Ethernet Controller (Gigabit Ethernet | et 1)    |                  | 1            |

| TSEC1_RXD[7:0]     | R5, U1, R3, U2, V3, V1, T3, T2                    | I        | LV <sub>DD</sub> | _            |

| TSEC1_TXD[7:0]     | T10, V7, U10, U5, U4, V6, T5, T8                  | 0        | LV <sub>DD</sub> | 5, 9         |

| TSEC1_COL          | R4                                                | I        | LV <sub>DD</sub> | _            |

| TSEC1_CRS          | V5                                                | I/O      | LV <sub>DD</sub> | 20           |

| TSEC1_GTX_CLK      | U7                                                | 0        | LV <sub>DD</sub> |              |

| TSEC1_RX_CLK       | U3                                                | I        | LV <sub>DD</sub> | —            |

| TSEC1_RX_DV        | V2                                                | I        | LV <sub>DD</sub> | _            |

| TSEC1_RX_ER        | T1                                                | I        | LV <sub>DD</sub> | _            |

| TSEC1_TX_CLK       | Т6                                                | I        | LV <sub>DD</sub> | —            |

| TSEC1_TX_EN        | U9                                                | 0        | LV <sub>DD</sub> | 30           |

| TSEC1_TX_ER        | Т7                                                | 0        | LV <sub>DD</sub> | <u> </u>     |

| Signal           | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin Type                                           | Power<br>Supply  | Notes        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------|--------------|

|                  | Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                    |                  | 1            |

| RTC              | AF16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | —            |

| SYSCLK           | AH17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | —            |

|                  | JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                    |                  | 1            |

| ТСК              | AG28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | —            |

| TDI              | AH28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 12           |

| TDO              | AF28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                  | OV <sub>DD</sub> | _            |

| TMS              | AH27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 12           |

| TRST             | AH23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 12           |

|                  | DFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                    |                  |              |

| L1_TSTCLK        | AC25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 25           |

| L2_TSTCLK        | AE22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 25           |

| LSSD_MODE        | AH20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 25           |

| TEST_SEL         | AH14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 25           |

|                  | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                    |                  |              |

| THERM0           | AG1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                  | _                | 14           |

| THERM1           | AH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                  |                  | 14           |

|                  | Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                    |                  |              |

| ASLEEP           | AH18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                  | OV <sub>DD</sub> | 9, 19,<br>29 |

|                  | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                    |                  | •            |

| GND              | <ul> <li>A11, B7, B24, C1, C3, C5, C12, C15, C26, D8,<br/>D11, D16, D20, D22, E1, E5, E9, E12, E15, E17,<br/>F4, F26, G12, G15, G18, G21, G24, H2, H6, H8,<br/>H28, J4, J12, J15, J17, J27, K7, K9, K11, K27,<br/>L3, L5, L12, L16, N11, N13, N15, N17, N19, P4,<br/>P9, P12, P14, P16, P18, R11, R13, R15, R17,<br/>R19, T4, T12, T14, T16, T18, U8, U11, U13,<br/>U15, U17, U19, V4, V12, V18, W6, W19, Y4, Y9,<br/>Y11, Y19, AA6, AA14, AA17, AA22, AA23, AB4,<br/>AC2, AC11, AC19, AC26, AD5, AD9, AD22,<br/>AE3, AE14, AF6, AF10, AF13, AG8, AG27,<br/>K28, L24, L26, N24, N27, P25, R28, T24, T26,<br/>U24, V25, W28, Y24, Y26, AA24, AA27, AB25,<br/>AC28, L21, L23, N22, P20, R23, T21, U22, V20,<br/>W23, Y21, U27</li> </ul> | _                                                  |                  |              |

| OV <sub>DD</sub> | V16, W11, W14, Y18, AA13, AA21, AB11,<br>AB17, AB24, AC4, AC9, AC21, AD6, AD13,<br>AD17, AD19, AE10, AE8, AE24, AF4, AF12,<br>AF22, AF27, AG26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Power for PCI<br>and other<br>standards<br>(3.3 V) | OV <sub>DD</sub> | _            |

Package Description

| Signal           | Package Pin Number                                                                                                                                                | Pin Type                                                          | Power<br>Supply  | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------|-------|

| LV <sub>DD</sub> | N8, R7, T9, U6                                                                                                                                                    | Power for<br>TSEC1 and<br>TSEC2<br>(2.5 V, 3.3 V)                 | LV <sub>DD</sub> | _     |

| TV <sub>DD</sub> | W9, Y6                                                                                                                                                            | Power for<br>TSEC3 and<br>TSEC4<br>(2,5 V, 3.3 V)                 | TV <sub>DD</sub> | _     |

| GV <sub>DD</sub> | B3, B11, C7, C9, C14, C17, D4, D6, D10, D15,<br>E2, E8, E11, E18, F5, F12, F16, G3, G7, G9,<br>G11, H5, H12, H15, H17, J10, K3, K12, K16,<br>K18, L6, M4, M8, M13 | Power for<br>DDR1 and<br>DDR2 DRAM<br>I/O voltage<br>(1.8 V, 2.5) | GV <sub>DD</sub> |       |

| BV <sub>DD</sub> | C21, C24, C27, E20, E25, G19, G23, H26, J20                                                                                                                       | Power for local<br>bus (1.8 V,<br>2.5 V, 3.3 V)                   | BV <sub>DD</sub> |       |

| V <sub>DD</sub>  | M19, N12, N14, N16, N18, P11, P13, P15, P17,<br>P19, R12, R14, R16, R18, T11, T13, T15, T17,<br>T19, U12, U14, U16, U18, V17, V19                                 | Power for core<br>(1.1 V)                                         | V <sub>DD</sub>  |       |

| SV <sub>DD</sub> | L25, L27, M24, N28, P24, P26, R24, R27, T25,<br>V24, V26, W24, W27, Y25, AA28, AC27                                                                               | Core Power<br>for SerDes<br>transceivers<br>(1.1 V)               | SV <sub>DD</sub> | —     |

| XV <sub>DD</sub> | L20, L22, N23, P21, R22, T20, U23, V21, W22,<br>Y20                                                                                                               | Pad Power for<br>SerDes<br>transceivers<br>(1.1 V)                | XV <sub>DD</sub> |       |

| AVDD_LBIU        | J28                                                                                                                                                               | Power for local<br>bus PLL<br>(1.1 V)                             | _                | 26    |

| AVDD_PCI1        | AH21                                                                                                                                                              | Power for<br>PCI1 PLL<br>(1.1 V)                                  | _                | 26    |

| AVDD_PCI2        | AH22                                                                                                                                                              | Power for<br>PCI2 PLL<br>(1.1 V)                                  | _                | 26    |

| AVDD_CORE        | AH15                                                                                                                                                              | Power for<br>e500 PLL (1.1<br>V)                                  | _                | 26    |

| AVDD_PLAT        | AH19                                                                                                                                                              | Powerfor CCB<br>PLL (1.1 V)                                       | —                | 26    |

| AVDD_SRDS        | U25                                                                                                                                                               | Power for<br>SRDSPLL<br>(1.1 V)                                   | _                | 26    |

| SENSEVDD         | M14                                                                                                                                                               | 0                                                                 | V <sub>DD</sub>  | 13    |

### Table 71. MPC8548E Pinout Listing (continued)

| Signal         | Package Pin Number                       | Pin Type   | Power<br>Supply  | Notes    |

|----------------|------------------------------------------|------------|------------------|----------|

| FIFO1_RXC2     | P5                                       | I          | LV <sub>DD</sub> | 104      |

| Reserved       | R1                                       | —          | —                | 104      |

| Reserved       | P10                                      | —          | —                | 105      |

| FIFO1_TXC2     | P7                                       | 0          | LV <sub>DD</sub> | 15       |

| cfg_dram_type1 | R10                                      | I          | LV <sub>DD</sub> | 5        |

| Three          | ee-Speed Ethernet Controller (Gigabit Et | thernet 3) |                  |          |

| TSEC3_TXD[3:0] | V8, W10, Y10, W7                         | 0          | TV <sub>DD</sub> | 5, 9, 29 |

| TSEC3_RXD[3:0] | Y1, W3, W5, W4                           | I          | TV <sub>DD</sub> |          |

| TSEC3_GTX_CLK  | W8                                       | 0          | TV <sub>DD</sub> |          |

| TSEC3_RX_CLK   | W2                                       | I          | TV <sub>DD</sub> | —        |

| TSEC3_RX_DV    | W1                                       | I          | TV <sub>DD</sub> | _        |

| TSEC3_RX_ER    | Y2                                       | I          | TV <sub>DD</sub> | _        |

| TSEC3_TX_CLK   | V10                                      | I          | TV <sub>DD</sub> | _        |

| TSEC3_TX_EN    | V9                                       | 0          | TV <sub>DD</sub> | 30       |

| TSEC3_TXD[7:4] | AB8, Y7, AA7, Y8                         | 0          | TV <sub>DD</sub> | 5, 9, 29 |

| TSEC3_RXD[7:4] | AA1, Y3, AA2, AA4                        | I          | TV <sub>DD</sub> | _        |

| Reserved       | AA5                                      | —          | —                | 15       |

| TSEC3_COL      | Y5                                       | I          | TV <sub>DD</sub> | —        |

| TSEC3_CRS      | AA3                                      | I/O        | TV <sub>DD</sub> | 31       |

| TSEC3_TX_ER    | AB6                                      | 0          | TV <sub>DD</sub> | —        |

|                | DUART                                    |            | •                |          |

| UART_CTS[0:1]  | AB3, AC5                                 | I          | OV <sub>DD</sub> |          |

| UART_RTS[0:1]  | AC6, AD7                                 | 0          | OV <sub>DD</sub> |          |

| UART_SIN[0:1]  | AB5, AC7                                 | I          | OV <sub>DD</sub> |          |

| UART_SOUT[0:1] | AB7, AD8                                 | 0          | OV <sub>DD</sub> | _        |

| <b>!</b>       | I <sup>2</sup> C interface               |            |                  | 1        |

| IIC1_SCL       | AG22                                     | I/O        | OV <sub>DD</sub> | 4, 27    |

| IIC1_SDA       | AG21                                     | I/O        | OV <sub>DD</sub> | 4, 27    |

| IIC2_SCL       | AG15                                     | I/O        | OV <sub>DD</sub> | 4, 27    |

| IIC2_SDA       | AG14                                     | I/O        | OV <sub>DD</sub> | 4, 27    |

|                | SerDes                                   | 1          |                  |          |

| SD_RX[0:3]     | M28, N26, P28, R26                       | I          | XV <sub>DD</sub> |          |

| SD_RX[0:3]     | M27, N25, P27, R25                       | I          | XV <sub>DD</sub> | —        |

| SD_TX[0:3]     | M22, N20, P22, R20                       | 0          | XV <sub>DD</sub> |          |

Package Description

| Signal           | Package Pin Number                                                                                                                                                | Pin Type                                                            | Power<br>Supply  | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------|-------|

| GV <sub>DD</sub> | B3, B11, C7, C9, C14, C17, D4, D6, D10, D15,<br>E2, E8, E11, E18, F5, F12, F16, G3, G7, G9,<br>G11, H5, H12, H15, H17, J10, K3, K12, K16,<br>K18, L6, M4, M8, M13 | Power for<br>DDR1 and<br>DDR2 DRAM<br>I/O voltage<br>(1.8 V, 2.5 V) | GV <sub>DD</sub> | _     |

| BV <sub>DD</sub> | C21, C24, C27, E20, E25, G19, G23, H26, J20                                                                                                                       | Power for local<br>bus (1.8 V,<br>2.5 V, 3.3 V)                     | BV <sub>DD</sub> | _     |

| V <sub>DD</sub>  | M19, N12, N14, N16, N18, P11, P13, P15, P17,<br>P19, R12, R14, R16, R18, T11, T13, T15, T17,<br>T19, U12, U14, U16, U18, V17, V19                                 | Power for core<br>(1.1 V)                                           | V <sub>DD</sub>  | -     |

| SV <sub>DD</sub> | SV <sub>DD</sub> L25, L27, M24, N28, P24, P26, R24, R27, T25, Core power<br>V24, V26, W24, W27, Y25, AA28, AC27 SerDes<br>transceiver<br>(1.1 V)                  |                                                                     | SV <sub>DD</sub> | _     |

| XV <sub>DD</sub> | L20, L22, N23, P21, R22, T20, U23, V21, W22,<br>Y20                                                                                                               | Pad power for<br>SerDes<br>transceivers<br>(1.1 V)                  | XV <sub>DD</sub> | —     |

| AVDD_LBIU        | J28                                                                                                                                                               | Power for local<br>bus PLL<br>(1.1 V)                               | _                | 26    |

| AVDD_PCI1        | AH21                                                                                                                                                              | Power for<br>PCI1 PLL<br>(1.1 V)                                    | —                | 26    |

| AVDD_PCI2        | AH22                                                                                                                                                              | Power for<br>PCI2 PLL<br>(1.1 V)                                    | _                | 26    |

| AVDD_CORE        | VDD_CORE AH15                                                                                                                                                     |                                                                     | _                | 26    |

| AVDD_PLAT        | AVDD_PLAT AH19                                                                                                                                                    |                                                                     | —                | 26    |

| AVDD_SRDS        | AVDD_SRDS U25                                                                                                                                                     |                                                                     | _                | 26    |

| SENSEVDD         | M14                                                                                                                                                               | 0                                                                   | V <sub>DD</sub>  | 13    |

| SENSEVSS         | M16                                                                                                                                                               | —                                                                   | —                | 13    |

|                  | Analog Signals                                                                                                                                                    |                                                                     |                  | •     |

| MVREF            | A18                                                                                                                                                               | I<br>Reference<br>voltage signal<br>for DDR                         | MVREF            |       |

### Table 73. MPC8545E Pinout Listing (continued)

#### Package Description

| Signal        | Package Pin Number | Pin Type                                       | Power<br>Supply       | Notes |

|---------------|--------------------|------------------------------------------------|-----------------------|-------|

| SENSEVSS      | M16                | —                                              | —                     | 13    |

|               | Analog Signals     |                                                |                       |       |

| MVREF         | A18                | l<br>Reference<br>voltage<br>signal for<br>DDR | MVREF                 | _     |

| SD_IMP_CAL_RX | L28                | I                                              | 200 Ω (±1%)<br>to GND | —     |

| SD_IMP_CAL_TX | AB26               | I                                              | 100 Ω (±1%)<br>to GND | —     |

| SD_PLL_TPA    | U26                | 0                                              | AVDD_SRDS             | 24    |

### Table 74. MPC8543E Pinout Listing (continued)

**Note:** All note references in this table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

# 21 Thermal

This section describes the thermal specifications of the device.

# 21.1 Thermal for Version 2.0 Silicon HiCTE FC-CBGA with Full Lid

This section describes the thermal specifications for the HiCTE FC-CBGA package for revision 2.0 silicon.

This table shows the package thermal characteristics.

| Characteristic                               | JEDEC Board             | Symbol                               | Value | Unit | Notes |