# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 1.2GHz                                                                |

| Co-Processors/DSP               | Signal Processing; SPE                                                |

| RAM Controllers                 | DDR, DDR2, SDRAM                                                      |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers |                                                                       |

| Ethernet                        | 10/100/1000Mbps (4)                                                   |

| SATA                            |                                                                       |

| USB                             | · · · · · · · · · · · · · · · · · · ·                                 |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                      |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | · .                                                                   |

| Package / Case                  | 783-BBGA, FCBGA                                                       |

| Supplier Device Package         | 783-FCBGA (29x29)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8548pxatgb |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.3 eTSEC Gigabit Reference Clock Timing

The following table provides the eTSEC gigabit reference clocks (EC\_GTX\_CLK125) AC timing specifications for the device.

| Parameter/Condition                                                  | Symbol            | Min      | Тур | Max         | Unit | Notes |

|----------------------------------------------------------------------|-------------------|----------|-----|-------------|------|-------|

| EC_GTX_CLK125 frequency                                              | f <sub>G125</sub> | _        | 125 | —           | MHz  | _     |

| EC_GTX_CLK125 cycle time                                             | t <sub>G125</sub> | —        | 8   | —           | ns   |       |

| EC_GTX_CLK125 rise and fall time<br>L/TVDD = 2.5 V<br>L/TVDD = 3.3 V |                   | —        | _   | 0.75<br>1.0 | ns   | 1     |

| EC_GTX_CLK125 duty cycle<br>GMII, TBI<br>1000Base-T for RGMII, RTBI  |                   | 45<br>47 | _   | 55<br>53    | %    | 2, 3  |

| Table 6. EC_ | GTX_CLK125 AC Tim | ning Specifications |

|--------------|-------------------|---------------------|

|--------------|-------------------|---------------------|

Notes:

1. Rise and fall times for EC\_GTX\_CLK125 are measured from 0.5 and 2.0 V for L/TV<sub>DD</sub> = 2.5 V, and from 0.6 and 2.7 V for L/TV<sub>DD</sub> = 3.3 V.

- 2. Timing is guaranteed by design and characterization.

- 3. EC\_GTX\_CLK125 is used to generate the GTX clock TSEC*n*\_GTX\_CLK for the eTSEC transmitter with 2% degradation. EC\_GTX\_CLK125 duty cycle can be loosened from 47/53% as long as the PHY device can tolerate the duty cycle generated by the TSEC*n*\_GTX\_CLK. See Section 8.2.6, "RGMII and RTBI AC Timing Specifications," for duty cycle for 10Base-T and 100Base-T reference clock.

# 4.4 PCI/PCI-X Reference Clock Timing

When the PCI/PCI-X controller is configured for asynchronous operation, the reference clock for the PCI/PCI-x controller is not the SYSCLK input, but instead the PCIn\_CLK. The following table provides the PCI/PCI-X reference clock AC timing specifications for the device.

| Table 7. PCIn_CLK AC Timing Specifications | Table 7. PCI <i>n</i> | CLK | AC Timing | Specifications |

|--------------------------------------------|-----------------------|-----|-----------|----------------|

|--------------------------------------------|-----------------------|-----|-----------|----------------|

At recommended operating conditions (see Table 2) with  $OV_{DD} = 3.3 \text{ V} \pm 165 \text{ mV}$ .

| Parameter/Condition         | Symbol                                    | Min | Тур | Мах | Unit | Notes |

|-----------------------------|-------------------------------------------|-----|-----|-----|------|-------|

| PCIn_CLK frequency          | f <sub>PCICLK</sub>                       | 16  | —   | 133 | MHz  | —     |

| PCIn_CLK cycle time         | t <sub>PCICLK</sub>                       | 7.5 | —   | 60  | ns   | —     |

| PCIn_CLK rise and fall time | t <sub>PCIKH</sub> , t <sub>PCIKL</sub>   | 0.6 | 1.0 | 2.1 | ns   | 1, 2  |

| PCIn_CLK duty cycle         | t <sub>PCIKHKL</sub> /t <sub>PCICLK</sub> | 40  | —   | 60  | %    | 2     |

Notes:

1. Rise and fall times for SYSCLK are measured at 0.6 and 2.7 V.

2. Timing is guaranteed by design and characterization.

# 4.5 Platform to FIFO Restrictions

Note the following FIFO maximum speed restrictions based on platform speed.

For FIFO GMII mode:

FIFO TX/RX clock frequency ≤ platform clock frequency/4.2

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency must be no more than 127 MHz.

For FIFO encoded mode:

FIFO TX/RX clock frequency  $\leq$  platform clock frequency/4.2

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency must be no more than 167 MHz.

## 4.6 Platform Frequency Requirements for PCI-Express and Serial RapidIO

The CCB clock frequency must be considered for proper operation of the high-speed PCI-Express and Serial RapidIO interfaces as described below.

For proper PCI Express operation, the CCB clock frequency must be greater than:

See *MPC8548ERM*, *Rev.* 2, *PowerQUICC III Integrated Processor Family Reference Manual*, Section 18.1.3.2, "Link Width," for PCI Express interface width details.

For proper serial RapidIO operation, the CCB clock frequency must be greater than:

$2 \times (0.80) \times (Serial RapidIO interface frequency) \times (Serial RapidIO link width)$

64

See *MPC8548ERM*, *Rev.* 2, *PowerQUICC III Integrated Processor Family Reference Manual*, Section 17.4, "1x/4x LP-Serial Signal Descriptions," for serial RapidIO interface width and frequency details.

# 4.7 Other Input Clocks

For information on the input clocks of other functional blocks of the platform see the specific section of this document.

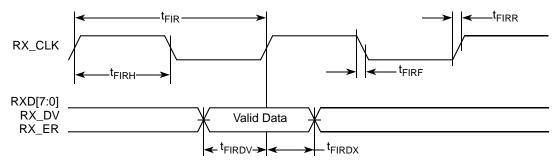

Figure 7. FIFO Receive AC Timing Diagram

## 8.2.2 GMII AC Timing Specifications

This section describes the GMII transmit and receive AC timing specifications.

## 8.2.2.1 GMII Transmit AC Timing Specifications

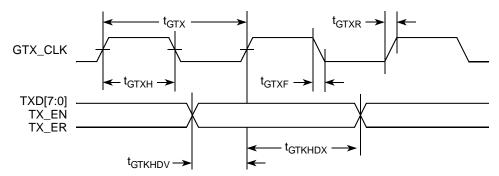

This table provides the GMII transmit AC timing specifications.

| Table 26. GMII Transmit AC Timing Specifications | Table 26 | <b>GMII</b> Transm | it AC Timing | Specifications |

|--------------------------------------------------|----------|--------------------|--------------|----------------|

|--------------------------------------------------|----------|--------------------|--------------|----------------|

| Parameter/Condition                               | Symbol <sup>1</sup>            | Min | Тур | Max | Unit |

|---------------------------------------------------|--------------------------------|-----|-----|-----|------|

| GMII data TXD[7:0], TX_ER, TX_EN setup time       | t <sub>GTKHDV</sub>            | 2.5 | —   | —   | ns   |

| GTX_CLK to GMII data TXD[7:0], TX_ER, TX_EN delay | <sup>t</sup> GTKHDX            | 0.5 | —   | 5.0 | ns   |

| GTX_CLK data clock rise time (20%–80%)            | t <sub>GTXR</sub> <sup>2</sup> | _   | —   | 1.0 | ns   |

| GTX_CLK data clock fall time (80%–20%)            | t <sub>GTXF</sub> <sup>2</sup> | _   | —   | 1.0 | ns   |

Notes:

The symbols used for timing specifications follow the pattern t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>GTKHDV</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) reaching the valid state (V) to state or setup time. Also, t<sub>GTKHDX</sub> symbolizes GMII transmit timing (GT) with respect to the high state (H) relative to the time date input signals (D) reaching the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GTX</sub> represents the GMII(G) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

2. Guaranteed by design.

Figure 8 shows the GMII transmit AC timing diagram.

Figure 8. GMII Transmit AC Timing Diagram

## 8.2.2.2 GMII Receive AC Timing Specifications

This table provides the GMII receive AC timing specifications.

| Table 27. GMII Receive AC | Timing Specifications |

|---------------------------|-----------------------|

|---------------------------|-----------------------|

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|---------------------------------------------|-------------------------------------|-----|-----|-----|------|

| RX_CLK clock period                         | t <sub>GRX</sub>                    | —   | 8.0 | —   | ns   |

| RX_CLK duty cycle                           | t <sub>GRXH</sub> /t <sub>GRX</sub> | 35  | _   | 75  | ns   |

| RXD[7:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>GRDVKH</sub>                 | 2.0 | _   | —   | ns   |

| RXD[7:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>GRDXKH</sub>                 | 0   | _   | —   | ns   |

| RX_CLK clock rise (20%-80%)                 | t <sub>GRXR</sub> 2                 | —   | _   | 1.0 | ns   |

| RX_CLK clock fall time (80%-20%)            | t <sub>GRXF</sub> 2                 |     |     | 1.0 | ns   |

#### Notes:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>GRDVKH</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) reaching the valid state (V) relative to the t<sub>RX</sub> clock reference (K) going to the high state (H) or setup time. Also, t<sub>GRDXKL</sub> symbolizes GMII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>GRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GRX</sub> represents the GMII (G) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

2. Guaranteed by design.

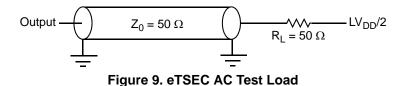

Figure 9 provides the AC test load for eTSEC.

# **10.2 Local Bus AC Electrical Specifications**

This table describes the timing parameters of the local bus interface at  $BV_{DD} = 3.3$  V. For information about the frequency range of local bus, see Section 20.1, "Clock Ranges."

| Parameter                                                             | Symbol <sup>1</sup>                 | Min | Max | Unit | Notes |

|-----------------------------------------------------------------------|-------------------------------------|-----|-----|------|-------|

| Local bus cycle time                                                  | t <sub>LBK</sub>                    | 7.5 | 12  | ns   | 2     |

| Local bus duty cycle                                                  | t <sub>LBKH/</sub> t <sub>LBK</sub> | 43  | 57  | %    | —     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                  | t <sub>LBKSKEW</sub>                | _   | 150 | ps   | 7, 8  |

| Input setup to local bus clock (except LGTA/LUPWAIT)                  | t <sub>LBIVKH1</sub>                | 1.8 |     | ns   | 3, 4  |

| LGTA/LUPWAIT input setup to local bus clock                           | t <sub>LBIVKH2</sub>                | 1.7 | _   | ns   | 3, 4  |

| Input hold from local bus clock (except LGTA/LUPWAIT)                 | t <sub>LBIXKH1</sub>                | 1.0 | _   | ns   | 3, 4  |

| LGTA/LUPWAIT input hold from local bus clock                          | t <sub>LBIXKH2</sub>                | 1.0 |     | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) | t <sub>LBOTOT</sub>                 | 1.5 | _   | ns   | 6     |

| Local bus clock to output valid (except LAD/LDP and LALE)             | t <sub>LBKHOV1</sub>                | _   | 2.0 | ns   | —     |

| Local bus clock to data valid for LAD/LDP                             | t <sub>LBKHOV2</sub>                | _   | 2.2 | ns   | 3     |

| Local bus clock to address valid for LAD                              | t <sub>LBKHOV3</sub>                | _   | 2.3 | ns   | 3     |

| Local bus clock to LALE assertion                                     | t <sub>LBKHOV4</sub>                | _   | 2.3 | ns   | 3     |

| Output hold from local bus clock (except LAD/LDP and LALE)            | t <sub>LBKHOX1</sub>                | 0.7 | _   | ns   | 3     |

| Output hold from local bus clock for LAD/LDP                          | t <sub>LBKHOX2</sub>                | 0.7 | _   | ns   | 3     |

| Local bus clock to output high Impedance (except LAD/LDP and LALE)    | t <sub>LBKHOZ1</sub>                |     | 2.5 | ns   | 5     |

| Local bus clock to output high impedance for LAD/LDP                  | t <sub>LBKHOZ2</sub>                | _   | 2.5 | ns   | 5     |

## Table 40. Local Bus Timing Parameters (BV<sub>DD</sub> = 3.3 V)—PLL Enabled

#### Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one (1). Also, t<sub>LBKH0X</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

</sub>

- 2. All timings are in reference to LSYNC\_IN for PLL enabled and internal local bus clock for PLL bypass mode.

- 3. All signals are measured from  $BV_{DD}/2$  of the rising edge of LSYNC\_IN for PLL enabled or internal local bus clock for PLL bypass mode to  $0.4 \times BV_{DD}$  of the signal in question for 3.3-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 6. t<sub>LBOTOT</sub> is a measurement of the minimum time between the negation of LALE and any change in LAD. t<sub>LBOTOT</sub> is programmed with the LBCR[AHD] parameter.

- 7. Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at BV<sub>DD</sub>/2.

- 8. Guaranteed by design.

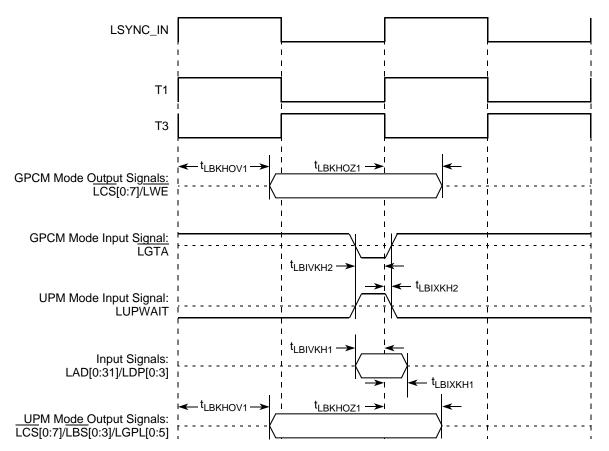

Figure 25. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 (PLL Enabled)

#### Local Bus

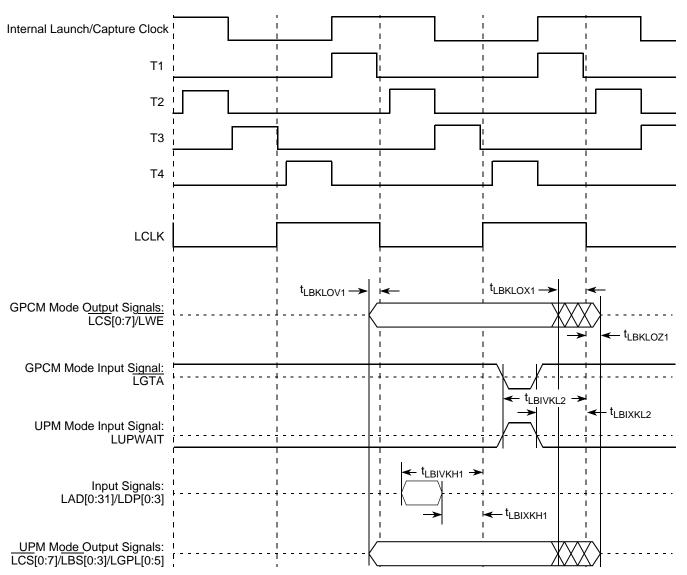

Figure 28. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 8 or 16 (PLL Bypass Mode)

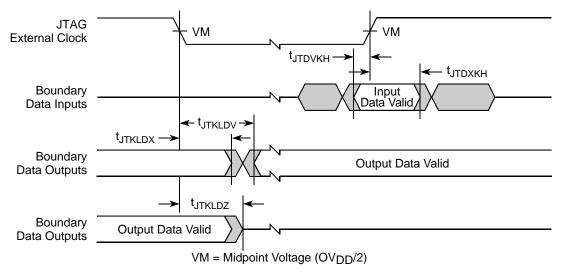

JTAG

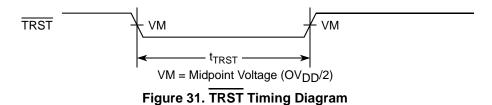

Figure 31 provides the  $\overline{\text{TRST}}$  timing diagram.

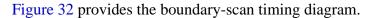

Figure 32. Boundary-Scan Timing Diagram

#### PCI/PCI-X

### Table 54. PCI-X AC Timing Specifications at 133 MHz (continued)

| Parameter                                        | Symbol              | Min | Max | Unit | Notes |

|--------------------------------------------------|---------------------|-----|-----|------|-------|

| HRESET to PCI-X initialization pattern hold time | t <sub>PCRHIX</sub> | 0   | 50  | ns   | 6, 12 |

Notes:

1. See the timing measurement conditions in the PCI-X 1.0a Specification.

- 2. Minimum times are measured at the package pin (not the test point). Maximum times are measured with the test point and load circuit.

- 3. Setup time for point-to-point signals applies to REQ and GNT only. All other signals are bused.

- 4. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- 5. Setup time applies only when the device is not driving the pin. Devices cannot drive and receive signals at the same time.

- 6. Maximum value is also limited by delay to the first transaction (time for HRESET high to first configuration access, t<sub>PCRHFV</sub>). The PCI-X initialization pattern control signals after the rising edge of HRESET must be negated no later than two clocks before the first FRAME and must be floated no later than one clock before FRAME is asserted.

- 7. A PCI-X device is permitted to have the minimum values shown for t<sub>PCKHOV</sub> and t<sub>CYC</sub> only in PCI-X mode. In conventional mode, the device must meet the requirements specified in PCI 2.2 for the appropriate clock frequency.

8. Device must meet this specification independent of how many outputs switch simultaneously.

9. The timing parameter t<sub>PCIVKH</sub> is a minimum of 1.4 ns rather than the minimum of 1.2 ns in the PCI-X 1.0a Specification.

- 10. The timing parameter t<sub>PCRHFV</sub> is a minimum of 10 clocks rather than the minimum of 5 clocks in the *PCI-X 1.0a Specification.*

- 11. Guaranteed by characterization.

12. Guaranteed by design.

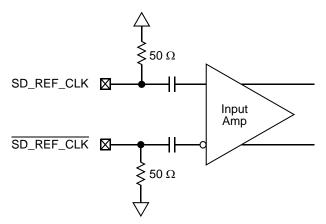

- The SD\_REF\_CLK and SD\_REF\_CLK are internally AC-coupled differential inputs as shown in Figure 39. Each differential clock input (SD\_REF\_CLK or SD\_REF\_CLK) has a 50-Ω termination to SGND\_SRDSn (xcorevss) followed by on-chip AC-coupling.

- The external reference clock driver must be able to drive this termination.

- The SerDes reference clock input can be either differential or single-ended. See the differential mode and single-ended mode description below for further detailed requirements.

- The maximum average current requirement that also determines the common mode voltage range:

- When the SerDes reference clock differential inputs are DC coupled externally with the clock driver chip, the maximum average current allowed for each input pin is 8 mA. In this case, the exact common mode input voltage is not critical as long as it is within the range allowed by the maximum average current of 8 mA (see the following bullet for more detail), since the input is AC-coupled on-chip.

- This current limitation sets the maximum common mode input voltage to be less than 0.4 V (0.4 V/50 = 8 mA) while the minimum common mode input level is 0.1 V above SGND\_SRDS*n* (xcorevss). For example, a clock with a 50/50 duty cycle can be produced by a clock driver with output driven by its current source from 0 to 16 mA (0–0.8 V), such that each phase of the differential input has a single-ended swing from 0 V to 800 mV with the common mode voltage at 400 mV.

- If the device driving the SD\_REF\_CLK and  $\overline{\text{SD}_{\text{REF}_{\text{CLK}}}}$  inputs cannot drive 50  $\Omega$  to SGND\_SRDS*n* (xcorevss) DC, or it exceeds the maximum input current limitations, then it must be AC-coupled off-chip.

- The input amplitude requirement:

- This requirement is described in detail in the following sections.

Figure 39. Receiver of SerDes Reference Clocks

## 16.2.2 DC Level Requirement for SerDes Reference Clocks

The DC level requirement for the SerDes reference clock inputs is different depending on the signaling mode used to connect the clock driver chip and SerDes reference clock inputs as described below:

• Differential mode

Table 57. Differential Receiver (RX) Input Specifications (continued)

| Symbol               | Parameter  | Min | Nom | Max | Unit | Comments                                                                                                                                                                                                                          |

|----------------------|------------|-----|-----|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L <sub>TX-SKEW</sub> | Total Skew | _   |     | 20  | ns   | Skew across all lanes on a Link. This includes<br>variation in the length of SKP ordered set (for<br>example, COM and one to five symbols) at the RX<br>as well as any delay differences arising from the<br>interconnect itself. |

#### Notes:

- 1. No test load is necessarily associated with this value.

- 2. Specified at the measurement point and measured over any 250 consecutive UIs. The test load in Figure 50 must be used as the RX device when taking measurements (also see the receiver compliance eye diagram shown in Figure 49). If the clocks to the RX and TX are not derived from the same reference clock, the TX UI recovered from 3500 consecutive UI must be used as a reference for the eye diagram.

- 3. A T<sub>RX-EYE</sub> = 0.40 UI provides for a total sum of 0.60 UI deterministic and random jitter budget for the transmitter and interconnect collected any 250 consecutive UIs. The T<sub>RX-EYE-MEDIAN-to-MAX-JITTER</sub> specification ensures a jitter distribution in which the median and the maximum deviation from the median is less than half of the total. UI jitter budget collected over any 250 consecutive TX UIs. Note that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value. If the clocks to the RX and TX are not derived from the same reference clock, the TX UI recovered from 3500 consecutive UI must be used as the reference for the eye diagram.

- 4. The receiver input impedance shall result in a differential return loss greater than or equal to 15 dB with the D+ line biased to 300 mV and the D– line biased to  $-{300 \text{ mV}}$  and a common mode return loss greater than or equal to 6 dB (no bias required) over a frequency range of 50 MHz to 1.25 GHz. This input impedance requirement applies to all valid input levels. The reference impedance for return loss measurements for is 50  $\Omega$  to ground for both the D+ and D– line (that is, as measured by a vector network analyzer with 50- $\Omega$  probes—see Figure 50). Note: that the series capacitors CTX is optional for the return loss measurement.

- 5. Impedance during all LTSSM states. When transitioning from a fundamental reset to detect (the initial state of the LTSSM) there is a 5 ms transition time before receiver termination values must be met on all unconfigured lanes of a port.

- 6. The RX DC common mode Impedance that exists when no power is present or fundamental reset is asserted. This helps ensure that the receiver detect circuit does not falsely assume a receiver is powered on when it is not. This term must be measured at 300 mV above the RX ground.

- 7. It is recommended that the recovered TX UI is calculated using all edges in the 3500 consecutive UI interval with a fit algorithm using a minimization merit function. Least squares and median deviation fits have worked well with experimental and simulated data.

# 17.5 Receiver Compliance Eye Diagrams

The RX eye diagram in Figure 49 is specified using the passive compliance/test measurement load (see Figure 50) in place of any real PCI Express RX component.

Note: In general, the minimum receiver eye diagram measured with the compliance/test measurement load (see Figure 50) is larger than the minimum receiver eye diagram measured over a range of systems at the input receiver of any real PCI Express component. The degraded eye diagram at the input receiver is due to traces internal to the package as well as silicon parasitic characteristics which cause the real PCI Express component to vary in impedance from the compliance/test measurement load. The input receiver eye diagram is implementation specific and is not specified. RX component designer must provide additional margin to adequately compensate for the degraded minimum receiver eye diagram (shown in Figure 49) expected at the input receiver based on some adequate combination of system simulations and the return loss measured looking into the RX package and silicon. The RX eye diagram must be aligned in time using the jitter median to locate the center of the eye diagram.

# 18 Serial RapidIO

This section describes the DC and AC electrical specifications for the RapidIO interface of the MPC8548E, for the LP-Serial physical layer. The electrical specifications cover both single- and multiple-lane links. Two transmitters (short and long run) and a single receiver are specified for each of three baud rates, 1.25, 2.50, and 3.125 GBaud.

Two transmitter specifications allow for solutions ranging from simple board-to-board interconnect to driving two connectors across a backplane. A single receiver specification is given that accepts signals from both the short- and long-run transmitter specifications.

The short-run transmitter must be used mainly for chip-to-chip connections on either the same printed-circuit board or across a single connector. This covers the case where connections are made to a mezzanine (daughter) card. The minimum swings of the short-run specification reduce the overall power used by the transceivers.

The long-run transmitter specifications use larger voltage swings that are capable of driving signals across backplanes. This allows a user to drive signals across two connectors and a backplane. The specifications allow a distance of at least 50 cm at all baud rates.

All unit intervals are specified with a tolerance of  $\pm 100$  ppm. The worst case frequency difference between any transmit and receive clock is 200 ppm.

To ensure interoperability between drivers and receivers of different vendors and technologies, AC coupling at the receiver input must be used.

# 18.1 <u>DC Requirements</u> for Serial RapidIO SD\_REF\_CLK and SD\_REF\_CLK

For more information, see Section 16.2, "SerDes Reference Clocks."

# 18.2 <u>AC Requirements</u> for Serial RapidIO SD\_REF\_CLK and SD\_REF\_CLK

Table 58 lists the Serial RapidIO SD\_REF\_CLK and SD\_REF\_CLK AC requirements.

| Symbol             | Parameter Description                                                                     | Min | Тур   | Мах | Unit | Comments                                                               |

|--------------------|-------------------------------------------------------------------------------------------|-----|-------|-----|------|------------------------------------------------------------------------|

| t <sub>REF</sub>   | REFCLK cycle time                                                                         | —   | 10(8) | —   | ns   | 8 ns applies only to serial<br>RapidIO with 125-MHz reference<br>clock |

| t <sub>REFCJ</sub> | REFCLK cycle-to-cycle jitter. Difference in the period of any two adjacent REFCLK cycles. | —   | —     | 80  | ps   | _                                                                      |

| t <sub>REFPJ</sub> | Phase jitter. Deviation in edge location with respect to mean edge location.              | -40 | —     | 40  | ps   | _                                                                      |

## Table 58. SD\_REF\_CLK and SD\_REF\_CLK AC Requirements

This section details package parameters, pin assignments, and dimensions.

## **19.1 Package Parameters**

The package parameters for both the HiCTE FC-CBGA and FC-PBGA are provided in Table 70.

| Parameter               | CBGA <sup>1</sup> | PBGA <sup>2</sup> |

|-------------------------|-------------------|-------------------|

| Package outline         | 29 mm × 29 mm     | 29 mm × 29 mm     |

| Interconnects           | 783               | 783               |

| Ball pitch              | 1 mm              | 1 mm              |

| Ball diameter (typical) | 0.6 mm            | 0.6 mm            |

| Solder ball             | 63% Sn            | 63% Sn            |

|                         | 37% Pb            | 37% Pb            |

|                         | 0% Ag             | 0% Ag             |

| Solder ball (lead-free) | 95% Sn            | 96.5% Sn          |

|                         | 4.5% Ag           | 3.5% Ag           |

|                         | 0.5% Cu           |                   |

Table 70. Package Parameters

Notes:

1. The HiCTE FC-CBGA package is available on only Version 2.0 of the device.

2. The FC-PBGA package is available on only versions 2.1.1 and 2.1.2, and 3.0 of the device.

| Signal             | Package Pin Number                                | Pin Type | Power<br>Supply  | Notes        |

|--------------------|---------------------------------------------------|----------|------------------|--------------|

| LSYNC_IN           | F27                                               | I        | BV <sub>DD</sub> | _            |

| LSYNC_OUT          | F28                                               | 0        | BV <sub>DD</sub> | —            |

|                    | DMA                                               |          |                  | 1            |

| DMA_DACK[0:1]      | AD3, AE1                                          | 0        | OV <sub>DD</sub> | 5, 9,<br>102 |

| DMA_DREQ[0:1]      | AD4, AE2                                          | I        | OV <sub>DD</sub> | _            |

| DMA_DDONE[0:1]     | AD2, AD1                                          | 0        | OV <sub>DD</sub> | —            |

|                    | Programmable Interrupt Controller                 |          | •                |              |

| UDE                | AH16                                              | I        | OV <sub>DD</sub> | —            |

| MCP                | AG19                                              | I        | OV <sub>DD</sub> | —            |

| IRQ[0:7]           | AG23, AF18, AE18, AF20, AG18, AF17, AH24, AE20    | I        | OV <sub>DD</sub> | -            |

| IRQ[8]             | AF19                                              | I        | OV <sub>DD</sub> | —            |

| IRQ[9]/DMA_DREQ3   | AF21                                              | I        | OV <sub>DD</sub> | 1            |

| IRQ[10]/DMA_DACK3  | AE19                                              | I/O      | OV <sub>DD</sub> | 1            |

| IRQ[11]/DMA_DDONE3 | AD20                                              | I/O      | OV <sub>DD</sub> | 1            |

| IRQ_OUT            | AD18                                              | 0        | OV <sub>DD</sub> | 2, 4         |

|                    | Ethernet Management Interface                     |          | •                |              |

| EC_MDC             | AB9                                               | 0        | OV <sub>DD</sub> | 5, 9         |

| EC_MDIO            | AC8                                               | I/O      | OV <sub>DD</sub> | —            |

|                    | Gigabit Reference Clock                           |          |                  | 1            |

| EC_GTX_CLK125      | V11                                               | I        | LV <sub>DD</sub> | _            |

|                    | Three-Speed Ethernet Controller (Gigabit Ethernet | et 1)    |                  | 1            |

| TSEC1_RXD[7:0]     | R5, U1, R3, U2, V3, V1, T3, T2                    | I        | LV <sub>DD</sub> | _            |

| TSEC1_TXD[7:0]     | T10, V7, U10, U5, U4, V6, T5, T8                  | 0        | LV <sub>DD</sub> | 5, 9         |

| TSEC1_COL          | R4                                                | I        | LV <sub>DD</sub> | _            |

| TSEC1_CRS          | V5                                                | I/O      | LV <sub>DD</sub> | 20           |

| TSEC1_GTX_CLK      | U7                                                | 0        | LV <sub>DD</sub> |              |

| TSEC1_RX_CLK       | U3                                                | I        | LV <sub>DD</sub> | —            |

| TSEC1_RX_DV        | V2                                                | I        | LV <sub>DD</sub> | _            |

| TSEC1_RX_ER        | T1                                                | I        | LV <sub>DD</sub> | _            |

| TSEC1_TX_CLK       | Т6                                                | I        | LV <sub>DD</sub> | —            |

| TSEC1_TX_EN        | U9                                                | 0        | LV <sub>DD</sub> | 30           |

| TSEC1_TX_ER        | Т7                                                | 0        | LV <sub>DD</sub> | <u> </u>     |

| Signal                 | Package Pin Number                       | Pin Type | Power<br>Supply  | Notes           |

|------------------------|------------------------------------------|----------|------------------|-----------------|

|                        | I <sup>2</sup> C interface               |          |                  |                 |

| IIC1_SCL               | AG22                                     | I/O      | OV <sub>DD</sub> | 4, 27           |

| IIC1_SDA               | AG21                                     | I/O      | OV <sub>DD</sub> | 4, 27           |

| IIC2_SCL               | AG15                                     | I/O      | OV <sub>DD</sub> | 4, 27           |

| IIC2_SDA               | AG14                                     | I/O      | OV <sub>DD</sub> | 4, 27           |

|                        | SerDes                                   |          |                  |                 |

| SD_RX[0:7]             | M28, N26, P28, R26, W26, Y28, AA26, AB28 | I        | XV <sub>DD</sub> | —               |

| SD_RX[0:7]             | M27, N25, P27, R25, W25, Y27, AA25, AB27 | I        | XV <sub>DD</sub> | —               |

| SD_TX[0:7]             | M22, N20, P22, R20, U20, V22, W20, Y22   | 0        | XV <sub>DD</sub> | _               |

| SD_TX[0:7]             | M23, N21, P23, R21, U21, V23, W21, Y23   | 0        | XV <sub>DD</sub> | —               |

| SD_PLL_TPD             | U28                                      | 0        | XV <sub>DD</sub> | 24              |

| SD_REF_CLK             | T28                                      | I        | XV <sub>DD</sub> | 3               |

| SD_REF_CLK             | T27                                      | I        | XV <sub>DD</sub> | 3               |

| Reserved               | AC1, AC3                                 | _        | —                | 2               |

| Reserved               | M26, V28                                 | _        | —                | 32              |

| Reserved               | M25, V27                                 | _        | —                | 34              |

| Reserved               | M20, M21, T22, T23                       | —        | —                | 38              |

|                        | General-Purpose Output                   |          |                  | 1               |

| GPOUT[24:31]           | K26, K25, H27, G28, H25, J26, K24, K23   | 0        | BV <sub>DD</sub> | _               |

|                        | System Control                           |          |                  | 1               |

| HRESET                 | AG17                                     | I        | OV <sub>DD</sub> | _               |

| HRESET_REQ             | AG16                                     | 0        | OV <sub>DD</sub> | 29              |

| SRESET                 | AG20                                     | I        | OV <sub>DD</sub> | —               |

| CKSTP_IN               | AA9                                      | I        | OV <sub>DD</sub> | —               |

| CKSTP_OUT              | AA8                                      | 0        | OV <sub>DD</sub> | 2, 4            |

|                        | Debug                                    |          |                  | 1               |

| TRIG_IN                | AB2                                      | I        | OV <sub>DD</sub> | _               |

| TRIG_OUT/READY/QUIESCE | AB1                                      | 0        | OV <sub>DD</sub> | 6, 9,<br>19, 29 |

| MSRCID[0:1]            | AE4, AG2                                 | 0        | OV <sub>DD</sub> | 5, 6, 9         |

| MSRCID[2:4]            | AF3, AF1, AF2                            | 0        | OV <sub>DD</sub> | 6, 19,<br>29    |

| MDVAL                  | AE5                                      | 0        | OV <sub>DD</sub> | 6               |

| CLK_OUT                | AE21                                     | 0        | OV <sub>DD</sub> | 11              |

| Signal           | Package Pin Number                                                                                                                                                | Pin Type                                                          | Power<br>Supply  | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------------------|-------|

| LV <sub>DD</sub> | N8, R7, T9, U6                                                                                                                                                    | Power for<br>TSEC1 and<br>TSEC2<br>(2.5 V, 3.3 V)                 | LV <sub>DD</sub> | _     |

| TV <sub>DD</sub> | W9, Y6                                                                                                                                                            | Power for<br>TSEC3 and<br>TSEC4<br>(2,5 V, 3.3 V)                 | TV <sub>DD</sub> | _     |

| GV <sub>DD</sub> | B3, B11, C7, C9, C14, C17, D4, D6, D10, D15,<br>E2, E8, E11, E18, F5, F12, F16, G3, G7, G9,<br>G11, H5, H12, H15, H17, J10, K3, K12, K16,<br>K18, L6, M4, M8, M13 | Power for<br>DDR1 and<br>DDR2 DRAM<br>I/O voltage<br>(1.8 V, 2.5) | GV <sub>DD</sub> |       |

| BV <sub>DD</sub> | C21, C24, C27, E20, E25, G19, G23, H26, J20                                                                                                                       | Power for local<br>bus (1.8 V,<br>2.5 V, 3.3 V)                   | BV <sub>DD</sub> |       |

| V <sub>DD</sub>  | M19, N12, N14, N16, N18, P11, P13, P15, P17,<br>P19, R12, R14, R16, R18, T11, T13, T15, T17,<br>T19, U12, U14, U16, U18, V17, V19                                 | Power for core<br>(1.1 V)                                         | V <sub>DD</sub>  |       |

| SV <sub>DD</sub> | L25, L27, M24, N28, P24, P26, R24, R27, T25,<br>V24, V26, W24, W27, Y25, AA28, AC27                                                                               | Core Power<br>for SerDes<br>transceivers<br>(1.1 V)               | SV <sub>DD</sub> | —     |

| XV <sub>DD</sub> | L20, L22, N23, P21, R22, T20, U23, V21, W22,<br>Y20                                                                                                               | Pad Power for<br>SerDes<br>transceivers<br>(1.1 V)                | XV <sub>DD</sub> |       |

| AVDD_LBIU        | J28                                                                                                                                                               | Power for local<br>bus PLL<br>(1.1 V)                             | _                | 26    |

| AVDD_PCI1        | AH21                                                                                                                                                              | Power for<br>PCI1 PLL<br>(1.1 V)                                  | _                | 26    |

| AVDD_PCI2        | AH22                                                                                                                                                              | Power for<br>PCI2 PLL<br>(1.1 V)                                  | _                | 26    |

| AVDD_CORE        | AH15                                                                                                                                                              | Power for<br>e500 PLL (1.1<br>V)                                  | _                | 26    |

| AVDD_PLAT        | AH19                                                                                                                                                              | Powerfor CCB<br>PLL (1.1 V)                                       | —                | 26    |

| AVDD_SRDS        | U25                                                                                                                                                               | Power for<br>SRDSPLL<br>(1.1 V)                                   | _                | 26    |

| SENSEVDD         | M14                                                                                                                                                               | 0                                                                 | V <sub>DD</sub>  | 13    |

## Table 71. MPC8548E Pinout Listing (continued)

### Table 72. MPC8547E Pinout Listing (continued)

| Signal     | Package Pin Number | Pin Type | Power<br>Supply | Notes |

|------------|--------------------|----------|-----------------|-------|

| SD_PLL_TPA | U26                | 0        | —               | 24    |

**Note:** All note references in this table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

Table 73 provides the pin-out listing for the MPC8545E 783 FC-PBGA package.

## NOTE

All note references in the following table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

| Signal                        | Package Pin Number                                                                                                                                                                                     | Pin Type | Power<br>Supply  | Notes    |  |  |  |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|--|--|--|

|                               | PCI1 and PCI2 (One 64-Bit or Two 32-Bit)                                                                                                                                                               |          |                  |          |  |  |  |

| PCI1_AD[63:32]/PCI2_AD[31:0]  | AB14, AC15, AA15, Y16, W16, AB16, AC16,<br>AA16, AE17, AA18, W18, AC17, AD16, AE16,<br>Y17, AC18, AB18, AA19, AB19, AB21, AA20,<br>AC20, AB20, AB22, AC22, AD21, AB23, AF23,<br>AD23, AE23, AC23, AC24 | I/O      | OV <sub>DD</sub> | 17       |  |  |  |

| PCI1_AD[31:0]                 | AH6, AE7, AF7, AG7, AH7, AF8, AH8, AE9,<br>AH9, AC10, AB10, AD10, AG10, AA10, AH10,<br>AA11, AB12, AE12, AG12, AH12, AB13, AA12,<br>AC13, AE13, Y14, W13, AG13, V14, AH13,<br>AC14, Y15, AB15          | I/O      | OV <sub>DD</sub> | 17       |  |  |  |

| PCI1_C_BE[7:4]/PCI2_C_BE[3:0] | AF15, AD14, AE15, AD15                                                                                                                                                                                 | I/O      | OV <sub>DD</sub> | 17       |  |  |  |

| PCI1_C_BE[3:0]                | AF9, AD11, Y12, Y13                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 17       |  |  |  |

| PCI1_PAR64/PCI2_PAR           | W15                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | —        |  |  |  |

| PCI1_GNT[4:1]                 | AG6, AE6, AF5, AH5                                                                                                                                                                                     | 0        | OV <sub>DD</sub> | 5, 9, 35 |  |  |  |

| PCI1_GNT0                     | AG5                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | —        |  |  |  |

| PCI1_IRDY                     | AF11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| PCI1_PAR                      | AD12                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | —        |  |  |  |

| PCI1_PERR                     | AC12                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| PCI1_SERR                     | V13                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2, 4     |  |  |  |

| PCI1_STOP                     | W12                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| PCI1_TRDY                     | AG11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| PCI1_REQ[4:1]                 | AH2, AG4, AG3, AH4                                                                                                                                                                                     | I        | OV <sub>DD</sub> | —        |  |  |  |

| PCI1_REQ0                     | AH3                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | —        |  |  |  |

| PCI1_CLK                      | AH26                                                                                                                                                                                                   | I        | OV <sub>DD</sub> | 39       |  |  |  |

| PCI1_DEVSEL                   | AH11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

## Table 73. MPC8545E Pinout Listing

| Signal        | Package Pin Number | Pin Type | Power<br>Supply | Notes |

|---------------|--------------------|----------|-----------------|-------|

| SD_IMP_CAL_RX | L28                | I        | 200 Ω to<br>GND | —     |

| SD_IMP_CAL_TX | AB26               | I        | 100 Ω to<br>GND | —     |

| SD_PLL_TPA    | U26                | 0        | —               | 24    |

### Table 73. MPC8545E Pinout Listing (continued)

Note: All note references in this table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

Table 74 provides the pin-out listing for the MPC8543E 783 FC-PBGA package.

## NOTE

All note references in the following table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

Table 74. MPC8543E Pinout Listing

| Signal         | Package Pin Number                                                                                                                                                                            | Pin Type | Power<br>Supply  | Notes    |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|--|--|--|

|                | PCI1 (One 32-Bit)                                                                                                                                                                             |          |                  |          |  |  |  |

| Reserved       | AB14, AC15, AA15, Y16, W16, AB16, AC16,<br>AA16, AE17, AA18, W18, AC17, AD16, AE16,<br>Y17, AC18,                                                                                             |          | _                | 110      |  |  |  |

| GPOUT[8:15]    | AB18, AA19, AB19, AB21, AA20, AC20, AB20, AB22                                                                                                                                                | 0        | OV <sub>DD</sub> | —        |  |  |  |

| GPIN[8:15]     | AC22, AD21, AB23, AF23, AD23, AE23, AC23, AC24                                                                                                                                                | I        | OV <sub>DD</sub> | 111      |  |  |  |

| PCI1_AD[31:0]  | AH6, AE7, AF7, AG7, AH7, AF8, AH8, AE9,<br>AH9, AC10, AB10, AD10, AG10, AA10, AH10,<br>AA11, AB12, AE12, AG12, AH12, AB13, AA12,<br>AC13, AE13, Y14, W13, AG13, V14, AH13,<br>AC14, Y15, AB15 | I/O      | OV <sub>DD</sub> | 17       |  |  |  |

| Reserved       | AF15, AD14, AE15, AD15                                                                                                                                                                        | _        | -                | 110      |  |  |  |

| PCI1_C_BE[3:0] | AF9, AD11, Y12, Y13                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 17       |  |  |  |

| Reserved       | W15                                                                                                                                                                                           |          |                  | 110      |  |  |  |

| PCI1_GNT[4:1]  | AG6, AE6, AF5, AH5                                                                                                                                                                            | 0        | OV <sub>DD</sub> | 5, 9, 35 |  |  |  |

| PCI1_GNT0      | AG5                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | —        |  |  |  |

| PCI1_IRDY      | AF11                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| PCI1_PAR       | AD12                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | —        |  |  |  |

| PCI1_PERR      | AC12                                                                                                                                                                                          | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| PCI1_SERR      | V13                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2, 4     |  |  |  |

| PCI1_STOP      | W12                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |  |  |  |

| Signal             | Package Pin Number                             | Pin Type | Power<br>Supply  | Notes     |

|--------------------|------------------------------------------------|----------|------------------|-----------|

| LSYNC_IN           | F27                                            | I        | BV <sub>DD</sub> | —         |

| LSYNC_OUT          | F28                                            | 0        | BV <sub>DD</sub> | —         |

|                    | DMA                                            |          |                  | 1         |

| DMA_DACK[0:1]      | AD3, AE1                                       | 0        | OV <sub>DD</sub> | 5, 9, 108 |

| DMA_DREQ[0:1]      | AD4, AE2                                       | I        | OV <sub>DD</sub> | —         |

| DMA_DDONE[0:1]     | AD2, AD1                                       | 0        | $OV_{DD}$        | —         |

|                    | Programmable Interrupt Controller              |          |                  | •         |

| UDE                | AH16                                           | Ι        | OV <sub>DD</sub> | —         |

| MCP                | AG19                                           | I        | OV <sub>DD</sub> | —         |

| IRQ[0:7]           | AG23, AF18, AE18, AF20, AG18, AF17, AH24, AE20 | I        | $OV_{DD}$        | —         |

| IRQ[8]             | AF19                                           | I        | OV <sub>DD</sub> | —         |

| IRQ[9]/DMA_DREQ3   | AF21                                           | I        | OV <sub>DD</sub> | 1         |

| IRQ[10]/DMA_DACK3  | AE19                                           | I/O      | OV <sub>DD</sub> | 1         |

| IRQ[11]/DMA_DDONE3 | AD20                                           | I/O      | OV <sub>DD</sub> | 1         |

| IRQ_OUT            | AD18                                           | 0        | OV <sub>DD</sub> | 2, 4      |

|                    | Ethernet Management Interface                  |          |                  | 1         |

| EC_MDC             | AB9                                            | 0        | OV <sub>DD</sub> | 5, 9      |

| EC_MDIO            | AC8                                            | I/O      | $OV_{DD}$        | —         |

|                    | Gigabit Reference Clock                        |          |                  |           |

| EC_GTX_CLK125      | V11                                            | Ι        | LV <sub>DD</sub> | —         |

|                    | Three-Speed Ethernet Controller (Gigabit Ether | rnet 1)  |                  | •         |

| TSEC1_RXD[7:0]     | R5, U1, R3, U2, V3, V1, T3, T2                 | Ι        | $LV_{DD}$        | —         |

| TSEC1_TXD[7:0]     | T10, V7, U10, U5, U4, V6, T5, T8               | 0        | $LV_{DD}$        | 5, 9      |

| TSEC1_COL          | R4                                             | I        | LV <sub>DD</sub> | —         |

| TSEC1_CRS          | V5                                             | I/O      | LV <sub>DD</sub> | 20        |

| TSEC1_GTX_CLK      | U7                                             | 0        | $LV_{DD}$        | —         |

| TSEC1_RX_CLK       | U3                                             | I        | LV <sub>DD</sub> | —         |

| TSEC1_RX_DV        | V2                                             | I        | LV <sub>DD</sub> | —         |

| TSEC1_RX_ER        | T1                                             | I        | LV <sub>DD</sub> | —         |

| TSEC1_TX_CLK       | Т6                                             | I        | LV <sub>DD</sub> | —         |

| TSEC1_TX_EN        | U9                                             | 0        | LV <sub>DD</sub> | 30        |

| TSEC1_TX_ER        | Т7                                             | 0        | $LV_{DD}$        | —         |

| GPIN[0:7]          | P2, R2, N1, N2, P3, M2, M1, N3                 | I        | LV <sub>DD</sub> | 103       |

| Signal           | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin Type                                              | Power<br>Supply  | Notes     |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------------------|-----------|

|                  | JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 11                                                    |                  |           |

| ТСК              | AG28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | —         |

| TDI              | AH28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 12        |

| TDO              | AF28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                     | $OV_{DD}$        | —         |

| TMS              | AH27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 12        |

| TRST             | AH23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 12        |

|                  | DFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                       |                  |           |

| L1_TSTCLK        | AC25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 25        |

| L2_TSTCLK        | AE22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 25        |

| LSSD_MODE        | AH20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 25        |

| TEST_SEL         | AH14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                     | $OV_{DD}$        | 109       |

|                  | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                       |                  |           |

| THERM0           | AG1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                     | _                | 14        |

| THERM1           | AH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                     | _                | 14        |

|                  | Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                       |                  |           |

| ASLEEP           | AH18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                     | $OV_{DD}$        | 9, 19, 29 |

|                  | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                       |                  |           |

| GND              | <ul> <li>A11, B7, B24, C1, C3, C5, C12, C15, C26, D8,<br/>D11, D16, D20, D22, E1, E5, E9, E12, E15, E17,<br/>F4, F26, G12, G15, G18, G21, G24, H2, H6, H8,<br/>H28, J4, J12, J15, J17, J27, K7, K9, K11, K27,<br/>L3, L5, L12, L16, N11, N13, N15, N17, N19, P4,<br/>P9, P12, P14, P16, P18, R11, R13, R15, R17,<br/>R19, T4, T12, T14, T16, T18, U8, U11, U13,<br/>U15, U17, U19, V4, V12, V18, W6, W19, Y4, Y9,<br/>Y11, Y19, AA6, AA14, AA17, AA22, AA23, AB4,<br/>AC2, AC11, AC19, AC26, AD5, AD9, AD22,<br/>AE3, AE14, AF6, AF10, AF13, AG8, AG27,<br/>K28, L24, L26, N24, N27, P25, R28, T24, T26,<br/>U24, V25, W28, Y24, Y26, AA24, AA27, AB25,<br/>AC28, L21, L23, N22, P20, R23, T21, U22, V20,<br/>W23, Y21, U27</li> </ul> | _                                                     |                  |           |

| OV <sub>DD</sub> | V16, W11, W14, Y18, AA13, AA21, AB11,<br>AB17, AB24, AC4, AC9, AC21, AD6, AD13,<br>AD17, AD19, AE10, AE8, AE24, AF4, AF12,<br>AF22, AF27, AG26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Power for<br>PCI and<br>other<br>standards<br>(3.3 V) | OV <sub>DD</sub> | _         |

| LV <sub>DD</sub> | N8, R7, T9, U6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Power for<br>TSEC1 and<br>TSEC2<br>(2.5 V, 3.3 V)     | LV <sub>DD</sub> | _         |