Welcome to **E-XFL.COM**

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

## **Applications of Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

| Details                         |                                                                       |

|---------------------------------|-----------------------------------------------------------------------|

| Product Status                  | Obsolete                                                              |

| Core Processor                  | PowerPC e500                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 1.333GHz                                                              |

| Co-Processors/DSP               | Signal Processing; SPE                                                |

| RAM Controllers                 | DDR, DDR2, SDRAM                                                      |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (4)                                                   |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                      |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                     |

| Package / Case                  | 783-BBGA, FCBGA                                                       |

| Supplier Device Package         | 783-FCPBGA (29x29)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8548vjaujd |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

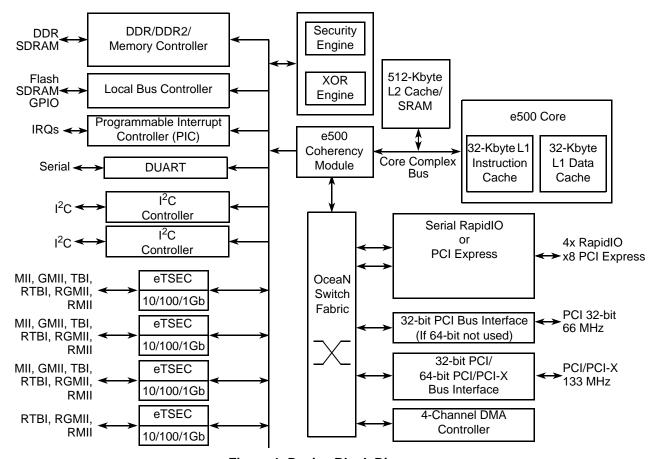

Figure 1. Device Block Diagram

# 1.1 Key Features

The following list provides an overview of the device feature set:

- High-performance 32-bit core built on Power Architecture® technology.

- 32-Kbyte L1 instruction cache and 32-Kbyte L1 data cache with parity protection. Caches can be locked entirely or on a per-line basis, with separate locking for instructions and data.

- Signal-processing engine (SPE) APU (auxiliary processing unit). Provides an extensive instruction set for vector (64-bit) integer and fractional operations. These instructions use both the upper and lower words of the 64-bit GPRs as they are defined by the SPE APU.

- Double-precision floating-point APU. Provides an instruction set for double-precision (64-bit) floating-point instructions that use the 64-bit GPRs.

- 36-bit real addressing

- Embedded vector and scalar single-precision floating-point APUs. Provide an instruction set for single-precision (32-bit) floating-point instructions.

- Memory management unit (MMU). Especially designed for embedded applications. Supports 4-Kbyte to 4-Gbyte page sizes.

- Enhanced hardware and software debug support

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

# 5 RESET Initialization

This section describes the AC electrical specifications for the RESET initialization timing requirements of the device. The following table provides the RESET initialization AC timing specifications for the DDR SDRAM component(s).

**Table 8. RESET Initialization Timing Specifications**

| Parameter/Condition                                                                                     | Min | Max | Unit    | Notes |

|---------------------------------------------------------------------------------------------------------|-----|-----|---------|-------|

| Required assertion time of HRESET                                                                       | 100 | _   | μS      | _     |

| Minimum assertion time for SRESET                                                                       | 3   | _   | SYSCLKs | 1     |

| PLL input setup time with stable SYSCLK before HRESET negation                                          | 100 | _   | μS      | _     |

| Input setup time for POR configs (other than PLL config) with respect to negation of HRESET             | 4   | _   | SYSCLKs | 1     |

| Input hold time for all POR configs (including PLL config) with respect to negation of HRESET           | 2   | _   | SYSCLKs | 1     |

| Maximum valid-to-high impedance time for actively driven POR configs with respect to negation of HRESET | _   | 5   | SYSCLKs | 1     |

#### Note:

The following table provides the PLL lock times.

**Table 9. PLL Lock Times**

| Parameter/Condition              | Min | Max | Unit |

|----------------------------------|-----|-----|------|

| Core and platform PLL lock times | _   | 100 | μS   |

| Local bus PLL lock time          | _   | 50  | μS   |

| PCI/PCI-X bus PLL lock time      | _   | 50  | μS   |

# 5.1 Power-On Ramp Rate

This section describes the AC electrical specifications for the power-on ramp rate requirements. Controlling the maximum power-on ramp rate is required to avoid falsely triggering the ESD circuitry. The following table provides the power supply ramp rate specifications.

**Table 10. Power Supply Ramp Rate**

| Parameter                    | Min | Max  | Unit | Notes |

|------------------------------|-----|------|------|-------|

| Required ramp rate for MVREF | _   | 3500 | V/s  | 1     |

| Required ramp rate for VDD   | _   | 4000 | V/s  | 1, 2  |

#### Note:

- 1. Maximum ramp rate from 200 to 500 mV is most critical as this range may falsely trigger the ESD circuitry.

- 2. VDD itself is not vulnerable to false ESD triggering; however, as per Section 22.2, "PLL Power Supply Filtering," the recommended AVDD\_CORE, AVDD\_PLAT, AVDD\_LBIU, AVDD\_PCI1 and AVDD\_PCI2 filters are all connected to VDD. Their ramp rates must be equal to or less than the VDD ramp rate.

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

<sup>1.</sup> SYSCLK is the primary clock input for the device.

# 6.2.2 DDR SDRAM Output AC Timing Specifications

## **Table 19. DDR SDRAM Output AC Timing Specifications**

At recommended operating conditions.

| Parameter                                                                  | Symbol <sup>1</sup>                         | Min                         | Max                         | Unit | Notes |

|----------------------------------------------------------------------------|---------------------------------------------|-----------------------------|-----------------------------|------|-------|

| MCK[n] cycle time, MCK[n]/MCK[n] crossing                                  | t <sub>MCK</sub>                            | 3.75                        | 6                           | ns   | 2     |

| ADDR/CMD output setup with respect to MCK 533 MHz 400 MHz 333 MHz          | <sup>t</sup> DDKHAS                         | 1.48<br>1.95<br>2.40        | _<br>_<br>_<br>_            | ns   | 3     |

| ADDR/CMD output hold with respect to MCK 533 MHz 400 MHz 333 MHz           | t <sub>DDKHAX</sub>                         | 1.48<br>1.95<br>2.40        | _<br>_<br>_                 | ns   | 3     |

| MCS[n] output setup with respect to MCK 533 MHz 400 MHz 333 MHz            | <sup>t</sup> DDKHCS                         | 1.48<br>1.95<br>2.40        | _<br>_<br>_                 | ns   | 3     |

| MCS[n] output hold with respect to MCK 533 MHz 400 MHz 333 MHz             | <sup>t</sup> DDKHCX                         | 1.48<br>1.95<br>2.40        | _<br>_<br>_                 | ns   | 3     |

| MCK to MDQS Skew                                                           | t <sub>DDKHMH</sub>                         | -0.6                        | 0.6                         | ns   | 4     |

| MDQ/MECC/MDM output setup with respect<br>to MDQS  533 MHz 400 MHz 333 MHz | <sup>t</sup> DDKHDS,<br><sup>t</sup> DDKLDS | 538<br>700<br>900           | _<br>_<br>_<br>_            | ps   | 5     |

| MDQ/MECC/MDM output hold with respect to MDQS  533 MHz 400 MHz 333 MHz     | <sup>t</sup> DDKHDX,<br><sup>t</sup> DDKLDX | 538<br>700<br>900           | _<br>_<br>_<br>_            | ps   | 5     |

| MDQS preamble start                                                        | t <sub>DDKHMP</sub>                         | $-0.5 \times t_{MCK} - 0.6$ | $-0.5 \times t_{MCK} + 0.6$ | ns   | 6     |

Table 23. GMII, MII, RMII, TBI, RGMII, RTBI, and FIFO DC Electrical Characteristics

| Parameters                                                                                    | Symbol                             | Min      | Max                     | Unit | Notes   |

|-----------------------------------------------------------------------------------------------|------------------------------------|----------|-------------------------|------|---------|

| Supply voltage 2.5 V                                                                          | LV <sub>DD</sub> /TV <sub>DD</sub> | 2.37     | 2.63                    | V    | 1, 2    |

| Output high voltage (LV <sub>DD</sub> /TV <sub>DD</sub> = Min, $I_{OH} = -1.0 \text{ mA}$ )   | V <sub>OH</sub>                    | 2.00     | $LV_{DD}/TV_{DD} + 0.3$ | V    | _       |

| Output low voltage (LV <sub>DD</sub> /TV <sub>DD</sub> = Min, $I_{OL}$ = 1.0 mA)              | V <sub>OL</sub>                    | GND -0.3 | 0.40                    | V    | _       |

| Input high voltage                                                                            | V <sub>IH</sub>                    | 1.70     | $LV_{DD}/TV_{DD} + 0.3$ | V    | _       |

| Input low voltage                                                                             | V <sub>IL</sub>                    | -0.3     | 0.90                    | V    | _       |

| Input high current (V <sub>IN</sub> = LV <sub>DD</sub> , V <sub>IN</sub> = TV <sub>DD</sub> ) | I <sub>IH</sub>                    | _        | 10                      | μΑ   | 1, 2, 3 |

| Input low current (V <sub>IN</sub> = GND)                                                     | I <sub>IL</sub>                    | -15      | _                       | μΑ   | 3       |

#### Notes:

- 1. LV<sub>DD</sub> supports eTSECs 1 and 2.

- 2. TV<sub>DD</sub> supports eTSECs 3 and 4.

- 3. Note that the symbol V<sub>IN</sub>, in this case, represents the LV<sub>IN</sub> and TV<sub>IN</sub> symbols referenced in Table 1 and Table 2.

# 8.2 FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI AC Timing Specifications

The AC timing specifications for FIFO, GMII, MII, TBI, RGMII, RMII, and RTBI are presented in this section.

# 8.2.1 FIFO AC Specifications

The basis for the AC specifications for the eTSEC's FIFO modes is the double data rate RGMII and RTBI specifications, since they have similar performances and are described in a source-synchronous fashion like FIFO modes. However, the FIFO interface provides deliberate skew between the transmitted data and source clock in GMII fashion.

When the eTSEC is configured for FIFO modes, all clocks are supplied from external sources to the relevant eTSEC interface. That is, the transmit clock must be applied to the eTSECn's TSECn\_TX\_CLK, while the receive clock must be applied to pin TSECn\_RX\_CLK. The eTSEC internally uses the transmit clock to synchronously generate transmit data and outputs an echoed copy of the transmit clock back out onto the TSECn\_GTX\_CLK pin (while transmit data appears on TSECn\_TXD[7:0], for example). It is intended that external receivers capture eTSEC transmit data using the clock on TSECn\_GTX\_CLK as a source- synchronous timing reference. Typically, the clock edge that launched the data can be used, since the clock is delayed by the eTSEC to allow acceptable set-up margin at the receiver. Note that there is relationship between the maximum FIFO speed and the platform speed. For more information see Section 4.5, "Platform to FIFO Restrictions."

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

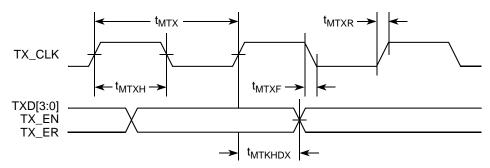

Figure 11 shows the MII transmit AC timing diagram.

Figure 11. MII Transmit AC Timing Diagram

#### 8.2.3.2 MII Receive AC Timing Specifications

This table provides the MII receive AC timing specifications.

Parameter/Condition Symbol<sup>1</sup> Min Тур Max Unit  $t_{MRX}^2$ RX\_CLK clock period 10 Mbps 400 ns RX\_CLK clock period 100 Mbps 40 ns  $t_{MRX}$ % RX\_CLK duty cycle t<sub>MRXH</sub>/t<sub>MRX</sub> 35 65 RXD[3:0], RX\_DV, RX\_ER setup time to RX\_CLK 10.0 t<sub>MRDVKH</sub> ns RXD[3:0], RX\_DV, RX\_ER hold time to RX\_CLK 10.0 ns t<sub>MRDXKH</sub>  $t_{MRXR}^2$ RX\_CLK clock rise (20%-80%) 1.0 4.0 ns  $t_{\mathsf{MRXF}}^{\phantom{\mathsf{2}}2}$ 1.0 RX\_CLK clock fall time (80%-20%) 4.0

Table 29. MII Receive AC Timing Specifications

#### Notes:

- 1. The symbols used for timing specifications follow the pattern of  $t_{\text{(first two letters of functional block)(signal)(state)(reference)(state)}}$  for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (Ď) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also,  $t_{MRDXKL}$  symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- 2. Guaranteed by design.

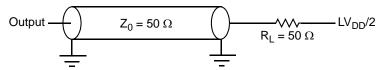

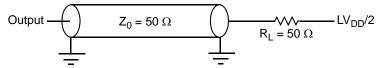

Figure 12 provides the AC test load for eTSEC.

Figure 12. eTSEC AC Test Load

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9 Freescale Semiconductor 33

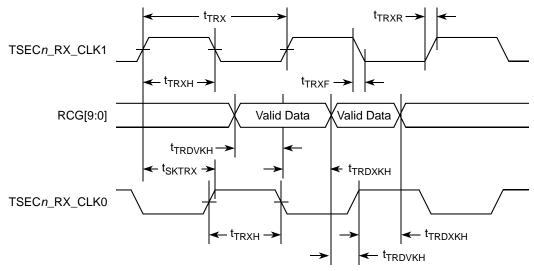

Figure 15 shows the TBI receive AC timing diagram.

Figure 15. TBI Receive AC Timing Diagram

# 8.2.5 TBI Single-Clock Mode AC Specifications

When the eTSEC is configured for TBI modes, all clocks are supplied from external sources to the relevant eTSEC interface. In single-clock TBI mode, when TBICON[CLKSEL] = 1, a 125-MHz TBI receive clock is supplied on the TSECn\_RX\_CLK pin (no receive clock is used on TSECn\_TX\_CLK in this mode, whereas for the dual-clock mode this is the PMA1 receive clock). The 125-MHz transmit clock is applied on the TSEC\_GTX\_CLK125 pin in all TBI modes.

A summary of the single-clock TBI mode AC specifications for receive appears in Table 32.

Parameter/Condition Symbol Min Max Unit Typ RX\_CLK clock period 7.5 t<sub>TRRX</sub> 8.0 8.5 ns RX\_CLK duty cycle 40 50 % 60 t<sub>TRRH/TRRX</sub> RX\_CLK peak-to-peak jitter 250 ps t<sub>TRRJ</sub> Rise time RX\_CLK (20%-80%) 1.0 ns **t**TRRR Fall time RX\_CLK (80%-20%) 1.0 ns t<sub>TRRF</sub> RCG[9:0] setup time to RX\_CLK rising edge **t**TRRDVKH 2.0 ns RCG[9:0] hold time to RX\_CLK rising edge 1.0 t<sub>TRRDXKH</sub> ns

Table 32. TBI single-clock Mode Receive AC Timing Specification

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

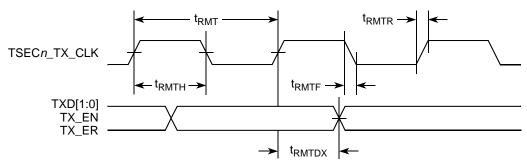

Table 34. RMII Transmit AC Timing Specifications (continued)

| Parameter/Condition                             | Symbol <sup>1</sup> | Min | Тур | Max  | Unit |

|-------------------------------------------------|---------------------|-----|-----|------|------|

| TSECn_TX_CLK to RMII data TXD[1:0], TX_EN delay | t <sub>RMTDX</sub>  | 1.0 | _   | 10.0 | ns   |

#### Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

Figure 18 shows the RMII transmit AC timing diagram.

Figure 18. RMII Transmit AC Timing Diagram

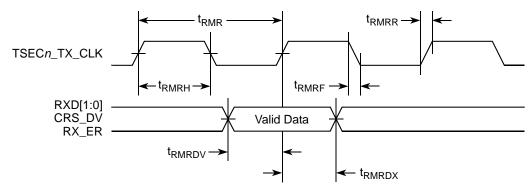

## 8.2.7.2 RMII Receive AC Timing Specifications

**Table 35. RMII Receive AC Timing Specifications**

| Parameter/Condition                                       | Symbol <sup>1</sup> | Min  | Тур  | Max  | Unit |

|-----------------------------------------------------------|---------------------|------|------|------|------|

| TSECn_TX_CLK clock period                                 | t <sub>RMR</sub>    | 15.0 | 20.0 | 25.0 | ns   |

| TSECn_TX_CLK duty cycle                                   | t <sub>RMRH</sub>   | 35   | 50   | 65   | %    |

| TSECn_TX_CLK peak-to-peak jitter                          | t <sub>RMRJ</sub>   | _    | _    | 250  | ps   |

| Rise time TSECn_TX_CLK(20%–80%)                           | t <sub>RMRR</sub>   | 1.0  | _    | 2.0  | ns   |

| Fall time TSECn_TX_CLK (80%–20%)                          | t <sub>RMRF</sub>   | 1.0  | _    | 2.0  | ns   |

| RXD[1:0], CRS_DV, RX_ER setup time to REF_CLK rising edge | t <sub>RMRDV</sub>  | 4.0  | _    | _    | ns   |

| RXD[1:0], CRS_DV, RX_ER hold time to REF_CLK rising edge  | t <sub>RMRDX</sub>  | 2.0  | _    | _    | ns   |

#### Note:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state)</sub> for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

#### **Enhanced Three-Speed Ethernet (eTSEC)**

Figure 19 provides the AC test load for eTSEC.

Figure 19. eTSEC AC Test Load

Figure 20 shows the RMII receive AC timing diagram.

Figure 20. RMII Receive AC Timing Diagram

#### **Local Bus**

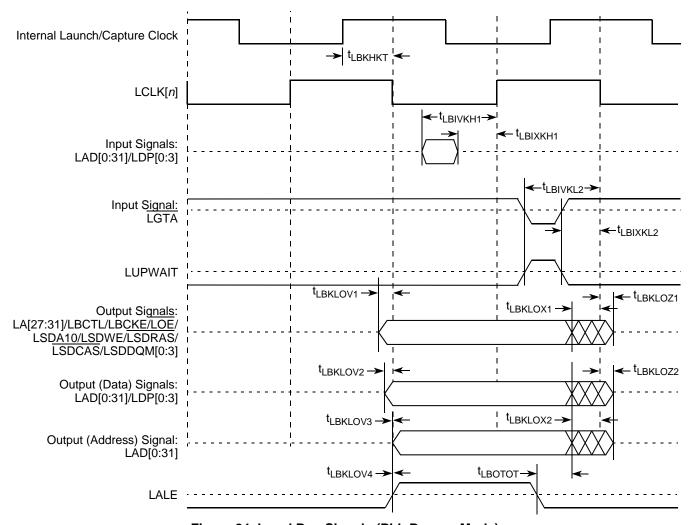

Figure 24. Local Bus Signals (PLL Bypass Mode)

## **NOTE**

In PLL bypass mode, LCLK[n] is the inverted version of the internal clock with the delay of  $t_{LBKHKT}$ . In this mode, signals are launched at the rising edge of the internal clock and are captured at falling edge of the internal clock with the exception of  $\overline{LGTA}/LUPWAIT$  (which is captured on the rising edge of the internal clock).

## **PCI Express**

Table 57. Differential Receiver (RX) Input Specifications (continued)

| Symbol                           | Parameter                                                          | Min   | Nom | Max | Unit | Comments                                                                                                                                                                                                                                     |

|----------------------------------|--------------------------------------------------------------------|-------|-----|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>RX-CM-ACp</sub>           | AC peak<br>common mode<br>input voltage                            | _     | _   | 150 | mV   | $\begin{split} &V_{\text{RX-CM-ACp}} =  V_{\text{RXD+}} - V_{\text{RXD-}} /2 + V_{\text{RX-CM-DC}} \\ &V_{\text{RX-CM-DC}} = DC_{\text{(avg)}} \text{ of }  V_{\text{RX-D+}} + V_{\text{RX-D-}}  \div 2. \\ &\text{See Note 2}. \end{split}$ |

| RL <sub>RX-DIFF</sub>            | Differential return loss                                           | 15    | _   | _   | dB   | Measured over 50 MHz to 1.25 GHz with the D+ and D- lines biased at +300 mV and -300 mV, respectively. See Note 4.                                                                                                                           |

| RL <sub>RX-CM</sub>              | Common mode return loss                                            | 6     | _   | _   | dB   | Measured over 50 MHz to 1.25 GHz with the D+ and D- lines biased at 0 V. See Note 4.                                                                                                                                                         |

| Z <sub>RX-DIFF-DC</sub>          | DC differential input impedance                                    | 80    | 100 | 120 | Ω    | RX DC differential mode impedance. See Note 5.                                                                                                                                                                                               |

| Z <sub>RX-DC</sub>               | DC input impedance                                                 | 40    | 50  | 60  | Ω    | Required RX D+ as well as D– DC impedance (50 ± 20% tolerance). See Notes 2 and 5.                                                                                                                                                           |

| Z <sub>RX-HIGH-IMP-DC</sub>      | Powered down<br>DC input<br>impedance                              | 200 k | _   | _   | Ω    | Required RX D+ as well as D– DC impedance when the receiver terminations do not have power. See Note 6.                                                                                                                                      |

| V <sub>RX-IDLE-DET-DIFFp-p</sub> | Electrical idle detect threshold                                   | 65    | _   | 175 | mV   | $V_{RX-IDLE-DET-DIFFp-p} = 2 \times  V_{RX-D+} - V_{RX-D-} .$ Measured at the package pins of the receiver                                                                                                                                   |

| T <sub>RX-IDLE-DET-DIFF</sub>    | Unexpected electrical idle enter detect threshold integration time | _     | _   | 10  | ms   | An unexpected electrical idle ( $V_{RX-DIFFp-p} < V_{RX-IDLE-DET-DIFFp-p}$ ) must be recognized no longer than $T_{RX-IDLE-DET-DIFF-ENTERING}$ to signal an unexpected idle condition.                                                       |

# **18.3 Signal Definitions**

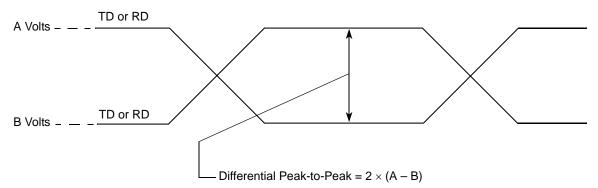

LP-serial links use differential signaling. This section defines terms used in the description and specification of differential signals. Figure 51 shows how the signals are defined. The figures show waveforms for either a transmitter output (TD and  $\overline{\text{TD}}$ ) or a receiver input (RD and  $\overline{\text{RD}}$ ). Each signal swings between A volts and B volts where A > B. Using these waveforms, the definitions are as follows:

- 1. The transmitter output signals and the receiver input signals TD, TD, RD, and RD each have a peak-to-peak swing of A B volts.

- 2. The differential output signal of the transmitter,  $V_{OD}$ , is defined as  $V_{TD} V_{\overline{TD}}$ .

- 3. The differential input signal of the receiver,  $V_{ID}$ , is defined as  $V_{RD} V_{\overline{RD}}$ .

- 4. The differential output signal of the transmitter and the differential input signal of the receiver each range from A B to -(A B) volts.

- 5. The peak value of the differential transmitter output signal and the differential receiver input signal is A B volts.

- 6. The peak-to-peak value of the differential transmitter output signal and the differential receiver input signal is  $2 \times (A B)$  volts.

Figure 51. Differential Peak-Peak Voltage of Transmitter or Receiver

To illustrate these definitions using real values, consider the case of a CML (current mode logic) transmitter that has a common mode voltage of 2.25 V and each of its outputs, TD and  $\overline{\text{TD}}$ , has a swing that goes between 2.5 and 2.0 V. Using these values, the peak-to-peak voltage swing of the signals TD and  $\overline{\text{TD}}$  is 500 mVp-p. The differential output signal ranges between 500 and -500 mV. The peak differential voltage is 500 mV. The peak-to-peak differential voltage is 1000 mVp-p.

# 18.4 Equalization

With the use of high-speed serial links, the interconnect media causes degradation of the signal at the receiver. Effects such as inter-symbol interference (ISI) or data dependent jitter are produced. This loss can be large enough to degrade the eye opening at the receiver beyond what is allowed in the specification. To negate a portion of these effects, equalization can be used. The most common equalization techniques that can be used are:

- A passive high pass filter network placed at the receiver. This is often referred to as passive equalization.

- The use of active circuits in the receiver. This is often referred to as adaptive equalization.

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

87

components are included in this requirement. The reference impedance for return loss measurements is  $100-\Omega$  resistive for differential return loss and  $25-\Omega$  resistive for common mode.

Table 66. Receiver AC Timing Specifications—1.25 GBaud

| Characteristic                                     | Symbol          | Range |                   | Unit   | Notes                                                        |

|----------------------------------------------------|-----------------|-------|-------------------|--------|--------------------------------------------------------------|

| Characteristic                                     | Symbol          | Min   | Max               | Oilit  | Notes                                                        |

| Differential input voltage                         | V <sub>IN</sub> | 200   | 1600              | mVp-p  | Measured at receiver                                         |

| Deterministic jitter tolerance                     | $J_D$           | 0.37  | _                 | UI p-p | Measured at receiver                                         |

| Combined deterministic and random jitter tolerance | J <sub>DR</sub> | 0.55  | _                 | UI p-p | Measured at receiver                                         |

| Total jitter tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65  | _                 | UI p-p | Measured at receiver                                         |

| Multiple input skew                                | S <sub>MI</sub> | _     | 24                | ns     | Skew at the receiver input between lanes of a multilane link |

| Bit error rate                                     | BER             | _     | 10 <sup>-12</sup> | _      | _                                                            |

| Unit interval                                      | UI              | 800   | 800               | ps     | ±100 ppm                                                     |

#### Note:

Table 67. Receiver AC Timing Specifications—2.5 GBaud

| Characteristic                                     | Symbol          | Range |                   | Unit   | Notes                                                        |

|----------------------------------------------------|-----------------|-------|-------------------|--------|--------------------------------------------------------------|

| Gharacteristic                                     | Gymbol          | Min   | Max               | Oilit  | Notes                                                        |

| Differential input voltage                         | V <sub>IN</sub> | 200   | 1600              | mVp-p  | Measured at receiver                                         |

| Deterministic jitter tolerance                     | $J_D$           | 0.37  | _                 | UI p-p | Measured at receiver                                         |

| Combined deterministic and random jitter tolerance | J <sub>DR</sub> | 0.55  | _                 | UI p-p | Measured at receiver                                         |

| Total jitter tolerance <sup>1</sup>                | J <sub>T</sub>  | 0.65  | _                 | UI p-p | Measured at receiver                                         |

| Multiple input skew                                | S <sub>MI</sub> | _     | 24                | ns     | Skew at the receiver input between lanes of a multilane link |

| Bit error rate                                     | BER             | _     | 10 <sup>-12</sup> |        | _                                                            |

| Unit interval                                      | UI              | 400   | 400               | ps     | ±100 ppm                                                     |

#### Note:

<sup>1.</sup> Total jitter is composed of three components, deterministic jitter, random jitter, and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 53. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk, and other variable system effects.

<sup>1.</sup> Total jitter is composed of three components, deterministic jitter, random jitter, and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 53. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk, and other variable system effects.

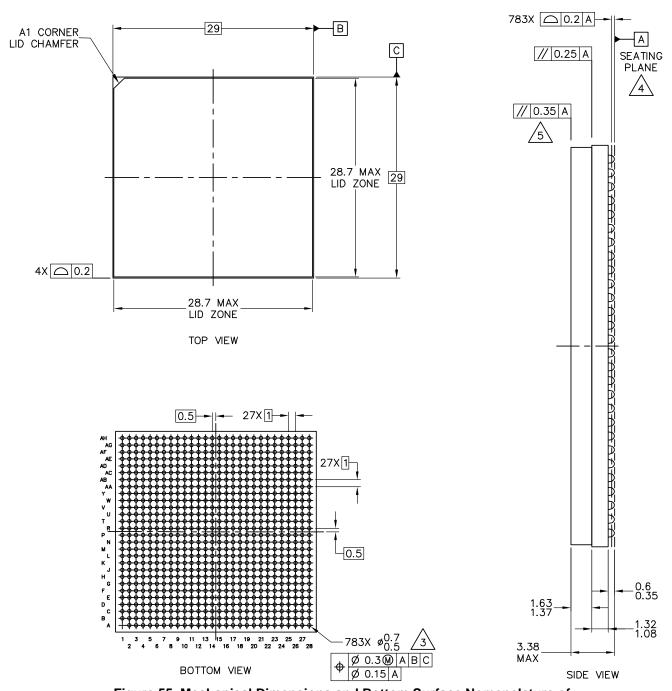

# 19.2 Mechanical Dimensions of the HiCTE FC-CBGA and FC-PBGA with Full Lid

The following figures show the mechanical dimensions and bottom surface nomenclature for the MPC8548E HiCTE FC-CBGA and FC-PBGA packages.

Figure 55. Mechanical Dimensions and Bottom Surface Nomenclature of the HiCTE FC-CBGA and FC-PBGA with Full Lid

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

## **Package Description**

Table 71. MPC8548E Pinout Listing (continued)

| Signal                 | Package Pin Number                                                                                                                                                                                                                                                                             | Pin Type | Power<br>Supply  | Notes    |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

| PCI1_REQ[4:1]          | AH2, AG4, AG3, AH4                                                                                                                                                                                                                                                                             | I        | OV <sub>DD</sub> | _        |

|                        |                                                                                                                                                                                                                                                                                                |          |                  | _        |

|                        |                                                                                                                                                                                                                                                                                                |          |                  | _        |

|                        |                                                                                                                                                                                                                                                                                                |          |                  | _        |

|                        |                                                                                                                                                                                                                                                                                                |          |                  | _        |

| PCI1_REQ0              | AH3                                                                                                                                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | _        |

| PCI1_CLK               | AH26                                                                                                                                                                                                                                                                                           | I        | OV <sub>DD</sub> | 39       |

| PCI1_DEVSEL            | AH11                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_FRAME             | AE11                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_IDSEL             | AG9                                                                                                                                                                                                                                                                                            | I        | OV <sub>DD</sub> | _        |

| PCI1_REQ64/PCI2_FRAME  | AF14                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2, 5, 10 |

| PCI1_ACK64/PCI2_DEVSEL | V15                                                                                                                                                                                                                                                                                            | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_CLK               | AE28                                                                                                                                                                                                                                                                                           | I        | OV <sub>DD</sub> | 39       |

| PCI2_IRDY              | AD26                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_PERR              | AD25                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_GNT[4:1]          | AE26, AG24, AF25, AE25                                                                                                                                                                                                                                                                         | 0        | OV <sub>DD</sub> | 5, 9, 35 |

| PCI2_GNT0              | AG25                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | _        |

| PCI2_SERR              | AD24                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2, 4     |

| PCI2_STOP              | AF24                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_TRDY              | AD27                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_REQ[4:1]          | AD28, AE27, W17, AF26                                                                                                                                                                                                                                                                          | I        | OV <sub>DD</sub> | _        |

| PCI2_REQ0              | AH25                                                                                                                                                                                                                                                                                           | I/O      | OV <sub>DD</sub> | _        |

|                        | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                     |          |                  | - I      |

| MDQ[0:63]              | L18, J18, K14, L13, L19, M18, L15, L14, A17, B17, A13, B12, C18, B18, B13, A12, H18, F18, J14, F15, K19, J19, H16, K15, D17, G16, K13, D14, D18, F17, F14, E14, A7, A6, D5, A4, C8, D7, B5, B4, A2, B1, D1, E4, A3, B2, D2, E3, F3, G4, J5, K5, F6, G5, J6, K4, J1, K2, M5, M3, J3, J2, L1, M6 | I/O      | GV <sub>DD</sub> | _        |

| MECC[0:7]              | H13, F13, F11, C11, J13, G13, D12, M12                                                                                                                                                                                                                                                         | I/O      | GV <sub>DD</sub> | _        |

| MDM[0:8]               | M17, C16, K17, E16, B6, C4, H4, K1, E13                                                                                                                                                                                                                                                        | 0        | GV <sub>DD</sub> | _        |

| MDQS[0:8]              | M15, A16, G17, G14, A5, D3, H1, L2, C13                                                                                                                                                                                                                                                        | I/O      | GV <sub>DD</sub> | _        |

| MDQS[0:8]              | L17, B16, J16, H14, C6, C2, H3, L4, D13                                                                                                                                                                                                                                                        | I/O      | GV <sub>DD</sub> | _        |

| MA[0:15]               | A8, F9, D9, B9, A9, L10, M10, H10, K10, G10,<br>B8, E10, B10, G6, A10, L11                                                                                                                                                                                                                     | 0        | GV <sub>DD</sub> | _        |

| MBA[0:2]               | F7, J7, M11                                                                                                                                                                                                                                                                                    | 0        | GV <sub>DD</sub> | _        |

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

## **Package Description**

Table 71. MPC8548E Pinout Listing (continued)

| Signal             | Package Pin Number                               | Pin Type | Power<br>Supply  | Notes        |

|--------------------|--------------------------------------------------|----------|------------------|--------------|

| LSYNC_IN           | F27                                              | l        | BV <sub>DD</sub> | _            |

| LSYNC_OUT          | F28                                              | 0        | BV <sub>DD</sub> | _            |

|                    | DMA                                              |          |                  |              |

| DMA_DACK[0:1]      | AD3, AE1                                         | 0        | OV <sub>DD</sub> | 5, 9,<br>102 |

| DMA_DREQ[0:1]      | AD4, AE2                                         | I        | OV <sub>DD</sub> | _            |

| DMA_DDONE[0:1]     | AD2, AD1                                         | 0        | OV <sub>DD</sub> | _            |

|                    | Programmable Interrupt Controller                |          |                  |              |

| UDE                | AH16                                             | ļ        | OV <sub>DD</sub> | _            |

| MCP                | AG19                                             | I        | OV <sub>DD</sub> | _            |

| IRQ[0:7]           | AG23, AF18, AE18, AF20, AG18, AF17, AH24, AE20   | I        | OV <sub>DD</sub> | _            |

| IRQ[8]             | AF19                                             | I        | OV <sub>DD</sub> | _            |

| IRQ[9]/DMA_DREQ3   | AF21                                             | I        | OV <sub>DD</sub> | 1            |

| IRQ[10]/DMA_DACK3  | AE19                                             | I/O      | OV <sub>DD</sub> | 1            |

| IRQ[11]/DMA_DDONE3 | AD20                                             | I/O      | OV <sub>DD</sub> | 1            |

| IRQ_OUT            | AD18                                             | 0        | OV <sub>DD</sub> | 2, 4         |

|                    | Ethernet Management Interface                    |          |                  |              |

| EC_MDC             | AB9                                              | 0        | OV <sub>DD</sub> | 5, 9         |

| EC_MDIO            | AC8                                              | I/O      | OV <sub>DD</sub> | _            |

|                    | Gigabit Reference Clock                          |          |                  |              |

| EC_GTX_CLK125      | V11                                              | I        | LV <sub>DD</sub> | _            |

|                    | Three-Speed Ethernet Controller (Gigabit Etherne | et 1)    | 1                | 1            |

| TSEC1_RXD[7:0]     | R5, U1, R3, U2, V3, V1, T3, T2                   | ļ        | LV <sub>DD</sub> | _            |

| TSEC1_TXD[7:0]     | T10, V7, U10, U5, U4, V6, T5, T8                 | 0        | LV <sub>DD</sub> | 5, 9         |

| TSEC1_COL          | R4                                               | ļ        | LV <sub>DD</sub> | _            |

| TSEC1_CRS          | V5                                               | I/O      | LV <sub>DD</sub> | 20           |

| TSEC1_GTX_CLK      | U7                                               | 0        | LV <sub>DD</sub> | _            |

| TSEC1_RX_CLK       | U3                                               | ļ        | LV <sub>DD</sub> | _            |

| TSEC1_RX_DV        | V2                                               | I        | LV <sub>DD</sub> | _            |

| TSEC1_RX_ER        | T1                                               | I        | LV <sub>DD</sub> | _            |

| TSEC1_TX_CLK       | Т6                                               | I        | LV <sub>DD</sub> | _            |

| TSEC1_TX_EN        | U9                                               | 0        | LV <sub>DD</sub> | 30           |

| TSEC1_TX_ER        | Т7                                               | 0        | LV <sub>DD</sub> | _            |

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

Table 71. MPC8548E Pinout Listing (continued)

| Signal           | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Pin Type                                           | Power<br>Supply  | Notes        |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------|--------------|--|--|

| Clock            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                    |                  |              |  |  |

| RTC              | AF16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                  | OV <sub>DD</sub> | _            |  |  |

| SYSCLK           | AH17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                  | OV <sub>DD</sub> | <u> </u>     |  |  |

|                  | JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                    |                  | •            |  |  |

| TCK              | AG28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                  | $OV_{DD}$        | _            |  |  |

| TDI              | AH28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Ţ                                                  | $OV_{DD}$        | 12           |  |  |

| TDO              | AF28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                  | OV <sub>DD</sub> | <u> </u>     |  |  |

| TMS              | AH27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                  | $OV_{DD}$        | 12           |  |  |

| TRST             | AH23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                  | OV <sub>DD</sub> | 12           |  |  |

|                  | DFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                    |                  | •            |  |  |

| L1_TSTCLK        | AC25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Ţ                                                  | $OV_{DD}$        | 25           |  |  |

| L2_TSTCLK        | AE22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Ţ                                                  | $OV_{DD}$        | 25           |  |  |

| LSSD_MODE        | AH20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                  | $OV_{DD}$        | 25           |  |  |

| TEST_SEL         | AH14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I                                                  | $OV_{DD}$        | 25           |  |  |

|                  | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                    |                  | •            |  |  |

| THERM0           | AG1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                  | _                | 14           |  |  |

| THERM1           | AH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                                  | _                | 14           |  |  |

|                  | Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                    |                  | •            |  |  |

| ASLEEP           | AH18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                  | $OV_{DD}$        | 9, 19,<br>29 |  |  |

|                  | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                    |                  | -            |  |  |

| GND              | A11, B7, B24, C1, C3, C5, C12, C15, C26, D8, D11, D16, D20, D22, E1, E5, E9, E12, E15, E17, F4, F26, G12, G15, G18, G21, G24, H2, H6, H8, H28, J4, J12, J15, J17, J27, K7, K9, K11, K27, L3, L5, L12, L16, N11, N13, N15, N17, N19, P4, P9, P12, P14, P16, P18, R11, R13, R15, R17, R19, T4, T12, T14, T16, T18, U8, U11, U13, U15, U17, U19, V4, V12, V18, W6, W19, Y4, Y9, Y11, Y19, AA6, AA14, AA17, AA22, AA23, AB4, AC2, AC11, AC19, AC26, AD5, AD9, AD22, AE3, AE14, AF6, AF10, AF13, AG8, AG27, K28, L24, L26, N24, N27, P25, R28, T24, T26, U24, V25, W28, Y24, Y26, AA24, AA27, AB25, AC28, L21, L23, N22, P20, R23, T21, U22, V20, W23, Y21, U27 |                                                    | _                | _            |  |  |

| OV <sub>DD</sub> | V16, W11, W14, Y18, AA13, AA21, AB11,<br>AB17, AB24, AC4, AC9, AC21, AD6, AD13,<br>AD17, AD19, AE10, AE8, AE24, AF4, AF12,<br>AF22, AF27, AG26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Power for PCI<br>and other<br>standards<br>(3.3 V) | OV <sub>DD</sub> | _            |  |  |

## Table 71. MPC8548E Pinout Listing (continued)

| Signal | Package Pin Number | Pin Type | Power<br>Supply | Notes |  |

|--------|--------------------|----------|-----------------|-------|--|

|--------|--------------------|----------|-----------------|-------|--|

- 25. These are test signals for factory use only and must be pulled up (100  $\Omega$ –1 k $\Omega$ ) to OV<sub>DD</sub> for normal machine operation.

- 26.Independent supplies derived from board V<sub>DD</sub>.

- 27.Recommend a pull-up resistor (~1 k $\Omega$ ) be placed on this pin to OV<sub>DD</sub>.

- 29. The following pins must NOT be pulled down during power-on reset: TSEC3\_TXD[3], TSEC4\_TXD3/TSEC3\_TXD7, HRESET\_REQ, TRIG\_OUT/READY/QUIESCE, MSRCID[2:4], ASLEEP.

- 30. This pin requires an external 4.7-k $\Omega$  pull-down resistor to prevent PHY from seeing a valid transmit enable before it is actively driven.

- 31. This pin is only an output in eTSEC3 FIFO mode when used as Rx flow control.

- 32. These pins must be connected to XV<sub>DD</sub>.

- 33.TSEC2\_TXD1, TSEC2\_TX\_ER are multiplexed as cfg\_dram\_type[0:1]. They must be valid at power-up, even before HRESET assertion.

- 34. These pins must be pulled to ground through a 300- $\Omega$  (±10%) resistor.

- 35.When a PCI block is disabled, either the POR config pin that selects between internal and external arbiter must be pulled down to select external arbiter if there is any other PCI device connected on the PCI bus, or leave the PCIn\_AD pins as 'no connect' or terminated through 2–10 kΩ pull-up resistors with the default of internal arbiter if the PCIn\_AD pins are not connected to any other PCI device. The PCI block drives the PCIn\_AD pins if it is configured to be the PCI arbiter—through POR config pins—irrespective of whether it is disabled via the DEVDISR register or not. It may cause contention if there is any other PCI device connected on the bus.

- 36.MDIC0 is grounded through an 18.2- $\Omega$  precision 1% resistor and MDIC1 is connected to GV<sub>DD</sub> through an 18.2- $\Omega$  precision 1% resistor. These pins are used for automatic calibration of the DDR IOs.

- 38. These pins must be left floating.

- 39. If PCI1 or PCI2 is configured as PCI asynchronous mode, a valid clock must be provided on pin PCI1\_CLK or PCI2\_CLK. Otherwise the processor will not boot up.

- 40. These pins must be connected to GND.

- 101. This pin requires an external 4.7-k $\Omega$  resistor to GND.

- 102.For Rev. 2.x silicon, DMA\_DACK[0:1] must be 0b11 during POR configuration; for rev. 1.x silicon, the pin values during POR configuration are don't care.

- 103.If these pins are not used as GPINn (general-purpose input), they must be pulled low (to GND) or high (to  $LV_{DD}$ ) through 2–10 k $\Omega$  resistors.

- 104. These must be pulled low to GND through 2–10 k $\Omega$  resistors if they are not used.

- 105. These must be pulled low or high to  $LV_{DD}$  through 2–10 k $\Omega$  resistors if they are not used.

- 106. For rev. 2.x silicon, DMA\_DACK[0:1] must be 0b10 during POR configuration; for rev. 1.x silicon, the pin values during POR configuration are don't care.

- 107.For rev. 2.x silicon, DMA\_DACK[0:1] must be 0b01 during POR configuration; for rev. 1.x silicon, the pin values during POR configuration are don't care.

- 108.For rev. 2.x silicon, DMA\_DACK[0:1] must be 0b11 during POR configuration; for rev. 1.x silicon, the pin values during POR configuration are don't care.

- 109. This is a test signal for factory use only and must be pulled down (100  $\Omega$  1 k $\Omega$ ) to GND for normal machine operation.

- 110. These pins must be pulled high to  $OV_{DD}$  through 2–10 k $\Omega$  resistors.

- 111.If these pins are not used as GPINn (general-purpose input), they must be pulled low (to GND) or high (to OV<sub>DD</sub>) through 2–10 k $\Omega$  resistors.

- 112. This pin must not be pulled down during POR configuration.

- 113.These should be pulled low or high to  ${\rm OV_{DD}}$  through 2–10 k $\Omega$  resistors.

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

## **Package Description**

Table 73. MPC8545E Pinout Listing (continued)

| Signal                | Package Pin Number                              | Pin Type | Power<br>Supply  | Notes    |

|-----------------------|-------------------------------------------------|----------|------------------|----------|

| UDE                   | AH16                                            | I        | OV <sub>DD</sub> | _        |

| MCP                   | AG19                                            | I        | OV <sub>DD</sub> | _        |

| IRQ[0:7]              | AG23, AF18, AE18, AF20, AG18, AF17, AH24, AE20  | I        | OV <sub>DD</sub> | _        |

| IRQ[8]                | AF19                                            | I        | OV <sub>DD</sub> | _        |

| IRQ[9]/DMA_DREQ3      | AF21                                            | I        | OV <sub>DD</sub> | 1        |

| IRQ[10]/DMA_DACK3     | AE19                                            | I/O      | OV <sub>DD</sub> | 1        |

| IRQ[11]/DMA_DDONE3    | AD20                                            | I/O      | OV <sub>DD</sub> | 1        |

| IRQ_OUT               | AD18                                            | 0        | OV <sub>DD</sub> | 2, 4     |

|                       | Ethernet Management Interface                   |          | 1                | <b>.</b> |

| EC_MDC                | AB9                                             | 0        | OV <sub>DD</sub> | 5, 9     |

| EC_MDIO               | AC8                                             | I/O      | OV <sub>DD</sub> | _        |

|                       | Gigabit Reference Clock                         |          |                  |          |

| EC_GTX_CLK125         | V11                                             | I        | LV <sub>DD</sub> |          |

|                       | Three-Speed Ethernet Controller (Gigabit Ethern | et 1)    |                  |          |

| TSEC1_RXD[7:0]        | R5, U1, R3, U2, V3, V1, T3, T2                  | I        | LV <sub>DD</sub> | _        |

| TSEC1_TXD[7:0]        | T10, V7, U10, U5, U4, V6, T5, T8                | 0        | LV <sub>DD</sub> | 5, 9     |

| TSEC1_COL             | R4                                              | I        | LV <sub>DD</sub> | _        |

| TSEC1_CRS             | V5                                              | I/O      | LV <sub>DD</sub> | 20       |

| TSEC1_GTX_CLK         | U7                                              | 0        | LV <sub>DD</sub> | _        |

| TSEC1_RX_CLK          | U3                                              | I        | LV <sub>DD</sub> | _        |

| TSEC1_RX_DV           | V2                                              | I        | LV <sub>DD</sub> | _        |

| TSEC1_RX_ER           | T1                                              | I        | LV <sub>DD</sub> | _        |

| TSEC1_TX_CLK          | Т6                                              | I        | LV <sub>DD</sub> | _        |

| TSEC1_TX_EN           | U9                                              | 0        | LV <sub>DD</sub> | 30       |

| TSEC1_TX_ER           | Т7                                              | 0        | LV <sub>DD</sub> | <u> </u> |

| GPIN[0:7]             | P2, R2, N1, N2, P3, M2, M1, N3                  | I        | LV <sub>DD</sub> | 103      |

| GPOUT[0:5]            | N9, N10, P8, N7, R9, N5                         | 0        | LV <sub>DD</sub> | -        |

| cfg_dram_type0/GPOUT6 | R8                                              | 0        | LV <sub>DD</sub> | 5, 9     |

| GPOUT7                | N6                                              | 0        | LV <sub>DD</sub> | -        |

| Reserved              | P1                                              | _        | _                | 104      |

| Reserved              | R6                                              | _        | <u> </u>         | 104      |

| Reserved              | P6                                              | _        | <u> </u>         | 15       |

| Reserved              | N4                                              | _        | _                | 105      |

MPC8548E PowerQUICC III Integrated Processor Hardware Specifications, Rev. 9

Table 73. MPC8545E Pinout Listing (continued)

| Signal        | Package Pin Number | Pin Type | Power<br>Supply | Notes |

|---------------|--------------------|----------|-----------------|-------|

| SD_IMP_CAL_RX | L28                | I        | 200 Ω to<br>GND | _     |

| SD_IMP_CAL_TX | AB26               | I        | 100 Ω to<br>GND | _     |

| SD_PLL_TPA    | U26                | 0        | _               | 24    |

**Note:** All note references in this table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

Table 74 provides the pin-out listing for the MPC8543E 783 FC-PBGA package.

## **NOTE**

All note references in the following table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

Table 74. MPC8543E Pinout Listing

| Signal         | Package Pin Number                                                                                                                                                                            | Pin Type | Power<br>Supply  | Notes    |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

|                | PCI1 (One 32-Bit)                                                                                                                                                                             |          | 1                |          |

| Reserved       | AB14, AC15, AA15, Y16, W16, AB16, AC16, AA16, AE17, AA18, W18, AC17, AD16, AE16, Y17, AC18,                                                                                                   | _        | _                | 110      |

| GPOUT[8:15]    | AB18, AA19, AB19, AB21, AA20, AC20, AB20, AB22                                                                                                                                                | 0        | OV <sub>DD</sub> | _        |

| GPIN[8:15]     | AC22, AD21, AB23, AF23, AD23, AE23, AC23, AC24                                                                                                                                                | I        | OV <sub>DD</sub> | 111      |

| PCI1_AD[31:0]  | AH6, AE7, AF7, AG7, AH7, AF8, AH8, AE9,<br>AH9, AC10, AB10, AD10, AG10, AA10, AH10,<br>AA11, AB12, AE12, AG12, AH12, AB13, AA12,<br>AC13, AE13, Y14, W13, AG13, V14, AH13,<br>AC14, Y15, AB15 | I/O      | OV <sub>DD</sub> | 17       |

| Reserved       | AF15, AD14, AE15, AD15                                                                                                                                                                        | _        | _                | 110      |

| PCI1_C_BE[3:0] | AF9, AD11, Y12, Y13                                                                                                                                                                           | I/O      | $OV_{DD}$        | 17       |

| Reserved       | W15                                                                                                                                                                                           | _        | _                | 110      |

| PCI1_GNT[4:1]  | AG6, AE6, AF5, AH5                                                                                                                                                                            | 0        | $OV_DD$          | 5, 9, 35 |