#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

ĿХF

| Product Status                  | Obsolete                                                   |

|---------------------------------|------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                               |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                             |

| Speed                           | 1.0GHz                                                     |

| Co-Processors/DSP               | Signal Processing; SPE                                     |

| RAM Controllers                 | DDR, DDR2, SDRAM                                           |

| Graphics Acceleration           | No                                                         |

| Display & Interface Controllers | -                                                          |

| Ethernet                        | 10/100/1000Mbps (4)                                        |

| SATA                            | -                                                          |

| USB                             | -                                                          |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                           |

| Operating Temperature           | 0°C ~ 105°C (TA)                                           |

| Security Features               | -                                                          |

| Package / Case                  | 783-BBGA, FCBGA                                            |

| Supplier Device Package         | 783-FCPBGA (29x29)                                         |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8548vtaqgd |

|                                 |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Performance monitor facility that is similar to, but separate from, the device performance monitor

The e500 defines features that are not implemented on this device. It also generally defines some features that this device implements more specifically. An understanding of these differences can be critical to ensure proper operations.

- 512-Kbyte L2 cache/SRAM

- Flexible configuration.

- Full ECC support on 64-bit boundary in both cache and SRAM modes

- Cache mode supports instruction caching, data caching, or both.

- External masters can force data to be allocated into the cache through programmed memory ranges or special transaction types (stashing).

- 1, 2, or 4 ways can be configured for stashing only.

- Eight-way set-associative cache organization (32-byte cache lines)

- Supports locking entire cache or selected lines. Individual line locks are set and cleared through Book E instructions or by externally mastered transactions.

- Global locking and Flash clearing done through writes to L2 configuration registers

- Instruction and data locks can be Flash cleared separately.

- SRAM features include the following:

- I/O devices access SRAM regions by marking transactions as snoopable (global).

- Regions can reside at any aligned location in the memory map.

- Byte-accessible ECC is protected using read-modify-write transaction accesses for smaller-than-cache-line accesses.

- Address translation and mapping unit (ATMU)

- Eight local access windows define mapping within local 36-bit address space.

- Inbound and outbound ATMUs map to larger external address spaces.

- Three inbound windows plus a configuration window on PCI/PCI-X and PCI Express

- Four inbound windows plus a default window on RapidIO<sup>™</sup>

- Four outbound windows plus default translation for PCI/PCI-X and PCI Express

- Eight outbound windows plus default translation for RapidIO with segmentation and sub-segmentation support

- DDR/DDR2 memory controller

- Programmable timing supporting DDR and DDR2 SDRAM

- 64-bit data interface

- Four banks of memory supported, each up to 4 Gbytes, to a maximum of 16 Gbytes

- DRAM chip configurations from 64 Mbits to 4 Gbits with ×8/×16 data ports

- Full ECC support

- Page mode support

- Up to 16 simultaneous open pages for DDR

#### Overview

- Single inbound doorbell message structure

- Facility to accept port-write messages

- PCI Express interface

- PCI Express 1.0a compatible

- Supports x8,x4,x2, and x1 link widths

- Auto-detection of number of connected lanes

- Selectable operation as root complex or endpoint

- Both 32- and 64-bit addressing

- 256-byte maximum payload size

- Virtual channel 0 only

- Traffic class 0 only

- Full 64-bit decode with 32-bit wide windows

- Pin multiplexing for the high-speed I/O interfaces supports one of the following configurations:

- 8 PCI Express

- 4 PCI Express and 4 serial RapidIO

- Power management

- Supports power saving modes: doze, nap, and sleep

- Employs dynamic power management, which automatically minimizes power consumption of blocks when they are idle

- System performance monitor

- Supports eight 32-bit counters that count the occurrence of selected events

- Ability to count up to 512 counter-specific events

- Supports 64 reference events that can be counted on any of the eight counters

- Supports duration and quantity threshold counting

- Burstiness feature that permits counting of burst events with a programmable time between bursts

- Triggering and chaining capability

- Ability to generate an interrupt on overflow

- System access port

- Uses JTAG interface and a TAP controller to access entire system memory map

- Supports 32-bit accesses to configuration registers

- Supports cache-line burst accesses to main memory

- Supports large block (4-Kbyte) uploads and downloads

- Supports continuous bit streaming of entire block for fast upload and download

- JTAG boundary scan, designed to comply with IEEE Std. 1149.1<sup>TM</sup>

# 4.5 Platform to FIFO Restrictions

Note the following FIFO maximum speed restrictions based on platform speed.

For FIFO GMII mode:

FIFO TX/RX clock frequency ≤ platform clock frequency/4.2

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency must be no more than 127 MHz.

For FIFO encoded mode:

FIFO TX/RX clock frequency  $\leq$  platform clock frequency/4.2

For example, if the platform frequency is 533 MHz, the FIFO TX/RX clock frequency must be no more than 167 MHz.

## 4.6 Platform Frequency Requirements for PCI-Express and Serial RapidIO

The CCB clock frequency must be considered for proper operation of the high-speed PCI-Express and Serial RapidIO interfaces as described below.

For proper PCI Express operation, the CCB clock frequency must be greater than:

See *MPC8548ERM*, *Rev.* 2, *PowerQUICC III Integrated Processor Family Reference Manual*, Section 18.1.3.2, "Link Width," for PCI Express interface width details.

For proper serial RapidIO operation, the CCB clock frequency must be greater than:

$2 \times (0.80) \times (Serial RapidIO interface frequency) \times (Serial RapidIO link width)$

64

See *MPC8548ERM*, *Rev.* 2, *PowerQUICC III Integrated Processor Family Reference Manual*, Section 17.4, "1x/4x LP-Serial Signal Descriptions," for serial RapidIO interface width and frequency details.

# 4.7 Other Input Clocks

For information on the input clocks of other functional blocks of the platform see the specific section of this document.

Table 13 provides the recommended operating conditions for the DDR SDRAM controller when  $GV_{DD}(typ) = 2.5 \text{ V}.$

| Parameter/Condition                             | Symbol            | Min                      | Max                      | Unit | Notes |

|-------------------------------------------------|-------------------|--------------------------|--------------------------|------|-------|

| I/O supply voltage                              | GV <sub>DD</sub>  | 2.375                    | 2.625                    | V    | 1     |

| I/O reference voltage                           | MV <sub>REF</sub> | $0.49 \times GV_{DD}$    | $0.51 	imes GV_{DD}$     | V    | 2     |

| I/O termination voltage                         | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04 | MV <sub>REF</sub> + 0.04 | V    | 3     |

| Input high voltage                              | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.15 | GV <sub>DD</sub> + 0.3   | V    | —     |

| Input low voltage                               | V <sub>IL</sub>   | -0.3                     | MV <sub>REF</sub> – 0.15 | V    | —     |

| Output leakage current                          | I <sub>OZ</sub>   | -50                      | 50                       | μΑ   | 4     |

| Output high current (V <sub>OUT</sub> = 1.95 V) | I <sub>OH</sub>   | -16.2                    | —                        | mA   | —     |

| Output low current (V <sub>OUT</sub> = 0.35 V)  | I <sub>OL</sub>   | 16.2                     | —                        | mA   | —     |

| Table 13. DDR SDRAM DC Electrical | Characteristics for GV <sub>DD</sub> (typ) = 2.5 V |

|-----------------------------------|----------------------------------------------------|

|                                   |                                                    |

#### Notes:

1.  ${\rm GV}_{\rm DD}$  is expected to be within 50 mV of the DRAM  ${\rm V}_{\rm DD}$  at all times.

2. MV<sub>REF</sub> is expected to be equal to 0.5 × GV<sub>DD</sub>, and to track GV<sub>DD</sub> DC variations as measured at the receiver. Peak-to-peak noise on MV<sub>REF</sub> may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail must track variations in the DC level of MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled,  $0 V \le V_{OUT} \le GV_{DD}$ .

Table 14 provides the DDR I/O capacitance when  $GV_{DD}(typ) = 2.5$  V.

### Table 14. DDR SDRAM Capacitance for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition                     | Symbol           | Min | Max | Unit | Notes |

|-----------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS | C <sub>DIO</sub> |     | 0.5 | pF   | 1     |

#### Note:

1. This parameter is sampled.  $GV_{DD} = 2.5 \text{ V} \pm 0.125 \text{ V}$ , f = 1 MHz, T<sub>A</sub> = 25°C,  $V_{OUT} = GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

This table provides the current draw characteristics for MV<sub>REF</sub>.

### Table 15. Current Draw Characteristics for MV<sub>REF</sub>

| Parameter/Condition                | Symbol             | Min | Max | Unit | Notes |

|------------------------------------|--------------------|-----|-----|------|-------|

| Current draw for MV <sub>REF</sub> | I <sub>MVREF</sub> |     | 500 | μA   | 1     |

#### Note:

1. The voltage regulator for  $MV_{REF}$  must be able to supply up to 500  $\mu$ A current.

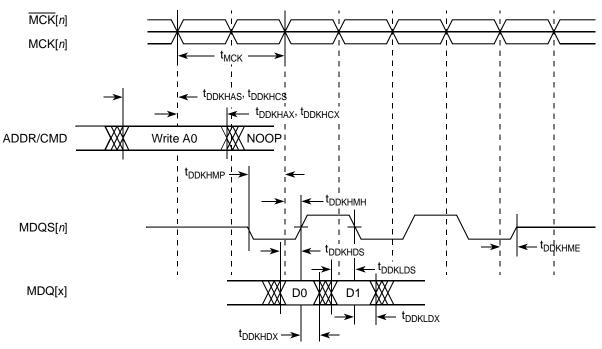

Figure 4 shows the DDR SDRAM output timing diagram.+

Figure 4. DDR SDRAM Output Timing Diagram

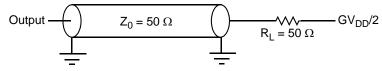

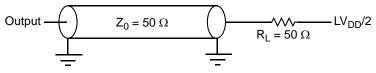

Figure 5 provides the AC test load for the DDR bus.

Figure 5. DDR AC Test Load

#### Enhanced Three-Speed Ethernet (eTSEC)

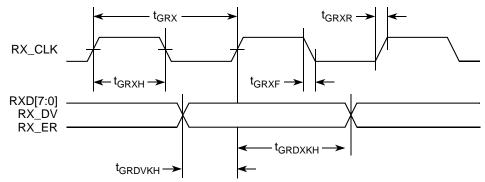

Figure 10 shows the GMII receive AC timing diagram.

Figure 10. GMII Receive AC Timing Diagram

### 8.2.3 MII AC Timing Specifications

This section describes the MII transmit and receive AC timing specifications.

### 8.2.3.1 MII Transmit AC Timing Specifications

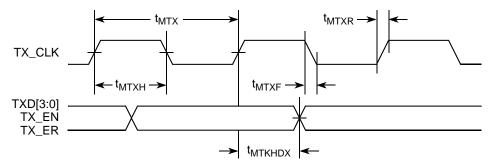

This table provides the MII transmit AC timing specifications.

| Table 28. MII Transmit A | C Timing Specifications |

|--------------------------|-------------------------|

|--------------------------|-------------------------|

| Parameter/Condition                             | Symbol <sup>1</sup>                 | Min | Тур | Max | Unit |

|-------------------------------------------------|-------------------------------------|-----|-----|-----|------|

| TX_CLK clock period 10 Mbps                     | t <sub>MTX</sub> <sup>2</sup>       | _   | 400 | —   | ns   |

| TX_CLK clock period 100 Mbps                    | t <sub>MTX</sub>                    | _   | 40  | —   | ns   |

| TX_CLK duty cycle                               | t <sub>MTXH</sub> /t <sub>MTX</sub> | 35  | _   | 65  | %    |

| TX_CLK to MII data TXD[3:0], TX_ER, TX_EN delay | t <sub>MTKHDX</sub>                 | 1   | 5   | 15  | ns   |

| TX_CLK data clock rise (20%–80%)                | t <sub>MTXR</sub> <sup>2</sup>      | 1.0 | _   | 4.0 | ns   |

| TX_CLK data clock fall (80%–20%)                | t <sub>MTXF</sub> <sup>2</sup>      | 1.0 | _   | 4.0 | ns   |

Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

2. Guaranteed by design.

Figure 11 shows the MII transmit AC timing diagram.

Figure 11. MII Transmit AC Timing Diagram

### 8.2.3.2 MII Receive AC Timing Specifications

This table provides the MII receive AC timing specifications.

| Parameter/Condition                         | Symbol <sup>1</sup>                 | Min  | Тур | Max | Unit |

|---------------------------------------------|-------------------------------------|------|-----|-----|------|

| RX_CLK clock period 10 Mbps                 | t <sub>MRX</sub> 2                  | _    | 400 | _   | ns   |

| RX_CLK clock period 100 Mbps                | t <sub>MRX</sub>                    |      | 40  |     | ns   |

| RX_CLK duty cycle                           | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35   | _   | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>MRDVKH</sub>                 | 10.0 | _   | _   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>MRDXKH</sub>                 | 10.0 | _   | _   | ns   |

| RX_CLK clock rise (20%–80%)                 | t <sub>MRXR</sub> <sup>2</sup>      | 1.0  | _   | 4.0 | ns   |

| RX_CLK clock fall time (80%–20%)            | t <sub>MRXF</sub> <sup>2</sup>      | 1.0  | _   | 4.0 | ns   |

Notes:

1. The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

2. Guaranteed by design.

Figure 12 provides the AC test load for eTSEC.

Figure 12. eTSEC AC Test Load

# 9 Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals MDIO (management data input/output) and MDC (management data clock). The electrical characteristics for GMII, RGMII, RMII, TBI, and RTBI are specified in "Section 8, "Enhanced Three-Speed Ethernet (eTSEC)."

# 9.1 MII Management DC Electrical Characteristics

The MDC and MDIO are defined to operate at a supply voltage of 3.3 V. The DC electrical characteristics for MDIO and MDC are provided in this table.

| Parameter                                                            | Symbol           | Min  | Мах                    | Unit |

|----------------------------------------------------------------------|------------------|------|------------------------|------|

| Supply voltage (3.3 V)                                               | OV <sub>DD</sub> | 3.13 | 3.47                   | V    |

| Output high voltage ( $OV_{DD} = Min, I_{OH} = -1.0 mA$ )            | V <sub>OH</sub>  | 2.10 | OV <sub>DD</sub> + 0.3 | V    |

| Output low voltage (OV <sub>DD</sub> =Min, I <sub>OL</sub> = 1.0 mA) | V <sub>OL</sub>  | GND  | 0.50                   | V    |

| Input high voltage                                                   | V <sub>IH</sub>  | 2.0  | —                      | V    |

| Input low voltage                                                    | V <sub>IL</sub>  | —    | 0.90                   | V    |

| Input high current ( $OV_{DD} = Max, V_{IN}^1 = 2.1 V$ )             | I <sub>IH</sub>  | —    | 40                     | μA   |

| Input low current ( $OV_{DD} = Max$ , $V_{IN} = 0.5 V$ )             | IIL              | -600 | —                      | μΑ   |

Table 36. MII Management DC Electrical Characteristics

Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

# 9.2 MII Management AC Electrical Specifications

This table provides the MII management AC timing specifications.

### Table 37. MII Management AC Timing Specifications

At recommended operating conditions with  $OV_{DD}$  is 3.3 V ± 5%.

| Parameter                  | Symbol <sup>1</sup> | Min                             | Тур | Мах                                | Unit | Notes   |

|----------------------------|---------------------|---------------------------------|-----|------------------------------------|------|---------|

| MDC frequency              | f <sub>MDC</sub>    | 0.72                            | 2.5 | 8.3                                | MHz  | 2, 3, 4 |

| MDC period                 | t <sub>MDC</sub>    | 120.5                           | _   | 1389                               | ns   | —       |

| MDC clock pulse width high | t <sub>MDCH</sub>   | 32                              | _   | —                                  | ns   | _       |

| MDC to MDIO valid          | t <sub>MDKHDV</sub> | $16 \times t_{CCB}$             | _   | —                                  | ns   | 5       |

| MDC to MDIO delay          | t <sub>MDKHDX</sub> | (16 × t <sub>CCB</sub> × 8) – 3 | _   | $(16 \times t_{CCB} \times 8) + 3$ | ns   | 5       |

| MDIO to MDC setup time     | t <sub>MDD∨KH</sub> | 5                               | _   | —                                  | ns   | _       |

| MDIO to MDC hold time      | t <sub>MDDXKH</sub> | 0                               | _   | —                                  | ns   | —       |

| MDC rise time              | t <sub>MDCR</sub>   | _                               |     | 10                                 | ns   | 4       |

# 14 GP<sub>OUT</sub>/GP<sub>IN</sub>

This section describes the DC and AC electrical specifications for the GP<sub>OUT</sub>/GP<sub>IN</sub> bus of the device.

# 14.1 GP<sub>OUT</sub>/GP<sub>IN</sub> Electrical Characteristics

Table 47 and Table 48 provide the DC electrical characteristics for the GP<sub>OUT</sub> interface.

| Parameter                                                                      | Symbol           | Min                    | Мах  | Unit |

|--------------------------------------------------------------------------------|------------------|------------------------|------|------|

| Supply voltage 3.3 V                                                           | BV <sub>DD</sub> | 3.13                   | 3.47 | V    |

| High-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OH</sub> = -2 mA) | V <sub>OH</sub>  | BV <sub>DD</sub> – 0.2 | _    | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> = min, I <sub>OL</sub> = 2 mA)   | V <sub>OL</sub>  | —                      | 0.2  | V    |

Table 47. GP<sub>OUT</sub> DC Electrical Characteristics (3.3 V DC)

Table 48. GP<sub>OUT</sub> DC Electrical Characteristics (2.5 V DC)

| Parameter                                                                  | Symbol           | Min       | Мах                    | Unit |

|----------------------------------------------------------------------------|------------------|-----------|------------------------|------|

| Supply voltage 2.5 V                                                       | BV <sub>DD</sub> | 2.37      | 2.63                   | V    |

| High-level output voltage<br>( $BV_{DD} = min, I_{OH} = -1 mA$ )           | V <sub>OH</sub>  | 2.0       | BV <sub>DD</sub> + 0.3 | V    |

| Low-level output voltage<br>(BV <sub>DD</sub> min, I <sub>OL</sub> = 1 mA) | V <sub>OL</sub>  | GND – 0.3 | 0.4                    | V    |

Table 49 and Table 50 provide the DC electrical characteristics for the GP<sub>IN</sub> interface.

Table 49. GP<sub>IN</sub> DC Electrical Characteristics (3.3 V DC)

| Parameter                                                                                      | Symbol           | Min  | Мах                    | Unit |

|------------------------------------------------------------------------------------------------|------------------|------|------------------------|------|

| Supply voltage 3.3 V                                                                           | BV <sub>DD</sub> | 3.13 | 3.47                   | V    |

| High-level input voltage                                                                       | V <sub>IH</sub>  | 2    | BV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage                                                                        | V <sub>IL</sub>  | -0.3 | 0.8                    | V    |

| Input current<br>(BV <sub>IN</sub> <sup>1</sup> = 0 V or BV <sub>IN</sub> = BV <sub>DD</sub> ) | I <sub>IN</sub>  | _    | ±5                     | μA   |

Note:

1. The symbol  $\mathsf{BV}_{\mathsf{IN}}$ , in this case, represents the  $\mathsf{BV}_{\mathsf{IN}}$  symbol referenced in Table 1.

#### PCI/PCI-X

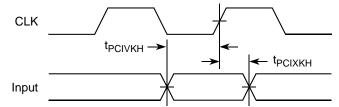

Figure 36 shows the PCI/PCI-X input AC timing conditions.

Figure 36. PCI/PCI-X Input AC Timing Measurement Conditions

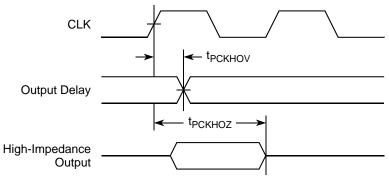

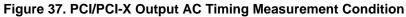

Figure 37 shows the PCI/PCI-X output AC timing conditions.

Table 53 provides the PCI-X AC timing specifications at 66 MHz.

| Table 53. PCI-X AC Timing | <b>Specifications at 66 MHz</b> |

|---------------------------|---------------------------------|

|---------------------------|---------------------------------|

| Parameter                                         | Symbol              | Min | Max | Unit   | Notes         |

|---------------------------------------------------|---------------------|-----|-----|--------|---------------|

| SYSCLK to signal valid delay                      | <sup>t</sup> PCKHOV | —   | 3.8 | ns     | 1, 2, 3, 7, 8 |

| Output hold from SYSCLK                           | t <sub>РСКНОХ</sub> | 0.7 | —   | ns     | 1, 10         |

| SYSCLK to output high impedance                   | t <sub>PCKHOZ</sub> | —   | 7   | ns     | 1, 4, 8, 11   |

| Input setup time to SYSCLK                        | t <sub>PCIVKH</sub> | 1.7 | —   | ns     | 3, 5          |

| Input hold time from SYSCLK                       | t <sub>PCIXKH</sub> | 0.5 | —   | ns     | 10            |

| REQ64 to HRESET setup time                        | t <sub>PCRVRH</sub> | 10  | —   | clocks | 11            |

| HRESET to REQ64 hold time                         | t <sub>PCRHRX</sub> | 0   | 50  | ns     | 11            |

| HRESET high to first FRAME assertion              | t <sub>PCRHFV</sub> | 10  | —   | clocks | 9, 11         |

| PCI-X initialization pattern to HRESET setup time | <sup>t</sup> PCIVRH | 10  | —   | clocks | 11            |

#### **PCI Express**

Figure 48. Minimum Transmitter Timing and Voltage Output Compliance Specifications

## 17.4.3 Differential Receiver (RX) Input Specifications

Table 57 defines the specifications for the differential input at all receivers (RXs). The parameters are specified at the component pins.

| Symbol                                       | Parameter                                                                                   | Min    | Nom | Max    | Unit | Comments                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------|---------------------------------------------------------------------------------------------|--------|-----|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| UI                                           | Unit interval                                                                               | 399.88 | 400 | 400.12 | ps   | Each UI is 400 ps $\pm$ 300 ppm. UI does not account<br>for spread spectrum clock dictated variations.<br>See Note 1.                                                                                                                                                                                                                                                                        |

| V <sub>RX-DIFFp-p</sub>                      | Differential<br>peak-to-peak<br>input voltage                                               | 0.175  | —   | 1.200  | V    | $V_{RX-DIFFp-p} = 2 \times  V_{RX-D+} - V_{RX-D-} $ . See Note 2.                                                                                                                                                                                                                                                                                                                            |

| T <sub>RX-EYE</sub>                          | Minimum<br>receiver eye<br>width                                                            | 0.4    | _   | _      | UI   | The maximum interconnect media and transmitter jitter that can be tolerated by the receiver can be derived as $T_{RX-MAX-JITTER} = 1 - T_{RX-EYE} = 0.6$ UI. See Notes 2 and 3.                                                                                                                                                                                                              |

| T <sub>RX-EYE-MEDIAN-to-</sub><br>MAX-JITTER | Maximum time<br>between the<br>jitter median and<br>maximum<br>deviation from<br>the median | —      |     | 0.3    | UI   | Jitter is defined as the measurement variation of<br>the crossing points ( $V_{RX-DIFFp-p} = 0$ V) in relation<br>to a recovered TX UI. A recovered TX UI is<br>calculated over 3500 consecutive unit intervals of<br>sample data. Jitter is measured using all edges of<br>the 250 consecutive UI in the center of the<br>3500 UI used for calculating the TX UI.<br>See Notes 2, 3, and 7. |

Table 57. Differential Receiver (RX) Input Specifications

Table 57. Differential Receiver (RX) Input Specifications (continued)

| Symbol               | Parameter  | Min | Nom | Max | Unit | Comments                                                                                                                                                                                                                          |

|----------------------|------------|-----|-----|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| L <sub>TX-SKEW</sub> | Total Skew | _   |     | 20  | ns   | Skew across all lanes on a Link. This includes<br>variation in the length of SKP ordered set (for<br>example, COM and one to five symbols) at the RX<br>as well as any delay differences arising from the<br>interconnect itself. |

#### Notes:

- 1. No test load is necessarily associated with this value.

- 2. Specified at the measurement point and measured over any 250 consecutive UIs. The test load in Figure 50 must be used as the RX device when taking measurements (also see the receiver compliance eye diagram shown in Figure 49). If the clocks to the RX and TX are not derived from the same reference clock, the TX UI recovered from 3500 consecutive UI must be used as a reference for the eye diagram.

- 3. A T<sub>RX-EYE</sub> = 0.40 UI provides for a total sum of 0.60 UI deterministic and random jitter budget for the transmitter and interconnect collected any 250 consecutive UIs. The T<sub>RX-EYE-MEDIAN-to-MAX-JITTER</sub> specification ensures a jitter distribution in which the median and the maximum deviation from the median is less than half of the total. UI jitter budget collected over any 250 consecutive TX UIs. Note that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value. If the clocks to the RX and TX are not derived from the same reference clock, the TX UI recovered from 3500 consecutive UI must be used as the reference for the eye diagram.

- 4. The receiver input impedance shall result in a differential return loss greater than or equal to 15 dB with the D+ line biased to 300 mV and the D– line biased to  $-{300 \text{ mV}}$  and a common mode return loss greater than or equal to 6 dB (no bias required) over a frequency range of 50 MHz to 1.25 GHz. This input impedance requirement applies to all valid input levels. The reference impedance for return loss measurements for is 50  $\Omega$  to ground for both the D+ and D– line (that is, as measured by a vector network analyzer with 50- $\Omega$  probes—see Figure 50). Note: that the series capacitors CTX is optional for the return loss measurement.

- 5. Impedance during all LTSSM states. When transitioning from a fundamental reset to detect (the initial state of the LTSSM) there is a 5 ms transition time before receiver termination values must be met on all unconfigured lanes of a port.

- 6. The RX DC common mode Impedance that exists when no power is present or fundamental reset is asserted. This helps ensure that the receiver detect circuit does not falsely assume a receiver is powered on when it is not. This term must be measured at 300 mV above the RX ground.

- 7. It is recommended that the recovered TX UI is calculated using all edges in the 3500 consecutive UI interval with a fit algorithm using a minimization merit function. Least squares and median deviation fits have worked well with experimental and simulated data.

## 17.5 Receiver Compliance Eye Diagrams

The RX eye diagram in Figure 49 is specified using the passive compliance/test measurement load (see Figure 50) in place of any real PCI Express RX component.

Note: In general, the minimum receiver eye diagram measured with the compliance/test measurement load (see Figure 50) is larger than the minimum receiver eye diagram measured over a range of systems at the input receiver of any real PCI Express component. The degraded eye diagram at the input receiver is due to traces internal to the package as well as silicon parasitic characteristics which cause the real PCI Express component to vary in impedance from the compliance/test measurement load. The input receiver eye diagram is implementation specific and is not specified. RX component designer must provide additional margin to adequately compensate for the degraded minimum receiver eye diagram (shown in Figure 49) expected at the input receiver based on some adequate combination of system simulations and the return loss measured looking into the RX package and silicon. The RX eye diagram must be aligned in time using the jitter median to locate the center of the eye diagram.

Package Description

| Signal                 | Package Pin Number                                                                                                                                                                                                                                                                                               | Pin Type | Power<br>Supply  | Notes    |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

| PCI1_REQ[4:1]          | AH2, AG4, AG3, AH4                                                                                                                                                                                                                                                                                               | I        | OV <sub>DD</sub> | _        |

|                        |                                                                                                                                                                                                                                                                                                                  |          |                  | _        |

|                        |                                                                                                                                                                                                                                                                                                                  |          |                  | —        |

|                        |                                                                                                                                                                                                                                                                                                                  |          |                  | —        |

|                        |                                                                                                                                                                                                                                                                                                                  |          |                  | —        |

| PCI1_REQ0              | AH3                                                                                                                                                                                                                                                                                                              | I/O      | OV <sub>DD</sub> | —        |

| PCI1_CLK               | AH26                                                                                                                                                                                                                                                                                                             | I        | OV <sub>DD</sub> | 39       |

| PCI1_DEVSEL            | AH11                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_FRAME             | AE11                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_IDSEL             | AG9                                                                                                                                                                                                                                                                                                              | I        | OV <sub>DD</sub> | —        |

| PCI1_REQ64/PCI2_FRAME  | AF14                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2, 5, 10 |

| PCI1_ACK64/PCI2_DEVSEL | V15                                                                                                                                                                                                                                                                                                              | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_CLK               | AE28                                                                                                                                                                                                                                                                                                             | I        | OV <sub>DD</sub> | 39       |

| PCI2_IRDY              | AD26                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_PERR              | AD25                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_GNT[4:1]          | AE26, AG24, AF25, AE25                                                                                                                                                                                                                                                                                           | 0        | OV <sub>DD</sub> | 5, 9, 35 |

| PCI2_GNT0              | AG25                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | —        |

| PCI2_SERR              | AD24                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2, 4     |

| PCI2_STOP              | AF24                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_TRDY              | AD27                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | 2        |

| PCI2_REQ[4:1]          | AD28, AE27, W17, AF26                                                                                                                                                                                                                                                                                            | I        | OV <sub>DD</sub> | —        |

| PCI2_REQ0              | AH25                                                                                                                                                                                                                                                                                                             | I/O      | OV <sub>DD</sub> | —        |

|                        | DDR SDRAM Memory Interface                                                                                                                                                                                                                                                                                       |          | 1                | -        |

| MDQ[0:63]              | L18, J18, K14, L13, L19, M18, L15, L14, A17,<br>B17, A13, B12, C18, B18, B13, A12, H18, F18,<br>J14, F15, K19, J19, H16, K15, D17, G16, K13,<br>D14, D18, F17, F14, E14, A7, A6, D5, A4, C8,<br>D7, B5, B4, A2, B1, D1, E4, A3, B2, D2, E3, F3,<br>G4, J5, K5, F6, G5, J6, K4, J1, K2, M5, M3, J3,<br>J2, L1, M6 | I/O      | GV <sub>DD</sub> | —        |

| MECC[0:7]              | H13, F13, F11, C11, J13, G13, D12, M12                                                                                                                                                                                                                                                                           | I/O      | GV <sub>DD</sub> | —        |

| MDM[0:8]               | M17, C16, K17, E16, B6, C4, H4, K1, E13                                                                                                                                                                                                                                                                          | 0        | GV <sub>DD</sub> | —        |

| MDQS[0:8]              | M15, A16, G17, G14, A5, D3, H1, L2, C13                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> |          |

| MDQS[0:8]              | L17, B16, J16, H14, C6, C2, H3, L4, D13                                                                                                                                                                                                                                                                          | I/O      | GV <sub>DD</sub> | —        |

| MA[0:15]               | A8, F9, D9, B9, A9, L10, M10, H10, K10, G10,<br>B8, E10, B10, G6, A10, L11                                                                                                                                                                                                                                       | 0        | GV <sub>DD</sub> | —        |

| MBA[0:2]               | F7, J7, M11                                                                                                                                                                                                                                                                                                      | 0        | GV <sub>DD</sub> | —        |

### Table 71. MPC8548E Pinout Listing (continued)

| Signal           | Package Pin Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Pin Type                                           | Power<br>Supply  | Notes        |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------|--------------|

|                  | Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                    |                  | 1            |

| RTC              | AF16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | —            |

| SYSCLK           | AH17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | —            |

|                  | JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                    |                  | 1            |

| ТСК              | AG28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | —            |

| TDI              | AH28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 12           |

| TDO              | AF28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                  | OV <sub>DD</sub> | _            |

| TMS              | AH27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 12           |

| TRST             | AH23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 12           |

|                  | DFT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                    |                  |              |

| L1_TSTCLK        | AC25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 25           |

| L2_TSTCLK        | AE22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 25           |

| LSSD_MODE        | AH20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 25           |

| TEST_SEL         | AH14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I                                                  | OV <sub>DD</sub> | 25           |

|                  | Thermal Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                    |                  |              |

| THERM0           | AG1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                  | _                | 14           |

| THERM1           | AH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                  |                  | 14           |

|                  | Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                    |                  |              |

| ASLEEP           | AH18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                  | OV <sub>DD</sub> | 9, 19,<br>29 |

|                  | Power and Ground Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                    |                  | •            |

| GND              | <ul> <li>A11, B7, B24, C1, C3, C5, C12, C15, C26, D8,<br/>D11, D16, D20, D22, E1, E5, E9, E12, E15, E17,<br/>F4, F26, G12, G15, G18, G21, G24, H2, H6, H8,<br/>H28, J4, J12, J15, J17, J27, K7, K9, K11, K27,<br/>L3, L5, L12, L16, N11, N13, N15, N17, N19, P4,<br/>P9, P12, P14, P16, P18, R11, R13, R15, R17,<br/>R19, T4, T12, T14, T16, T18, U8, U11, U13,<br/>U15, U17, U19, V4, V12, V18, W6, W19, Y4, Y9,<br/>Y11, Y19, AA6, AA14, AA17, AA22, AA23, AB4,<br/>AC2, AC11, AC19, AC26, AD5, AD9, AD22,<br/>AE3, AE14, AF6, AF10, AF13, AG8, AG27,<br/>K28, L24, L26, N24, N27, P25, R28, T24, T26,<br/>U24, V25, W28, Y24, Y26, AA24, AA27, AB25,<br/>AC28, L21, L23, N22, P20, R23, T21, U22, V20,<br/>W23, Y21, U27</li> </ul> | _                                                  |                  |              |

| OV <sub>DD</sub> | V16, W11, W14, Y18, AA13, AA21, AB11,<br>AB17, AB24, AC4, AC9, AC21, AD6, AD13,<br>AD17, AD19, AE10, AE8, AE24, AF4, AF12,<br>AF22, AF27, AG26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Power for PCI<br>and other<br>standards<br>(3.3 V) | OV <sub>DD</sub> | _            |

### Table 72. MPC8547E Pinout Listing (continued)

| Signal     | Package Pin Number | Pin Type | Power<br>Supply | Notes |

|------------|--------------------|----------|-----------------|-------|

| SD_PLL_TPA | U26                | 0        | —               | 24    |

**Note:** All note references in this table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

Table 73 provides the pin-out listing for the MPC8545E 783 FC-PBGA package.

### NOTE

All note references in the following table use the same numbers as those for Table 71. See Table 71 for the meanings of these notes.

|                               | •                                                                                                                                                                                                      |          |                  |          |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------|----------|

| Signal                        | Package Pin Number                                                                                                                                                                                     | Pin Type | Power<br>Supply  | Notes    |

|                               | PCI1 and PCI2 (One 64-Bit or Two 32-Bit)                                                                                                                                                               |          |                  |          |

| PCI1_AD[63:32]/PCI2_AD[31:0]  | AB14, AC15, AA15, Y16, W16, AB16, AC16,<br>AA16, AE17, AA18, W18, AC17, AD16, AE16,<br>Y17, AC18, AB18, AA19, AB19, AB21, AA20,<br>AC20, AB20, AB22, AC22, AD21, AB23, AF23,<br>AD23, AE23, AC23, AC24 | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_AD[31:0]                 | AH6, AE7, AF7, AG7, AH7, AF8, AH8, AE9,<br>AH9, AC10, AB10, AD10, AG10, AA10, AH10,<br>AA11, AB12, AE12, AG12, AH12, AB13, AA12,<br>AC13, AE13, Y14, W13, AG13, V14, AH13,<br>AC14, Y15, AB15          | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_C_BE[7:4]/PCI2_C_BE[3:0] | AF15, AD14, AE15, AD15                                                                                                                                                                                 | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_C_BE[3:0]                | AF9, AD11, Y12, Y13                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 17       |

| PCI1_PAR64/PCI2_PAR           | W15                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | —        |

| PCI1_GNT[4:1]                 | AG6, AE6, AF5, AH5                                                                                                                                                                                     | 0        | OV <sub>DD</sub> | 5, 9, 35 |

| PCI1_GNT0                     | AG5                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | —        |

| PCI1_IRDY                     | AF11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_PAR                      | AD12                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | —        |

| PCI1_PERR                     | AC12                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_SERR                     | V13                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2, 4     |

| PCI1_STOP                     | W12                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_TRDY                     | AG11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |

| PCI1_REQ[4:1]                 | AH2, AG4, AG3, AH4                                                                                                                                                                                     | I        | OV <sub>DD</sub> | —        |

| PCI1_REQ0                     | AH3                                                                                                                                                                                                    | I/O      | OV <sub>DD</sub> | —        |

| PCI1_CLK                      | AH26                                                                                                                                                                                                   | I        | OV <sub>DD</sub> | 39       |

| PCI1_DEVSEL                   | AH11                                                                                                                                                                                                   | I/O      | OV <sub>DD</sub> | 2        |

### Table 73. MPC8545E Pinout Listing

Package Description

| Signal                | Package Pin Number                              |                         | Power<br>Supply  | Notes |  |

|-----------------------|-------------------------------------------------|-------------------------|------------------|-------|--|

| UDE                   | AH16                                            | I                       | OV <sub>DD</sub> | _     |  |

| MCP                   | AG19                                            | I                       | OV <sub>DD</sub> | _     |  |

| IRQ[0:7]              | AG23, AF18, AE18, AF20, AG18, AF17, AH24, AE20  | I                       | OV <sub>DD</sub> | -     |  |

| IRQ[8]                | AF19                                            | I                       | OV <sub>DD</sub> | —     |  |

| IRQ[9]/DMA_DREQ3      | AF21                                            | I                       | OV <sub>DD</sub> | 1     |  |

| IRQ[10]/DMA_DACK3     | AE19                                            | I/O                     | OV <sub>DD</sub> | 1     |  |

| IRQ[11]/DMA_DDONE3    | AD20                                            | I/O                     | OV <sub>DD</sub> | 1     |  |

| IRQ_OUT               | AD18                                            | AD18 O OV <sub>DD</sub> |                  | 2, 4  |  |

|                       | Ethernet Management Interface                   |                         | 1                |       |  |

| EC_MDC                | AB9                                             | 0                       | OV <sub>DD</sub> | 5, 9  |  |

| EC_MDIO               | AC8                                             | I/O                     | OV <sub>DD</sub> | _     |  |

|                       | Gigabit Reference Clock                         |                         |                  |       |  |

| EC_GTX_CLK125         | V11                                             | I                       | LV <sub>DD</sub> |       |  |

|                       | Three-Speed Ethernet Controller (Gigabit Ethern | et 1)                   | 1                |       |  |

| TSEC1_RXD[7:0]        | R5, U1, R3, U2, V3, V1, T3, T2                  | I                       | LV <sub>DD</sub> |       |  |

| TSEC1_TXD[7:0]        | T10, V7, U10, U5, U4, V6, T5, T8                | 0                       | LV <sub>DD</sub> | 5, 9  |  |

| TSEC1_COL             | R4                                              | I                       | LV <sub>DD</sub> |       |  |

| TSEC1_CRS             | V5                                              | I/O                     | LV <sub>DD</sub> | 20    |  |

| TSEC1_GTX_CLK         | U7                                              | 0                       | LV <sub>DD</sub> | _     |  |

| TSEC1_RX_CLK          | U3                                              | I                       | LV <sub>DD</sub> |       |  |

| TSEC1_RX_DV           | V2                                              | I                       | LV <sub>DD</sub> | _     |  |

| TSEC1_RX_ER           | T1                                              | I                       | LV <sub>DD</sub> | _     |  |

| TSEC1_TX_CLK          | Т6                                              | I                       | LV <sub>DD</sub> | —     |  |

| TSEC1_TX_EN           | U9                                              | 0                       | LV <sub>DD</sub> | 30    |  |

| TSEC1_TX_ER           | Т7                                              | 0                       | LV <sub>DD</sub> | _     |  |

| GPIN[0:7]             | P2, R2, N1, N2, P3, M2, M1, N3                  | I                       | LV <sub>DD</sub> | 103   |  |

| GPOUT[0:5]            | N9, N10, P8, N7, R9, N5                         | 0                       | LV <sub>DD</sub> | _     |  |

| cfg_dram_type0/GPOUT6 | R8                                              | 0                       | LV <sub>DD</sub> | 5, 9  |  |

| GPOUT7                | N6                                              | 0                       | LV <sub>DD</sub> | —     |  |

| Reserved              | P1                                              | _                       | —                | 104   |  |

| Reserved              | R6                                              |                         | —                | 104   |  |

| Reserved              | P6                                              |                         | —                | 15    |  |

| Reserved              | N4                                              | _                       | _                | 105   |  |

Package Description

| Signal           | Package Pin Number                                                                                                                                                | ckage Pin Number Pin Type                                           |                  |    |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|------------------|----|--|--|

| GV <sub>DD</sub> | B3, B11, C7, C9, C14, C17, D4, D6, D10, D15,<br>E2, E8, E11, E18, F5, F12, F16, G3, G7, G9,<br>G11, H5, H12, H15, H17, J10, K3, K12, K16,<br>K18, L6, M4, M8, M13 | Power for<br>DDR1 and<br>DDR2 DRAM<br>I/O voltage<br>(1.8 V, 2.5 V) | GV <sub>DD</sub> | _  |  |  |