Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                            |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | -                                                                                   |

| Core Size                  | -                                                                                   |

| Speed                      | -                                                                                   |

| Connectivity               | -                                                                                   |

| Peripherals                | -                                                                                   |

| Number of I/O              | -                                                                                   |

| Program Memory Size        | -                                                                                   |

| Program Memory Type        | -                                                                                   |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | -                                                                                   |

| Voltage - Supply (Vcc/Vdd) | -                                                                                   |

| Data Converters            | -                                                                                   |

| Oscillator Type            | -                                                                                   |

| Operating Temperature      | -                                                                                   |

| Mounting Type              | -                                                                                   |

| Package / Case             | -                                                                                   |

| Supplier Device Package    | -                                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/upd78f0078gc-8bs-a |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

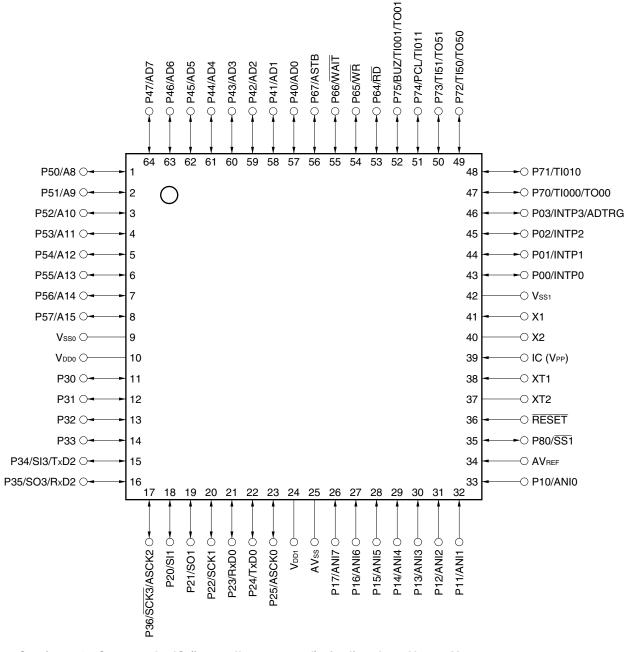

# 1.5 Pin Configuration (Top View)

- 64-pin plastic LQFP (14 × 14)

- 64-pin plastic QFP ( $14 \times 14$ )

- 64-pin plastic TQFP (12 × 12)

Cautions 1. Connect the IC (internally connected) pin directly to V<sub>SS0</sub> or V<sub>SS1</sub>. 2. Connect the AV<sub>SS</sub> pin to V<sub>SS0</sub>.

- Remarks 1. When these devices are used in applications that require the reduction of noise generated from an on-chip microcontroller, the implementation of noise measures is recommended, such as supplying VDD0 and VDD1 independently, connecting Vss0 and Vss1 independently to ground lines, and so on.

- 2. Pin connection in parentheses is intended for the  $\mu$ PD78F0078.

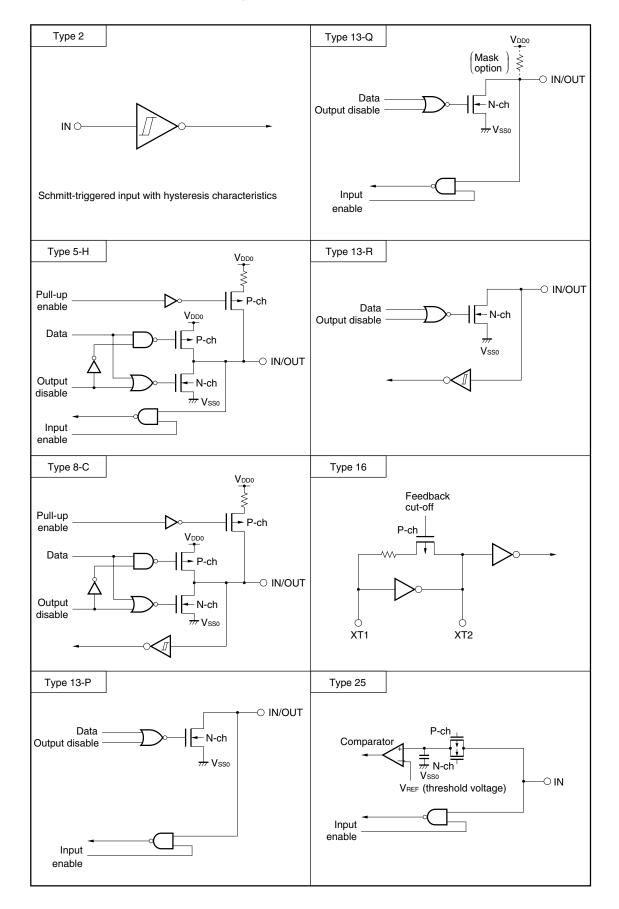

Figure 4-1. Pin I/O Circuits

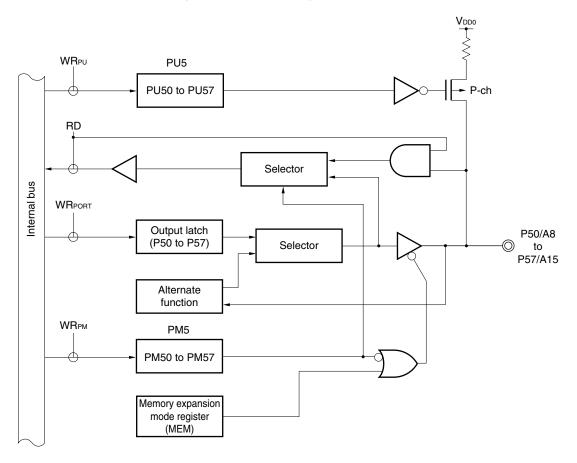

# 6.2.7 Port 5

Port 5 is an 8-bit I/O port with an output latch. Port 5 can be set to the input or output mode in 1-bit units using port mode register 5 (PM5). An on-chip pull-up resistor can be connected to P50 to P57 in 1-bit units using pull-up resistor option register 5 (PU5).

Port 5 can drive LEDs directly.

This port can also be used as an address bus in external memory expansion mode.

RESET input sets port 5 to input mode.

Figure 6-16 shows a block diagram of port 5.

# Caution An on-chip pull-up resistor is not disconnected even if the external memory expansion mode is set when PU5n = 1 (n = 0 to 7).

Figure 6-16. Block Diagram of P50 to P57

- PU5: Pull-up resistor option register 5

- PM5: Port mode register 5

- RD: Read signal

- WR×x: Write signal

# 9.4 Operation of 8-Bit Timer/Event Counters 50, 51

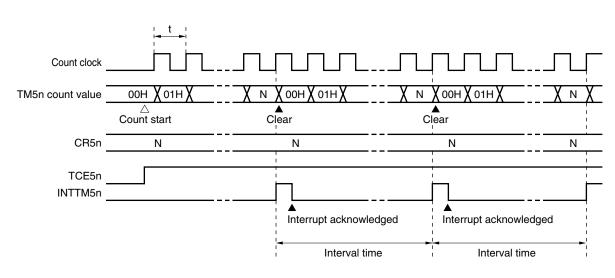

#### 9.4.1 8-bit interval timer operation

The 8-bit timer/event counters operate as interval timers that generate interrupt requests repeatedly at intervals of the count value preset to 8-bit timer compare register 5n (CR5n).

When the count value of 8-bit timer counter 5n (TM5n) matches the value set to CR5n, counting continues with the TM5n value cleared to 0 and an interrupt request signal (INTTM5n) is generated.

The count clock of TM5n can be selected with bits 0 to 2 (TCL5n0 to TCL5n2) of timer clock select register 5n (TCL5n).

#### Setting

<1> Set each register.

- TCL5n: Select count clock.

- CR5n: Compare value

- TMC5n: Count operation stop, clear & start mode on match between TM5n and CR5n. (TMC5n = 0000×××0B × = don't care)

- <2> After TCE5n = 1 is set, count operation starts.

- <3> If the values of TM5n and CR5n match, INTTM5n is generated (TM5n is cleared to 00H).

- <4> INTTM5n is generated repeatedly at the same interval. Set TCE5n to 0 to stop the count operation.

**Remark** n = 0, 1

#### (a) Basic operation

**Remarks 1.** Interval time =  $(N + 1) \times t$ N = 00H to FFH

**2.** n = 0, 1

**2.** n = 0, 1

| STT0                                                                                                                                                                                                                                                   | Start condition trigger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|--|--|--|--|--|

| 0                                                                                                                                                                                                                                                      | Do not generate a start condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                  |  |  |  |  |  |

| 1                                                                                                                                                                                                                                                      | When bus is released (during STOP mode):         Generate a start condition (for starting as master). The SDA0 line is changed from high level to low         level and then the start condition is generated. Next, after the rated amount of time has elapsed,         SCL0 is changed to low level.         When bus is not used:         This trigger functions as a start condition reservation flag. When set, it releases the bus and then         automatically generates a start condition.         Wait status (during master mode):         Generate a restart condition after wait is released. |                                  |  |  |  |  |  |

| <ul><li>For mast</li><li>For mast</li></ul>                                                                                                                                                                                                            | <ul> <li>Generate a restart condition after wait is released.</li> <li>Cautions concerning set timing         <ul> <li>For master reception:</li> <li>Cannot be set during transfer. Can be set only in the waiting period when ACKEC has been set to 0 and slave has been notified of final reception.</li> </ul> </li> <li>For master transmission: A start condition may not be generated normally during the acknowledgment period Therefore, set it during the waiting period.</li> <li>Cannot be set at the same time as SPT0.</li> </ul>                                                             |                                  |  |  |  |  |  |

| Condition f                                                                                                                                                                                                                                            | or clearing (STT0 = 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Condition for setting (STT0 = 1) |  |  |  |  |  |

| <ul> <li>Cleared by loss in arbitration</li> <li>Cleared after start condition is generated by master device</li> <li>Cleared by LREL0 = 1 (exit from communications)</li> <li>When IICE0 = 0 (operation stop)</li> <li>When RESET is input</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Set by instruction               |  |  |  |  |  |

# Figure 18-5. Format of IIC Control Register 0 (IICC0) (3/4)

Remark Bit 1 (STT0) is 0 when read after data has been set.

## 18.5.7 Interrupt request (INTIIC0) generation timing and wait control

The setting of bit 3 (WTIM0) of IIC control register 0 (IICC0) determines the timing by which INTIIC0 is generated and the corresponding wait control, as shown in Table 18-2.

| During Slave Device Operation |                         |                |                   | During Master Device Operation |                |                   |  |  |

|-------------------------------|-------------------------|----------------|-------------------|--------------------------------|----------------|-------------------|--|--|

| WTIM0                         | Address                 | Data Reception | Data Transmission | Address                        | Data Reception | Data Transmission |  |  |

| 0                             | <sub>9</sub> Notes 1, 2 | 8Note 2        | 8Note 2           | 9                              | 8              | 8                 |  |  |

| 1                             | <sub>9</sub> Notes 1, 2 | 9Note 2        | 9Note 2           | 9                              | 9              | 9                 |  |  |

#### Table 18-2. INTIICO Generation Timing and Wait Control

Notes 1. The slave device's INTIICO signal and wait period occurs at the falling edge of the ninth clock only when there is a match with the address set to slave address register 0 (SVA0). At this point, ACK is generated regardless of the value set to IICCO's bit 2 (ACKE0). For a slave device that has received an extension code, INTIICO occurs at the falling edge of the eighth clock. However, if the address does not match after restart, INTIICO is generated at the falling edge of the 9th clock, but wait does not occur.

2. If the received address does not match the contents of slave address register 0 (SVA0) and extension code is not received, neither INTIIC0 nor a wait occurs.

#### (1) During address transmission/reception

- Slave device operation: Interrupt and wait timing are determined depending on the conditions described in

Notes 1 and 2 above, regardless of the WTIM0 bit.

- Master device operation: Interrupt and wait timing occur at the falling edge of the ninth clock regardless of the WTIM0 bit.

#### (2) During data reception

• Master/slave device operation: Interrupt and wait timing are determined according to the WTIM0 bit.

#### (3) During data transmission

Master/slave device operation: Interrupt and wait timing are determined according to the WTIM0 bit.

## (4) Wait cancellation method

The four wait cancellation methods are as follows.

- By setting bit 5 (WREL0) of IIC control register 0 (IICC0) to 1

- By writing to IIC shift register 0 (IIC0)

- By setting a start condition (setting bit 1 (STT0) of IICC0 to 1)Note

- By setting a stop condition (setting bit 0 (SPT0) of IICC0 to 1)<sup>Note</sup>

Note Master only.

When an 8-clock wait has been selected (WTIM0 = 0), the presence/absence of  $\overline{ACK}$  generation must be determined prior to wait cancellation.

**Remark** The numbers in the table indicate the number of the serial clock's clock signals. Interrupt requests and wait control are both synchronized with the falling edge of these clock signals.

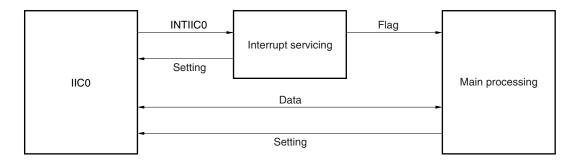

# (2) Slave operation

The processing procedure of the slave operation is as follows.

Basically, the slave operation is event-driven. Therefore, processing by the INTIIC0 interrupt (processing that must substantially change the operation status such as detection of a stop condition during communication) is necessary.

In the following explanation, it is assumed that the extension code is not supported for data communication. It is also assumed that the INTIIC0 interrupt servicing only performs status transition processing, and that actual data communication is performed by the main processing.

Therefore, data communication processing is performed by preparing the following three flags and passing them to the main processing instead of INTIICO.

## <1> Communication mode flag

This flag indicates the following two communication statuses.

- Clear mode: Status in which data communication is not performed

- Communication mode: Status in which data communication is performed (from valid address detection to stop condition detection, no detection of ACK from master, address mismatch)

## <2> Ready flag

This flag indicates that data communication is enabled. Its function is the same as the INTIIC0 interrupt for ordinary data communication. This flag is set by interrupt servicing and cleared by the main processing. Clear this flag by interrupt servicing when communication is started. However, the ready flag is not set by interrupt servicing when the first data is transmitted. Therefore, the first data is transmitted without the flag being cleared (an address match is interpreted as a request for the next data).

# <3> Communication direction flag

This flag indicates the direction of communication. Its value is the same as TRC0.

# (b) When arbitration loss occurs during transmission of extension code

(i) When WTIM0 = 0

| ST AD6-AD0                | R/W ACK              | D7-D0 ACK          | D7-D0 ACK       | SP               |        |

|---------------------------|----------------------|--------------------|-----------------|------------------|--------|

|                           | ▲1                   | ▲2                 | ▲3              | ∆4               |        |

| ▲1 : IICS0 = (            | 0110×010B ( <b>E</b> | xample When ALD    | ) is read durin | a interrupt serv | icina) |

| ▲2 : IICS0 = 0            |                      | •                  |                 | 0                | 0,     |

| ▲3 : IICS0 = 0            | 0010×000B            |                    |                 |                  |        |

| $\triangle 4$ : IICS0 = 0 | 00000001B            |                    |                 |                  |        |

| Remark                    | ▲: Always g          | generated          |                 |                  |        |

|                           | ∆: Generate          | ed only when SPIE0 | = 1             |                  |        |

|                           | ×: Don't ca          | re                 |                 |                  |        |

# (ii) When WTIM0 = 1

| ST AD6-AD                 | 0 R/W ACK    | D7-D0       | ACK C    | 07-D0   | ĀCK    | SP         |             |      |

|---------------------------|--------------|-------------|----------|---------|--------|------------|-------------|------|

|                           | ▲1 ▲         | 2           | ▲3       |         |        | 4 <i>L</i> | <u>5</u>    |      |

| ▲1 : IICS0 = (            | 0110~010B (E | vample W    |          | is road | ldurin | a inter    | runt convic | ina) |

| ▲1 : 11CS0 = 0            |              | valliple w  |          | 15 1640 | uunni  | y inten    | upt servic  | ng)  |

| ▲2 : IICS0 = (            |              |             |          |         |        |            |             |      |

|                           |              |             |          |         |        |            |             |      |

| ▲4 : IICS0 = 0            |              |             |          |         |        |            |             |      |

| $\triangle 5$ : IICS0 = 0 | 00000018     |             |          |         |        |            |             |      |

| Remark                    | ▲: Always    | generated   |          |         |        |            |             |      |

|                           | ∆: Generat   | ed only who | en SPIE0 | = 1     |        |            |             |      |

|                           | ×:Don't ca   | re          |          |         |        |            |             |      |

(1) Start condition ~ address

Note To cancel master wait, write "FFH" to IIC0 or set WREL0.

#### 19.4 Interrupt Servicing Operations

#### 19.4.1 Non-maskable interrupt request acknowledgment operation

A non-maskable interrupt request is unconditionally acknowledged even in an interrupt acknowledgment disabled state. It does not undergo interrupt priority control and has the highest priority of all interrupts.

If a non-maskable interrupt request is acknowledged, the contents are saved into the stacks in the order of PSW, then PC, the IE flag and ISP flag are reset (0), and the contents of the vector table are loaded into the PC and branched. This disables the acknowledgment of multiple interrupts.

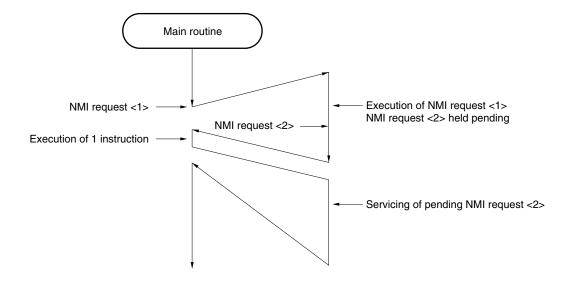

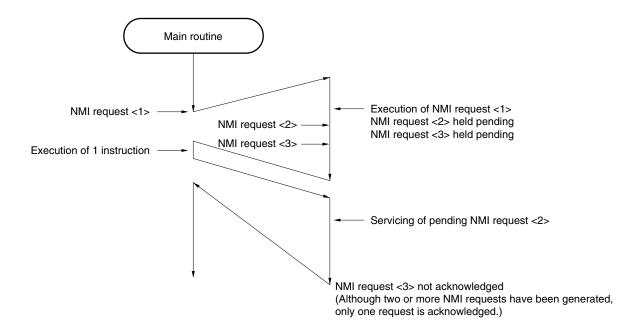

A new non-maskable interrupt request generated during execution of a non-maskable interrupt servicing program is acknowledged after the current non-maskable interrupt servicing program is terminated (following RETI instruction execution) and one main routine instruction has been executed. However, if a new non-maskable interrupt request is generated twice or more during non-maskable interrupt servicing program execution, only one non-maskable interrupt request is acknowledged after termination of the non-maskable interrupt servicing program.

Figures 19-7, 19-8, and 19-9 show the flowchart of non-maskable interrupt request generation through acknowledgment, the acknowledgment timing of a non-maskable interrupt request, and the acknowledgment operation when multiple non-maskable interrupt requests are generated, respectively.

Caution Be sure to use the RETI instruction to restore processing from the non-maskable interrupt.

Figure 19-9. Non-Maskable Interrupt Request Acknowledgment Operation

(a) If a non-maskable interrupt request is generated during non-maskable interrupt servicing program execution

(b) If two non-maskable interrupt requests are generated during non-maskable interrupt servicing program execution

| Instruction Mnemonic |           | Onevende      | Dutes | Clocks |                      | Quanting                               |   | Flag | g  |

|----------------------|-----------|---------------|-------|--------|----------------------|----------------------------------------|---|------|----|

| Group                | winemonic | Operands      | Bytes | Note 1 | Note 2               | Operation                              | Z | AC   | CY |

| Bit                  | AND1      | CY, saddr.bit | 3     | 6      | 7                    | $CY \leftarrow CY \land (saddr.bit)$   |   |      | ×  |

| manipu-              |           | CY, sfr.bit   | 3     | -      | 7                    | $CY \leftarrow CY \land sfr.bit$       |   |      | ×  |

| late                 |           | CY, A.bit     | 2     | 4      | -                    | $CY \leftarrow CY \land A.bit$         |   |      | ×  |

|                      |           | CY, PSW.bit   | 3     | -      | 7                    | $CY \leftarrow CY \land PSW.bit$       |   |      | ×  |

|                      |           | CY, [HL].bit  | 2     | 6      | 7 + n                | $CY \leftarrow CY \land (HL).bit$      |   |      | Х  |

|                      | OR1       | CY, saddr.bit | 3     | 6      | 7                    | $CY \gets CY \lor (saddr.bit)$         |   |      | ×  |

|                      |           | CY, sfr.bit   | 3     | -      | 7                    | $CY \leftarrow CY \lor sfr.bit$        |   |      | ×  |

|                      |           | CY, A.bit     | 2     | 4      | -                    | $CY \leftarrow CY \lor A.bit$          |   |      | ×  |

|                      |           | CY, PSW.bit   | 3     | -      | 7                    | $CY \leftarrow CY \lor PSW.bit$        |   |      | ×  |

|                      |           | CY, [HL].bit  | 2     | 6      | 7 + n                | $CY \leftarrow CY \lor (HL).bit$       |   |      | ×  |

|                      | XOR1      | CY, saddr.bit | 3     | 6      | 7                    | $CY \leftarrow CY \forall$ (saddr.bit) |   |      | ×  |

|                      |           | CY, sfr.bit   | 3     | -      | 7                    | $CY \leftarrow CY \forall sfr.bit$     |   |      | х  |

|                      |           | CY, A.bit     | 2     | 4      | -                    | $CY \leftarrow CY \forall A.bit$       |   |      | Х  |

|                      |           | CY, PSW. bit  | 3     | -      | 7                    | $CY \leftarrow CY \forall PSW.bit$     |   |      | ×  |

|                      |           | CY, [HL].bit  | 2     | 6      | 7 + n                | $CY \leftarrow CY \forall (HL).bit$    |   |      | ×  |

|                      | SET1      | saddr.bit     | 2     | 4      | 6                    | $(saddr.bit) \leftarrow 1$             |   |      |    |

|                      |           | sfr.bit       | 3     | -      | 8                    | sfr.bit $\leftarrow 1$                 |   |      |    |

|                      |           | A.bit         | 2     | 4      | -                    | A.bit ← 1                              |   |      |    |

|                      |           | PSW.bit       | 2     | -      | 6                    | $PSW.bit \leftarrow 1$                 | × | ×    | ×  |

|                      |           | [HL].bit      | 2     | 6      | 8 + n + m            | (HL).bit $\leftarrow$ 1                |   |      |    |

|                      | CLR1      | saddr.bit     | 2     | 4      | 6                    | $(saddr.bit) \leftarrow 0$             |   |      |    |

|                      |           | sfr.bit       | 3     | -      | 8                    | sfr.bit ← 0                            |   |      |    |

|                      | A.bit     | 2             | 4     |        | A.bit $\leftarrow$ 0 |                                        |   |      |    |

|                      | PSW.bit   | 2             | -     | 6      | $PSW.bit \gets 0$    | ×                                      | × | ×    |    |

|                      |           | [HL].bit      | 2     | 6      | 8 + n + m            | (HL).bit $\leftarrow$ 0                |   |      |    |

|                      | SET1      | CY            | 1     | 2      | -                    | CY ← 1                                 |   |      | 1  |

|                      | CLR1      | CY            | 1     | 2      | -                    | $CY \leftarrow 0$                      |   |      | 0  |

|                      | NOT1      | CY            | 1     | 2      | -                    | $CY \leftarrow \overline{CY}$          |   |      | ×  |

Notes 1. When the internal high-speed RAM area is accessed or an instruction with no data access is executed.

2. When an area except the internal high-speed RAM area is accessed

- **Remarks 1.** One instruction clock cycle is one cycle of the CPU clock (fcPU) selected by the processor clock control register (PCC).

- 2. The number of clocks applies when there is a program in the internal ROM.

- 3. n is the number of waits when external memory expansion area is read from.

- 4. m is the number of waits when external memory expansion area is written to.

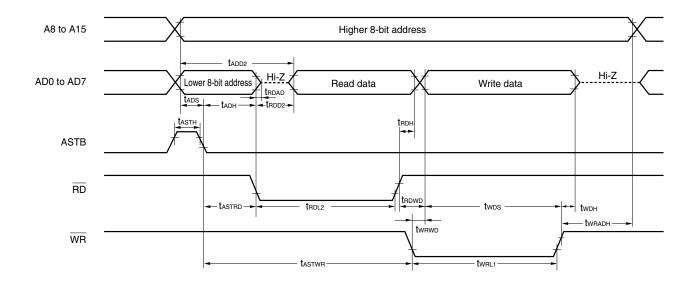

# External data access (no wait):

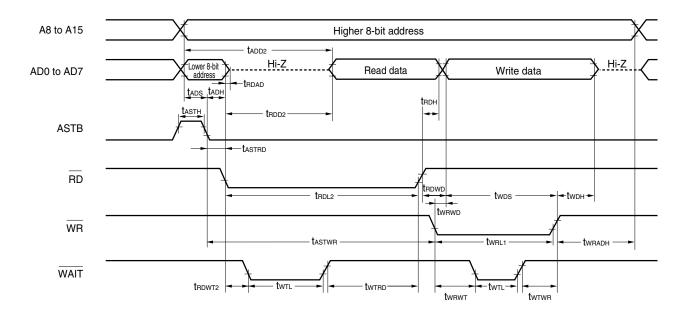

External data access (wait insertion):

Flash Memory Programming Characteristics ( $T_A = +10$  to  $+40^{\circ}C$ ,  $V_{DD} = 2.7$  to 5.5 V,  $V_{SS} = AV_{SS} = 0$  V)

| Parameter                                        | Symbol | Conditions                                |                            |                                   | MIN. | TYP. | MAX. | Unit       |

|--------------------------------------------------|--------|-------------------------------------------|----------------------------|-----------------------------------|------|------|------|------------|

| Operating frequency                              | fx     | $4.0 \ V \leq V_{DD}$                     | ≤ 5.5 V                    |                                   | 1.0  |      | 8.38 | MHz        |

|                                                  |        | $2.7~V \leq V_{\text{DD}}$                | < 4.0 V                    |                                   | 1.0  |      | 5.00 | MHz        |

| VPP supply voltage                               | VPP2   | During flash                              | n memory program           | nming                             | 9.7  | 10.0 | 10.3 | V          |

| VDD supply current                               | IDD    | When                                      | fx = 8.38 MHz              | $V_{DD} = 5.0 \text{ V} \pm 10\%$ |      |      | 24   | mA         |

|                                                  |        | $V_{PP} = V_{PP2}$                        | fx = 5.00 MHz              | $V_{DD} = 3.0 \text{ V} \pm 10\%$ |      |      | 12   | mA         |

| VPP supply current                               | Ірр    | When VPP =                                | When VPP = VPP2            |                                   |      |      | 100  | mA         |

| Step erase time <sup>Note 1</sup>                | Ter    |                                           |                            |                                   | 0.99 | 1.0  | 1.01 | s          |

| Overall erase time per area <sup>Note 2</sup>    | Tera   | When step                                 | When step erase time = 1 s |                                   |      |      | 20   | s/area     |

| Step write time                                  | Twr    |                                           |                            |                                   | 50   |      | 100  | μs         |

| Overall write time per<br>word <sup>Note 3</sup> | Twrw   | When step write time = 100 $\mu$ s        |                            |                                   |      |      | 1000 | μs         |

| Number of rewrites per area <sup>Note 4</sup>    | Cerwr  | 1 erase + 1 write after erase = 1 rewrite |                            |                                   |      |      | 20   | Times/area |

## (1) Write erase characteristics

Notes 1. The recommended setting value of the step erase time is 1 s.

- 2. The prewrite time before erasure and the erase verify time (writeback time) are not included.

- 3. The actual write time per word is  $100 \mu s$  longer. The internal verify time during or after a write is not included.

- When a product is first written after shipment, "erase → write" and "write only" are both taken as one rewrite.

Example: P: Write, E: Erase

Shipped product →P→E→P→E→P: 3 rewrites

- Shipped product  $\rightarrow E \rightarrow P \rightarrow E \rightarrow P \rightarrow E \rightarrow P$ : 3 rewrites

| (2) | Serial | write | operation | characteristics |

|-----|--------|-------|-----------|-----------------|

|-----|--------|-------|-----------|-----------------|

| Parameter                                             | Symbol | Conditions | MIN.   | TYP. | MAX.   | Unit |

|-------------------------------------------------------|--------|------------|--------|------|--------|------|

| Set time from VDD↑ to VPP↑                            | top    |            | 10     |      |        | μs   |

| Release time from V <sub>PP</sub> ↑ to RESET↑         | tpr    |            | 1.0    |      |        | μs   |

| V <sub>PP</sub> pulse input start time from<br>RESET↑ | trp    |            | 1.0    |      |        | μs   |

| VPP pulse high-/low-level width                       | tew    |            | 8.0    |      |        | μs   |

| V <sub>PP</sub> pulse input end time from<br>RESET↑   | trpe   |            |        |      | 20     | ms   |

| VPP pulse low-level input voltage                     | VPPL   |            | 0.8Vdd | Vdd  | 1.2VDD | V    |

| VPP pulse high-level input voltage                    | VPPH   |            | 9.7    | 10.0 | 10.3   | V    |

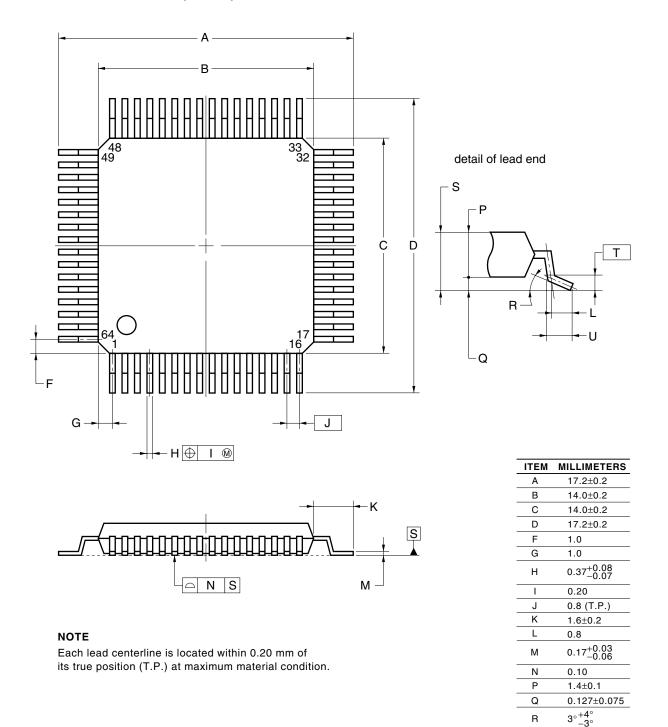

# 64-PIN PLASTIC LQFP (14x14)

**Remark** The external dimensions and materials of the ES version are the same as those of the mass-produced version.

1.7 MAX.

0.886±0.15 P64GC-80-8BS

0.25

S T

U

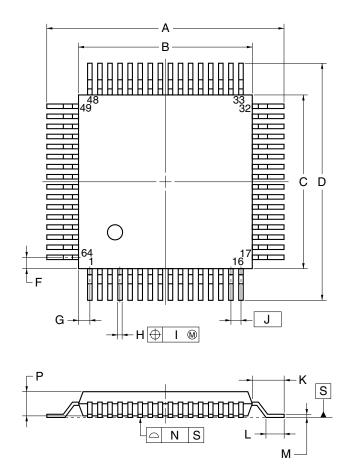

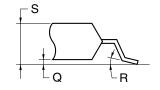

# 64-PIN PLASTIC QFP (14x14)

detail of lead end

#### NOTE

Each lead centerline is located within 0.15 mm of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS                     |

|------|---------------------------------|

| А    | 17.6±0.4                        |

| В    | 14.0±0.2                        |

| С    | 14.0±0.2                        |

| D    | 17.6±0.4                        |

| F    | 1.0                             |

| G    | 1.0                             |

| н    | $0.37\substack{+0.08 \\ -0.07}$ |

| I    | 0.15                            |

| J    | 0.8 (T.P.)                      |

| К    | 1.8±0.2                         |

| L    | 0.8±0.2                         |

| М    | $0.17\substack{+0.08 \\ -0.07}$ |

| N    | 0.10                            |

| Р    | 2.55±0.1                        |

| Q    | 0.1±0.1                         |

| R    | 5°±5°                           |

| S    | 2.85 MAX.                       |

|      | P64GC-80-AB8-5                  |

**Remark** The external dimensions and materials of the ES version are the same as those of the mass-produced version.

# Table A-2. Major Differences Between $\mu$ PD78018F, 780024A, 780034A, and 780078 Subseries (Software) (1/2)

| Name                                                                                                                                      | µPD78018F Subseries <sup>Note 1</sup>                                    | μPD780024A, 780034A                                                                                                                                                                                            | μPD780078                                                                                                               | 3 Subseries                                          |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|

| Item                                                                                                                                      |                                                                          | Subseries                                                                                                                                                                                                      |                                                                                                                         |                                                      |  |  |

| A/D converter                                                                                                                             | _                                                                        | Take the appropriate measures for the first A/D conversion result immediately after the A/D conversion operation is started (ADCS0 is set to 1), such as discarding it, because it may not satisfy the rating. |                                                                                                                         |                                                      |  |  |

|                                                                                                                                           |                                                                          |                                                                                                                                                                                                                | However, if a<br>14 $\mu$ s (MIN.) I<br>secured after<br>set to 1 before<br>operation (AD<br>1), the first dat<br>used. | nas been<br>ADCE0 was<br>e starting<br>CS0 is set to |  |  |

| 16-bit timer/event counter                                                                                                                | 1 ch                                                                     | 1 ch                                                                                                                                                                                                           | 2 ch                                                                                                                    |                                                      |  |  |

|                                                                                                                                           |                                                                          | TM0                                                                                                                                                                                                            | <br>TM00                                                                                                                | <br>                                                 |  |  |

| Interval timer<br>PWM output                                                                                                              | 0<br>0                                                                   | 0                                                                                                                                                                                                              | 0 _                                                                                                                     |                                                      |  |  |

| PPG output<br>Pulse width measurement<br>External event counter<br>Square wave output                                                     | 0                                                                        |                                                                                                                                                                                                                |                                                                                                                         |                                                      |  |  |

| Count clock                                                                                                                               | fx/2, fx/2 <sup>2</sup> , fx/2 <sup>3</sup> , TI0                        | fx, fx/2 <sup>2</sup> , fx/2 <sup>6</sup> , TI00                                                                                                                                                               | fx, fx/2 <sup>2</sup> ,<br>fx/2 <sup>6</sup> , TI000                                                                    | fx/2, fx/2 <sup>3</sup><br>fx/2 <sup>9</sup> , TI001 |  |  |

| Control register<br>Output control register<br>Compare/capture register<br>Prescaler mode register<br>Capture/compare control<br>register | TMC0<br>TOC0<br>CR00, CR01 (Capture only)<br>TCL0 <sup>Note 2</sup><br>— | TMC0<br>TOC0<br>CR00, CR01<br>PRM0<br>CRC0                                                                                                                                                                     | TMC00<br>TOC00<br>CR000, CR010<br>PRM00<br>CRC00                                                                        | TMC01<br>TOC01<br>CR001, CR011<br>PRM01<br>CRC01     |  |  |

| Interrupt                                                                                                                                 | INTTMO                                                                   | INTTM00, INTTM01                                                                                                                                                                                               | INTTM000,<br>INTTM010                                                                                                   | INTTM001,<br>INTTM011                                |  |  |

Notes 1. Maintenance product

2. TCL0: Timer clock select register 0

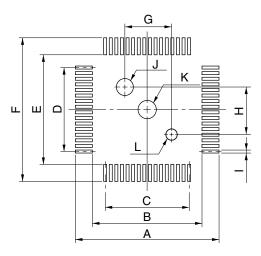

# Figure B-3. EV-9200GC-64 Recommended Board Mounting Pattern (for Reference Only)

| EV-9200GC-64-P1E |

|------------------|

|                  |

| ITEM | MILLIMETERS             | INCHES                                                                  |  |

|------|-------------------------|-------------------------------------------------------------------------|--|

| Α    | 19.5                    | 0.768                                                                   |  |

| В    | 14.8                    | 0.583                                                                   |  |

| С    | 0.8-0.02 × 15=12.0-0.05 | $0.031^{+0.002}_{-0.001}\!\!\times 0.591\!=\!\!0.472^{+0.003}_{-0.002}$ |  |

| D    | 0.8-0.02 × 15=12.0-0.05 | $0.031^{+0.002}_{-0.001}\!\!\times 0.591\!=\!\!0.472^{+0.003}_{-0.002}$ |  |

| E    | 14.8                    | 0.583                                                                   |  |

| F    | 19.5                    | 0.768                                                                   |  |

| G    | 6.00-0.08               | $0.236^{+0.004}_{-0.003}$                                               |  |

| Н    | 6.00-0.08               | $0.236^{+0.004}_{-0.003}$                                               |  |

| I    | 0.5-0.02                | $0.197\substack{+0.001\\-0.002}$                                        |  |

| J    | ¢2.36-0.03              | $\phi$ 0.093 <sup>+0.001</sup> <sub>-0.002</sub>                        |  |

| К    | ¢2.2-0.1                | $\phi_{0.087 \pm 0.005}^{+0.004}$                                       |  |

| L    | ¢1.57-0.03              | $\phi_{0.062}^{+0.001}_{-0.002}$                                        |  |

Caution Dimensions of mount pad for EV-9200 and that for target device (QFP) may be different in some parts. For the recommended mount pad dimensions for QFP, refer to "Semiconductor Device Mount Manual" (http://www.necel.com/pkg/en/mount/index. html).

| Edition | Contents                                                                                                                                                                            | Applied to:                                                                                  |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|

| 2nd     | Modification of 18.5.16 (3) (d) (ii) When WTIM0 = 1 (after restart, does not match with address (= not extension code))                                                             | CHAPTER 18 SERIAL<br>INTERFACE IIC0                                                          |  |

|         | Modification of (1) Start condition ~ address and (2) Data in Figure 18-23<br>Example of Master to Slave Communication (When 9-Clock Wait Is Selected<br>for Both Master and Slave) | (μPD780078Y SUBSERIES<br>ONLY)                                                               |  |

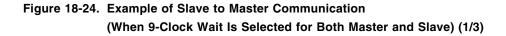

|         | Modification of Figure 18-24 Example of Slave to Master Communication<br>(When 9-Clock Wait Is Selected for Both Master and Slave)                                                  | -                                                                                            |  |

|         | Modification of (E) Software interrupt in Figure 19-1 Basic Configuration of Interrupt Function                                                                                     | CHAPTER 19 INTERRUPT<br>FUNCTIONS                                                            |  |

|         | Addition of Cautions 3 and 4 in Figure 19-2 Format of Interrupt Request Flag<br>Register (IF0L, IF0H, IF1L)                                                                         | -                                                                                            |  |

|         | Addition of Caution in Figure 19-5 Format of External Interrupt Rising Edge<br>Enable Register (EGP), External Interrupt Falling Edge Enable Register<br>(EGN)                      | -                                                                                            |  |

|         | Addition of description and <b>Remark</b> in <b>19.4.1 Non-maskable interrupt request</b> acknowledgment operation                                                                  | -                                                                                            |  |

|         | Addition of description in 19.4.2 Maskable interrupt acknowledgment operation                                                                                                       | -                                                                                            |  |

|         | Addition of item to Table 19-4 Interrupt Requests Enabled for Multiple<br>Interrupt Servicing                                                                                       | -                                                                                            |  |

|         | Addition of description about when using expanded-specification products                                                                                                            | CHAPTER 20 EXTERNAL<br>DEVICE EXPANSION<br>FUNCTION                                          |  |

|         | Addition of clock output and buzzer output in Table 21-1 HALT Mode Operating Statuses                                                                                               | CHAPTER 21 STANDBY<br>FUNCTION                                                               |  |

|         | Modification of clock output in Table 21-3 STOP Mode Operating Statuses                                                                                                             | -                                                                                            |  |

|         | Modification of chapter                                                                                                                                                             | CHAPTER 23<br>μPD78F0078, 78F0078Υ                                                           |  |

|         | Addition of chapters                                                                                                                                                                | CHAPTER 25<br>ELECTRICAL<br>SPECIFICATIONS                                                   |  |

|         |                                                                                                                                                                                     | CHAPTER 26 PACKAGE<br>DRAWINGS                                                               |  |

|         |                                                                                                                                                                                     | CHAPTER 27<br>RECOMMENDED<br>SOLDERING CONDITIONS                                            |  |

|         | Addition of <b>Table A-2 Major Differences Between</b> μ <b>PD78018F, 780024A</b> , <b>780034A, and 780078 Subseries (Software)</b>                                                 | APPENDIX A<br>DIFFERENCES BETWEEN<br>μPD78018F, 780024A,<br>780034A, AND 780078<br>SUBSERIES |  |

|         | Modification of chapter                                                                                                                                                             | APPENDIX B<br>DEVELOPMENT TOOLS                                                              |  |

|         | Addition of chapters                                                                                                                                                                | APPENDIX C NOTES ON<br>TARGET SYSTEM DESIGI                                                  |  |

|         |                                                                                                                                                                                     | APPENDIX E REVISION<br>HISTORY                                                               |  |

|         |                                                                                                                                                                         | (1/1)                                                                                                                      |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|

| Edition | Contents                                                                                                                                                                | Applied to:                                                                                                                |  |

| 3rd     | Modification of description in (1) Registers to be used in 16.4.2 3-wire serial I/O mode                                                                                | CHAPTER 16 SERIAL<br>INTERFACE SIO3                                                                                        |  |

|         | Modification of Table 16-3 Register Settings                                                                                                                            |                                                                                                                            |  |

|         | Partial modification of Figure 17-1 Block Diagram of Serial Interface CSI1                                                                                              | CHAPTER 17 SERIAL                                                                                                          |  |

|         | Partial modification of Figure 17-3 Format of Serial Clock Select Register 1 (CSIC1)                                                                                    | INTERFACE CSI1                                                                                                             |  |

|         | Modification of description in (1) Registers to be used in 17.4.2 3-wire serial I/O mode                                                                                |                                                                                                                            |  |

|         | Addition of (5) SO1 output to 17.4.2 3-wire serial I/O mode                                                                                                             |                                                                                                                            |  |

|         | Modification of Figure 18-18 Communication Reservation Timing                                                                                                           | CHAPTER 18 SERIAL                                                                                                          |  |

|         | Modification of Figure 18-21 Master Operation Flowchart (5/5)                                                                                                           | INTERFACE IIC0<br>- (μPD780078Y SUBSERIES<br>ONLY)                                                                         |  |

|         | Modification of Figure 18-21 Master Operation Flowchart                                                                                                                 |                                                                                                                            |  |

|         | Modification of (2) Slave operation in 18.5.15 Communication operations                                                                                                 |                                                                                                                            |  |

|         | Addition of Table 19-3 Ports Corresponding to EGPn and EGNn                                                                                                             | CHAPTER 19 INTERRUPT<br>FUNCTIONS                                                                                          |  |

|         | Modification of part of description in 19.4.1 Non-maskable interrupt request acknowledgment operation                                                                   |                                                                                                                            |  |

|         | Modification of part of description in 19.4.2 Maskable interrupt request acknowledgment operation                                                                       |                                                                                                                            |  |

|         | Addition of Note to Figure 20-2 Format of Memory Expansion Mode Register (MEM) and addition of Figure 20-3 Pins Specified for Address (with $\mu$ PD780076 and 780076Y) | CHAPTER 20 EXTERNAL<br>DEVICE EXPANSION<br>FUNCTION                                                                        |  |

|         | Partial modification of Table 23-3 Communication Mode List                                                                                                              | CHAPTER 23<br>μPD78F0078, 78F0078Υ                                                                                         |  |

|         | Division of Note in previous edition of Figure 23-5 Example of Connection with Dedicated Flash Programmer to Notes 1 and 2 and modification of contents                 |                                                                                                                            |  |

|         | Addition of description on voltage monitoring of dedicated flash programmer to<br>< <b>Power supply</b> > in <b>23.3.3 On-board pin processing</b>                      |                                                                                                                            |  |

|         | Revision of CHAPTER 25 ELECTRICAL SPECIFICATIONS (EXPANDED-<br>SPECIFICATION PRODUCTS OF μPD780076, 780078, 78F0078)                                                    | CHAPTER 25 ELECTRI-<br>CAL SPECIFICATIONS<br>(EXPANDED-SPECIFICA-<br>TION PRODUCTS OF<br>μPD780076, 780078,<br>78F0078)    |  |

|         | Addition of CHAPTER 26 ELECTRICAL SPECIFICATIONS (EXPANDED-<br>SPECIFICATION PRODUCTS OF μPD780076Y, 780078Y, 78F0078Y)                                                 | CHAPTER 26 ELECTRI-<br>CAL SPECIFICATIONS<br>(EXPANDED-SPECIFICA-<br>TION PRODUCTS OF<br>μPD780076Y, 780078Y,<br>78F0078Y) |  |

|         | Revision of CHAPTER 27 ELECTRICAL SPECIFICATIONS (CONVENTIONAL<br>PRODUCTS)                                                                                             | CHAPTER 27 ELECTRI-<br>CAL SPECIFICATIONS<br>(CONVENTIONAL<br>PRODUCTS)                                                    |  |

|         | Partial modification of Table 29-1 Surface Mounting Type Soldering<br>Conditions                                                                                        | CHAPTER 29 RECOM-<br>MENDED SOLDERING<br>CONDITIONS                                                                        |  |

|         | Deletion of <b>B.7 Embedded Software</b> and <b>B.8 System Upgrade from Former</b><br>In-circuit Emulator for 78K/0 Series to IE-78001-R-A in the previous edition      | APPENDIX B DEVELOP-<br>MENT TOOLS                                                                                          |  |

(7/7)