#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4                                                      |

| Core Size                  | 32-Bit Single-Core                                                   |

| Speed                      | 72MHz                                                                |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, SPI, UART/USART             |

| Peripherals                | DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                            |

| Number of I/O              | 57                                                                   |

| Program Memory Size        | 64KB (64K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | 2K x 8                                                               |

| RAM Size                   | 16K × 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                         |

| Data Converters            | A/D 39x16b; D/A 1x12b                                                |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                   |

| Mounting Type              | Surface Mount                                                        |

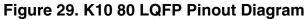

| Package / Case             | 121-LFBGA                                                            |

| Supplier Device Package    | 121-MAPBGA (8x8)                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mk10dx64vmb7 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.3.1 Example

This is an example of an attribute:

| Symbol | Description                        | Min. | Max. | Unit |

|--------|------------------------------------|------|------|------|

| CIN_D  | Input capacitance:<br>digital pins | _    | 7    | pF   |

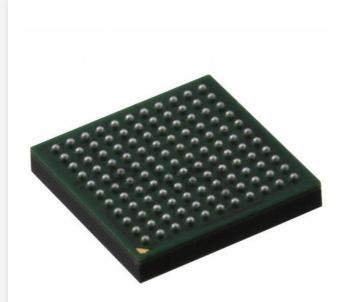

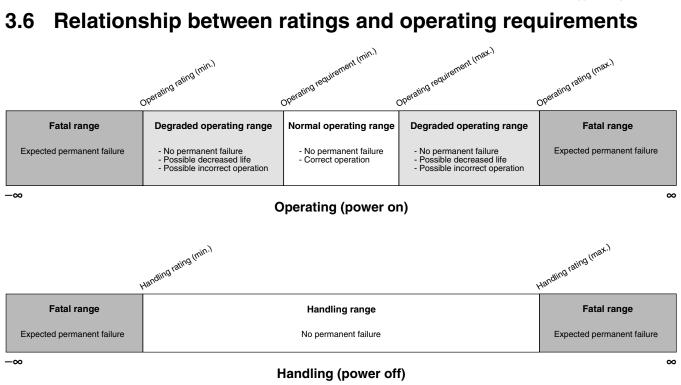

# 3.4 Definition: Rating

A *rating* is a minimum or maximum value of a technical characteristic that, if exceeded, may cause permanent chip failure:

- Operating ratings apply during operation of the chip.

- *Handling ratings* apply when the chip is not powered.

# 3.4.1 Example

This is an example of an operating rating:

| Symbol          | Description               | Min. | Max. | Unit |

|-----------------|---------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply voltage | -0.3 | 1.2  | V    |

# 3.5 Result of exceeding a rating

Terminology and guidelines

# 3.7 Guidelines for ratings and operating requirements

Follow these guidelines for ratings and operating requirements:

- Never exceed any of the chip's ratings.

- During normal operation, don't exceed any of the chip's operating requirements.

- If you must exceed an operating requirement at times other than during normal operation (for example, during power sequencing), limit the duration as much as possible.

# 3.8 Definition: Typical value

A *typical value* is a specified value for a technical characteristic that:

- Lies within the range of values specified by the operating behavior

- Given the typical manufacturing process, is representative of that characteristic during operation when you meet the typical-value conditions or other specified conditions

Typical values are provided as design guidelines and are neither tested nor guaranteed.

# 3.8.1 Example 1

This is an example of an operating behavior that includes a typical value:

| Symbol          | Description                                    | Min. | Тур. | Max. | Unit |

|-----------------|------------------------------------------------|------|------|------|------|

| I <sub>WP</sub> | Digital I/O weak<br>pullup/pulldown<br>current | 10   | 70   | 130  | μΑ   |

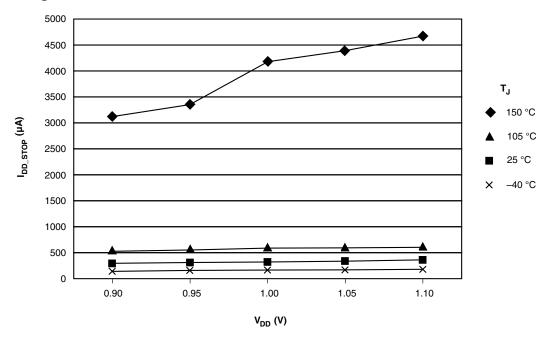

# 3.8.2 Example 2

This is an example of a chart that shows typical values for various voltage and temperature conditions:

# 3.9 Typical value conditions

Typical values assume you meet the following conditions (or other conditions as specified):

| Symbol          | Description          | Value | Unit |

|-----------------|----------------------|-------|------|

| T <sub>A</sub>  | Ambient temperature  | 25    | ٥°C  |

| V <sub>DD</sub> | 3.3 V supply voltage | 3.3   | V    |

| Symbol           | Description                                                                                           | Min.                  | Max.  | Unit | Notes |

|------------------|-------------------------------------------------------------------------------------------------------|-----------------------|-------|------|-------|

| V <sub>OH</sub>  | Output high voltage — high drive strength                                                             |                       |       |      |       |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = -9mA                                   | V <sub>DD</sub> – 0.5 | —     | V    |       |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OH}} = -3\text{mA}$    | V <sub>DD</sub> – 0.5 | —     | V    |       |

|                  | Output high voltage — low drive strength                                                              |                       |       |      |       |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = -2mA                                   | $V_{DD} - 0.5$        | —     | V    |       |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OH}} = -0.6 \text{mA}$ | V <sub>DD</sub> – 0.5 | —     | V    |       |

| I <sub>OHT</sub> | Output high current total for all ports                                                               | —                     | 100   | mA   |       |

| V <sub>OL</sub>  | Output low voltage — high drive strength                                                              |                       |       |      |       |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OL</sub> = 9mA                                    | —                     | 0.5   | V    |       |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OL}} = 3\text{mA}$     | —                     | 0.5   | V    |       |

|                  | Output low voltage — low drive strength                                                               |                       |       |      |       |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OL</sub> = 2mA                                    | _                     | 0.5   | V    |       |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OL}} = 0.6 \text{mA}$  | —                     | 0.5   | V    |       |

| I <sub>OLT</sub> | Output low current total for all ports                                                                | —                     | 100   | mA   |       |

| I <sub>IN</sub>  | Input leakage current (per pin) for full temperature range                                            | -                     | 1     | μΑ   | 1     |

| I <sub>IN</sub>  | Input leakage current (per pin) at 25°C                                                               | —                     | 0.025 | μA   | 1     |

| I <sub>OZ</sub>  | Hi-Z (off-state) leakage current (per pin)                                                            |                       | 1     | μA   |       |

| R <sub>PU</sub>  | Internal pullup resistors                                                                             | 20                    | 50    | kΩ   | 2     |

| R <sub>PD</sub>  | Internal pulldown resistors                                                                           | 20                    | 50    | kΩ   | 3     |

### 5.2.3 Voltage and current operating behaviors Table 4. Voltage and current operating behaviors

1. Measured at VDD=3.6V

2. Measured at  $V_{DD}$  supply voltage =  $V_{DD}$  min and Vinput =  $V_{SS}$

3. Measured at  $V_{\text{DD}}$  supply voltage =  $V_{\text{DD}}$  min and Vinput =  $V_{\text{DD}}$

### 5.2.4 Power mode transition operating behaviors

All specifications except  $t_{POR}$ , and VLLSx $\rightarrow$ RUN recovery times in the following table assume this clock configuration:

- CPU and system clocks = 72 MHz

- Bus clock = 36 MHz

- FlexBus clock = 36 MHz

- Flash clock = 24 MHz

| Symbol           | Description                                                                                                                                                        | Min. | Max. | Unit | Notes |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| t <sub>POR</sub> | After a POR event, amount of time from the point $V_{DD}$ reaches 1.71 V to execution of the first instruction across the operating temperature range of the chip. | _    | 300  | μs   | 1     |

|                  | VLLS1 → RUN                                                                                                                                                        |      | 112  | μs   |       |

|                  | • VLLS2 $\rightarrow$ RUN                                                                                                                                          | _    | 74   | μs   |       |

|                  | • VLLS3 $\rightarrow$ RUN                                                                                                                                          |      | 73   | μs   |       |

|                  | • LLS → RUN                                                                                                                                                        | _    | 5.9  | μs   |       |

|                  | • VLPS → RUN                                                                                                                                                       |      | 5.8  | μs   |       |

|                  | • STOP → RUN                                                                                                                                                       |      | 4.2  | μs   |       |

### Table 5. Power mode transition operating behaviors

1. Normal boot (FTFL\_OPT[LPBOOT]=1)

# 5.2.5 Power consumption operating behaviors

Table 6. Power consumption operating behaviors

| Symbol               | Description                                                                      | Min. | Тур.  | Max.     | Unit | Notes |

|----------------------|----------------------------------------------------------------------------------|------|-------|----------|------|-------|

| I <sub>DDA</sub>     | Analog supply current                                                            | —    | —     | See note | mA   | 1     |

| I <sub>DD_RUN</sub>  | Run mode current — all peripheral clocks disabled, code executing from flash     |      |       |          |      | 2     |

|                      | • @ 1.8V                                                                         | _    | 21.5  | 25       | mA   |       |

|                      | • @ 3.0V                                                                         | —    | 21.5  | 30       | mA   |       |

| I <sub>DD_RUN</sub>  | Run mode current — all peripheral clocks enabled, code executing from flash      |      |       |          |      | 3, 4  |

|                      | • @ 1.8V                                                                         | _    | 31    | 34       | mA   |       |

|                      | • @ 3.0V                                                                         |      |       |          |      |       |

|                      | • @ 25°C                                                                         | _    | 31    | 34       | mA   |       |

|                      | • @ 125°C                                                                        | _    | 32    | 39       | mA   |       |

| I <sub>DD_WAIT</sub> | Wait mode high frequency current at 3.0 V — all peripheral clocks disabled       | _    | 12.5  | —        | mA   | 2     |

| I <sub>DD_WAIT</sub> | Wait mode reduced frequency current at 3.0 V<br>— all peripheral clocks disabled | _    | 7.2   | —        | mA   | 5     |

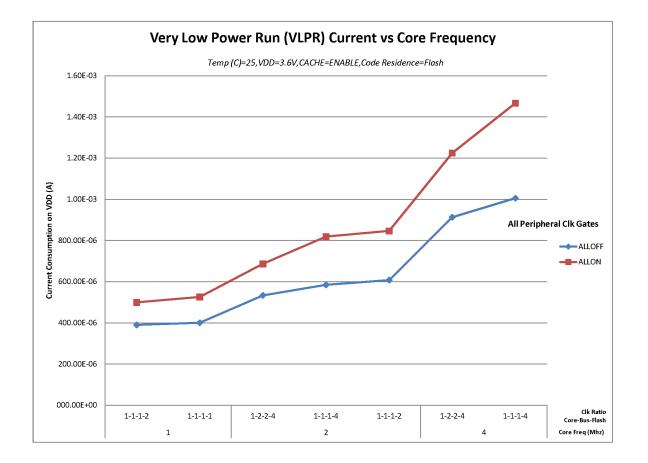

| I <sub>DD_VLPR</sub> | Very-low-power run mode current at 3.0 V — all peripheral clocks disabled        | _    | 0.996 | —        | mA   | 6     |

Table continues on the next page...

Figure 3. VLPR mode supply current vs. core frequency

# 5.2.6 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions:

- 1. Go to http://www.freescale.com.

- 2. Perform a keyword search for "EMC design."

# 5.2.7 Capacitance attributes

Table 7. Capacitance attributes

| Sy | ymbol             | Description                    | Min. | Max. | Unit |

|----|-------------------|--------------------------------|------|------|------|

| C  | C <sub>IN_A</sub> | Input capacitance: analog pins | —    | 7    | pF   |

Table continues on the next page...

K10 Sub-Family Data Sheet, Rev. 2, 4/2012.

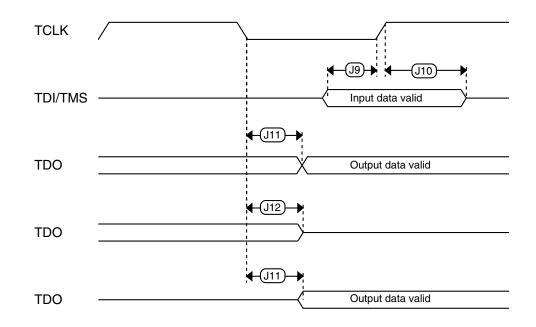

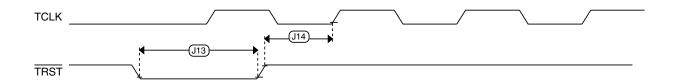

Figure 8. Test Access Port timing

# 6.2 System modules

There are no specifications necessary for the device's system modules.

# 6.3 Clock modules

| Symbol                  | Description                                          | Min.       | Тур.        | Max. | Unit | Notes |

|-------------------------|------------------------------------------------------|------------|-------------|------|------|-------|

| t <sub>pgmchk</sub>     | Program Check execution time                         | _          | _           | 45   | μs   | 1     |

| t <sub>rdrsrc</sub>     | Read Resource execution time                         |            |             | 30   | μs   | 1     |

| t <sub>pgm4</sub>       | Program Longword execution time                      |            | 65          | 145  | μs   |       |

|                         | Erase Flash Block execution time                     |            |             |      |      | 2     |

| t <sub>ersblk32k</sub>  | 32 KB data flash                                     | —          | 55          | 465  | ms   |       |

| t <sub>ersblk256k</sub> | 256 KB program flash                                 | —          | 122         | 985  | ms   |       |

| t <sub>ersscr</sub>     | Erase Flash Sector execution time                    |            | 14          | 114  | ms   | 2     |

|                         | Program Section execution time                       |            |             |      |      |       |

| t <sub>pgmsec512p</sub> | • 512 B program flash                                | —          | 2.4         | _    | ms   |       |

| t <sub>pgmsec512d</sub> | • 512 B data flash                                   | —          | 4.7         | —    | ms   |       |

| t <sub>pgmsec1kp</sub>  | • 1 KB program flash                                 | —          | 4.7         | —    | ms   |       |

| t <sub>pgmsec1kd</sub>  | • 1 KB data flash                                    | —          | 9.3         | —    | ms   |       |

| t <sub>rd1all</sub>     | Read 1s All Blocks execution time                    | _          |             | 1.8  | ms   |       |

| t <sub>rdonce</sub>     | Read Once execution time                             | _          |             | 25   | μs   | 1     |

| t <sub>pgmonce</sub>    | Program Once execution time                          | _          | 65          |      | μs   |       |

| t <sub>ersall</sub>     | Erase All Blocks execution time                      | —          | 175         | 1500 | ms   | 2     |

| t <sub>vfykey</sub>     | Verify Backdoor Access Key execution time            | —          | —           | 30   | μs   | 1     |

|                         | Swap Control execution time                          |            |             |      |      |       |

| t <sub>swapx01</sub>    | control code 0x01                                    | —          | 200         | —    | μs   |       |

| t <sub>swapx02</sub>    | control code 0x02                                    | —          | 70          | 150  | μs   |       |

| t <sub>swapx04</sub>    | control code 0x04                                    | —          | 70          | 150  | μs   |       |

| t <sub>swapx08</sub>    | control code 0x08                                    | —          | _           | 30   | μs   |       |

|                         | Program Partition for EEPROM execution time          |            |             |      |      |       |

| t <sub>pgmpart32k</sub> | • 32 KB FlexNVM                                      | —          | 70          | _    | ms   |       |

|                         | Set FlexRAM Function execution time:                 |            |             |      |      |       |

| t <sub>setramff</sub>   | Control Code 0xFF                                    | _          | 50          | _    | μs   |       |

| t <sub>setram8k</sub>   | 8 KB EEPROM backup                                   | _          | 0.3         | 0.5  | ms   |       |

| t <sub>setram32k</sub>  | 32 KB EEPROM backup                                  | _          | 0.7         | 1.0  | ms   |       |

|                         | Byte-write to FlexRAM                                | for EEPRON | l operation |      |      |       |

| t <sub>eewr8bers</sub>  | Byte-write to erased FlexRAM location execution time | _          | 175         | 260  | μs   | 3     |

### Table 19. Flash command timing specifications (continued)

Table continues on the next page...

| Symbol                  | Description                                              | Min.       | Тур.         | Max. | Unit     | Notes |

|-------------------------|----------------------------------------------------------|------------|--------------|------|----------|-------|

| -                       | Byte-write to FlexRAM execution time:                    |            |              |      |          |       |

| t <sub>eewr8b8k</sub>   | 8 KB EEPROM backup                                       | _          | 340          | 1700 | μs       |       |

| t <sub>eewr8b16k</sub>  | 16 KB EEPROM backup                                      | —          | 385          | 1800 | μs       |       |

| t <sub>eewr8b32k</sub>  | 32 KB EEPROM backup                                      | _          | 475          | 2000 | μs       |       |

|                         | Word-write to FlexRAM                                    | for EEPRON | I operation  | Į    | <u> </u> |       |

| t <sub>eewr16bers</sub> | Word-write to erased FlexRAM location execution time     | _          | 175          | 260  | μs       |       |

|                         | Word-write to FlexRAM execution time:                    |            |              |      |          |       |

| t <sub>eewr16b8k</sub>  | 8 KB EEPROM backup                                       | _          | 340          | 1700 | μs       |       |

| t <sub>eewr16b16k</sub> | 16 KB EEPROM backup                                      | —          | 385          | 1800 | μs       |       |

| t <sub>eewr16b32k</sub> | 32 KB EEPROM backup                                      | _          | 475          | 2000 | μs       |       |

|                         | Longword-write to FlexRA                                 | M for EEPR | OM operation | ו    |          |       |

| t <sub>eewr32bers</sub> | Longword-write to erased FlexRAM location execution time | _          | 360          | 540  | μs       |       |

|                         | Longword-write to FlexRAM execution time:                |            |              |      |          |       |

| t <sub>eewr32b8k</sub>  | 8 KB EEPROM backup                                       | _          | 545          | 1950 | μs       |       |

| t <sub>eewr32b16k</sub> | 16 KB EEPROM backup                                      | —          | 630          | 2050 | μs       |       |

| t <sub>eewr32b32k</sub> | 32 KB EEPROM backup                                      | _          | 810          | 2250 | μs       |       |

Table 19. Flash command timing specifications (continued)

1. Assumes 25MHz flash clock frequency.

2. Maximum times for erase parameters based on expectations at cycling end-of-life.

3. For byte-writes to an erased FlexRAM location, the aligned word containing the byte must be erased.

### 6.4.1.3 Flash current and power specfications Table 20. Flash current and power specfications

| Symbol              | Description                                     | Тур. | Unit |

|---------------------|-------------------------------------------------|------|------|

| I <sub>DD_PGM</sub> | Worst case programming current in program flash | 10   | mA   |

### 6.4.1.4 Reliability specifications Table 21. NVM reliability specifications

| Symbol                  | Description                            | Min.    | Typ. <sup>1</sup> | Max. | Unit   | Notes |

|-------------------------|----------------------------------------|---------|-------------------|------|--------|-------|

|                         | Program                                | n Flash | -                 | -    | -      |       |

| t <sub>nvmretp10k</sub> | Data retention after up to 10 K cycles | 5       | 50                | _    | years  |       |

| t <sub>nvmretp1k</sub>  | Data retention after up to 1 K cycles  | 20      | 100               | _    | years  |       |

| n <sub>nvmcycp</sub>    | Cycling endurance                      | 10 K    | 50 K              | —    | cycles | 2     |

Table continues on the next page ...

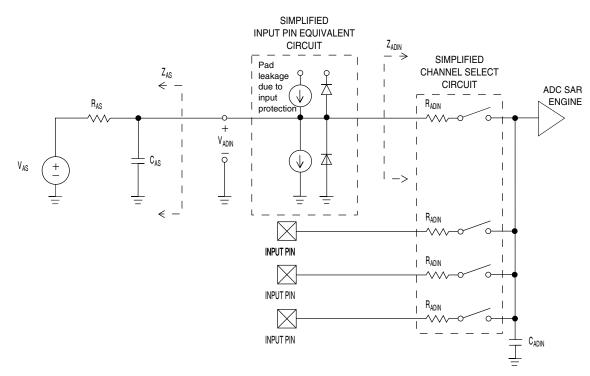

# 6.6.1 ADC electrical specifications

The 16-bit accuracy specifications listed in Table 25 and Table 26 are achievable on the differential pins ADCx\_DP0, ADCx\_DM0.

The ADCx\_DP2 and ADCx\_DM2 ADC inputs are connected to the PGA outputs and are not direct device pins. Accuracy specifications for these pins are defined in Table 27 and Table 28.

All other ADC channels meet the 13-bit differential/12-bit single-ended accuracy specifications.

| Symbol            | Description                       | Conditions                                                        | Min.              | Typ. <sup>1</sup> | Max.              | Unit | Notes |

|-------------------|-----------------------------------|-------------------------------------------------------------------|-------------------|-------------------|-------------------|------|-------|

| V <sub>DDA</sub>  | Supply voltage                    | Absolute                                                          | 1.71              | —                 | 3.6               | V    |       |

| $\Delta V_{DDA}$  | Supply voltage                    | Delta to V <sub>DD</sub> (V <sub>DD</sub> -<br>V <sub>DDA</sub> ) | -100              | 0                 | +100              | mV   | 2     |

| $\Delta V_{SSA}$  | Ground voltage                    | Delta to V <sub>SS</sub> (V <sub>SS</sub> -<br>V <sub>SSA</sub> ) | -100              | 0                 | +100              | mV   | 2     |

| V <sub>REFH</sub> | ADC reference voltage high        |                                                                   | 1.13              | V <sub>DDA</sub>  | V <sub>DDA</sub>  | V    |       |

| V <sub>REFL</sub> | Reference<br>voltage low          |                                                                   | V <sub>SSA</sub>  | V <sub>SSA</sub>  | V <sub>SSA</sub>  | V    |       |

| V <sub>ADIN</sub> | Input voltage                     |                                                                   | V <sub>REFL</sub> | —                 | V <sub>REFH</sub> | V    |       |

| C <sub>ADIN</sub> | Input<br>capacitance              | <ul> <li>16 bit modes</li> <li>8/10/12 bit modes</li> </ul>       | -                 | 8<br>4            | 10<br>5           | pF   |       |

| R <sub>ADIN</sub> | Input resistance                  |                                                                   | -                 | 2                 | 5                 | kΩ   |       |

| R <sub>AS</sub>   | Analog source<br>resistance       | 13/12 bit modes<br>f <sub>ADCK</sub> < 4MHz                       | _                 | _                 | 5                 | kΩ   | 3     |

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency | ≤ 13 bit modes                                                    | 1.0               | _                 | 18.0              | MHz  | 4     |

| f <sub>ADCK</sub> | ADC conversion<br>clock frequency | 16 bit modes                                                      | 2.0               | _                 | 12.0              | MHz  | 4     |

### 6.6.1.1 16-bit ADC operating conditions Table 25. 16-bit ADC operating conditions

Table continues on the next page...

| Symbol            | Description            | Conditions                                                                           | Min.   | Typ. <sup>1</sup> | Max.    | Unit | Notes |

|-------------------|------------------------|--------------------------------------------------------------------------------------|--------|-------------------|---------|------|-------|

| C <sub>rate</sub> | ADC conversion<br>rate | ≤ 13 bit modes<br>No ADC hardware<br>averaging<br>Continuous<br>conversions enabled, | 20.000 |                   | 818.330 | Ksps | 5     |

| C <sub>rate</sub> | ADC conversion         | subsequent conversion<br>time<br>16 bit modes                                        |        |                   |         |      | 5     |

|                   | rate                   | No ADC hardware averaging                                                            | 37.037 | —                 | 461.467 | Ksps |       |

|                   |                        | Continuous<br>conversions enabled,<br>subsequent conversion<br>time                  |        |                   |         |      |       |

Table 25. 16-bit ADC operating conditions (continued)

Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25°C, f<sub>ADCK</sub> = 1.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

2. DC potential difference.

3. This resistance is external to MCU. The analog source resistance should be kept as low as possible in order to achieve the best results. The results in this datasheet were derived from a system which has <8  $\Omega$  analog source resistance. The R<sub>AS</sub>/ C<sub>AS</sub> time constant should be kept to <1ns.

4. To use the maximum ADC conversion clock frequency, the ADHSC bit should be set and the ADLPC bit should be clear.

For guidelines and examples of conversion rate calculation, download the ADC calculator tool: http://cache.freescale.com/ files/soft\_dev\_tools/software/app\_software/converters/ADC\_CALCULATOR\_CNV.zip?fpsp=1

Figure 14. ADC input impedance equivalency diagram

Peripheral operating requirements and behaviors

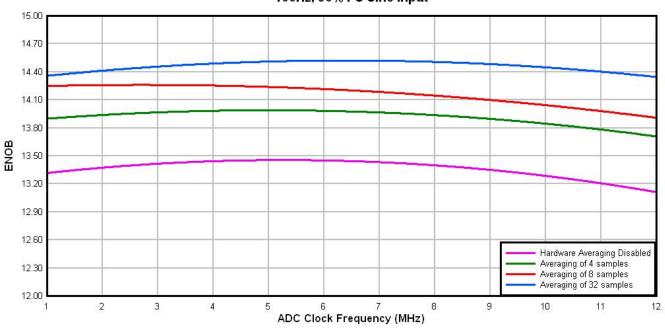

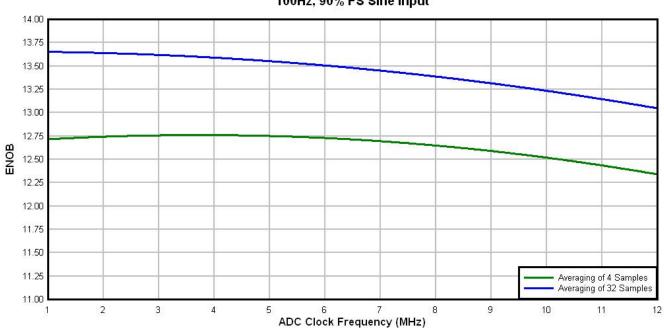

Typical ADC 16-bit Differential ENOB vs ADC Clock 100Hz, 90% FS Sine Input

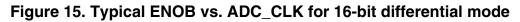

Typical ADC 16-bit Single-Ended ENOB vs ADC Clock 100Hz, 90% FS Sine Input

Figure 16. Typical ENOB vs. ADC\_CLK for 16-bit single-ended mode

### 6.6.1.4 16-bit ADC with PGA characteristics with Chop enabled (ADC\_PGA[PGACHPb] =0) Table 28. 16-bit ADC with PGA characteristics

| Symbol               | Description                  | Conditions                                                    | Min.                                                   | Typ. <sup>1</sup>                  | Max.                          | Unit   | Notes                                                                 |

|----------------------|------------------------------|---------------------------------------------------------------|--------------------------------------------------------|------------------------------------|-------------------------------|--------|-----------------------------------------------------------------------|

| I <sub>DDA_PGA</sub> | Supply current               | Low power<br>(ADC_PGA[PGALPb]=0)                              | _                                                      | 420                                | 644                           | μA     | 2                                                                     |

| I <sub>DC_PGA</sub>  | Input DC current             |                                                               | $\frac{2}{R_{\text{PGAD}}} \left( \frac{1}{2} \right)$ | V <sub>REFPGA</sub> ×0.5<br>(Gain+ | $\frac{183}{-1} - V_{\rm CM}$ | A      | 3                                                                     |

|                      |                              | Gain =1, $V_{REFPGA}$ =1.2V,<br>$V_{CM}$ =0.5V                | _                                                      | 1.54                               | _                             | μΑ     |                                                                       |

|                      |                              | Gain =64, V <sub>REFPGA</sub> =1.2V,<br>V <sub>CM</sub> =0.1V | -                                                      | 0.57                               | _                             | μΑ     |                                                                       |

| G                    | Gain <sup>4</sup>            | • PGAG=0                                                      | 0.95                                                   | 1                                  | 1.05                          |        | $R_{AS} < 100\Omega$                                                  |

|                      |                              | • PGAG=1                                                      | 1.9                                                    | 2                                  | 2.1                           |        |                                                                       |

|                      |                              | • PGAG=2                                                      | 3.8                                                    | 4                                  | 4.2                           |        |                                                                       |

|                      |                              | • PGAG=3                                                      | 7.6                                                    | 8                                  | 8.4                           |        |                                                                       |

|                      |                              | • PGAG=4                                                      | 15.2                                                   | 16                                 | 16.6                          |        |                                                                       |

|                      |                              | • PGAG=5                                                      | 30.0                                                   | 31.6                               | 33.2                          |        |                                                                       |

|                      |                              | • PGAG=6                                                      | 58.8                                                   | 63.3                               | 67.8                          |        |                                                                       |

| BW                   | Input signal                 | 16-bit modes                                                  |                                                        | _                                  | 4                             | kHz    |                                                                       |

|                      | bandwidth                    | <ul> <li>&lt; 16-bit modes</li> </ul>                         | _                                                      | _                                  | 40                            | kHz    |                                                                       |

| PSRR                 | Power supply rejection ratio | Gain=1                                                        | _                                                      | -84                                | _                             | dB     | V <sub>DDA</sub> = 3V<br>±100mV,<br>f <sub>VDDA</sub> = 50Hz,<br>60Hz |

| CMRR                 | Common mode                  | • Gain=1                                                      | _                                                      | -84                                | —                             | dB     | V <sub>CM</sub> =                                                     |

|                      | rejection ratio              | • Gain=64                                                     | _                                                      | -85                                | _                             | dB     | 500mVpp,<br>f <sub>VCM</sub> = 50Hz,<br>100Hz                         |

| V <sub>OFS</sub>     | Input offset<br>voltage      |                                                               | _                                                      | 0.2                                |                               | mV     | Output offset =<br>V <sub>OFS</sub> *(Gain+1                          |

| T <sub>GSW</sub>     | Gain switching settling time |                                                               | —                                                      | —                                  | 10                            | μs     | 5                                                                     |

| dG/dT                | Gain drift over full         | • Gain=1                                                      | _                                                      | 6                                  | 10                            | ppm/°C |                                                                       |

|                      | temperature<br>range         | • Gain=64                                                     | —                                                      | 31                                 | 42                            | ppm/°C |                                                                       |

| dG/dV <sub>DDA</sub> | Gain drift over              | • Gain=1                                                      | —                                                      | 0.07                               | 0.21                          | %/V    | V <sub>DDA</sub> from 1.7                                             |

|                      | supply voltage               | • Gain=64                                                     | _                                                      | 0.14                               | 0.31                          | %/V    | to 3.6V                                                               |

Table continues on the next page ...

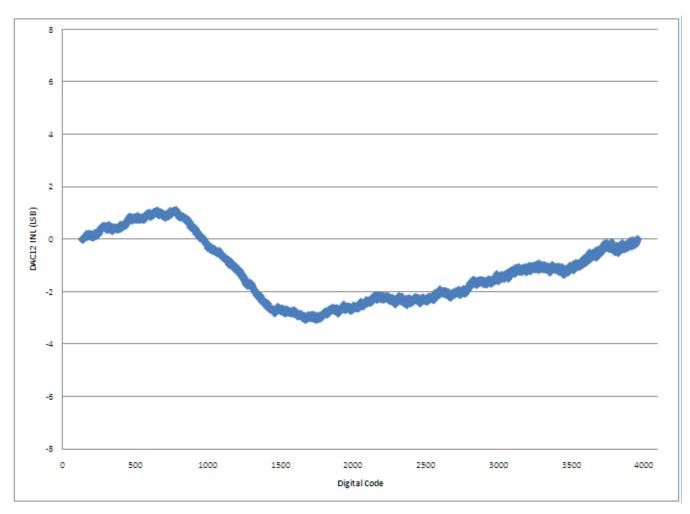

6. VDDA = 3.0V, reference select set for VDDA (DACx\_CO:DACRFS = 1), high power mode(DACx\_CO:LPEN = 0), DAC set to 0x800, Temp range from -40C to 105C

Figure 19. Typical INL error vs. digital code

| Symbol              | Description                                                                                | Min.   | Тур.  | Max.   | Unit | Notes |

|---------------------|--------------------------------------------------------------------------------------------|--------|-------|--------|------|-------|

| V <sub>out</sub>    | Voltage reference output with factory trim at nominal $V_{\text{DDA}}$ and temperature=25C | 1.1915 | 1.195 | 1.1977 | V    |       |

| V <sub>out</sub>    | Voltage reference output — factory trim                                                    | 1.1584 | _     | 1.2376 | V    |       |

| V <sub>out</sub>    | Voltage reference output — user trim                                                       | 1.193  | _     | 1.197  | V    |       |

| V <sub>step</sub>   | Voltage reference trim step                                                                | _      | 0.5   | _      | mV   |       |

| V <sub>tdrift</sub> | Temperature drift (Vmax -Vmin across the full temperature range)                           | _      | _     | 80     | mV   |       |

| I <sub>bg</sub>     | Bandgap only current                                                                       | _      | _     | 80     | μA   | 1     |

| I <sub>lp</sub>     | Low-power buffer current                                                                   | _      | _     | 360    | uA   | 1     |

| I <sub>hp</sub>     | High-power buffer current                                                                  | _      | —     | 1      | mA   | 1     |

| $\Delta V_{LOAD}$   | Load regulation                                                                            |        |       |        | μV   | 1, 2  |

|                     | • current = ± 1.0 mA                                                                       | —      | 200   | _      |      |       |

| T <sub>stup</sub>   | Buffer startup time                                                                        |        | —     | 20     | μs   |       |

| V <sub>vdrift</sub> | Voltage drift (Vmax - Vmin across the full voltage range)                                  |        | 2     | _      | mV   | 1     |

### Table 33. VREF full-range operating behaviors

1. See the chip's Reference Manual for the appropriate settings of the VREF Status and Control register.

2. Load regulation voltage is the difference between the VREF\_OUT voltage with no load vs. voltage with defined load

### Table 34. VREF limited-range operating requirements

| Symbol         | Description | Min. | Max. | Unit | Notes |

|----------------|-------------|------|------|------|-------|

| T <sub>A</sub> | Temperature | 0    | 50   | °C   |       |

### Table 35. VREF limited-range operating behaviors

| Symbol           | Description                                | Min.  | Max.  | Unit | Notes |

|------------------|--------------------------------------------|-------|-------|------|-------|

| V <sub>out</sub> | Voltage reference output with factory trim | 1.173 | 1.225 | V    |       |

| Symbol         | Description                                      | Min   | Max   | Unit | Notes |

|----------------|--------------------------------------------------|-------|-------|------|-------|

| VREFH          | Voltage reference<br>output with factory<br>trim | 1.173 | 1.225 | V    |       |

| VREFL          | Voltage reference<br>output                      | 0.38  | 0.42  | V    |       |

| IBIASP_AFE_4µA | P-bias current<br>output                         | 3.5µ  | 4.5µ  | A    |       |

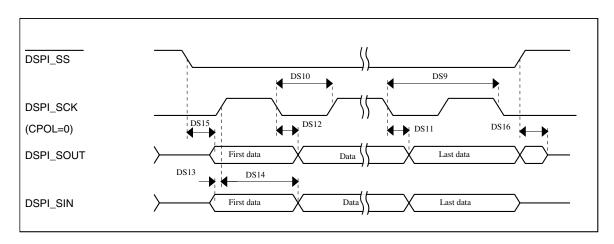

| Num  | Description                              | Min.                      | Max.                     | Unit |

|------|------------------------------------------|---------------------------|--------------------------|------|

|      | Operating voltage                        | 1.71                      | 3.6                      | V    |

|      | Frequency of operation                   | _                         | 6.25                     | MHz  |

| DS9  | DSPI_SCK input cycle time                | 8 x t <sub>BUS</sub>      | _                        | ns   |

| DS10 | DSPI_SCK input high/low time             | (t <sub>SCK</sub> /2) - 4 | (t <sub>SCK/2)</sub> + 4 | ns   |

| DS11 | DSPI_SCK to DSPI_SOUT valid              | _                         | 20                       | ns   |

| DS12 | DSPI_SCK to DSPI_SOUT invalid            | 0                         | —                        | ns   |

| DS13 | DSPI_SIN to DSPI_SCK input setup         | 2                         | _                        | ns   |

| DS14 | DSPI_SCK to DSPI_SIN input hold          | 7                         | —                        | ns   |

| DS15 | DSPI_SS active to DSPI_SOUT driven       | _                         | 19                       | ns   |

| DS16 | DSPI_SS inactive to DSPI_SOUT not driven | _                         | 19                       | ns   |

Figure 24. DSPI classic SPI timing — slave mode

# 6.8.4 I<sup>2</sup>C switching specifications

See General switching specifications.

# 6.8.5 UART switching specifications

See General switching specifications.

# 6.8.6 I2S/SAI Switching Specifications

This section provides the AC timing for the I2S/SAI module in master mode (clocks are driven) and slave mode (clocks are input). All timing is given for noninverted serial clock polarity (TCR2[BCP] is 0, RCR2[BCP] is 0) and a noninverted frame sync (TCR4[FSP] is 0, RCR4[FSP] is 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the bit clock signal (BCLK) and/or the frame sync (FS) signal shown in the following figures.

# 6.8.6.1 Normal Run, Wait and Stop mode performance over the full operating voltage range

This section provides the operating performance over the full operating voltage for the device in Normal Run, Wait and Stop modes.

| Num. | Characteristic                                                    | Min. | Max. | Unit        |

|------|-------------------------------------------------------------------|------|------|-------------|

|      | Operating voltage                                                 | 1.71 | 3.6  | V           |

| S1   | I2S_MCLK cycle time                                               | 40   | —    | ns          |

| S2   | I2S_MCLK pulse width high/low                                     | 45%  | 55%  | MCLK period |

| S3   | I2S_TX_BCLK/I2S_RX_BCLK cycle time (output)                       | 80   | —    | ns          |

| S4   | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low                      | 45%  | 55%  | BCLK period |

| S5   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output valid   | —    | 15   | ns          |

| S6   | I2S_TX_BCLK/I2S_RX_BCLK to I2S_TX_FS/<br>I2S_RX_FS output invalid | -1.0 | —    | ns          |

| S7   | I2S_TX_BCLK to I2S_TXD valid                                      | —    | 15   | ns          |

| S8   | I2S_TX_BCLK to I2S_TXD invalid                                    | 0    | —    | ns          |

| S9   | I2S_RXD/I2S_RX_FS input setup before<br>I2S_RX_BCLK               | 20.5 | —    | ns          |

| S10  | I2S_RXD/I2S_RX_FS input hold after I2S_RX_BCLK                    | 0    | —    | ns          |

Table 41. I2S/SAI master mode timing in Normal Run, Wait and Stop modes (full voltage range)

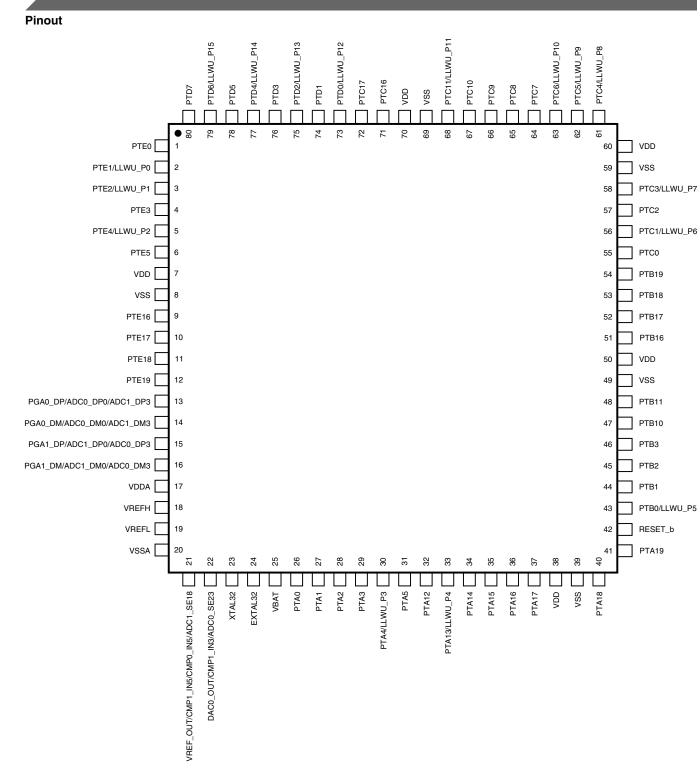

#### Pinout

| 81<br>Map<br>Bga | 80<br>LQFP | Pin Name                                         | Default                                          | ALTO                                             | ALT1              | ALT2                                | ALT3                                | ALT4       | ALT5     | ALT6             | ALT7                   | EzPort   |

|------------------|------------|--------------------------------------------------|--------------------------------------------------|--------------------------------------------------|-------------------|-------------------------------------|-------------------------------------|------------|----------|------------------|------------------------|----------|

| L3               | 21         | VREF_OUT/<br>CMP1_IN5/<br>CMP0_IN5/<br>ADC1_SE18 | VREF_OUT/<br>CMP1_IN5/<br>CMP0_IN5/<br>ADC1_SE18 | VREF_OUT/<br>CMP1_IN5/<br>CMP0_IN5/<br>ADC1_SE18 |                   |                                     |                                     |            |          |                  |                        |          |

| K5               | 22         | DAC0_OUT/<br>CMP1_IN3/<br>ADC0_SE23              | DAC0_OUT/<br>CMP1_IN3/<br>ADC0_SE23              | DAC0_OUT/<br>CMP1_IN3/<br>ADC0_SE23              |                   |                                     |                                     |            |          |                  |                        |          |

| L7               | -          | RTC_<br>WAKEUP_B                                 | RTC_<br>WAKEUP_B                                 | RTC_<br>WAKEUP_B                                 |                   |                                     |                                     |            |          |                  |                        |          |

| L4               | 23         | XTAL32                                           | XTAL32                                           | XTAL32                                           |                   |                                     |                                     |            |          |                  |                        |          |

| L5               | 24         | EXTAL32                                          | EXTAL32                                          | EXTAL32                                          |                   |                                     |                                     |            |          |                  |                        |          |

| K6               | 25         | VBAT                                             | VBAT                                             | VBAT                                             |                   |                                     |                                     |            |          |                  |                        |          |

| J6               | 26         | PTA0                                             | JTAG_TCLK/<br>SWD_CLK/<br>EZP_CLK                | TSI0_CH1                                         | PTA0              | UARTO_CTS_<br>b/<br>UARTO_COL_<br>b | FTM0_CH5                            |            |          |                  | JTAG_TCLK/<br>SWD_CLK  | EZP_CLK  |

| H8               | 27         | PTA1                                             | JTAG_TDI/<br>EZP_DI                              | TSI0_CH2                                         | PTA1              | UART0_RX                            | FTM0_CH6                            |            |          |                  | JTAG_TDI               | EZP_DI   |

| J7               | 28         | PTA2                                             | JTAG_TDO/<br>TRACE_SWO/<br>EZP_DO                | TSI0_CH3                                         | PTA2              | UART0_TX                            | FTM0_CH7                            |            |          |                  | JTAG_TDO/<br>TRACE_SWO | EZP_DO   |

| H9               | 29         | PTA3                                             | JTAG_TMS/<br>SWD_DIO                             | TSI0_CH4                                         | PTA3              | UART0_RTS_<br>b                     | FTM0_CH0                            |            |          |                  | JTAG_TMS/<br>SWD_DIO   |          |

| J8               | 30         | PTA4/<br>LLWU_P3                                 | NMI_b/<br>EZP_CS_b                               | TSI0_CH5                                         | PTA4/<br>LLWU_P3  |                                     | FTM0_CH1                            |            |          |                  | NMI_b                  | EZP_CS_b |

| K7               | 31         | PTA5                                             | DISABLED                                         |                                                  | PTA5              |                                     | FTM0_CH2                            |            | CMP2_OUT | I2S0_TX_<br>BCLK | JTAG_TRST_<br>b        |          |

| E5               | —          | VDD                                              | VDD                                              | VDD                                              |                   |                                     |                                     |            |          |                  |                        |          |

| G3               | -          | VSS                                              | VSS                                              | VSS                                              |                   |                                     |                                     |            |          |                  |                        |          |

| K8               | 32         | PTA12                                            | CMP2_IN0                                         | CMP2_IN0                                         | PTA12             | CAN0_TX                             | FTM1_CH0                            |            |          | I2S0_TXD0        | FTM1_QD_<br>PHA        |          |

| L8               | 33         | PTA13/<br>LLWU_P4                                | CMP2_IN1                                         | CMP2_IN1                                         | PTA13/<br>LLWU_P4 | CAN0_RX                             | FTM1_CH1                            |            |          | I2S0_TX_FS       | FTM1_QD_<br>PHB        |          |

| K9               | 34         | PTA14                                            | DISABLED                                         |                                                  | PTA14             | SPI0_PCS0                           | UART0_TX                            |            |          | I2S0_RX_<br>BCLK | I2S0_TXD1              |          |

| L9               | 35         | PTA15                                            | DISABLED                                         |                                                  | PTA15             | SPI0_SCK                            | UART0_RX                            |            |          | I2S0_RXD0        |                        |          |

| J10              | 36         | PTA16                                            | DISABLED                                         |                                                  | PTA16             | SPI0_SOUT                           | UARTO_CTS_<br>b/<br>UARTO_COL_<br>b |            |          | I2S0_RX_FS       | 12S0_RXD1              |          |

| H10              | 37         | PTA17                                            | ADC1_SE17                                        | ADC1_SE17                                        | PTA17             | SPI0_SIN                            | UARTO_RTS_<br>b                     |            |          | I2S0_MCLK        |                        |          |

| L10              | 38         | VDD                                              | VDD                                              | VDD                                              |                   |                                     |                                     |            |          |                  |                        |          |

| K10              | 39         | VSS                                              | VSS                                              | VSS                                              |                   |                                     |                                     |            |          |                  |                        |          |

| L11              | 40         | PTA18                                            | EXTALO                                           | EXTALO                                           | PTA18             |                                     | FTM0_FLT2                           | FTM_CLKIN0 |          |                  |                        |          |

| K11              | 41         | PTA19                                            | XTALO                                            | XTAL0                                            | PTA19             |                                     | FTM1_FLT0                           | FTM_CLKIN1 |          | LPTMR0_<br>ALT1  |                        |          |

| 81<br>MAP | 80<br>LQFP | Pin Name | Default | ALT0 | ALT1 | ALT2 | ALT3 | ALT4 | ALT5 | ALT6 | ALT7 | EzPort |

|-----------|------------|----------|---------|------|------|------|------|------|------|------|------|--------|

| BGA       | LUFP       |          |         |      |      |      |      |      |      |      |      |        |

| J9        | -          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| J4        | _          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| H11       | _          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| F11       | _          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| E11       | _          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| D11       | _          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| E10       | _          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| F10       | _          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| F9        | _          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| F8        | _          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| E8        | _          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| B6        | _          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| A6        | _          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| A5        | -          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| B5        | _          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| B4        | -          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| A4        | _          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| A10       | —          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| A9        | —          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| B1        | _          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| C2        | _          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| C1        | -          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| D2        | _          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| D1        | _          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

| E1        | _          | NC       | NC      | NC   |      |      |      |      |      |      |      |        |

# 8.2 K10 Pinouts

The below figure shows the pinout diagram for the devices supported by this document. Many signals may be multiplexed onto a single pin. To determine what signals can be used on which pin, see the previous section.

Pinout