## Intel - 5CSEBA5U19C7N Datasheet

Welcome to E-XFL.COM

Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

### What are Embedded - System On Chip (SoC)?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

| Product Status          | Active                                                                             |

|-------------------------|------------------------------------------------------------------------------------|

| Architecture            | MCU, FPGA                                                                          |

| Core Processor          | Dual ARM® Cortex®-A9 MPCore <sup>™</sup> with CoreSight <sup>™</sup>               |

| Flash Size              | -                                                                                  |

| RAM Size                | 64KB                                                                               |

| Peripherals             | DMA, POR, WDT                                                                      |

| Connectivity            | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Speed                   | 800MHz                                                                             |

| Primary Attributes      | FPGA - 85K Logic Elements                                                          |

| Operating Temperature   | 0°C ~ 85°C (TJ)                                                                    |

| Package / Case          | 484-FBGA                                                                           |

| Supplier Device Package | 484-UBGA (19x19)                                                                   |

| Purchase URL            | https://www.e-xfl.com/product-detail/intel/5cseba5u19c7n                           |

|                         |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

This datasheet describes the electrical characteristics, switching characteristics, configuration specifications, and I/O timing for Cyclone<sup>®</sup> V devices.

Cyclone V devices are offered in commercial and industrial grades. Commercial devices are offered in -C6 (fastest), -C7, and -C8 speed grades. Industrial grade devices are offered in the -I7 speed grade. Automotive devices are offered in the -A7 speed grade.

Cyclone V SoC devices are also offered in a low-power variant, as indicated by the L power option in the device part number. These devices have 30% static power reduction for devices with 25K LE and 40K LE, and 20% static power reduction for devices with 85K LE and 110K LE. Note that the L power option devices are only available in –I7 speed grade, and have the equivalent operating conditions and timing specifications as the standard –I7 speed grade devices.

| Density | Ordering Part Number (OPN) | Static Power Reduction |

|---------|----------------------------|------------------------|

| 25K LE  | 5CSEBA2U19I7LN             | 30%                    |

|         | 5CSEBA2U23I7LN             |                        |

|         | 5CSXFC2C6U23I7LN           |                        |

| 40K LE  | 5CSEBA4U19I7LN             |                        |

|         | 5CSEBA4U23I7LN             |                        |

|         | 5CSXFC4C6U23I7LN           |                        |

| 85K LE  | 5CSEBA5U19I7LN             | 20%                    |

|         | 5CSEBA5U23I7LN             |                        |

|         | 5CSXC5C6U23I7LN            |                        |

|         |                            | continued              |

#### Table 1.Low Power Variants

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

\*Other names and brands may be claimed as the property of others.

## **Maximum Allowed Overshoot and Undershoot Voltage**

During transitions, input signals may overshoot to the voltage listed in the following table and undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

The maximum allowed overshoot duration is specified as a percentage of high time over the lifetime of the device. A DC signal is equivalent to 100% duty cycle.

For example, a signal that overshoots to 4.00 V can only be at 4.00 V for  $\sim$ 15% over the lifetime of the device; for a device lifetime of 10 years, this amounts to 1.5 years.

#### Table 3. Maximum Allowed Overshoot During Transitions for Cyclone V Devices

| Symbol  | Description      | Condition (V) | Overshoot Duration as % of High Time | Unit      |

|---------|------------------|---------------|--------------------------------------|-----------|

| Vi (AC) | AC input voltage | 3.8           | 100                                  | %         |

|         |                  | 3.85          | 68                                   | %         |

|         |                  | 3.9           | 45                                   | %         |

|         |                  | 3.95          | 28                                   | %         |

|         |                  | 4             | 15                                   | %         |

|         |                  | 4.05          | 13                                   | %         |

|         |                  |               | 4.1                                  | 11        |

|         |                  | 4.15          | 9                                    | %         |

|         |                  | 4.2           | 8                                    | %         |

|         |                  | 4.25          | 7                                    | %         |

|         |                  | 4.3           | 5.4                                  | %         |

|         |                  | 4.35          | 3.2                                  | %         |

|         |                  | 4.4           | 1.9                                  | %         |

|         |                  | 4.45          | 1.1                                  | %         |

|         | 1                |               |                                      | continued |

This table lists the maximum allowed input overshoot voltage and the duration of the overshoot voltage as a percentage of device lifetime.

| Symbol                                     | Description                                   | Condition | Minimum <sup>(11)</sup> | Typical | Maximum <sup>(11)</sup> | Unit |

|--------------------------------------------|-----------------------------------------------|-----------|-------------------------|---------|-------------------------|------|

|                                            |                                               | 1.8 V     | 1.71                    | 1.8     | 1.89                    | V    |

| V <sub>CCPLL_HPS</sub>                     | HPS PLL analog voltage regulator power supply | —         | 2.375                   | 2.5     | 2.625                   | V    |

| V <sub>CC_AUX_SHARED</sub> <sup>(14)</sup> | HPS auxiliary power supply                    | _         | 2.375                   | 2.5     | 2.625                   | V    |

## **Related Information**

Recommended Operating Conditions on page 8 Provides the steady-state voltage values for the FPGA portion of the device.

## **DC Characteristics**

#### **Supply Current and Power Consumption**

Intel offers two ways to estimate power for your design—the Excel-based EPE and the Intel<sup>®</sup> Quartus<sup>®</sup> Prime Power Analyzer feature.

Use the Excel-based EPE before you start your design to estimate the supply current for your design. The EPE provides a magnitude estimate of the device power because these currents vary greatly with the resources you use.

The Intel Quartus Prime Power Analyzer provides better quality estimates based on the specifics of the design after you complete place-and-route. The Power Analyzer can apply a combination of user-entered, simulation-derived, and estimated signal activities that, when combined with detailed circuit models, yields very accurate power estimates.

#### **Related Information**

- Early Power Estimator User Guide Provides more information about power estimation tools.

- Power Analysis chapter, Intel Quartus Prime Handbook Provides more information about power estimation tools.

<sup>&</sup>lt;sup>(11)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(14)</sup> V<sub>CC\_AUX\_SHARED</sub> must be powered by the same source as V<sub>CC\_AUX</sub> for Cyclone V SX C5, C6, D5, and D6 devices, and Cyclone V SE A5 and A6 devices.

## Table 9. OCT Calibration Accuracy Specifications for Cyclone V Devices

Calibration accuracy for the calibrated on-chip series termination ( $R_S$  OCT) and on-chip parallel termination ( $R_T$  OCT) are applicable at the moment of calibration. When process, voltage, and temperature (PVT) conditions change after calibration, the tolerance may change.

| Symbol                                                                             | Description                                                                                                                            | Condition (V)                               | Ca         | alibration Accura | су         | Unit |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------|-------------------|------------|------|

|                                                                                    |                                                                                                                                        |                                             | -C6        | -I7, -C7          | -C8, -A7   |      |

| 25-Ω R <sub>S</sub>                                                                | Internal series termination with calibration (25-Ω setting)                                                                            | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 | ±15        | ±15               | ±15        | %    |

| 50-Ω R <sub>S</sub>                                                                | Internal series termination with calibration (50-Ω setting)                                                                            | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 | ±15        | ±15               | ±15        | %    |

| 34- $\Omega$ and 40- $\Omega$ $R_S$                                                | Internal series termination with calibration ( $34-\Omega$ and $40-\Omega$ setting)                                                    | V <sub>CCIO</sub> = 1.5, 1.35, 1.25, 1.2    | ±15        | ±15               | ±15        | %    |

| 48- $\Omega$ , 60- $\Omega$ , and 80- $\Omega$ R <sub>S</sub>                      | Internal series termination with calibration (48- $\Omega$ , 60- $\Omega$ , and 80- $\Omega$ setting)                                  | V <sub>CCI0</sub> = 1.2                     | ±15        | ±15               | ±15        | %    |

| 50-Ω R <sub>T</sub>                                                                | Internal parallel termination with calibration (50-Ω setting)                                                                          | V <sub>CCIO</sub> = 2.5, 1.8, 1.5, 1.2      | -10 to +40 | -10 to +40        | -10 to +40 | %    |

| 20- $\Omega$ , 30- $\Omega$ , 40- $\Omega$ ,60- $\Omega$ , and 120- $\Omega$ $R_T$ | Internal parallel termination with calibration (20- $\Omega$ , 30- $\Omega$ , 40- $\Omega$ , 60- $\Omega$ , and 120- $\Omega$ setting) | V <sub>CCIO</sub> = 1.5, 1.35, 1.25         | -10 to +40 | -10 to +40        | -10 to +40 | %    |

| 60- $\Omega$ and 120- $\Omega$ $R_T$                                               | Internal parallel termination with calibration ( $60-\Omega$ and $120-\Omega$ setting)                                                 | V <sub>CCIO</sub> = 1.2                     | -10 to +40 | -10 to +40        | -10 to +40 | %    |

| $25-\Omega R_{S\_left\_shift}$                                                     | Internal left shift series termination with calibration (25- $\Omega R_{S\_left\_shift}$ setting)                                      | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 | ±15        | ±15               | ±15        | %    |

| I/O Standard            | V <sub>CCI0</sub> (V) |      |       | V <sub>REF</sub> (V)     |                       |                        | ν <sub>ττ</sub> (ν)      |                       |                        |  |

|-------------------------|-----------------------|------|-------|--------------------------|-----------------------|------------------------|--------------------------|-----------------------|------------------------|--|

|                         | Min                   | Тур  | Мах   | Min                      | Тур                   | Max                    | Min                      | Тур                   | Max                    |  |

| SSTL-15 Class I,<br>II  | 1.425                 | 1.5  | 1.575 | 0.49 × V <sub>CCIO</sub> | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ | $0.49 \times V_{CCIO}$   | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ |  |

| SSTL-135 Class<br>I, II | 1.283                 | 1.35 | 1.418 | 0.49 × V <sub>CCIO</sub> | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ | $0.49 \times V_{CCIO}$   | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ |  |

| SSTL-125 Class<br>I, II | 1.19                  | 1.25 | 1.26  | 0.49 × V <sub>CCIO</sub> | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ | 0.49 × V <sub>CCIO</sub> | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ |  |

| HSTL-18 Class I,<br>II  | 1.71                  | 1.8  | 1.89  | 0.85                     | 0.9                   | 0.95                   | _                        | V <sub>CCIO</sub> /2  | _                      |  |

| HSTL-15 Class I,<br>II  | 1.425                 | 1.5  | 1.575 | 0.68                     | 0.75                  | 0.9                    | _                        | V <sub>CCIO</sub> /2  | _                      |  |

| HSTL-12 Class I,<br>II  | 1.14                  | 1.2  | 1.26  | $0.47 \times V_{CCIO}$   | $0.5 \times V_{CCIO}$ | $0.53 \times V_{CCIO}$ | -                        | V <sub>CCIO</sub> /2  | _                      |  |

| HSUL-12                 | 1.14                  | 1.2  | 1.3   | $0.49 \times V_{CCIO}$   | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ | _                        | -                     | _                      |  |

## Single-Ended SSTL, HSTL, and HSUL I/O Standards Signal Specifications

## Table 17. Single-Ended SSTL, HSTL, and HSUL I/O Standards Signal Specifications for Cyclone V Devices

| I/O Standard        | VIL  | (DC) <b>(V)</b>          | V <sub>IH(DC</sub>       | c) <b>(V)</b>           | V <sub>IL(AC)</sub> (V) | V <sub>IH(AC)</sub> (V) | V <sub>OL</sub> (V)     | V <sub>он</sub> (V)      | I <sub>OL</sub> <sup>(19)</sup> | I <sub>OH</sub> <sup>(19)</sup> |

|---------------------|------|--------------------------|--------------------------|-------------------------|-------------------------|-------------------------|-------------------------|--------------------------|---------------------------------|---------------------------------|

|                     | Min  | Max                      | Min                      | Max                     | Max                     | Min                     | Max                     | Min                      | (mA)                            | (mA)                            |

| SSTL-2 Class I      | -0.3 | V <sub>REF</sub> - 0.15  | $V_{REF} + 0.15$         | $V_{CCIO} + 0.3$        | V <sub>REF</sub> - 0.31 | V <sub>REF</sub> + 0.31 | V <sub>TT</sub> - 0.608 | V <sub>TT</sub> + 0.608  | 8.1                             | -8.1                            |

| SSTL-2 Class<br>II  | -0.3 | V <sub>REF</sub> - 0.15  | V <sub>REF</sub> + 0.15  | V <sub>CCI0</sub> + 0.3 | V <sub>REF</sub> - 0.31 | V <sub>REF</sub> + 0.31 | V <sub>TT</sub> - 0.81  | V <sub>TT</sub> + 0.81   | 16.2                            | -16.2                           |

| SSTL-18 Class<br>I  | -0.3 | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 | V <sub>CCI0</sub> + 0.3 | V <sub>REF</sub> – 0.25 | V <sub>REF</sub> + 0.25 | V <sub>TT</sub> – 0.603 | V <sub>TT</sub> + 0.603  | 6.7                             | -6.7                            |

| SSTL-18 Class<br>II | -0.3 | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 | V <sub>CCI0</sub> + 0.3 | V <sub>REF</sub> - 0.25 | V <sub>REF</sub> + 0.25 | 0.28                    | V <sub>CCIO</sub> – 0.28 | 13.4                            | -13.4                           |

|                     |      | •                        |                          |                         |                         |                         |                         |                          | со                              | ntinued                         |

<sup>&</sup>lt;sup>(19)</sup> To meet the  $I_{OL}$  and  $I_{OH}$  specifications, you must set the current strength settings accordingly. For example, to meet the SSTL15CI specification (8 mA), you should set the current strength settings to 8 mA. Setting at lower current strength may not meet the  $I_{OL}$  and  $I_{OH}$  specifications in the datasheet.

| I/O Standard        | VIL   | <sub>(DC)</sub> (V)     | V <sub>IH(DC</sub>      | c) (V)                   | V <sub>IL(AC)</sub> (V)  | V <sub>IH(AC)</sub> (V)  | V <sub>OL</sub> (V)    | V <sub>OH</sub> (V)     | I <sub>OL</sub> <sup>(19)</sup> | I <sub>OH</sub> <sup>(19)</sup> |

|---------------------|-------|-------------------------|-------------------------|--------------------------|--------------------------|--------------------------|------------------------|-------------------------|---------------------------------|---------------------------------|

|                     | Min   | Max                     | Min                     | Max                      | Max                      | Min                      | Max                    | Min                     | (mA)                            | (mA)                            |

| SSTL-15 Class<br>I  | _     | V <sub>REF</sub> - 0.1  | $V_{REF} + 0.1$         | _                        | V <sub>REF</sub> - 0.175 | V <sub>REF</sub> + 0.175 | $0.2 \times V_{CCIO}$  | 0.8 × V <sub>CCIO</sub> | 8                               | -8                              |

| SSTL-15 Class<br>II | _     | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | -                        | V <sub>REF</sub> - 0.175 | V <sub>REF</sub> + 0.175 | $0.2 \times V_{CCIO}$  | $0.8 \times V_{CCIO}$   | 16                              | -16                             |

| SSTL-135            | _     | V <sub>REF</sub> - 0.09 | V <sub>REF</sub> + 0.09 | _                        | V <sub>REF</sub> - 0.16  | V <sub>REF</sub> + 0.16  | $0.2 \times V_{CCIO}$  | $0.8 \times V_{CCIO}$   | _                               | _                               |

| SSTL-125            | _     | V <sub>REF</sub> - 0.85 | V <sub>REF</sub> + 0.85 | _                        | V <sub>REF</sub> - 0.15  | V <sub>REF</sub> + 0.15  | $0.2 \times V_{CCIO}$  | $0.8 \times V_{CCIO}$   | -                               | -                               |

| HSTL-18 Class<br>I  | _     | V <sub>REF</sub> - 0.1  | $V_{REF} + 0.1$         | _                        | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 0.4                    | V <sub>CCIO</sub> – 0.4 | 8                               | -8                              |

| HSTL-18 Class<br>II | _     | V <sub>REF</sub> - 0.1  | $V_{REF} + 0.1$         | _                        | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 0.4                    | V <sub>CCIO</sub> – 0.4 | 16                              | -16                             |

| HSTL-15 Class<br>I  | _     | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | -                        | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 0.4                    | V <sub>CCIO</sub> – 0.4 | 8                               | -8                              |

| HSTL-15 Class<br>II | _     | V <sub>REF</sub> - 0.1  | V <sub>REF</sub> + 0.1  | _                        | V <sub>REF</sub> - 0.2   | V <sub>REF</sub> + 0.2   | 0.4                    | V <sub>CCIO</sub> – 0.4 | 16                              | -16                             |

| HSTL-12 Class<br>I  | -0.15 | V <sub>REF</sub> - 0.08 | V <sub>REF</sub> + 0.08 | V <sub>CCIO</sub> + 0.15 | V <sub>REF</sub> - 0.15  | V <sub>REF</sub> + 0.15  | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$  | 8                               | -8                              |

| HSTL-12 Class<br>II | -0.15 | V <sub>REF</sub> - 0.08 | V <sub>REF</sub> + 0.08 | V <sub>CCIO</sub> + 0.15 | V <sub>REF</sub> - 0.15  | V <sub>REF</sub> + 0.15  | $0.25 \times V_{CCIO}$ | $0.75 \times V_{CCIO}$  | 16                              | -16                             |

| HSUL-12             | _     | V <sub>REF</sub> - 0.13 | V <sub>REF</sub> + 0.13 | _                        | V <sub>REF</sub> – 0.22  | V <sub>REF</sub> + 0.22  | $0.1 \times V_{CCIO}$  | 0.9 × V <sub>CCIO</sub> | -                               | _                               |

<sup>&</sup>lt;sup>(19)</sup> To meet the  $I_{OL}$  and  $I_{OH}$  specifications, you must set the current strength settings accordingly. For example, to meet the SSTL15CI specification (8 mA), you should set the current strength settings to 8 mA. Setting at lower current strength may not meet the  $I_{OL}$  and  $I_{OH}$  specifications in the datasheet.

CV-51002 | 2018.05.07

| Symbol | V <sub>OD</sub> Setting <sup>(48)</sup> | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting <sup>(48)</sup> | V <sub>OD</sub> Value (mV) |

|--------|-----------------------------------------|----------------------------|-----------------------------------------|----------------------------|

|        | 25                                      | 500                        | 53                                      | 1060                       |

|        | 26                                      | 520                        | 54                                      | 1080                       |

|        | 27                                      | 540                        | 55                                      | 1100                       |

|        | 28                                      | 560                        | 56                                      | 1120                       |

|        | 29                                      | 580                        | 57                                      | 1140                       |

|        | 30                                      | 600                        | 58                                      | 1160                       |

|        | 31                                      | 620                        | 59                                      | 1180                       |

|        | 32                                      | 640                        | 60                                      | 1200                       |

|        | 33                                      | 660                        |                                         |                            |

## **Transmitter Pre-Emphasis Levels**

The following table lists the simulation data on the transmitter pre-emphasis levels in dB for the first post tap under the following conditions:

- Low-frequency data pattern—five 1s and five 0s

- Data rate—2.5 Gbps

The levels listed are a representation of possible pre-emphasis levels under the specified conditions only and the preemphasis levels may change with data pattern and data rate.

Cyclone V devices only support 1st post tap pre-emphasis with the following conditions:

- The 1st post tap pre-emphasis settings must satisfy  $|B| + |C| \le 60$  where  $|B| = V_{OD}$  setting with termination value,  $R_{TERM} = 100 \Omega$  and |C| = 1st post tap pre-emphasis setting.

- |B| |C| > 5 for data rates < 5 Gbps and |B| |C| > 8.25 for data rates > 5 Gbps.

- $(V_{MAX}/V_{MIN} 1)\% < 600\%$ , where  $V_{MAX} = |B| + |C|$  and  $V_{MIN} = |B| |C|$ .

<sup>&</sup>lt;sup>(48)</sup> Convert these values to their binary equivalent form if you are using the dynamic reconfiguration mode for PMA analog controls.

| Symbol                   | Parameter                                                                                                       | Condition                     | Min | Тур | Max                 | Unit      |

|--------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------|-----|-----|---------------------|-----------|

|                          |                                                                                                                 | -C8, -A7 speed grades         | 600 | -   | 1300                | MHz       |

| teinduty                 | Input clock or external feedback clock input duty cycle                                                         | _                             | 40  | -   | 60                  | %         |

| f <sub>OUT</sub>         | Output frequency for internal global or regional clock                                                          | –C6, –C7, –I7 speed<br>grades | _   | -   | 550 <sup>(54)</sup> | MHz       |

|                          |                                                                                                                 | -C8, -A7 speed grades         | -   | _   | 460 <sup>(54)</sup> | MHz       |

| f <sub>OUT_EXT</sub>     | Output frequency for external clock output                                                                      | -C6, -C7, -I7 speed<br>grades | _   | -   | 667 <sup>(54)</sup> | MHz       |

|                          |                                                                                                                 | -C8, -A7 speed grades         | _   | -   | 533 <sup>(54)</sup> | MHz       |

| t <sub>outduty</sub>     | Duty cycle for external clock output (when set to 50%)                                                          | _                             | 45  | 50  | 55                  | %         |

| t <sub>FCOMP</sub>       | External feedback clock compensation time                                                                       | _                             | _   | -   | 10                  | ns        |

| t <sub>DYCONFIGCLK</sub> | Dynamic configuration clock for mgmt_clk and scanclk                                                            | _                             | _   | -   | 100                 | MHz       |

| t <sub>LOCK</sub>        | Time required to lock from end-of-device configuration or deassertion of areset                                 | _                             | _   | -   | 1                   | ms        |

| t <sub>DLOCK</sub>       | Time required to lock dynamically (after<br>switchover or reconfiguring any non-post-<br>scale counters/delays) | -                             | _   | -   | 1                   | ms        |

| f <sub>CLBW</sub>        | PLL closed-loop bandwidth                                                                                       | Low                           | -   | 0.3 | _                   | MHz       |

|                          |                                                                                                                 | Medium                        | _   | 1.5 | -                   | MHz       |

|                          |                                                                                                                 | High <sup>(55)</sup>          | -   | 4   | -                   | MHz       |

| t <sub>PLL_PSERR</sub>   | Accuracy of PLL phase shift                                                                                     | _                             | _   | _   | ±50                 | ps        |

|                          |                                                                                                                 |                               |     | 1   |                     | continued |

<sup>&</sup>lt;sup>(53)</sup> The VCO frequency reported by the Intel Quartus Prime software takes into consideration the VCO post-scale counter  $\kappa$  value. Therefore, if the counter  $\kappa$  has a value of 2, the frequency reported can be lower than the f<sub>VCO</sub> specification.

$<sup>^{(54)}</sup>$  This specification is limited by the lower of the two: I/O  $f_{MAX}$  or  $F_{OUT}$  of the PLL.

<sup>&</sup>lt;sup>(55)</sup> High bandwidth PLL settings are not supported in external feedback mode.

## **DSP Block Performance Specifications**

## Table 32. DSP Block Performance Specifications for Cyclone V Devices

|                            | Mode                                                     |     |          | Unit     |     |

|----------------------------|----------------------------------------------------------|-----|----------|----------|-----|

|                            |                                                          | -C6 | -C7, -I7 | -C8, -A7 |     |

| Modes using One DSP Block  | Independent 9 $\times$ 9 multiplication                  | 340 | 300      | 260      | MHz |

|                            | Independent 18 × 19 multiplication                       | 287 | 250      | 200      | MHz |

|                            | Independent 18 × 18 multiplication                       | 287 | 250      | 200      | MHz |

|                            | Independent 27 × 27 multiplication                       | 250 | 200      | 160      | MHz |

|                            | Independent 18 × 25 multiplication                       | 310 | 250      | 200      | MHz |

|                            | Independent 20 × 24 multiplication                       | 310 | 250      | 200      | MHz |

|                            | Two 18 $\times$ 19 multiplier adder mode                 | 310 | 250      | 200      | MHz |

|                            | $18 \times 18$ multiplier added summed with 36-bit input | 310 | 250      | 200      | MHz |

| Modes using Two DSP Blocks | Complex 18 × 19 multiplication                           | 310 | 250      | 200      | MHz |

## **Memory Block Performance Specifications**

To achieve the maximum memory block performance, use a memory block clock that comes through global clock routing from an on-chip PLL and set to 50% output duty cycle. Use the Intel Quartus Prime software to report timing for the memory block clocking schemes.

When you use the error detection cyclical redundancy check (CRC) feature, there is no degradation in f<sub>MAX</sub>.

### Table 33. Memory Block Performance Specifications for Cyclone V Devices

| Memory | Mode                                                     | Resources Used |        |     | Unit     |          |           |

|--------|----------------------------------------------------------|----------------|--------|-----|----------|----------|-----------|

|        |                                                          | ALUTs          | Memory | -C6 | -C7, -I7 | -C8, -A7 |           |

| MLAB   | Single port, all supported widths                        | 0              | 1      | 420 | 350      | 300      | MHz       |

|        | Simple dual-port, all supported widths                   | 0              | 1      | 420 | 350      | 300      | MHz       |

|        | Simple dual-port with read and write at the same address | 0              | 1      | 340 | 290      | 240      | MHz       |

|        |                                                          |                |        | •   |          |          | continued |

CV-51002 | 2018.05.07

| Memory     | Mode                                                                                                    | Resources Used |        | Performance |          |          | Unit |

|------------|---------------------------------------------------------------------------------------------------------|----------------|--------|-------------|----------|----------|------|

|            |                                                                                                         | ALUTs          | Memory | -C6         | -C7, -I7 | -C8, -A7 |      |

|            | ROM, all supported width                                                                                | 0              | 1      | 420         | 350      | 300      | MHz  |

| M10K Block | Single-port, all supported widths                                                                       | 0              | 1      | 315         | 275      | 240      | MHz  |

|            | Simple dual-port, all supported widths                                                                  | 0              | 1      | 315         | 275      | 240      | MHz  |

|            | Simple dual-port with the <b>read-during-write</b> option set to <b>Old Data</b> , all supported widths | 0              | 1      | 275         | 240      | 180      | MHz  |

|            | True dual port, all supported widths                                                                    | 0              | 1      | 315         | 275      | 240      | MHz  |

|            | ROM, all supported widths                                                                               | 0              | 1      | 315         | 275      | 240      | MHz  |

## **Periphery Performance**

This section describes the periphery performance, high-speed I/O, and external memory interface.

Actual achievable frequency depends on design and system specific factors. Ensure proper timing closure in your design and perform HSPICE/IBIS simulations based on your specific design and system setup to determine the maximum achievable frequency in your system.

## **DLL Frequency Range Specifications**

### Table 35. DLL Frequency Range Specifications for Cyclone V Devices

| Parameter                     | -C6       | -C7, -I7  | -C8       | Unit |

|-------------------------------|-----------|-----------|-----------|------|

| DLL operating frequency range | 167 - 400 | 167 - 400 | 167 - 333 | MHz  |

## **DQS Logic Block Specifications**

#### Table 36. DQS Phase Shift Error Specification for DLL-Delayed Clock (t<sub>DOS PSERR</sub>) for Cyclone V Devices

This error specification is the absolute maximum and minimum error.

| Number of DQS Delay Buffer | -C6 | -C7, -I7 | -C8 | Unit |

|----------------------------|-----|----------|-----|------|

| 2                          | 40  | 80       | 80  | ps   |

## Memory Output Clock Jitter Specifications

#### Table 37. Memory Output Clock Jitter Specifications for Cyclone V Devices

The memory output clock jitter measurements are for 200 consecutive clock cycles, as specified in the JEDEC DDR2/DDR3 SDRAM standard.

The memory output clock jitter is applicable when an input jitter of 30 ps (p-p) is applied with bit error rate (BER) 10<sup>-12</sup>, equivalent to 14 sigma.

Intel recommends using the UniPHY intellectual property (IP) with PHYCLK connections for better jitter performance.

| Parameter                    | Clock Network | Symbol                | -C6 |     | -C7, -I7 |     | -C8 |     | Unit |

|------------------------------|---------------|-----------------------|-----|-----|----------|-----|-----|-----|------|

|                              |               |                       | Min | Max | Min      | Max | Min | Max |      |

| Clock period jitter          | PHYCLK        | t <sub>JIT(per)</sub> | -60 | 60  | -70      | 70  | -70 | 70  | ps   |

| Cycle-to-cycle period jitter | PHYCLK        | t <sub>JIT(cc)</sub>  | _   | 90  | _        | 100 | _   | 100 | ps   |

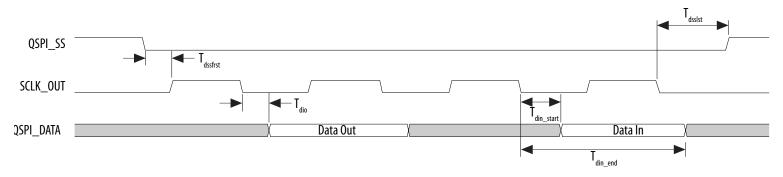

## **Quad SPI Flash Timing Characteristics**

## Table 43. Quad Serial Peripheral Interface (SPI) Flash Timing Requirements for Cyclone V Devices

| Symbol                 | Description                                        | Min                                               | Тур                      | Мах                                                                         | Unit |

|------------------------|----------------------------------------------------|---------------------------------------------------|--------------------------|-----------------------------------------------------------------------------|------|

| F <sub>clk</sub>       | SCLK_OUT clock frequency (External clock)          | -                                                 | _                        | 108                                                                         | MHz  |

| T <sub>qspi_clk</sub>  | QSPI_CLK clock period (Internal reference clock)   | 2.32                                              | -                        | —                                                                           | ns   |

| T <sub>dutycycle</sub> | SCLK_OUT duty cycle                                | 45                                                | _                        | 55                                                                          | %    |

| T <sub>dssfrst</sub>   | Output delay QSPI_SS valid before first clock edge | -                                                 | 1/2 cycle of<br>SCLK_OUT | _                                                                           | ns   |

| T <sub>dsslst</sub>    | Output delay QSPI_SS valid after last clock edge   | -1                                                | _                        | 1                                                                           | ns   |

| T <sub>dio</sub>       | I/O data output delay                              | -1                                                | -                        | 1                                                                           | ns   |

| T <sub>din_start</sub> | Input data valid start                             | -                                                 | _                        | (2 + R <sub>delay</sub> ) ×<br>T <sub>qspi_clk</sub> - 7.52 <sup>(68)</sup> | ns   |

| T <sub>din_end</sub>   | Input data valid end                               | $(2 + R_{delay}) \times T_{qspi_clk} - 1.21$ (68) | _                        | _                                                                           | ns   |

## Figure 6. Quad SPI Flash Timing Diagram

This timing diagram illustrates clock polarity mode 0 and clock phase mode 0.

<sup>(68)</sup> R<sub>delay</sub> is set by programming the register gspiregs.rddatacap. For the SoC EDS software version 13.1 and later, Intel provides automatic Quad SPI calibration in the preloader. For more information about R<sub>delay</sub>, refer to the Quad SPI Flash Controller chapter in the Cyclone V Hard Processor System Technical Reference Manual.

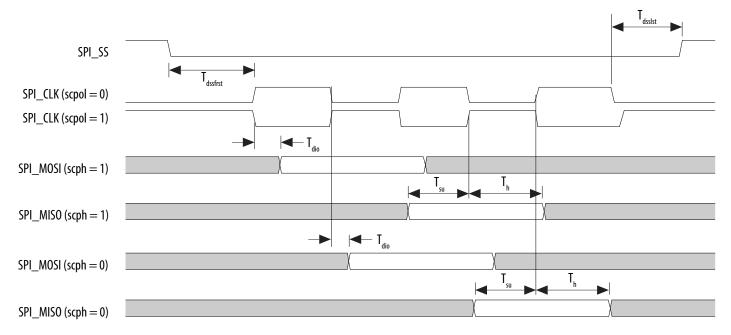

## Figure 7. SPI Master Timing Diagram

#### Table 45. SPI Slave Timing Requirements for Cyclone V Devices

The setup and hold times can be used for Texas Instruments SSP mode and National Semiconductor Microwire mode.

| Symbol            | Description                                        | Min    | Мах | Unit |

|-------------------|----------------------------------------------------|--------|-----|------|

| T <sub>clk</sub>  | CLK clock period                                   | 20     | —   | ns   |

| T <sub>s</sub>    | MOSI Setup time                                    | 5      | _   | ns   |

| T <sub>h</sub>    | MOSI Hold time                                     | 5      | _   | ns   |

| T <sub>suss</sub> | Setup time SPI_SS valid before first clock edge    | 8      | —   | ns   |

| T <sub>hss</sub>  | Hold time SPI_SS valid after last clock edge     8 |        | _   | ns   |

| T <sub>d</sub>    | MISO output delay                                  | — 6 ns |     | ns   |

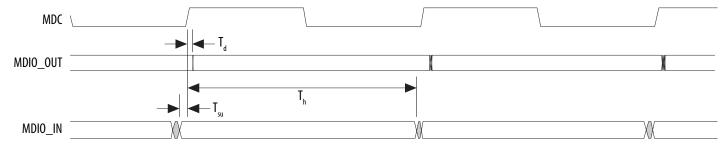

## Figure 13. MDIO Timing Diagram

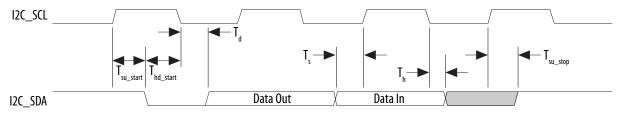

## I<sup>2</sup>C Timing Characteristics

| Table 51. I | <sup>2</sup> C Timing | <b>Requirements for</b> | Cyclone V Devices |

|-------------|-----------------------|-------------------------|-------------------|

|-------------|-----------------------|-------------------------|-------------------|

| Symbol                | Description                                       | Description Standar |      | Fast | Fast Mode |    |

|-----------------------|---------------------------------------------------|---------------------|------|------|-----------|----|

|                       |                                                   | Min                 | Мах  | Min  | Max       |    |

| T <sub>clk</sub>      | Serial clock (SCL) clock period                   | 10                  | _    | 2.5  | -         | μs |

| T <sub>clkhigh</sub>  | SCL high time                                     | 4.7                 | _    | 0.6  | -         | μs |

| T <sub>clklow</sub>   | SCL low time                                      | 4                   | _    | 1.3  | -         | μs |

| Ts                    | Setup time for serial data line (SDA) data to SCL | 0.25                | _    | 0.1  | -         | μs |

| T <sub>h</sub>        | Hold time for SCL to SDA data                     | 0                   | 3.45 | 0    | 0.9       | μs |

| T <sub>d</sub>        | SCL to SDA output data delay                      | _                   | 0.2  | -    | 0.2       | μs |

| T <sub>su_start</sub> | Setup time for a repeated start condition         | 4.7                 | _    | 0.6  | -         | μs |

| T <sub>hd_start</sub> | Hold time for a repeated start condition          | 4                   | _    | 0.6  | -         | μs |

| T <sub>su_stop</sub>  | Setup time for a stop condition                   | 4                   | _    | 0.6  | -         | μs |

## Figure 14. I<sup>2</sup>C Timing Diagram

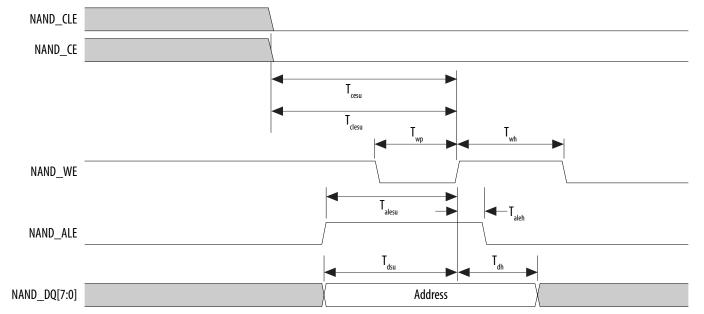

## **NAND Timing Characteristics**

### Table 52. NAND ONFI 1.0 Timing Requirements for Cyclone V Devices

The NAND controller supports Open NAND FLASH Interface (ONFI) 1.0 Mode 5 timing as well as legacy NAND devices. This table lists the requirements for ONFI 1.0 mode 5 timing. The HPS NAND controller can meet this timing by programming the C4 output of the main HPS PLL and timing registers provided in the NAND controller.

| Symbol                             | Description                                     | Min | Мах | Unit      |

|------------------------------------|-------------------------------------------------|-----|-----|-----------|

| T <sub>wp</sub> <sup>(72)</sup>    | Write enable pulse width                        | 10  | -   | ns        |

| T <sub>wh</sub> <sup>(72)</sup>    | Write enable hold time                          | 7   | -   | ns        |

| T <sub>rp</sub> <sup>(72)</sup>    | Read enable pulse width                         | 10  | -   | ns        |

| T <sub>reh</sub> (72)              | Read enable hold time                           | 7   | -   | ns        |

| T <sub>clesu</sub> <sup>(72)</sup> | Command latch enable to write enable setup time | 10  | -   | ns        |

| T <sub>cleh</sub> <sup>(72)</sup>  | Command latch enable to write enable hold time  | 5   | -   | ns        |

| T <sub>cesu</sub> (72)             | Chip enable to write enable setup time          | 15  | -   | ns        |

| T <sub>ceh</sub> <sup>(72)</sup>   | Chip enable to write enable hold time           | 5   | _   | ns        |

| T <sub>alesu</sub> <sup>(72)</sup> | Address latch enable to write enable setup time | 10  | -   | ns        |

| T <sub>aleh</sub> <sup>(72)</sup>  | Address latch enable to write enable hold time  | 5   | -   | ns        |

| T <sub>dsu</sub> <sup>(72)</sup>   | Data to write enable setup time                 | 10  | _   | ns        |

| T <sub>dh</sub> (72)               | Data to write enable hold time                  | 5   | -   | ns        |

|                                    | •                                               |     |     | continued |

<sup>(72)</sup> Timing of the NAND interface is controlled through the NAND configuration registers.

## Figure 16. NAND Address Latch Timing Diagram

## **Related Information**

Configuration Files on page 76

## **Remote System Upgrades**

#### Table 66. Remote System Upgrade Circuitry Timing Specifications for Cyclone V Devices

| Parameter                                | Minimum | Unit |

|------------------------------------------|---------|------|

| t <sub>RU_nCONFIG</sub> <sup>(98)</sup>  | 250     | ns   |

| t <sub>RU_nRSTIMER</sub> <sup>(99)</sup> | 250     | ns   |

#### **Related Information**

- Remote System Upgrade State Machine Provides more information about configuration reset (RU\_CONFIG) signal.

- User Watchdog Timer Provides more information about reset\_timer (RU\_nRSTIMER) signal.

## **User Watchdog Internal Oscillator Frequency Specifications**

## Table 67. User Watchdog Internal Oscillator Frequency Specifications for Cyclone V Devices

| Parameter                                   | Minimum | Typical | Maximum | Unit |

|---------------------------------------------|---------|---------|---------|------|

| User watchdog internal oscillator frequency | 5.3     | 7.9     | 12.5    | MHz  |

## **I/O Timing**

Intel offers two ways to determine I/O timing—the Excel-based I/O timing and the Intel Quartus Prime Timing Analyzer.

<sup>&</sup>lt;sup>(98)</sup> This is equivalent to strobing the reconfiguration input of the Remote Update Intel FPGA IP core high for the minimum timing specification.

<sup>&</sup>lt;sup>(99)</sup> This is equivalent to strobing the reset timer input of the Remote Update Intel FPGA IP core high for the minimum timing specification.

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| July 2014     | 3.9     | <ul> <li>Added a note in Table 3, Table 4, and Table 5: The power supply value describes the budget for the DC (static) power<br/>supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget<br/>for the dynamic tolerance requirements.</li> </ul>                                                                                 |

|               |         | • Added a note in Table 19: Differential inputs are powered by $V_{CCPD}$ which requires 2.5 V.                                                                                                                                                                                                                                                                                                    |

|               |         | • Updated "Minimum differential eye opening at the receiver serial input pins" specification in Table 20.                                                                                                                                                                                                                                                                                          |

|               |         | • Updated h2f_user2_clk specification for -C6, -C7, and -I7 speed grades in Table 34.                                                                                                                                                                                                                                                                                                              |

|               |         | Updated description in "HPS PLL Specifications" section.                                                                                                                                                                                                                                                                                                                                           |

|               |         | Updated VCO range maximum specification in Table 35.                                                                                                                                                                                                                                                                                                                                               |

|               |         | • Updated $T_d$ and $T_h$ specifications in Table 41.                                                                                                                                                                                                                                                                                                                                              |

|               |         | Added T <sub>h</sub> specification in Table 43 and Figure 10.                                                                                                                                                                                                                                                                                                                                      |

|               |         | • Updated a note in Figure 17, Figure 18, and Figure 20 as follows: Do not leave DCLK floating after configuration. DCLK is ignored after configuration is complete. It can toggle high or low if required.                                                                                                                                                                                        |

|               |         | Removed "Remote update only in AS mode" specification in Table 54.                                                                                                                                                                                                                                                                                                                                 |

|               |         | Added DCLK device initialization clock source specification in Table 56.                                                                                                                                                                                                                                                                                                                           |

|               |         | • Added description in "Configuration Files" section: The IOCSR .rbf size is specifically for the Configuration via Protocol (CvP) feature.                                                                                                                                                                                                                                                        |

|               |         | Added "Recommended EPCQ Serial Configuration Device" values in Table 57.                                                                                                                                                                                                                                                                                                                           |

|               |         | Removed f <sub>MAX_RU_CLK</sub> specification in Table 59.                                                                                                                                                                                                                                                                                                                                         |

| February 2014 | 3.8     | Updated V <sub>CCRSTCLK_HPS</sub> maximum specification in Table 1.                                                                                                                                                                                                                                                                                                                                |

|               |         | Added V <sub>CC_AUX_SHARED</sub> specification in Table 1.                                                                                                                                                                                                                                                                                                                                         |

| December 2013 | 3.7     | Updated Table 1, Table 3, Table 19, Table 20, Table 23, Table 25, Table 27, Table 34, Table 44, Table 51, Table 52, Table 55, and Table 61.                                                                                                                                                                                                                                                        |

|               |         | • Removed Preliminary tags for Table 1, Table 2, Table 3, Table 4, Table 5, Table 6, Table 7, Table 9, Table 12, Table 13, Table 14, Table 15, Table 16, Table 17, Table 18, Table 19, Table 20, Table 24, Table 25, Table 26, Table 27, Table 28, Table 32, Table 33, Table 49, Table 50, Table 51, Table 52, Table 53, Table 54, Table 55, Table 57, Table 58, Table 59, Table 60, and Table 62. |

| November 2013 | 3.6     | Updated Table 23, Table 30, and Table 31.                                                                                                                                                                                                                                                                                                                                                          |

| October 2013  | 3.5     | Added "HPS PLL Specifications".                                                                                                                                                                                                                                                                                                                                                                    |

|               |         | Added Table 23, Table 35, and Table 36.                                                                                                                                                                                                                                                                                                                                                            |

|               |         | • Updated Table 1, Table 5, Table 11, Table 19, Table 20, Table 21, Table 22, Table 25, Table 28, Table 34, Table 37, Table 38, Table 39, Table 40, Table 41, Table 42, Table 43, Table 44, Table 45, Table 46, Table 47, and Table 53.                                                                                                                                                            |

|               |         | • Updated Figure 1, Figure 2, Figure 4, Figure 10, Figure 12, Figure 13, and Figure 16.                                                                                                                                                                                                                                                                                                            |

|               |         | Removed table: GPIO Pulse Width for Cyclone V Devices.                                                                                                                                                                                                                                                                                                                                             |

|               |         | continued                                                                                                                                                                                                                                                                                                                                                                                          |

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2013     | 3.4     | <ul> <li>Updated Table 20, Table 27, and Table 34.</li> <li>Updated "UART Interface" and "CAN Interface" sections.</li> <li>Removed the following tables: <ul> <li>Table 45: UART Baud Rate for Cyclone V Devices</li> <li>Table 47: CAN Pulse Width for Cyclone V Devices</li> </ul> </li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                         |

| May 2013      | 3.3     | <ul> <li>Added Table 33.</li> <li>Updated Figure 5, Figure 6, Figure 17, Figure 19, and Figure 20.</li> <li>Updated Table 1, Table 4, Table 5, Table 10, Table 13, Table 19, Table 20, Table 26, Table 32, Table 35, Table 36, Table 43, Table 53, Table 54, Table 57, and Table 61.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                           |

| March 2013    | 3.2     | <ul> <li>Added HPS reset information in the "HPS Specifications" section.</li> <li>Added Table 57.</li> <li>Updated Table 1, Table 2, Table 17, Table 20, Table 52, and Table 56.</li> <li>Updated Figure 18.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| January 2013  | 3.1     | Updated Table 4, Table 20, and Table 56.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| November 2012 | 3.0     | <ul> <li>Updated Table 1, Table 4, Table 5, Table 9, Table 14, Table 16, Table 17, Table 19, Table 20, Table 25, Table 28, Table 52, Table 55, Table 56, and Table 59.</li> <li>Removed table: Transceiver Block Jitter Specifications for Cyclone V GX Devices.</li> <li>Added HPS information: <ul> <li>Added "HPS Specifications" section.</li> <li>Added Table 33, Table 34, Table 35, Table 36, Table 37, Table 38, Table 39, Table 40, Table 41, Table 42, Table 43, Table 44, Table 45, and Table 46.</li> <li>Added Figure 4, Figure 5, Figure 6, Figure 7, Figure 8, Figure 9, Figure 10, Figure 11, Figure 12, Figure 13, Figure 14, Figure 15, and Figure 16.</li> <li>Updated Table 3.</li> </ul> </li> </ul> |

| June 2012     | 2.0     | <ul> <li>Updated for the Quartus Prime software v12.0 release:</li> <li>Restructured document.</li> <li>Removed "Power Consumption" section.</li> <li>Updated Table 1,Table 3, Table 19, Table 20, Table 25, Table 27, Table 28, Table 30, Table 31, Table 34, Table 36, Table 37, Table 38, Table 39, Table 41, Table 43, and Table 46.</li> <li>Added Table 22, Table 23, and Table 29.</li> <li>Added Figure 1 and Figure 2.</li> <li>Added "Initialization" and "Configuration Files" sections.</li> </ul>                                                                                                                                                                                                            |

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                               |

|---------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 2012 | 1.2     | <ul> <li>Added automotive speed grade information.</li> <li>Added Figure 2–1.</li> <li>Updated Table 2–3, Table 2–8, Table 2–9, Table 2–19, Table 2–20, Table 2–21, Table 2–22, Table 2–23, Table 2–24, Table 2–25, Table 2–26, Table 2–27, Table 2–28, Table 2–30, Table 2–35, and Table 2–43.</li> <li>Minor text edits.</li> </ul> |

| November 2011 | 1.1     | <ul> <li>Added Table 2–5.</li> <li>Updated Table 2–3, Table 2–4, Table 2–11, Table 2–13, Table 2–20, and Table 2–21.</li> </ul>                                                                                                                                                                                                       |

| October 2011  | 1.0     | Initial release.                                                                                                                                                                                                                                                                                                                      |