Welcome to **E-XFL.COM**

# **Embedded - System On Chip (SoC):** The Heart of Modern Embedded Systems

Embedded - System On Chip (SoC) refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

### What are **Embedded - System On Chip (SoC)**?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

| Details                 |                                                                                    |

|-------------------------|------------------------------------------------------------------------------------|

| Product Status          | Active                                                                             |

| Architecture            | MCU, FPGA                                                                          |

| Core Processor          | Dual ARM® Cortex®-A9 MPCore™ with CoreSight™                                       |

| Flash Size              | -                                                                                  |

| RAM Size                | 64KB                                                                               |

| Peripherals             | DMA, POR, WDT                                                                      |

| Connectivity            | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Speed                   | 800MHz                                                                             |

| Primary Attributes      | FPGA - 85K Logic Elements                                                          |

| Operating Temperature   | -40°C ~ 100°C (TJ)                                                                 |

| Package / Case          | 484-FBGA                                                                           |

| Supplier Device Package | 484-UBGA (19x19)                                                                   |

| Purchase URL            | https://www.e-xfl.com/product-detail/intel/5cseba5u19i7n                           |

|                         |                                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

This datasheet describes the electrical characteristics, switching characteristics, configuration specifications, and I/O timing for Cyclone® V devices.

Cyclone V devices are offered in commercial and industrial grades. Commercial devices are offered in -C6 (fastest), -C7, and -C8 speed grades. Industrial grade devices are offered in the -I7 speed grade. Automotive devices are offered in the -A7 speed grade.

Cyclone V SoC devices are also offered in a low-power variant, as indicated by the L power option in the device part number. These devices have 30% static power reduction for devices with 25K LE and 40K LE, and 20% static power reduction for devices with 85K LE and 110K LE. Note that the L power option devices are only available in –I7 speed grade, and have the equivalent operating conditions and timing specifications as the standard –I7 speed grade devices.

**Table 1.** Low Power Variants

| Density | Ordering Part Number (OPN) | Static Power Reduction |

|---------|----------------------------|------------------------|

| 25K LE  | 5CSEBA2U19I7LN             | 30%                    |

|         | 5CSEBA2U23I7LN             |                        |

|         | 5CSXFC2C6U23I7LN           |                        |

| 40K LE  | 5CSEBA4U19I7LN             |                        |

|         | 5CSEBA4U23I7LN             |                        |

|         | 5CSXFC4C6U23I7LN           |                        |

| 85K LE  | 5CSEBA5U19I7LN             | 20%                    |

|         | 5CSEBA5U23I7LN             |                        |

|         | 5CSXC5C6U23I7LN            |                        |

|         |                            | continued              |

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2008 Registered

### **Recommended Operating Conditions**

#### Table 4. Recommended Operating Conditions for Cyclone V Devices

This table lists the steady-state voltage values expected from Cyclone V devices. Power supply ramps must all be strictly monotonic, without plateaus.

| Symbol                           | Description                                                                                | Condition                                                    | Minimum <sup>(2)</sup> | Typical | Maximum <sup>(2)</sup> | Unit      |

|----------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------|---------|------------------------|-----------|

| V <sub>CC</sub>                  | Core voltage, periphery circuitry power supply, transceiver physical coding sublayer (PCS) | Devices without internal scrubbing feature                   | 1.07                   | 1.1     | 1.13                   | V         |

|                                  | power supply, and transceiver PCI Express* (PCIe*) hard IP digital power supply            | Devices with internal scrubbing feature (with SC suffix) (3) | 1.12                   | 1.15    | 1.18                   | V         |

| V <sub>CC_AUX</sub>              | Auxiliary supply                                                                           | _                                                            | 2.375                  | 2.5     | 2.625                  | V         |

| V <sub>CCPD</sub> <sup>(4)</sup> | I/O pre-driver power supply                                                                | 3.3 V                                                        | 3.135                  | 3.3     | 3.465                  | V         |

|                                  |                                                                                            | 3.0 V                                                        | 2.85                   | 3.0     | 3.15                   | V         |

|                                  |                                                                                            | 2.5 V                                                        | 2.375                  | 2.5     | 2.625                  | V         |

| V <sub>CCIO</sub>                | I/O buffers power supply                                                                   | 3.3 V                                                        | 3.135                  | 3.3     | 3.465                  | V         |

|                                  |                                                                                            | 3.0 V                                                        | 2.85                   | 3.0     | 3.15                   | V         |

|                                  |                                                                                            | 2.5 V                                                        | 2.375                  | 2.5     | 2.625                  | V         |

|                                  |                                                                                            | 1.8 V                                                        | 1.71                   | 1.8     | 1.89                   | V         |

|                                  |                                                                                            | 1.5 V                                                        | 1.425                  | 1.5     | 1.575                  | V         |

|                                  |                                                                                            | 1.35 V                                                       | 1.283                  | 1.35    | 1.418                  | V         |

|                                  |                                                                                            | 1.25 V                                                       | 1.19                   | 1.25    | 1.31                   | V         |

|                                  |                                                                                            | 1.2 V                                                        | 1.14                   | 1.2     | 1.26                   | V         |

|                                  |                                                                                            |                                                              |                        |         |                        | continued |

<sup>(2)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(3)</sup> The SEU internal scrubbing feature is available for Cyclone V E, GX, SE, and SX devices with the "SC" suffix in the part number. For device availability and ordering, contact your local Intel sales representatives.

$<sup>^{(4)}</sup>$  V<sub>CCPD</sub> must be 2.5 V when V<sub>CCIO</sub> is 2.5, 1.8, 1.5, 1.35, 1.25, or 1.2 V. V<sub>CCPD</sub> must be 3.0 V when V<sub>CCIO</sub> is 3.0 V. V<sub>CCPD</sub> must be 3.3 V when V<sub>CCIO</sub> is 3.3 V.

#### CV-51002 | 2018.05.07

| Symbol                               | Description                                                                 | Condition    | Minimum <sup>(2)</sup> | Typical | Maximum <sup>(2)</sup> | Unit |

|--------------------------------------|-----------------------------------------------------------------------------|--------------|------------------------|---------|------------------------|------|

| V <sub>CCPGM</sub>                   | Configuration pins power supply                                             | 3.3 V        | 3.135                  | 3.3     | 3.465                  | V    |

|                                      |                                                                             | 3.0 V        | 2.85                   | 3.0     | 3.15                   | V    |

|                                      |                                                                             | 2.5 V        | 2.375                  | 2.5     | 2.625                  | V    |

|                                      |                                                                             | 1.8 V        | 1.71                   | 1.8     | 1.89                   | V    |

| V <sub>CCA_FPLL</sub> <sup>(5)</sup> | PLL analog voltage regulator power supply                                   | _            | 2.375                  | 2.5     | 2.625                  | V    |

| V <sub>CCBAT</sub> <sup>(6)</sup>    | Battery back-up power supply<br>(For design security volatile key register) | _            | 1.2                    | _       | 3.0                    | V    |

| V <sub>I</sub>                       | DC input voltage                                                            | _            | -0.5                   | _       | 3.6                    | V    |

| Vo                                   | Output voltage                                                              | _            | 0                      | _       | V <sub>CCIO</sub>      | V    |

| T <sub>J</sub>                       | Operating junction temperature                                              | Commercial   | 0                      | _       | 85                     | °C   |

|                                      |                                                                             | Industrial   | -40                    | _       | 100                    | °C   |

|                                      |                                                                             | Automotive   | -40                    | _       | 125                    | °C   |

| t <sub>RAMP</sub> <sup>(7)</sup>     | Power supply ramp time                                                      | Standard POR | 200µs                  | _       | 100ms                  | _    |

|                                      |                                                                             | Fast POR     | 200µs                  | _       | 4ms                    | _    |

<sup>(2)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

$<sup>^{(5)}</sup>$  PLL digital voltage is regulated from  $V_{CCA\ FPLL}$ .

<sup>(6)</sup> If you do not use the design security feature in Cyclone V devices, connect  $V_{CCBAT}$  to a 1.5-V, 2.5-V, or 3.0-V power supply. Cyclone V power-on reset (POR) circuitry monitors  $V_{CCBAT}$ . Cyclone V devices do not exit POR if  $V_{CCBAT}$  is not powered up.

<sup>(7)</sup> This is also applicable to HPS power supply. For HPS power supply, refer to  $t_{RAMP}$  specifications for standard POR when HPS\_PORSEL = 0 and  $t_{RAMP}$  specifications for fast POR when HPS PORSEL = 1.

### Table 9. OCT Calibration Accuracy Specifications for Cyclone V Devices

Calibration accuracy for the calibrated on-chip series termination ( $R_S$  OCT) and on-chip parallel termination ( $R_T$  OCT) are applicable at the moment of calibration. When process, voltage, and temperature (PVT) conditions change after calibration, the tolerance may change.

| Symbol                                        | Description                                                                                                                            | Condition (V)                               | Ca         | alibration Accura | cy         | Unit |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|------------|-------------------|------------|------|

|                                               |                                                                                                                                        |                                             | -C6        | -I7, -C7          | -C8, -A7   |      |

| 25-Ω R <sub>S</sub>                           | Internal series termination with calibration (25- $\Omega$ setting)                                                                    | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 | ±15        | ±15               | ±15        | %    |

| 50-Ω R <sub>S</sub>                           | Internal series termination with calibration (50- $\Omega$ setting)                                                                    | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 | ±15        | ±15               | ±15        | %    |

| 34- $\Omega$ and 40- $\Omega$ R <sub>S</sub>  | Internal series termination with calibration (34- $\Omega$ and 40- $\Omega$ setting)                                                   | V <sub>CCIO</sub> = 1.5, 1.35, 1.25, 1.2    | ±15        | ±15               | ±15        | %    |

| 48-Ω, 60-Ω, and 80-Ω $R_S$                    | Internal series termination with calibration (48- $\Omega$ , 60- $\Omega$ , and 80- $\Omega$ setting)                                  | V <sub>CCIO</sub> = 1.2                     | ±15        | ±15               | ±15        | %    |

| 50-Ω R <sub>T</sub>                           | Internal parallel termination with calibration (50- $\Omega$ setting)                                                                  | V <sub>CCIO</sub> = 2.5, 1.8, 1.5, 1.2      | -10 to +40 | -10 to +40        | -10 to +40 | %    |

| 20-Ω, 30-Ω, 40-Ω,60-Ω, and 120-Ω $R_T$        | Internal parallel termination with calibration (20- $\Omega$ , 30- $\Omega$ , 40- $\Omega$ , 60- $\Omega$ , and 120- $\Omega$ setting) | V <sub>CCIO</sub> = 1.5, 1.35, 1.25         | -10 to +40 | -10 to +40        | -10 to +40 | %    |

| 60- $\Omega$ and 120- $\Omega$ R <sub>T</sub> | Internal parallel termination with calibration (60- $\Omega$ and 120- $\Omega$ setting)                                                | V <sub>CCIO</sub> = 1.2                     | -10 to +40 | -10 to +40        | -10 to +40 | %    |

| 25-Ω R <sub>S_left_shift</sub>                | Internal left shift series termination with calibration (25- $\Omega$ R <sub>S_left_shift</sub> setting)                               | V <sub>CCIO</sub> = 3.0, 2.5, 1.8, 1.5, 1.2 | ±15        | ±15               | ±15        | %    |

Table 14. Internal Weak Pull-Up Resistor Values for Cyclone V Devices

| Symbol          | Description                                                                    | Condition (V) <sup>(16)</sup> | Value <sup>(17)</sup> | Unit |

|-----------------|--------------------------------------------------------------------------------|-------------------------------|-----------------------|------|

| R <sub>PU</sub> | Value of the I/O pin pull-up resistor before and during configuration, as well | V <sub>CCIO</sub> = 3.3 ±5%   | 25                    | kΩ   |

|                 | as user mode if you have enabled the programmable pull-up resistor option.     | V <sub>CCIO</sub> = 3.0 ±5%   | 25                    | kΩ   |

|                 |                                                                                | V <sub>CCIO</sub> = 2.5 ±5%   | 25                    | kΩ   |

|                 |                                                                                | V <sub>CCIO</sub> = 1.8 ±5%   | 25                    | kΩ   |

|                 |                                                                                | V <sub>CCIO</sub> = 1.5 ±5%   | 25                    | kΩ   |

|                 |                                                                                | V <sub>CCIO</sub> = 1.35 ±5%  | 25                    | kΩ   |

|                 |                                                                                | V <sub>CCIO</sub> = 1.25 ±5%  | 25                    | kΩ   |

|                 |                                                                                | V <sub>CCIO</sub> = 1.2 ±5%   | 25                    | kΩ   |

#### **Related Information**

Cyclone V Device Family Pin Connection Guidelines

Provides more information about the pins that support internal weak pull-up and internal weak pull-down features.

### I/O Standard Specifications

Tables in this section list the input voltage ( $V_{IH}$  and  $V_{IL}$ ), output voltage ( $V_{OH}$  and  $V_{OL}$ ), and current drive characteristics ( $I_{OH}$  and  $I_{OL}$ ) for various I/O standards supported by Cyclone V devices.

You must perform timing closure analysis to determine the maximum achievable frequency for general purpose I/O standards.

$<sup>^{(16)}</sup>$  Pin pull-up resistance values may be lower if an external source drives the pin higher than  $V_{CCIO}$ .

$<sup>^{(17)}</sup>$  Valid with  $\pm 10\%$  tolerances to cover changes over PVT.

### **Single-Ended I/O Standards**

Table 15. Single-Ended I/O Standards for Cyclone V Devices

| I/O Standard |       | V <sub>CCIO</sub> (V) |       | ١    | / <sub>IL</sub> (V)      | V <sub>IH</sub>          | (V)                     | V <sub>OL</sub> (V)      | V <sub>OH</sub> (V)      | I <sub>OL</sub> (18) | I <sub>OH</sub> <sup>(18)</sup> (mA) |

|--------------|-------|-----------------------|-------|------|--------------------------|--------------------------|-------------------------|--------------------------|--------------------------|----------------------|--------------------------------------|

|              | Min   | Тур                   | Max   | Min  | Max                      | Min                      | Max                     | Max                      | Min                      | (mA)                 | (mA)                                 |

| 3.3-V LVTTL  | 3.135 | 3.3                   | 3.465 | -0.3 | 0.8                      | 1.7                      | 3.6                     | 0.45                     | 2.4                      | 4                    | -4                                   |

| 3.3-V LVCMOS | 3.135 | 3.3                   | 3.465 | -0.3 | 0.8                      | 1.7                      | 3.6                     | 0.2                      | V <sub>CCIO</sub> - 0.2  | 2                    | -2                                   |

| 3.0-V LVTTL  | 2.85  | 3                     | 3.15  | -0.3 | 0.8                      | 1.7                      | 3.6                     | 0.4                      | 2.4                      | 2                    | -2                                   |

| 3.0-V LVCMOS | 2.85  | 3                     | 3.15  | -0.3 | 0.8                      | 1.7                      | 3.6                     | 0.2                      | V <sub>CCIO</sub> - 0.2  | 0.1                  | -0.1                                 |

| 3.0-V PCI*   | 2.85  | 3                     | 3.15  | _    | 0.3 × V <sub>CCIO</sub>  | 0.5 × V <sub>CCIO</sub>  | V <sub>CCIO</sub> + 0.3 | 0.1 × V <sub>CCIO</sub>  | 0.9 × V <sub>CCIO</sub>  | 1.5                  | -0.5                                 |

| 3.0-V PCI-X  | 2.85  | 3                     | 3.15  | _    | 0.35 × V <sub>CCIO</sub> | 0.5 × V <sub>CCIO</sub>  | V <sub>CCIO</sub> + 0.3 | 0.1 × V <sub>CCIO</sub>  | 0.9 × V <sub>CCIO</sub>  | 1.5                  | -0.5                                 |

| 2.5 V        | 2.375 | 2.5                   | 2.625 | -0.3 | 0.7                      | 1.7                      | 3.6                     | 0.4                      | 2                        | 1                    | -1                                   |

| 1.8 V        | 1.71  | 1.8                   | 1.89  | -0.3 | 0.35 × V <sub>CCIO</sub> | 0.65 × V <sub>CCIO</sub> | V <sub>CCIO</sub> + 0.3 | 0.45                     | V <sub>CCIO</sub> - 0.45 | 2                    | -2                                   |

| 1.5 V        | 1.425 | 1.5                   | 1.575 | -0.3 | 0.35 × V <sub>CCIO</sub> | 0.65 × V <sub>CCIO</sub> | V <sub>CCIO</sub> + 0.3 | 0.25 × V <sub>CCIO</sub> | 0.75 × V <sub>CCIO</sub> | 2                    | -2                                   |

| 1.2 V        | 1.14  | 1.2                   | 1.26  | -0.3 | 0.35 × V <sub>CCIO</sub> | 0.65 × V <sub>CCIO</sub> | V <sub>CCIO</sub> + 0.3 | 0.25 × V <sub>CCIO</sub> | 0.75 × V <sub>CCIO</sub> | 2                    | -2                                   |

### Single-Ended SSTL, HSTL, and HSUL I/O Reference Voltage Specifications

Table 16. Single-Ended SSTL, HSTL, and HSUL I/O Reference Voltage Specifications for Cyclone V Devices

| I/O Standard           |       | V <sub>CCIO</sub> (V) V <sub>REF</sub> (V) V <sub>TT</sub> (V) |       |                          |                         |                          |                         |                  |                         |

|------------------------|-------|----------------------------------------------------------------|-------|--------------------------|-------------------------|--------------------------|-------------------------|------------------|-------------------------|

|                        | Min   | Тур                                                            | Max   | Min                      | Тур                     | Max                      | Min                     | Тур              | Max                     |

| SSTL-2 Class I,<br>II  | 2.375 | 2.5                                                            | 2.625 | 0.49 × V <sub>CCIO</sub> | 0.5 × V <sub>CCIO</sub> | 0.51 × V <sub>CCIO</sub> | V <sub>REF</sub> - 0.04 | V <sub>REF</sub> | V <sub>REF</sub> + 0.04 |

| SSTL-18 Class I,<br>II | 1.71  | 1.8                                                            | 1.89  | 0.833                    | 0.9                     | 0.969                    | V <sub>REF</sub> - 0.04 | V <sub>REF</sub> | V <sub>REF</sub> + 0.04 |

|                        |       | '                                                              |       |                          |                         |                          |                         |                  | continued               |

To meet the  $I_{OL}$  and  $I_{OH}$  specifications, you must set the current strength settings accordingly. For example, to meet the 3.3-V LVTTL specification (4 mA), you should set the current strength settings to 4 mA. Setting at lower current strength may not meet the  $I_{OL}$  and  $I_{OH}$  specifications in the datasheet.

# **Transceiver Performance Specifications**

### Transceiver Specifications for Cyclone V GX, GT, SX, and ST Devices

Table 21. Reference Clock Specifications for Cyclone V GX, GT, SX, and ST Devices

| Symbol/Description                                     | Condition                                                | Transceiv | er Speed G     | rade 5 <sup>(30)</sup> | Transce     | iver Speed     | Grade 6                   | Transce     | iver Speed     | Grade 7 | Unit    |

|--------------------------------------------------------|----------------------------------------------------------|-----------|----------------|------------------------|-------------|----------------|---------------------------|-------------|----------------|---------|---------|

|                                                        |                                                          | Min       | Тур            | Max                    | Min         | Тур            | Max                       | Min         | Тур            | Max     |         |

| Supported I/O standards                                |                                                          | 1.2       | 2 V PCML, 1.   | 5 V PCML, 2.           | 5 V PCML, [ | Differential L | VPECL <sup>(31)</sup> , H | CSL, and LV | DS             |         |         |

| Input frequency from REFCLK input pins <sup>(32)</sup> | _                                                        | 27        | _              | 550                    | 27          | _              | 550                       | 27          | _              | 550     | MHz     |

| Rise time                                              | Measure at ±60 mV of differential signal <sup>(33)</sup> | _         | _              | 400                    | _           | _              | 400                       | _           | _              | 400     | ps      |

| Fall time                                              | Measure at ±60 mV of differential signal <sup>(33)</sup> | _         | _              | 400                    | _           | _              | 400                       | _           | _              | 400     | ps      |

| Duty cycle                                             | _                                                        | 45        | _              | 55                     | 45          | _              | 55                        | 45          | _              | 55      | %       |

| Peak-to-peak differential input voltage                | _                                                        | 200       | _              | 2000                   | 200         | _              | 2000                      | 200         | _              | 2000    | mV      |

| Spread-spectrum<br>modulating clock frequency          | PCIe                                                     | 30        | _              | 33                     | 30          | _              | 33                        | 30          | _              | 33      | kHz     |

| Spread-spectrum<br>downspread                          | PCIe                                                     | _         | 0 to -<br>0.5% | _                      | _           | 0 to -<br>0.5% | _                         | _           | 0 to -<br>0.5% | _       | _       |

| On-chip termination resistors                          | _                                                        | _         | 100            | _                      | _           | 100            | _                         | _           | 100            | _       | Ω       |

|                                                        |                                                          |           |                |                        |             |                |                           |             |                | co      | ntinued |

<sup>(30)</sup> Transceiver Speed Grade 5 covers specifications for Cyclone V GT and ST devices.

<sup>(31)</sup> Differential LVPECL signal levels must comply to the minimum and maximum peak-to-peak differential input voltage specified in this table.

<sup>(32)</sup> The reference clock frequency must be  $\geq$  307.2 MHz to be fully compliance to CPRI transmit jitter specification at 6.144 Gbps. For more information about CPRI 6.144 Gbps, refer to the *Transceiver Protocol Configurations in Cyclone V Devices* chapter.

$<sup>^{(33)}</sup>$  REFCLK performance requires to meet transmitter REFCLK phase noise specification.

CV-51002 | 2018.05.07

| Symbol/Description                        | Symbol/Description Condition                                               |     |              |                                          | Transceiver Speed Grade 6 |              |                   | Transceiver Speed Grade 7 |             |     | Unit |

|-------------------------------------------|----------------------------------------------------------------------------|-----|--------------|------------------------------------------|---------------------------|--------------|-------------------|---------------------------|-------------|-----|------|

|                                           |                                                                            | Min | Тур          | Max                                      | Min                       | Тур          | Max               | Min                       | Тур         | Max |      |

| Programmable ppm detector <sup>(46)</sup> | _                                                                          |     |              | ±62.5                                    | 5, 100, 125,              | 200, 250, 3  | 00, 500, and      | 1000                      |             |     | ppm  |

| Run length                                | _                                                                          | _   | _            | 200                                      | _                         | _            | 200               | _                         | _           | 200 | UI   |

| Programmable equalization AC and DC gain  | AC gain setting = 0<br>to 3 <sup>(47)</sup><br>DC gain setting = 0<br>to 1 |     | X, and ST De | se at Data Revices and Cl<br>DC Gain for | TLE Respons               | e at Data Ra | $tes \leq 3.25$ ( | Gbps across               | Supported A |     | dB   |

Table 24. Transmitter Specifications for Cyclone V GX, GT, SX, and ST Devices

| Symbol/Description            | Condition     | Transceiv | er Speed G | rade 5 <sup>(30)</sup>        | Transce | iver Speed | Grade 6 | Transce | Unit |      |         |

|-------------------------------|---------------|-----------|------------|-------------------------------|---------|------------|---------|---------|------|------|---------|

|                               |               | Min       | Тур        | Max                           | Min     | Тур        | Max     | Min     | Тур  | Max  |         |

| Supported I/O standards       |               |           |            |                               | 1.5 V   | PCML       | •       |         |      |      |         |

| Data rate                     | _             | 614       | _          | 5000/614<br>4 <sup>(35)</sup> | 614     | _          | 3125    | 614     | _    | 2500 | Mbps    |

| V <sub>OCM</sub> (AC coupled) | _             | _         | 650        | _                             | _       | 650        | _       | _       | 650  | _    | mV      |

| Differential on-chip          | 85-Ω setting  | _         | 85         | _                             | _       | 85         | _       | _       | 85   | _    | Ω       |

| termination resistors         | 100-Ω setting | _         | 100        | _                             | _       | 100        | _       | _       | 100  | _    | Ω       |

|                               | 120-Ω setting | _         | 120        | _                             | _       | 120        | _       | _       | 120  | _    | Ω       |

|                               | 150-Ω setting | _         | 150        | _                             | _       | 150        | _       | _       | 150  | _    | Ω       |

|                               |               | •         |            |                               |         | •          | •       |         |      | co   | ntinued |

$<sup>^{(45)}</sup>$   $t_{LTR\_LTD\_manual}$  is the time the receiver CDR must be kept in lock to reference (LTR) mode after the rx\_is\_lockedtoref signal goes high when the CDR is functioning in the manual mode.

$<sup>^{(46)}</sup>$  The rate matcher supports only up to  $\pm 300$  parts per million (ppm).

<sup>(47)</sup> The Intel Quartus Prime software allows AC gain setting = 3 for design with data rate between 614 Mbps and 1.25 Gbps only.

### Typical TX $V_{OD}$ Setting for Cyclone V Transceiver Channels with termination of 100 $\Omega$

### Table 27. Typical TX $V_{OD}$ Setting for Cyclone V Transceiver Channels with termination of 100 $\Omega$

| Symbol                               | V <sub>OD</sub> Setting <sup>(48)</sup> | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting <sup>(48)</sup> | V <sub>OD</sub> Value (mV) |

|--------------------------------------|-----------------------------------------|----------------------------|-----------------------------------------|----------------------------|

| OD differential peak-to-peak typical | 6(49)                                   | 120                        | 34                                      | 680                        |

|                                      | 7 <sup>(49)</sup>                       | 140                        | 35                                      | 700                        |

|                                      | 8(49)                                   | 160                        | 36                                      | 720                        |

|                                      | 9                                       | 180                        | 37                                      | 740                        |

|                                      | 10                                      | 200                        | 38                                      | 760                        |

|                                      | 11                                      | 220                        | 39                                      | 780                        |

|                                      | 12                                      | 240                        | 40                                      | 800                        |

|                                      | 13                                      | 260                        | 41                                      | 820                        |

|                                      | 14                                      | 280                        | 42                                      | 840                        |

|                                      | 15                                      | 300                        | 43                                      | 860                        |

|                                      | 16                                      | 320                        | 44                                      | 880                        |

|                                      | 17                                      | 340                        | 45                                      | 900                        |

|                                      | 18                                      | 360                        | 46                                      | 920                        |

|                                      | 19                                      | 380                        | 47                                      | 940                        |

|                                      | 20                                      | 400                        | 48                                      | 960                        |

|                                      | 21                                      | 420                        | 49                                      | 980                        |

|                                      | 22                                      | 440                        | 50                                      | 1000                       |

|                                      | 23                                      | 460                        | 51                                      | 1020                       |

|                                      | 24                                      | 480                        | 52                                      | 1040                       |

|                                      |                                         | •                          |                                         | continu                    |

<sup>(48)</sup> Convert these values to their binary equivalent form if you are using the dynamic reconfiguration mode for PMA analog controls.

<sup>(49)</sup> Only valid for data rates  $\leq$  5 Gbps.

### **Transceiver Compliance Specification**

The following table lists the physical medium attachment (PMA) specification compliance of all supported protocol for Cyclone V GX, GT, SX, and ST devices. For more information about the protocol parameter details and compliance specifications, contact your Intel Sales Representative.

Table 29. Transceiver Compliance Specification for All Supported Protocol for Cyclone V GX, GT, SX, and ST Devices

| Protocol                             | Sub-protocol              | Data Rate (Mbps) |

|--------------------------------------|---------------------------|------------------|

| PCIe                                 | PCIe Gen1                 | 2,500            |

|                                      | PCIe Gen2 <sup>(50)</sup> | 5,000            |

|                                      | PCIe Cable                | 2,500            |

| XAUI                                 | XAUI 2135                 | 3,125            |

| Serial RapidIO® (SRIO)               | SRIO 1250 SR              | 1,250            |

|                                      | SRIO 1250 LR              | 1,250            |

|                                      | SRIO 2500 SR              | 2,500            |

|                                      | SRIO 2500 LR              | 2,500            |

|                                      | SRIO 3125 SR              | 3,125            |

|                                      | SRIO 3125 LR              | 3,125            |

|                                      | SRIO 5000 SR              | 5,000            |

|                                      | SRIO 5000 MR              | 5,000            |

|                                      | SRIO 5000 LR              | 5,000            |

| Common Public Radio Interface (CPRI) | CPRI E6LV                 | 614.4            |

|                                      | CPRI E6HV                 | 614.4            |

|                                      | CPRI E6LVII               | 614.4            |

|                                      |                           | continued        |

<sup>(50)</sup> For PCIe Gen2 sub-protocol, Intel recommends increasing the V<sub>CCE\_GXBL</sub> and V<sub>CCL\_GXBL</sub> typical value from 1.1 V to 1.2 V for Cyclone V GT and ST FPGA systems which ensure full compliance to the PCIe Gen2 transmit jitter specification. For more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices under this condition, refer to the *Transceiver Protocol Configurations in Cyclone V Devices* chapter.

CV-51002 | 2018.05.07

| Protocol                       | Sub-protocol                 | Data Rate (Mbps) |

|--------------------------------|------------------------------|------------------|

|                                | CPRI E12LV                   | 1,228.8          |

|                                | CPRI E12HV                   | 1,228.8          |

|                                | CPRI E12LVII                 | 1,228.8          |

|                                | CPRI E24LV                   | 2,457.6          |

|                                | CPRI E24LVII                 | 2,457.6          |

|                                | CPRI E30LV                   | 3,072            |

|                                | CPRI E30LVII                 | 3,072            |

|                                | CPRI E48LVII <sup>(51)</sup> | 4,915.2          |

|                                | CPRI E60LVII <sup>(51)</sup> | 6,144            |

| Gbps Ethernet (GbE)            | GbE 1250                     | 1,250            |

| OBSAI                          | OBSAI 768                    | 768              |

|                                | OBSAI 1536                   | 1,536            |

|                                | OBSAI 3072                   | 3,072            |

| Serial digital interface (SDI) | SDI 270 SD                   | 270              |

|                                | SDI 1485 HD                  | 1,485            |

|                                | SDI 2970 3G                  | 2,970            |

| VbyOne                         | VbyOne 3750                  | 3,750            |

| HiGig+                         | HIGIG 3750                   | 3,750            |

#### **Related Information**

• PCIe Supported Configurations and Placement Guidelines

Provides more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices which require full compliance to the PCIe Gen2 transmit jitter specification.

<sup>(51)</sup> For CPRI E48LVII and E60LVII, Intel recommends increasing the V<sub>CCE\_GXBL</sub> and V<sub>CCL\_GXBL</sub> typical value from 1.1 V to 1.2 V for full compliance to CPRI transmit jitter specification at 4.9152 Gbps (Cyclone V GT and ST devices) and 6.144 Gbps (Cyclone V GT and ST devices for CPRI 6.144 Gbps, refer to the *Transceiver Protocol Configurations in Cyclone V Devices* chapter.

#### CV-51002 | 2018.05.07

| Symbol                                                                                                                                   | Condition                                               |      | -C6 |      |      | -C7, -I7 |      |      | -C8, -A7 |      | Unit  |

|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------|-----|------|------|----------|------|------|----------|------|-------|

|                                                                                                                                          |                                                         | Min  | Тур | Max  | Min  | Тур      | Max  | Min  | Тур      | Max  |       |

|                                                                                                                                          | SERDES factor J<br>= 1 to 2, uses<br>DDR registers      | (65) | _   | (66) | (65) | _        | (66) | (65) | _        | (66) | Mbps  |

| Emulated Differential I/O<br>Standards with Three External<br>Output Resistor Networks- f <sub>HSDR</sub><br>(data rate) <sup>(67)</sup> | SERDES factor J<br>= 4 to 10                            | (65) | _   | 640  | (65) | -        | 640  | (65) | _        | 550  | Mbps  |

| Emulated Differential I/O<br>Standards with One External<br>Output Resistor Network - f <sub>HSDR</sub><br>(data rate)                   | SERDES factor J<br>= 4 to 10                            | (65) | _   | 170  | (65) | _        | 170  | (65) | _        | 170  | Mbps  |

| t <sub>x Jitter</sub> -True Differential I/O<br>Standards <sup>(67)</sup>                                                                | Total Jitterfor<br>Data Rate, 600<br>Mbps – 840<br>Mbps | _    | _   | 350  | _    | _        | 380  | _    | _        | 500  | ps    |

|                                                                                                                                          | Total Jitter for<br>Data Rate <<br>600Mbps              | _    | _   | 0.21 | _    | _        | 0.23 | _    | _        | 0.30 | UI    |

| t <sub>x Jitter</sub> -Emulated Differential I/O<br>Standards with Three External<br>Output Resistor Networks                            | Total Jitter for<br>Data Rate <<br>640Mbps              | _    | _   | 500  | _    | _        | 500  | _    | _        | 500  | ps    |

| t <sub>x Jitter</sub> -Emulated Differential I/O<br>Standards with One External<br>Output Resistor Network                               | Total Jitter for<br>Data Rate <<br>640Mbps              | _    | _   | 0.15 | _    | _        | 0.15 | _    | _        | 0.15 | UI    |

| t <sub>DUTY</sub>                                                                                                                        | TX output clock<br>duty cycle for<br>both True and      | 45   | 50  | 55   | 45   | 50       | 55   | 45   | 50       | 55   | %     |

| <b>'</b>                                                                                                                                 |                                                         |      |     |      | ·    | 1        | 1    |      | 1        | cont | inued |

The maximum ideal data rate is the SERDES factor (J)  $\times$  PLL max output frequency ( $f_{out}$ ), provided you can close the design timing and the signal integrity simulation is clean. You can estimate the achievable maximum data rate by performing link timing closure analysis. You must consider the board skew margin, transmitter delay margin, and receiver sampling margin to determine the maximum data rate supported.

<sup>(67)</sup> You must calculate the leftover timing margin in the receiver by performing link timing closure analysis. You must consider the board skew margin, transmitter channel-to-channel skew, and receiver sampling margin to determine the leftover timing margin.

### **SD/MMC Timing Characteristics**

### Table 46. Secure Digital (SD)/MultiMediaCard (MMC) Timing Requirements for Cyclone V Devices

After power up or cold reset, the Boot ROM uses drvsel = 3 and smplsel = 0 to execute the code. At the same time, the SD/MMC controller enters the Identification Phase followed by the Data Phase. During this time, the value of interface output clock SDMMC\_CLK\_OUT changes from a maximum of 400 kHz (Identification Phase) up to a maximum of 12.5 MHz (Data Phase), depending on the internal reference clock SDMMC\_CLK and the CSEL setting. The value of SDMMC\_CLK is based on the external oscillator frequency and has a maximum value of 50 MHz.

After the Boot ROM code exits and control is passed to the preloader, software can adjust the value of drvsel and smplsel via the system manager. drvsel can be set from 1 to 7 and smplsel can be set from 0 to 7. While the preloader is executing, the values for SDMMC\_CLK and SDMMC\_CLK\_OUT increase to a maximum of 200 MHz and 50 MHz respectively.

| Symbol                                              | Description                                      | Min                                                      | Max                                                           | Unit |

|-----------------------------------------------------|--------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------|------|

| T <sub>sdmmc_clk</sub> (internal reference clock)   | SDMMC_CLK clock period (Identification mode)     | 20                                                       | _                                                             | ns   |

|                                                     | SDMMC_CLK clock period (Default speed mode)      | 5                                                        | _                                                             | ns   |

|                                                     | SDMMC_CLK clock period (High speed mode)         | 5                                                        | _                                                             | ns   |

| T <sub>sdmmc_clk_out</sub> (interface output clock) | SDMMC_CLK_OUT clock period (Identification mode) | 2500                                                     | _                                                             | ns   |

|                                                     | SDMMC_CLK_OUT clock period (Default speed mode)  | 40                                                       | _                                                             | ns   |

|                                                     | SDMMC_CLK_OUT clock period (High speed mode)     | 20                                                       | _                                                             | ns   |

| T <sub>dutycycle</sub>                              | SDMMC_CLK_OUT duty cycle                         | 45                                                       | 55                                                            | %    |

| T <sub>d</sub>                                      | SDMMC_CMD/SDMMC_D output delay                   | (T <sub>sdmmc_clk</sub> × drvsel)/2 - 1.23               | (T <sub>sdmmc_clk</sub> × drvsel)/2<br>+ 1.69 <sup>(70)</sup> | ns   |

| T <sub>su</sub>                                     | Input setup time                                 | $1.05 - (T_{\text{sdmmc\_clk}} \times \text{smplsel})/2$ | _                                                             | ns   |

| T <sub>h</sub>                                      | Input hold time                                  | $(T_{sdmmc\_clk} \times smplsel)/2$ (71)                 | _                                                             | ns   |

$<sup>^{(70)}</sup>$  drvsel is the drive clock phase shift select value.

$<sup>^{(71)}</sup>$  smplsel is the sample clock phase shift select value.

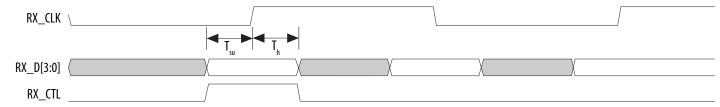

### Table 49. RGMII RX Timing Requirements for Cyclone V Devices

| Symbol                        | Description            | Min | Тур | Unit |

|-------------------------------|------------------------|-----|-----|------|

| T <sub>clk</sub> (1000Base-T) | RX_CLK clock period    | _   | 8   | ns   |

| T <sub>clk</sub> (100Base-T)  | RX_CLK clock period    | _   | 40  | ns   |

| T <sub>clk</sub> (10Base-T)   | RX_CLK clock period    | _   | 400 | ns   |

| T <sub>su</sub>               | RX_D/RX_CTL setup time | 1   | _   | ns   |

| T <sub>h</sub>                | RX_D/RX_CTL hold time  | 1   | _   | ns   |

### Figure 12. RGMII RX Timing Diagram

Table 50. Management Data Input/Output (MDIO) Timing Requirements for Cyclone V Devices

| Symbol           | Description                   | Min | Тур | Max | Unit |

|------------------|-------------------------------|-----|-----|-----|------|

| T <sub>clk</sub> | MDC clock period              | _   | 400 | _   | ns   |

| T <sub>d</sub>   | MDC to MDIO output data delay | 10  | _   | 20  | ns   |

| T <sub>s</sub>   | Setup time for MDIO data      | 10  | _   | _   | ns   |

| T <sub>h</sub>   | Hold time for MDIO data       | 0   | -   | _   | ns   |

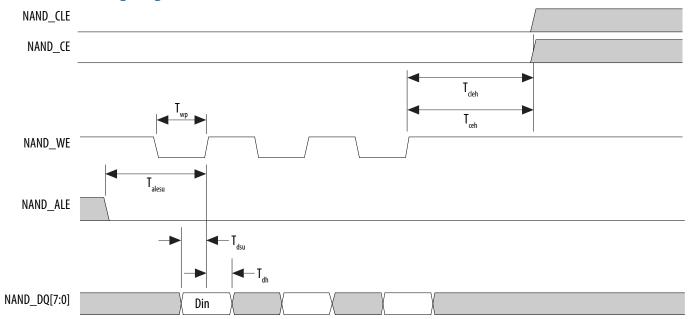

Figure 17. NAND Data Write Timing Diagram

#### CV-51002 | 2018.05.07

| Symbol            | Description                              | Min | Max                | Unit |

|-------------------|------------------------------------------|-----|--------------------|------|

| t <sub>JPCO</sub> | JTAG port clock to output                | _   | 11 <sup>(76)</sup> | ns   |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output | _   | 14 <sup>(76)</sup> | ns   |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance | _   | 14 <sup>(76)</sup> | ns   |

### **FPP Configuration Timing**

### DCLK-to-DATA[] Ratio (r) for FPP Configuration

Fast passive parallel (FPP) configuration requires a different DCLK-to-DATA[] ratio when you turn on encryption or the compression feature.

Depending on the DCLK-to-DATA[] ratio, the host must send a DCLK frequency that is r times the DATA[] rate in byte per second (Bps) or word per second (Wps). For example, in FPP  $\times 16$  where the r is 2, the DCLK frequency must be 2 times the DATA[] rate in Wps.

Cyclone V devices use additional clock cycles to decrypt and decompress the configuration data. If the DCLK-to-DATA[] ratio is greater than 1, at the end of configuration, you can only stop the DCLK (DCLK-to-DATA[] ratio - 1) clock cycles after the last data is latched into the Cyclone V device.

**Table 57. DCLK-to-DATA[] Ratio for Cyclone V Devices**

| Configuration Scheme | Encryption | Compression | DCLK-to-DATA[] Ratio (r) |

|----------------------|------------|-------------|--------------------------|

| FPP (8-bit wide)     | Off        | Off         | 1                        |

|                      | On         | Off         | 1                        |

|                      | Off        | On          | 2                        |

|                      | On         | On          | 2                        |

| FPP (16-bit wide)    | Off        | Off         | 1                        |

|                      |            |             | continued                |

<sup>(76)</sup> A 1-ns adder is required for each VCCIO voltage step down from 3.0 V. For example, tJPCO= 13 ns if VCCIO of the TDO I/O bank = 2.5 V, or 14 ns if it equals 1.8 V.

## **Active Serial (AS) Configuration Timing**

#### Table 60. AS Timing Parameters for AS ×1 and ×4 Configurations in Cyclone V Devices

The minimum and maximum numbers apply to both the internal oscillator and CLKUSR when either one is used as the clock source for device configuration.

The  $t_{CF2ST0}$ ,  $t_{CF2ST0}$ ,  $t_{CF2ST0}$ ,  $t_{CF2ST0}$ ,  $t_{CF2ST1}$  timing parameters are identical to the timing parameters for passive serial (PS) mode listed in PS Timing Parameters for Cyclone V Devices table. You can obtain the  $t_{CF2ST1}$  value if you do not delay configuration by externally holding nSTATUS low.

| Symbol                          | Parameter                                                 | Minimum                                       | Maximum | Unit   |

|---------------------------------|-----------------------------------------------------------|-----------------------------------------------|---------|--------|

| t <sub>co</sub>                 | DCLK falling edge to the AS_DATAO/ASDO output             | _                                             | 2       | ns     |

| t <sub>SU</sub>                 | Data setup time before the falling edge on DCLK           | 1.5                                           | _       | ns     |

| t <sub>DH</sub> <sup>(86)</sup> | Data hold time after the falling edge on DCLK             | 2.5 <sup>(87)</sup> /2.9 <sup>(88)</sup>      | _       | ns     |

| t <sub>CD2UM</sub>              | CONF_DONE high to user mode                               | 175                                           | 437     | μs     |

| t <sub>CD2CU</sub>              | CONF_DONE high to CLKUSR enabled                          | 4 × maximum DCLK period                       | _       | _      |

| t <sub>CD2UMC</sub>             | CONF_DONE high to user mode with CLKUSR option on         | $t_{CD2CU} + (T_{init} \times CLKUSR period)$ | _       | _      |

| T <sub>init</sub>               | Number of clock cycles required for device initialization | 8,576                                         | _       | Cycles |

#### **Related Information**

- Passive Serial (PS) Configuration Timing on page 74

- AS Configuration Timing

Provides the AS configuration timing waveform.

- AN822: Intel FPGA Configuration Device Migration Guideline

<sup>(86)</sup> Note: To evaluate the data setup (t<sub>SU</sub>) and data hold time (t<sub>DH</sub>) slack on your board in order to ensure you are meeting the t<sub>SU</sub> and t<sub>DH</sub> requirement, you are recommended to follow the guideline in the "Evaluating Data Setup and Hold Timing Slack" chapter in AN822: Intel FPGA Configuration Device Migration Guideline.

<sup>(87)</sup> Specification for -6 speed grade

<sup>(88)</sup> Specification for -7 and -8 speed grade

# **Configuration Files**

### Table 64. Uncompressed .rbf Sizes for Cyclone V Devices

Use this table to estimate the file size before design compilation. Different configuration file formats, such as a hexadecimal file (.hex) or tabular text file (.ttf) format, have different file sizes.

For the different types of configuration file and file sizes, refer to the Intel Quartus Prime software. However, for a specific version of the Intel Quartus Prime software, any design targeted for the same device has the same uncompressed configuration file size.

The IOCSR raw binary file (.rbf) size is specifically for the Configuration via Protocol (CvP) feature.

| Variant                     | Member Code | Configuration .rbf Size (bits) | IOCSR .rbf Size (bits) | Recommended EPCQ Serial Configuration Device <sup>(94)</sup> |

|-----------------------------|-------------|--------------------------------|------------------------|--------------------------------------------------------------|

| Cyclone V E <sup>(95)</sup> | A2          | 21,061,280                     | 275,608                | EPCQ64                                                       |

|                             | A4          | 21,061,280                     | 275,608                | EPCQ64                                                       |

|                             | A5          | 33,958,560                     | 322,072                | EPCQ128                                                      |

|                             | A7          | 56,167,552                     | 435,288                | EPCQ128                                                      |

|                             | A9          | 102,871,776                    | 400,408                | EPCQ256                                                      |

| Cyclone V GX                | C3          | 14,510,912                     | 320,280                | EPCQ32                                                       |

|                             | C4          | 33,958,560                     | 322,072                | EPCQ128                                                      |

|                             | C5          | 33,958,560                     | 322,072                | EPCQ128                                                      |

|                             | C7          | 56,167,552                     | 435,288                | EPCQ128                                                      |

|                             | C9          | 102,871,776                    | 400,408                | EPCQ256                                                      |

| Cyclone V GT                | D5          | 33,958,560                     | 322,072                | EPCQ128                                                      |

|                             | D7          | 56,167,552                     | 435,288                | EPCQ128                                                      |

|                             | D9          | 102,871,776                    | 400,408                | EPCQ256                                                      |

| Cyclone V SE (95)           | A2          | 33,958,560                     | 322,072                | EPCQ128                                                      |

|                             |             |                                |                        | continued                                                    |

<sup>(94)</sup> The recommended EPCQ serial configuration devices are able to store more than one image.

<sup>(95)</sup> No PCIe hard IP, configuration via protocol (CvP) is not supported in this family.

| Variant      | Member Code |       | Active Seria | l <sup>(96)</sup>                  |       | Fast Passive Pa | rallel <sup>(97)</sup>          |

|--------------|-------------|-------|--------------|------------------------------------|-------|-----------------|---------------------------------|

|              |             | Width | DCLK (MHz)   | Minimum Configuration<br>Time (ms) | Width | DCLK (MHz)      | Minimum Configuration Time (ms) |

|              | A9          | 4     | 100          | 257                                | 16    | 125             | 51                              |

| Cyclone V GX | C3          | 4     | 100          | 36                                 | 16    | 125             | 7                               |

|              | C4          | 4     | 100          | 85                                 | 16    | 125             | 17                              |

|              | C5          | 4     | 100          | 85                                 | 16    | 125             | 17                              |

|              | C7          | 4     | 100          | 140                                | 16    | 125             | 28                              |

|              | C9          | 4     | 100          | 257                                | 16    | 125             | 51                              |

| Cyclone V GT | D5          | 4     | 100          | 85                                 | 16    | 125             | 17                              |

|              | D7          | 4     | 100          | 140                                | 16    | 125             | 28                              |

|              | D9          | 4     | 100          | 257                                | 16    | 125             | 51                              |

| Cyclone V SE | A2          | 4     | 100          | 85                                 | 16    | 125             | 17                              |

|              | A4          | 4     | 100          | 85                                 | 16    | 125             | 17                              |

|              | A5          | 4     | 100          | 140                                | 16    | 125             | 28                              |

|              | A6          | 4     | 100          | 140                                | 16    | 125             | 28                              |

| Cyclone V SX | C2          | 4     | 100          | 85                                 | 16    | 125             | 17                              |

|              | C4          | 4     | 100          | 85                                 | 16    | 125             | 17                              |

|              | C5          | 4     | 100          | 140                                | 16    | 125             | 28                              |

|              | C6          | 4     | 100          | 140                                | 16    | 125             | 28                              |

| Cyclone V ST | D5          | 4     | 100          | 140                                | 16    | 125             | 28                              |

|              | D6          | 4     | 100          | 140                                | 16    | 125             | 28                              |

$<sup>^{(96)}\,</sup>$  DCLK frequency of 100 MHz using external CLKUSR.

<sup>(97)</sup> Maximum FPGA FPP bandwidth may exceed bandwidth available from some external storage or control logic.

CV-51002 | 2018.05.07

# **Programmable Output Buffer Delay**

### Table 69. Programmable Output Buffer Delay for Cyclone V Devices

This table lists the delay chain settings that control the rising and falling edge delays of the output buffer.

You can set the programmable output buffer delay in the Intel Quartus Prime software by setting the **Output Buffer Delay Control** assignment to either positive, negative, or both edges, with the specific values stated here (in ps) for the **Output Buffer Delay** assignment.

| Symbol              | Parameter                        | Typical     | Unit |

|---------------------|----------------------------------|-------------|------|

| D <sub>OUTBUF</sub> | Rising and/or falling edge delay | 0 (default) | ps   |

|                     |                                  | 50          | ps   |

|                     |                                  | 100         | ps   |

|                     |                                  | 150         | ps   |

# **Glossary**

### Table 70. Glossary

| Term                       | Definition               |

|----------------------------|--------------------------|

| Differential I/O standards | Receiver Input Waveforms |

|                            | continued                |