Welcome to **E-XFL.COM**

**Embedded - System On Chip (SoC):** The Heart of Modern Embedded Systems

Embedded - System On Chip (SoC) refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

What are **Embedded - System On Chip (SoC)?**

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

| Details                 |                                                                                    |

|-------------------------|------------------------------------------------------------------------------------|

| Product Status          | Active                                                                             |

| Architecture            | MCU, FPGA                                                                          |

| Core Processor          | Dual ARM® Cortex®-A9 MPCore™ with CoreSight™                                       |

| Flash Size              | -                                                                                  |

| RAM Size                | 64KB                                                                               |

| Peripherals             | DMA, POR, WDT                                                                      |

| Connectivity            | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Speed                   | 800MHz                                                                             |

| Primary Attributes      | FPGA - 110K Logic Elements                                                         |

| Operating Temperature   | 0°C ~ 85°C (TJ)                                                                    |

| Package / Case          | 672-FBGA                                                                           |

| Supplier Device Package | 672-UBGA (23x23)                                                                   |

| Purchase URL            | https://www.e-xfl.com/product-detail/intel/5cseba6u23c7n                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Density | Ordering Part Number (OPN) | Static Power Reduction |

|---------|----------------------------|------------------------|

| 110K LE | 5CSEBA6U19I7LN             |                        |

|         | 5CSEBA6U23I7LN             |                        |

|         | 5CSXFC6C6U23I7LN           |                        |

To estimate total power consumption for a low-power device, listed in Table 1 on page 3:

- 1. Multiply the Total Static Power reported by the Early Power Estimator (EPE) by the appropriate scale factor:

- For 25K LE and 40K LE devices, use 0.7

- For 85K LE and 110K LE devices, use 0.8

- 2. Add the result from Step 1 on page 4 to the Total Dynamic Power reported by the EPE.

#### **Related Information**

Cyclone V Device Overview

Provides more information about the densities and packages of devices in the Cyclone V family.

## **Electrical Characteristics**

The following sections describe the operating conditions and power consumption of Cyclone V devices.

# **Operating Conditions**

Cyclone V devices are rated according to a set of defined parameters. To maintain the highest possible performance and reliability of the Cyclone V devices, you must consider the operating requirements described in this section.

# **Absolute Maximum Ratings**

This section defines the maximum operating conditions for Cyclone V devices. The values are based on experiments conducted with the devices and theoretical modeling of breakdown and damage mechanisms.

The functional operation of the device is not implied for these conditions.

#### Caution:

Conditions outside the range listed in the following table may cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse effects on the device.

## **Maximum Allowed Overshoot and Undershoot Voltage**

During transitions, input signals may overshoot to the voltage listed in the following table and undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

The maximum allowed overshoot duration is specified as a percentage of high time over the lifetime of the device. A DC signal is equivalent to 100% duty cycle.

For example, a signal that overshoots to 4.00 V can only be at 4.00 V for  $\sim 15\%$  over the lifetime of the device; for a device lifetime of 10 years, this amounts to 1.5 years.

### Table 3. Maximum Allowed Overshoot During Transitions for Cyclone V Devices

This table lists the maximum allowed input overshoot voltage and the duration of the overshoot voltage as a percentage of device lifetime.

| Symbol  | Description      | Condition (V) | Overshoot Duration as % of High Time | Unit      |

|---------|------------------|---------------|--------------------------------------|-----------|

| Vi (AC) | AC input voltage | 3.8           | 100                                  | %         |

|         |                  | 3.85          | 68                                   | %         |

|         |                  | 3.9           | 45                                   | %         |

|         |                  | 3.95          | 28                                   | %         |

|         |                  | 4             | 15                                   | %         |

|         |                  | 4.05          | 13                                   | %         |

|         |                  | 4.1           | 11                                   | %         |

|         |                  | 4.15          | 9                                    | %         |

|         |                  | 4.2           | 8                                    | %         |

|         |                  | 4.25          | 7                                    | %         |

|         |                  | 4.3           | 5.4                                  | %         |

|         |                  | 4.35          | 3.2                                  | %         |

|         |                  | 4.4           | 1.9                                  | %         |

|         |                  | 4.45          | 1.1                                  | %         |

|         | ·                |               | ·                                    | continued |

### **Differential I/O Standard Specifications**

#### Table 20. Differential I/O Standard Specifications for Cyclone V Devices

Differential inputs are powered by  $V_{\text{CCPD}}$  which requires 2.5 V.

| I/O Standard               | ,      | V <sub>CCIO</sub> (V) |       |     | V <sub>ID</sub> (mV) <sup>(21)</sup> V <sub>I</sub> |     | V <sub>ICM(DC)</sub> (V) | V <sub>OD</sub> (V) <sup>(22)</sup> V <sub>OCM</sub> (V) <sup>(23)</sup> |       | V <sub>OD</sub> (V) <sup>(22</sup> |     | <sub>M</sub> (V) <sup>(22)</sup> | (23)  |            |          |

|----------------------------|--------|-----------------------|-------|-----|-----------------------------------------------------|-----|--------------------------|--------------------------------------------------------------------------|-------|------------------------------------|-----|----------------------------------|-------|------------|----------|

|                            | Min    | Тур                   | Max   | Min | Condition                                           | Max | Min                      | Condition                                                                | Max   | Min                                | Тур | Max                              | Min   | Тур        | Max      |

| PCML                       | Transm | itter, rece           |       |     | ence clock pins<br>fications, refer                 |     |                          |                                                                          |       |                                    |     |                                  |       | nd referen | ce clock |

| 2.5 V LVDS <sup>(24)</sup> | 2.375  | 2.5                   | 2.625 | 100 | V <sub>CM</sub> = 1.25<br>V                         | _   | 0.05                     | D <sub>MAX</sub> ≤ 700<br>Mbps                                           | 1.80  | 0.247                              | _   | 0.6                              | 1.125 | 1.25       | 1.375    |

|                            |        |                       |       |     |                                                     |     | 1.05                     | D <sub>MAX</sub> > 700<br>Mbps                                           | 1.55  |                                    |     |                                  |       |            |          |

| BLVDS <sup>(25)(26)</sup>  | 2.375  | 2.5                   | 2.625 | 100 | _                                                   | _   | -                        | _                                                                        | _     | _                                  | _   | _                                | _     | -          | _        |

| RSDS (HIO) <sup>(27)</sup> | 2.375  | 2.5                   | 2.625 | 100 | V <sub>CM</sub> = 1.25<br>V                         | _   | 0.25                     | _                                                                        | 1.45  | 0.1                                | 0.2 | 0.6                              | 0.5   | 1.2        | 1.4      |

| Mini-LVDS (HIO)            | 2.375  | 2.5                   | 2.625 | 200 | _                                                   | 600 | 0.300                    | _                                                                        | 1.425 | 0.25                               | _   | 0.6                              | 1     | 1.2        | 1.4      |

|                            | •      |                       |       |     |                                                     |     | •                        |                                                                          |       |                                    |     |                                  |       | cont       | inued    |

$<sup>^{(21)}</sup>$  The minimum  $V_{\text{ID}}$  value is applicable over the entire common mode range,  $V_{\text{CM}}.$

<sup>&</sup>lt;sup>(22)</sup>  $R_L$  range:  $90 \le R_L \le 110 \Omega$ .

<sup>(23)</sup> This applies to default pre-emphasis setting only.

<sup>(24)</sup> For optimized LVDS receiver performance, the receiver voltage input range must be within 1.0 V to 1.6 V for data rate above 700 Mbps and 0.00 V to 1.85 V for data rate below 700 Mbps.

<sup>(25)</sup> There are no fixed  $V_{ICM}$ ,  $V_{OD}$ , and  $V_{OCM}$  specifications for BLVDS. They depend on the system topology.

<sup>(26)</sup> For more information about BLVDS interface support in Intel devices, refer to AN522: Implementing Bus LVDS Interface in Supported Intel Device Families.

<sup>(27)</sup> For optimized RSDS receiver performance, the receiver voltage input range must be within 0.25 V to 1.45 V.

<sup>(28)</sup> For optimized mini-LVDS receiver performance, the receiver voltage input range must be within 0.300 V to 1.425 V.

Exceptions for PCIe Gen2 design:

- V<sub>OD</sub> setting = 50 and pre-emphasis setting = 22 are allowed for PCIe Gen2 design with transmit de-emphasis -6dB setting (pipe\_txdeemp = 1'b0) using Intel PCIe Hard IP and PIPE IP cores.

- V<sub>OD</sub> setting = 50 and pre-emphasis setting = 12 are allowed for PCIe Gen2 design with transmit de-emphasis -3.5dB setting (pipe\_txdeemp = 1'b1) using Intel PCIe Hard IP and PIPE IP cores.

For example, when  $V_{OD} = 800$  mV, the corresponding  $V_{OD}$  value setting is 40. The following conditions show that the 1st post tap pre-emphasis setting = 2 is valid:

- $|B| + |C| \le 60 \rightarrow 40 + 2 = 42$

- $|B| |C| > 5 \rightarrow 40 2 = 38$

- $(V_{MAX}/V_{MIN} 1)\% < 600\% \rightarrow (42/38 1)\% = 10.52\%$

To predict the pre-emphasis level for your specific data rate and pattern, run simulations using the Cyclone V HSSI HSPICE models.

**Table 28.** Transmitter Pre-Emphasis Levels for Cyclone V Devices

| Intel Quartus Prime 1st          |             |             | Intel Qu    | uartus Prime V <sub>OD</sub> | Setting     |             |              | Unit      |

|----------------------------------|-------------|-------------|-------------|------------------------------|-------------|-------------|--------------|-----------|

| Post Tap Pre-Emphasis<br>Setting | 10 (200 mV) | 20 (400 mV) | 30 (600 mV) | 35 (700 mV)                  | 40 (800 mV) | 45 (900 mV) | 50 (1000 mV) |           |

| 0                                | 0           | 0           | 0           | 0                            | 0           | 0           | 0            | dB        |

| 1                                | 1.97        | 0.88        | 0.43        | 0.32                         | 0.24        | 0.19        | 0.13         | dB        |

| 2                                | 3.58        | 1.67        | 0.95        | 0.76                         | 0.61        | 0.5         | 0.41         | dB        |

| 3                                | 5.35        | 2.48        | 1.49        | 1.2                          | 1           | 0.83        | 0.69         | dB        |

| 4                                | 7.27        | 3.31        | 2           | 1.63                         | 1.36        | 1.14        | 0.96         | dB        |

| 5                                | _           | 4.19        | 2.55        | 2.1                          | 1.76        | 1.49        | 1.26         | dB        |

| 6                                | _           | 5.08        | 3.11        | 2.56                         | 2.17        | 1.83        | 1.56         | dB        |

| 7                                | _           | 5.99        | 3.71        | 3.06                         | 2.58        | 2.18        | 1.87         | dB        |

| 8                                | _           | 6.92        | 4.22        | 3.47                         | 2.93        | 2.48        | 2.11         | dB        |

| 9                                | _           | 7.92        | 4.86        | 4                            | 3.38        | 2.87        | 2.46         | dB        |

| 10                               | _           | 9.04        | 5.46        | 4.51                         | 3.79        | 3.23        | 2.77         | dB        |

|                                  |             |             |             |                              |             |             |              | continued |

## **Transceiver Compliance Specification**

The following table lists the physical medium attachment (PMA) specification compliance of all supported protocol for Cyclone V GX, GT, SX, and ST devices. For more information about the protocol parameter details and compliance specifications, contact your Intel Sales Representative.

Table 29. Transceiver Compliance Specification for All Supported Protocol for Cyclone V GX, GT, SX, and ST Devices

| Protocol                             | Sub-protocol              | Data Rate (Mbps) |

|--------------------------------------|---------------------------|------------------|

| PCIe                                 | PCIe Gen1                 | 2,500            |

|                                      | PCIe Gen2 <sup>(50)</sup> | 5,000            |

|                                      | PCIe Cable                | 2,500            |

| XAUI                                 | XAUI 2135                 | 3,125            |

| Serial RapidIO® (SRIO)               | SRIO 1250 SR              | 1,250            |

|                                      | SRIO 1250 LR              | 1,250            |

|                                      | SRIO 2500 SR              | 2,500            |

|                                      | SRIO 2500 LR              | 2,500            |

|                                      | SRIO 3125 SR              | 3,125            |

|                                      | SRIO 3125 LR              | 3,125            |

|                                      | SRIO 5000 SR              | 5,000            |

|                                      | SRIO 5000 MR              | 5,000            |

|                                      | SRIO 5000 LR              | 5,000            |

| Common Public Radio Interface (CPRI) | CPRI E6LV                 | 614.4            |

|                                      | CPRI E6HV                 | 614.4            |

|                                      | CPRI E6LVII               | 614.4            |

|                                      |                           | continued        |

<sup>(50)</sup> For PCIe Gen2 sub-protocol, Intel recommends increasing the V<sub>CCE\_GXBL</sub> and V<sub>CCL\_GXBL</sub> typical value from 1.1 V to 1.2 V for Cyclone V GT and ST FPGA systems which ensure full compliance to the PCIe Gen2 transmit jitter specification. For more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices under this condition, refer to the *Transceiver Protocol Configurations in Cyclone V Devices* chapter.

#### Cyclone V Device Datasheet

#### CV-51002 | 2018.05.07

| Symbol                   | Parameter                                                                                                | Condition                  | Min | Тур      | Max                 | Unit      |

|--------------------------|----------------------------------------------------------------------------------------------------------|----------------------------|-----|----------|---------------------|-----------|

|                          |                                                                                                          | -C8, -A7 speed grades      | 600 | _        | 1300                | MHz       |

| t <sub>EINDUTY</sub>     | Input clock or external feedback clock input duty cycle                                                  | Г                          | 40  | _        | 60                  | %         |

| fout                     | Output frequency for internal global or regional clock                                                   | -C6, -C7, -I7 speed grades | _   | _        | 550 <sup>(54)</sup> | MHz       |

|                          |                                                                                                          | -C8, -A7 speed grades      | _   | _        | 460 <sup>(54)</sup> | MHz       |

| f <sub>OUT_EXT</sub>     | Output frequency for external clock output                                                               | -C6, -C7, -I7 speed grades | _   | _        | 667 <sup>(54)</sup> | MHz       |

|                          |                                                                                                          | -C8, -A7 speed grades      | _   | _        | 533 <sup>(54)</sup> | MHz       |

| t <sub>оитриту</sub>     | Duty cycle for external clock output (when set to 50%)                                                   | _                          | 45  | 50       | 55                  | %         |

| t <sub>FCOMP</sub>       | External feedback clock compensation time                                                                | _                          | _   | _        | 10                  | ns        |

| t <sub>DYCONFIGCLK</sub> | Dynamic configuration clock for mgmt_clk and scanclk                                                     | _                          | _   | _        | 100                 | MHz       |

| t <sub>LOCK</sub>        | Time required to lock from end-of-device configuration or deassertion of areset                          | _                          | _   | _        | 1                   | ms        |

| t <sub>DLOCK</sub>       | Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/delays) | _                          | _   | _        | 1                   | ms        |

| f <sub>CLBW</sub>        | PLL closed-loop bandwidth                                                                                | Low                        | _   | 0.3      | _                   | MHz       |

|                          |                                                                                                          | Medium                     | _   | 1.5      | _                   | MHz       |

|                          |                                                                                                          | High <sup>(55)</sup>       | _   | 4        | _                   | MHz       |

| t <sub>PLL_PSERR</sub>   | Accuracy of PLL phase shift                                                                              | _                          | -   | _        | ±50                 | ps        |

|                          |                                                                                                          |                            |     | <u>'</u> | <u> </u>            | continued |

<sup>(53)</sup> The VCO frequency reported by the Intel Quartus Prime software takes into consideration the VCO post-scale counter  $\kappa$  value. Therefore, if the counter  $\kappa$  has a value of 2, the frequency reported can be lower than the  $f_{VCO}$  specification.

$<sup>^{(54)}</sup>$  This specification is limited by the lower of the two: I/O  $f_{MAX}$  or  $F_{OUT}$  of the PLL.

<sup>(55)</sup> High bandwidth PLL settings are not supported in external feedback mode.

#### Cyclone V Device Datasheet

#### CV-51002 | 2018.05.07

| Symbol                               | Parameter                                                              | Condition                    | Min    | Тур     | Max        | Unit      |

|--------------------------------------|------------------------------------------------------------------------|------------------------------|--------|---------|------------|-----------|

|                                      |                                                                        | F <sub>OUT</sub> < 100 MHz   | -      | -       | 65         | mUI (p-p) |

| t <sub>OUTCCJ_IO</sub> (58)(60)      | Cycle-to-cycle jitter for clock output on                              | F <sub>OUT</sub> ≥ 100 MHz   | _      | _       | 650        | ps (p-p)  |

|                                      | regular I/O in integer PLL                                             | F <sub>OUT</sub> < 100 MHz   | _      | _       | 65         | mUI (p-p) |

| t <sub>FOUTCCJ_IO</sub> (58)(60)(61) | Cycle-to-cycle jitter for clock output on                              | F <sub>OUT</sub> ≥ 100 MHz   | _      | _       | 650        | ps (p-p)  |

|                                      | regular I/O in fractional PLL                                          | F <sub>OUT</sub> < 100 MHz   | _      | _       | 65         | mUI (p-p) |

| t <sub>CASC_OUTPJ_DC</sub> (58)(62)  | Period jitter for dedicated clock output in                            | F <sub>OUT</sub> ≥ 100 MHz   | -      | -       | 300        | ps (p-p)  |

|                                      | cascaded PLLs                                                          | F <sub>OUT</sub> < 100 MHz   | _      | _       | 30         | mUI (p-p) |

| t <sub>DRIFT</sub>                   | Frequency drift after PFDENA is disabled for a duration of 100 $\mu s$ | _                            | _      | _       | ±10        | %         |

| dK <sub>BIT</sub>                    | Bit number of Delta Sigma Modulator (DSM)                              | _                            | 8      | 24      | 32         | Bits      |

| k <sub>VALUE</sub>                   | Numerator of fraction                                                  | _                            | 128    | 8388608 | 2147483648 | _         |

| f <sub>RES</sub>                     | Resolution of VCO frequency                                            | f <sub>INPFD</sub> = 100 MHz | 390625 | 5.96    | 0.023      | Hz        |

#### **Related Information**

Memory Output Clock Jitter Specifications on page 49

Provides more information about the external memory interface clock output jitter specifications.

$<sup>^{(61)}</sup>$  This specification only covers fractional PLL for low bandwidth. The  $f_{VCO}$  for fractional value range 0.05–0.95 must be  $\geq$  1000 MHz.

<sup>(62)</sup> The cascaded PLL specification is only applicable with the following conditions:

<sup>•</sup> Upstream PLL: 0.59 MHz ≤ Upstream PLL BW < 1 MHz

<sup>•</sup> Downstream PLL: Downstream PLL BW > 2 MHz

|                 | Symbol                                  | Condition                                                                        |      | -C6 |                     |      | -C7, -I7 |                     |      | -C8, -A7 | ,                   | Unit |

|-----------------|-----------------------------------------|----------------------------------------------------------------------------------|------|-----|---------------------|------|----------|---------------------|------|----------|---------------------|------|

|                 |                                         |                                                                                  | Min  | Тур | Max                 | Min  | Тур      | Max                 | Min  | Тур      | Max                 |      |

|                 |                                         | Emulated<br>Differential I/O<br>Standards                                        |      |     |                     |      |          |                     |      |          |                     |      |

|                 | t <sub>RISE</sub> and t <sub>FALL</sub> | True Differential I/O Standards                                                  | _    | _   | 200                 | _    | _        | 200                 | _    | _        | 200                 | ps   |

|                 |                                         | Emulated Differential I/O Standards with Three External Output Resistor Networks | _    | _   | 250                 | _    | _        | 250                 | _    | _        | 300                 | ps   |

|                 |                                         | Emulated Differential I/O Standards with One External Output Resistor Network    | _    | _   | 300                 | _    | _        | 300                 | _    | _        | 300                 | ps   |

|                 | TCCS                                    | True Differential I/O Standards                                                  | _    | _   | 200                 | _    | _        | 250                 | _    | _        | 250                 | ps   |

|                 |                                         | Emulated Differential I/O Standards with Three External Output Resistor Networks | _    | _   | 300                 | _    | _        | 300                 | _    | _        | 300                 | ps   |

|                 |                                         | Emulated Differential I/O Standards with One External Output Resistor Network    | _    | _   | 300                 | _    | _        | 300                 | _    | _        | 300                 | ps   |

| Receiver        | f <sub>HSDR</sub> (data rate)           | SERDES factor J<br>=4 to 10 <sup>(64)</sup>                                      | (65) | _   | 875 <sup>(67)</sup> | (65) | _        | 840 <sup>(67)</sup> | (65) | _        | 640 <sup>(67)</sup> | Mbps |

|                 |                                         | SERDES factor J<br>= 1 to 2, uses<br>DDR registers                               | (65) | _   | (66)                | (65) | _        | (66)                | (65) | _        | (66)                | Mbps |

| Sampling Windov | V                                       | _                                                                                | _    | _   | 350                 | _    | _        | 350                 | _    | _        | 350                 | ps   |

#### **Related Information**

Ouad SPI Flash Controller Chapter, Cyclone V Hard Processor System Technical Reference Manual Provides more information about R<sub>delay</sub>.

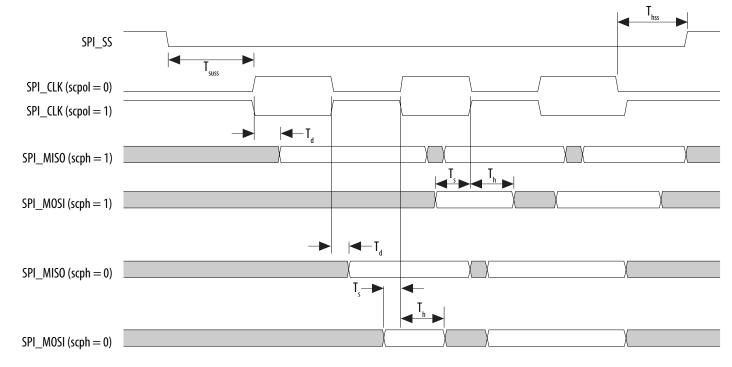

### **SPI Timing Characteristics**

#### **SPI Master Timing Requirements for Cyclone V Devices** Table 44.

The setup and hold times can be used for Texas Instruments SSP mode and National Semiconductor Microwire mode.

| Symbol                 | Description                                       | Min                  | Max | Unit |

|------------------------|---------------------------------------------------|----------------------|-----|------|

| T <sub>clk</sub>       | CLK clock period                                  | 16.67                | _   | ns   |

| T <sub>su</sub>        | SPI Master-in slave-out (MISO) setup time         | 8.35 <sup>(69)</sup> | _   | ns   |

| T <sub>h</sub>         | SPI MISO hold time                                | 1                    | _   | ns   |

| T <sub>dutycycle</sub> | SPI_CLK duty cycle                                | 45                   | 55  | %    |

| T <sub>dssfrst</sub>   | Output delay SPI_SS valid before first clock edge | 8                    | _   | ns   |

| T <sub>dsslst</sub>    | Output delay SPI_SS valid after last clock edge   | 8                    | _   | ns   |

| T <sub>dio</sub>       | Master-out slave-in (MOSI) output delay           | -1                   | 1   | ns   |

<sup>(69)</sup> This value is based on rx\_sample\_dly = 1 and spi\_m\_clk = 120 MHz. spi\_m\_clk is the internal clock that is used by SPI Master to derive it's SCLK\_OUT. These timings are based on rx\_sample\_dly of 1. This delay can be adjusted as needed to accommodate slower response times from the slave. Note that a delay of 0 is not allowed. The setup time can be used as a reference starting point. It is very crucial to do a calibration to get the correct rx\_sample\_dly value because each SPI slave device may have different output delay and each application board may have different path delay. For more information about rx sample delay, refer to the SPI Controller chapter in the Hard Processor System Technical Reference Manual.

Figure 8. SPI Slave Timing Diagram

### **Related Information**

SPI Controller, Cyclone V Hard Processor System Technical Reference Manual Provides more information about rx\_sample\_delay.

## **SD/MMC Timing Characteristics**

#### Table 46. Secure Digital (SD)/MultiMediaCard (MMC) Timing Requirements for Cyclone V Devices

After power up or cold reset, the Boot ROM uses drvsel = 3 and smplsel = 0 to execute the code. At the same time, the SD/MMC controller enters the Identification Phase followed by the Data Phase. During this time, the value of interface output clock SDMMC\_CLK\_OUT changes from a maximum of 400 kHz (Identification Phase) up to a maximum of 12.5 MHz (Data Phase), depending on the internal reference clock SDMMC\_CLK and the CSEL setting. The value of SDMMC\_CLK is based on the external oscillator frequency and has a maximum value of 50 MHz.

After the Boot ROM code exits and control is passed to the preloader, software can adjust the value of drvsel and smplsel via the system manager. drvsel can be set from 1 to 7 and smplsel can be set from 0 to 7. While the preloader is executing, the values for SDMMC\_CLK and SDMMC\_CLK\_OUT increase to a maximum of 200 MHz and 50 MHz respectively.

| Symbol                                              | Description                                      | Min                                                      | Max                                            | Unit |

|-----------------------------------------------------|--------------------------------------------------|----------------------------------------------------------|------------------------------------------------|------|

| T <sub>sdmmc_clk</sub> (internal reference clock)   | SDMMC_CLK clock period (Identification mode)     | 20                                                       | _                                              | ns   |

|                                                     | SDMMC_CLK clock period (Default speed mode)      | 5                                                        | _                                              | ns   |

|                                                     | SDMMC_CLK clock period (High speed mode)         | 5                                                        | _                                              | ns   |

| T <sub>sdmmc_clk_out</sub> (interface output clock) | SDMMC_CLK_OUT clock period (Identification mode) | 2500                                                     | _                                              | ns   |

|                                                     | SDMMC_CLK_OUT clock period (Default speed mode)  | 40                                                       | -                                              | ns   |

|                                                     | SDMMC_CLK_OUT clock period (High speed mode)     | 20                                                       | -                                              | ns   |

| T <sub>dutycycle</sub>                              | SDMMC_CLK_OUT duty cycle                         | 45                                                       | 55                                             | %    |

| T <sub>d</sub>                                      | SDMMC_CMD/SDMMC_D output delay                   | (T <sub>sdmmc_clk</sub> × drvsel)/2 - 1.23               | $(T_{sdmmc\_clk} \times drvsel)/2 + 1.69$ (70) | ns   |

| T <sub>su</sub>                                     | Input setup time                                 | $1.05 - (T_{\text{sdmmc\_clk}} \times \text{smplsel})/2$ | <del>-</del>                                   | ns   |

| T <sub>h</sub>                                      | Input hold time                                  | $(T_{sdmmc\_clk} \times smplsel)/2$ (71)                 | -                                              | ns   |

$<sup>^{(70)}</sup>$  drvsel is the drive clock phase shift select value.

<sup>(71)</sup> smplsel is the sample clock phase shift select value.

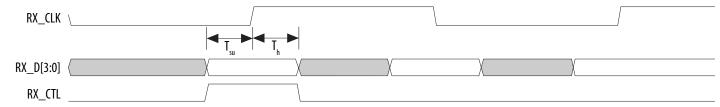

# Table 49. RGMII RX Timing Requirements for Cyclone V Devices

| Symbol                        | Description            | Min | Тур | Unit |

|-------------------------------|------------------------|-----|-----|------|

| T <sub>clk</sub> (1000Base-T) | RX_CLK clock period    | _   | 8   | ns   |

| T <sub>clk</sub> (100Base-T)  | RX_CLK clock period    | _   | 40  | ns   |

| T <sub>clk</sub> (10Base-T)   | RX_CLK clock period    | _   | 400 | ns   |

| T <sub>su</sub>               | RX_D/RX_CTL setup time | 1   | _   | ns   |

| T <sub>h</sub>                | RX_D/RX_CTL hold time  | 1   | _   | ns   |

# Figure 12. RGMII RX Timing Diagram

Table 50. Management Data Input/Output (MDIO) Timing Requirements for Cyclone V Devices

| Symbol           | Description                   | Min | Тур | Max | Unit |

|------------------|-------------------------------|-----|-----|-----|------|

| T <sub>clk</sub> | MDC clock period              | _   | 400 | _   | ns   |

| T <sub>d</sub>   | MDC to MDIO output data delay | 10  | _   | 20  | ns   |

| T <sub>s</sub>   | Setup time for MDIO data      | 10  | _   | _   | ns   |

| T <sub>h</sub>   | Hold time for MDIO data       | 0   | -   | _   | ns   |

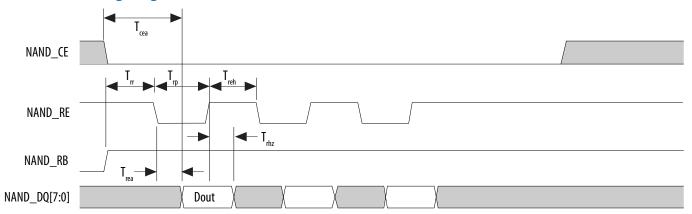

Figure 18. NAND Data Read Timing Diagram

# **Arm Trace Timing Characteristics**

## **Table 53.** Arm Trace Timing Requirements for Cyclone V Devices

Most debugging tools have a mechanism to adjust the capture point of trace data.

| Description                     | Min  | Max | Unit |

|---------------------------------|------|-----|------|

| CLK clock period                | 12.5 | _   | ns   |

| CLK maximum duty cycle          | 45   | 55  | %    |

| CLK to D0 -D7 output data delay | -1   | 1   | ns   |

## **UART Interface**

The maximum UART baud rate is 6.25 megasymbols per second.

### **GPIO Interface**

The minimum detectable general-purpose I/O (GPIO) pulse width is 2  $\mu$ s. The pulse width is based on a debounce clock frequency of 1 MHz.

# **POR Specifications**

Fast and Standard POR Delay Specification for Cyclone V Devices Table 55.

| POR Delay | Minimum | Maximum            | Unit |

|-----------|---------|--------------------|------|

| Fast      | 4       | 12 <sup>(74)</sup> | ms   |

| Standard  | 100     | 300                | ms   |

#### **Related Information**

**MSEL Pin Settings**

Provides more information about POR delay based on MSEL pin settings for each configuration scheme.

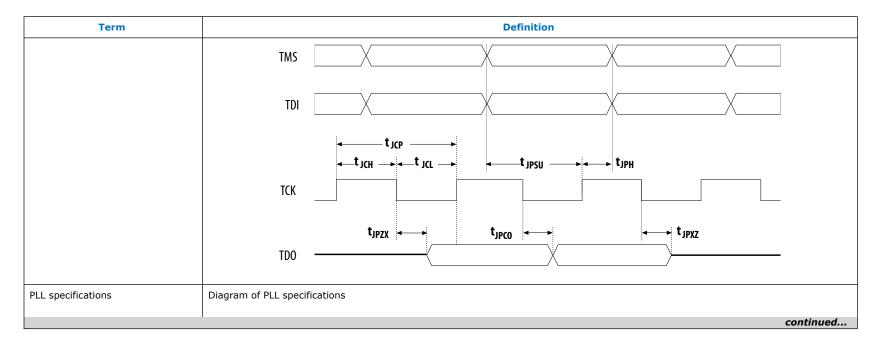

# **FPGA JTAG Configuration Timing**

**FPGA JTAG Timing Parameters and Values for Cyclone V Devices** Table 56.

| Symbol                  | Description              | Min                     | Max | Unit      |

|-------------------------|--------------------------|-------------------------|-----|-----------|

| t <sub>JCP</sub>        | TCK clock period         | 30, 167 <sup>(75)</sup> | _   | ns        |

| t <sub>JCH</sub>        | TCK clock high time      | 14                      | _   | ns        |

| t <sub>JCL</sub>        | TCK clock low time       | 14                      | _   | ns        |

| t <sub>JPSU (TDI)</sub> | TDI JTAG port setup time | 1                       | _   | ns        |

| t <sub>JPSU (TMS)</sub> | TMS JTAG port setup time | 3                       | _   | ns        |

| t <sub>JPH</sub>        | JTAG port hold time      | 5                       | _   | ns        |

|                         |                          |                         |     | continued |

<sup>(74)</sup> The maximum pulse width of the fast POR delay is 12 ms, providing enough time for the PCIe hard IP to initialize after the POR trip.

<sup>(75)</sup> The minimum TCK clock period is 167 ns if  $V_{CCBAT}$  is within the range 1.2 V – 1.5 V when you perform the volatile key programming.

| Variant      | Member Code |       | Active Seria | al (96)                            |       | Fast Passive Pa | rallel <sup>(97)</sup>          |

|--------------|-------------|-------|--------------|------------------------------------|-------|-----------------|---------------------------------|

|              |             | Width | DCLK (MHz)   | Minimum Configuration<br>Time (ms) | Width | DCLK (MHz)      | Minimum Configuration Time (ms) |

|              | A9          | 4     | 100          | 257                                | 16    | 125             | 51                              |

| Cyclone V GX | C3          | 4     | 100          | 36                                 | 16    | 125             | 7                               |

|              | C4          | 4     | 100          | 85                                 | 16    | 125             | 17                              |

|              | C5          | 4     | 100          | 85                                 | 16    | 125             | 17                              |

|              | C7          | 4     | 100          | 140                                | 16    | 125             | 28                              |

|              | C9          | 4     | 100          | 257                                | 16    | 125             | 51                              |

| Cyclone V GT | D5          | 4     | 100          | 85                                 | 16    | 125             | 17                              |

|              | D7          | 4     | 100          | 140                                | 16    | 125             | 28                              |

|              | D9          | 4     | 100          | 257                                | 16    | 125             | 51                              |

| Cyclone V SE | A2          | 4     | 100          | 85                                 | 16    | 125             | 17                              |

|              | A4          | 4     | 100          | 85                                 | 16    | 125             | 17                              |

|              | A5          | 4     | 100          | 140                                | 16    | 125             | 28                              |

|              | A6          | 4     | 100          | 140                                | 16    | 125             | 28                              |

| Cyclone V SX | C2          | 4     | 100          | 85                                 | 16    | 125             | 17                              |

|              | C4          | 4     | 100          | 85                                 | 16    | 125             | 17                              |

|              | C5          | 4     | 100          | 140                                | 16    | 125             | 28                              |

|              | C6          | 4     | 100          | 140                                | 16    | 125             | 28                              |

| Cyclone V ST | D5          | 4     | 100          | 140                                | 16    | 125             | 28                              |

|              | D6          | 4     | 100          | 140                                | 16    | 125             | 28                              |

$<sup>^{(96)}\,</sup>$  DCLK frequency of 100 MHz using external CLKUSR.

<sup>(97)</sup> Maximum FPGA FPP bandwidth may exceed bandwidth available from some external storage or control logic.

CV-51002 | 2018.05.07

#### **Related Information**

Configuration Files on page 76

# **Remote System Upgrades**

#### Table 66. Remote System Upgrade Circuitry Timing Specifications for Cyclone V Devices

| Parameter                     | Minimum | Unit |

|-------------------------------|---------|------|

| t <sub>RU_nCONFIG</sub> (98)  | 250     | ns   |

| t <sub>RU_nRSTIMER</sub> (99) | 250     | ns   |

#### **Related Information**

- Remote System Upgrade State Machine

Provides more information about configuration reset (RU\_CONFIG) signal.

- User Watchdog Timer

Provides more information about reset\_timer (RU\_nRSTIMER) signal.

# **User Watchdog Internal Oscillator Frequency Specifications**

#### Table 67. User Watchdog Internal Oscillator Frequency Specifications for Cyclone V Devices

| Parameter                                   | Minimum | Typical | Maximum | Unit |

|---------------------------------------------|---------|---------|---------|------|

| User watchdog internal oscillator frequency | 5.3     | 7.9     | 12.5    | MHz  |

# I/O Timing

Intel offers two ways to determine I/O timing—the Excel-based I/O timing and the Intel Quartus Prime Timing Analyzer.

<sup>(98)</sup> This is equivalent to strobing the reconfiguration input of the Remote Update Intel FPGA IP core high for the minimum timing specification.

<sup>(99)</sup> This is equivalent to strobing the reset timer input of the Remote Update Intel FPGA IP core high for the minimum timing specification.

Excel-based I/O timing provides pin timing performance for each device density and speed grade. The data is typically used prior to designing the FPGA to get an estimate of the timing budget as part of the link timing analysis.

The Intel Quartus Prime Timing Analyzer provides a more accurate and precise I/O timing data based on the specifics of the design after you complete place-and-route.

#### **Related Information**

Cyclone V I/O Timing Spreadsheet

Provides the Cyclone V Excel-based I/O timing spreadsheet.

# **Programmable IOE Delay**

I/O element (IOE) Programmable Delay for Cyclone V Devices Table 68.

| Parameter(100 |          |             |            |            | Slow Model |       |       |       |       | Unit |

|---------------|----------|-------------|------------|------------|------------|-------|-------|-------|-------|------|

| ,             | Settings | Offset(101) | Industrial | Commercial | -C6        | -C7   | -C8   | -17   | -A7   |      |

| D1            | 32       | 0           | 0.508      | 0.517      | 0.971      | 1.187 | 1.194 | 1.179 | 1.160 | ns   |

| D3            | 8        | 0           | 1.761      | 1.793      | 3.291      | 4.022 | 3.961 | 3.999 | 3.929 | ns   |

| D4            | 32       | 0           | 0.510      | 0.519      | 1.180      | 1.187 | 1.195 | 1.180 | 1.160 | ns   |

| D5            | 32       | 0           | 0.508      | 0.517      | 0.970      | 1.186 | 1.194 | 1.179 | 1.179 | ns   |

<sup>(100</sup> You can set this value in the Intel Quartus Prime software by selecting **D1**, **D3**, **D4**, and **D5** in the **Assignment Name** column of ) Assignment Editor.

<sup>(101</sup> Minimum offset does not include the intrinsic delay.

### Cyclone V Device Datasheet

### CV-51002 | 2018.05.07

| Term                       | Definition                                                                                                                                                            |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| t <sub>OUTP3_IO</sub>      | Period jitter on the GPIO driven by a PLL                                                                                                                             |

| t <sub>OUTPJ_DC</sub>      | Period jitter on the dedicated clock output driven by a PLL                                                                                                           |

| t <sub>RISE</sub>          | Signal low-to-high transition time (20–80%)                                                                                                                           |

| Timing Unit Interval (TUI) | The timing budget allowed for skew, propagation delays, and the data sampling window. (TUI = $1/(Receiver\ Input\ Clock\ Frequency\ Multiplication\ Factor) = t_C/w)$ |

| V <sub>CM(DC)</sub>        | DC common mode input voltage.                                                                                                                                         |

| V <sub>ICM</sub>           | Input common mode voltage—The common mode of the differential signal at the receiver.                                                                                 |

| V <sub>ID</sub>            | Input differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission at the receiver.          |

| V <sub>DIF(AC)</sub>       | AC differential input voltage—Minimum AC input differential voltage required for switching.                                                                           |

| V <sub>DIF(DC)</sub>       | DC differential input voltage— Minimum DC input differential voltage required for switching.                                                                          |

| V <sub>IH</sub>            | Voltage input high—The minimum positive voltage applied to the input which is accepted by the device as a logic high.                                                 |

| V <sub>IH(AC)</sub>        | High-level AC input voltage                                                                                                                                           |

| V <sub>IH(DC)</sub>        | High-level DC input voltage                                                                                                                                           |

| V <sub>IL</sub>            | Voltage input low—The maximum positive voltage applied to the input which is accepted by the device as a logic low.                                                   |

| V <sub>IL(AC)</sub>        | Low-level AC input voltage                                                                                                                                            |

| V <sub>IL(DC)</sub>        | Low-level DC input voltage                                                                                                                                            |

| V <sub>OCM</sub>           | Output common mode voltage—The common mode of the differential signal at the transmitter.                                                                             |

| V <sub>OD</sub>            | Output differential voltage swing—The difference in voltage between the positive and complementary conductors of a differential transmission line at the transmitter. |

| V <sub>SWING</sub>         | Differential input voltage                                                                                                                                            |

| V <sub>X</sub>             | Input differential cross point voltage                                                                                                                                |

| V <sub>OX</sub>            | Output differential cross point voltage                                                                                                                               |

| W                          | High-speed I/O block—Clock boost factor                                                                                                                               |

# **Document Revision History for Cyclone V Device Datasheet**

| Document<br>Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2018.05.07          | <ul> <li>Added description about the low-power option ("L" suffix) for Cyclone V SE and SX devices.</li> <li>Added the Cyclone V Devices Overshoot Duration diagram.</li> <li>Removed the description on SD/MMC interface calibration support in the Secure Digital (SD)/MultiMediaCard (MMC) Timing Requirements for Cyclone V Devices table. This feature is currently supported in the preloader.</li> <li>Removed the note to Cyclone V SE A2 and A4 devices, and Cyclone V SX C2 and C4 devices in the Uncompressed .rbf Sizes for Cyclone V Devices table. These devices are currently supported in the Intel Quartus Prime software.</li> <li>Removed PowerPlay text from tool name.</li> <li>Updated the IP name from ALTREMOTE_UPDATE to Remote Update Intel FPGA IP.</li> <li>Rebranded as Intel.</li> <li>Added the Low Power Variants table and the estimating power consumption steps to the "Cyclone V Device Datasheet" Overview section.</li> <li>Updated the minimum value for t<sub>DH</sub> to 2.5 for -6 speed grade/2.9 for -7 and -8 speed grade.</li> </ul> |

| Devices table.                                                                                                                                                                                                                                                                                                              | Date          | Version    | Changes                                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| - AS Timing Parameters for AS ×1 and ×4 Configurations in Cyclone V Devices - PS Timing Parameters for Cyclone V Devices  June 2016  2016.06.10  • Changed pin capacitance to maximum values. • Updated SPI Master Timing Requirements for Cyclone V Devices table Added T <sub>su</sub> and T <sub>h</sub> specifications. | December 2016 | 2016.12.09 | <ul> <li>Added maximum specification for T<sub>d</sub> in Management Data Input/Output (MDIO) Timing Requirements for Cyclone V Devices table.</li> <li>Updated T<sub>init</sub> specifications in the following tables:         <ul> <li>FPP Timing Parameters When DCLK-to-DATA[] Ratio is 1 for Cyclone V Devices</li> </ul> </li> </ul> |

| <ul> <li>Updated SPI Master Timing Requirements for Cyclone V Devices table.</li> <li>Added T<sub>su</sub> and T<sub>h</sub> specifications.</li> </ul>                                                                                                                                                                     |               |            | AS Timing Parameters for AS ×1 and ×4 Configurations in Cyclone V Devices                                                                                                                                                                                                                                                                   |

| <ul> <li>Updated SPI Master Timing Diagram.</li> <li>Updated T<sub>clk</sub> spec from maximum to minimum in I<sup>2</sup>C Timing Requirements for Cyclone V Devices table.</li> </ul>                                                                                                                                     | June 2016     | 2016.06.10 | <ul> <li>Updated SPI Master Timing Requirements for Cyclone V Devices table.</li> <li>Added T<sub>su</sub> and T<sub>h</sub> specifications.</li> <li>Removed T<sub>dinmax</sub> specifications.</li> <li>Updated SPI Master Timing Diagram.</li> </ul>                                                                                     |