# Intel - 5CSEMA5U23C8N Datasheet

Welcome to E-XFL.COM

#### Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

### What are Embedded - System On Chip (SoC)?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

| Product Status          | Active                                                                                        |

|-------------------------|-----------------------------------------------------------------------------------------------|

| Architecture            | MCU, FPGA                                                                                     |

| Core Processor          | Dual ARM <sup>®</sup> Cortex <sup>®</sup> -A9 MPCore <sup>™</sup> with CoreSight <sup>™</sup> |

| Flash Size              | -                                                                                             |

| RAM Size                | 64KB                                                                                          |

| Peripherals             | DMA, POR, WDT                                                                                 |

| Connectivity            | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, MMC/SD/SDIO, SPI, UART/USART, USB OTG            |

| Speed                   | 600MHz                                                                                        |

| Primary Attributes      | FPGA - 85K Logic Elements                                                                     |

| Operating Temperature   | 0°C ~ 85°C (TJ)                                                                               |

| Package / Case          | 672-FBGA                                                                                      |

| Supplier Device Package | 672-UBGA (23x23)                                                                              |

| Purchase URL            | https://www.e-xfl.com/product-detail/intel/5csema5u23c8n                                      |

|                         |                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Density | Ordering Part Number (OPN) | Static Power Reduction |

|---------|----------------------------|------------------------|

| 110K LE | 5CSEBA6U19I7LN             |                        |

|         | 5CSEBA6U23I7LN             |                        |

|         | 5CSXFC6C6U23I7LN           |                        |

To estimate total power consumption for a low-power device, listed in Table 1 on page 3:

- 1. Multiply the Total Static Power reported by the Early Power Estimator (EPE) by the appropriate scale factor:

- For 25K LE and 40K LE devices, use 0.7

- For 85K LE and 110K LE devices, use 0.8

- 2. Add the result from Step 1 on page 4 to the Total Dynamic Power reported by the EPE.

### **Related Information**

#### Cyclone V Device Overview

Provides more information about the densities and packages of devices in the Cyclone V family.

# **Electrical Characteristics**

The following sections describe the operating conditions and power consumption of Cyclone V devices.

# **Operating Conditions**

Cyclone V devices are rated according to a set of defined parameters. To maintain the highest possible performance and reliability of the Cyclone V devices, you must consider the operating requirements described in this section.

## **Absolute Maximum Ratings**

This section defines the maximum operating conditions for Cyclone V devices. The values are based on experiments conducted with the devices and theoretical modeling of breakdown and damage mechanisms.

The functional operation of the device is not implied for these conditions.

**Caution:** Conditions outside the range listed in the following table may cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse effects on the device.

### **Recommended Operating Conditions**

## Table 4. Recommended Operating Conditions for Cyclone V Devices

This table lists the steady-state voltage values expected from Cyclone V devices. Power supply ramps must all be strictly monotonic, without plateaus.

| Symbol                           | Description                                                                                   | Condition                                                                     | Minimum <sup>(2)</sup> | Typical | Maximum <sup>(2)</sup> | Unit      |

|----------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|------------------------|---------|------------------------|-----------|

| V <sub>CC</sub>                  | Core voltage, periphery circuitry power supply,<br>transceiver physical coding sublayer (PCS) | Devices without internal scrubbing feature                                    | 1.07                   | 1.1     | 1.13                   | V         |

|                                  | power supply, and transceiver PCI Express*<br>(PCIe*) hard IP digital power supply            | Devices with internal<br>scrubbing feature (with SC<br>suffix) <sup>(3)</sup> | 1.12                   | 1.15    | 1.18                   | V         |

| V <sub>CC_AUX</sub>              | Auxiliary supply                                                                              | _                                                                             | 2.375                  | 2.5     | 2.625                  | V         |

| V <sub>CCPD</sub> <sup>(4)</sup> | I/O pre-driver power supply                                                                   | 3.3 V                                                                         | 3.135                  | 3.3     | 3.465                  | V         |

|                                  |                                                                                               | 3.0 V                                                                         | 2.85                   | 3.0     | 3.15                   | V         |

|                                  |                                                                                               | 2.5 V                                                                         | 2.375                  | 2.5     | 2.625                  | V         |

| V <sub>CCIO</sub>                | I/O buffers power supply                                                                      | 3.3 V                                                                         | 3.135                  | 3.3     | 3.465                  | V         |

|                                  |                                                                                               | 3.0 V                                                                         | 2.85                   | 3.0     | 3.15                   | V         |

|                                  |                                                                                               | 2.5 V                                                                         | 2.375                  | 2.5     | 2.625                  | V         |

|                                  |                                                                                               | 1.8 V                                                                         | 1.71                   | 1.8     | 1.89                   | V         |

|                                  |                                                                                               | 1.5 V                                                                         | 1.425                  | 1.5     | 1.575                  | V         |

|                                  |                                                                                               | 1.35 V                                                                        | 1.283                  | 1.35    | 1.418                  | V         |

|                                  |                                                                                               | 1.25 V                                                                        | 1.19                   | 1.25    | 1.31                   | V         |

|                                  |                                                                                               | 1.2 V                                                                         | 1.14                   | 1.2     | 1.26                   | V         |

|                                  |                                                                                               |                                                                               |                        |         |                        | continued |

<sup>(2)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(3)</sup> The SEU internal scrubbing feature is available for Cyclone V E, GX, SE, and SX devices with the "SC" suffix in the part number. For device availability and ordering, contact your local Intel sales representatives.

<sup>(4)</sup>  $V_{CCPD}$  must be 2.5 V when  $V_{CCIO}$  is 2.5, 1.8, 1.5, 1.35, 1.25, or 1.2 V.  $V_{CCPD}$  must be 3.0 V when  $V_{CCIO}$  is 3.0 V.  $V_{CCPD}$  must be 3.3 V when  $V_{CCIO}$  is 3.3 V.

## I/O Pin Leakage Current

# Table 7. I/O Pin Leakage Current for Cyclone V Devices

|    | Symbol | Description        | Condition                              | Min | Тур | Max | Unit |

|----|--------|--------------------|----------------------------------------|-----|-----|-----|------|

| II |        | Input pin          | $V_{\rm I}$ = 0 V to $V_{\rm CCIOMAX}$ | -30 | —   | 30  | μA   |

| Ic | DZ     | Tri-stated I/O pin | $V_{O} = 0 V$ to $V_{CCIOMAX}$         | -30 | —   | 30  | μA   |

## **Bus Hold Specifications**

## Table 8. Bus Hold Parameters for Cyclone V Devices

| Parameter                                | Symbol            | Condition                                                   |     |         |       |       |         | V <sub>CCIC</sub> | , (V) |      |     |      |     |      | Unit |

|------------------------------------------|-------------------|-------------------------------------------------------------|-----|---------|-------|-------|---------|-------------------|-------|------|-----|------|-----|------|------|

|                                          |                   |                                                             | 1.  | 1.2 1.5 |       |       | 1.8 2.5 |                   |       | .5   | 3.0 |      | 3.3 |      |      |

|                                          |                   |                                                             | Min | Max     | Min   | Max   | Min     | Max               | Min   | Max  | Min | Max  | Min | Max  |      |

| Bus-hold, low,<br>sustaining<br>current  | I <sub>SUSL</sub> | V <sub>IN</sub> > V <sub>IL</sub><br>(max)                  | 8   | _       | 12    | _     | 30      | _                 | 50    | -    | 70  | _    | 70  | _    | μA   |

| Bus-hold, high,<br>sustaining<br>current | I <sub>SUSH</sub> | V <sub>IN</sub> < V <sub>IH</sub><br>(min)                  | -8  | _       | -12   | _     | -30     | _                 | -50   | -    | -70 | _    | -70 | _    | μA   |

| Bus-hold, low,<br>overdrive current      | I <sub>ODL</sub>  | $\begin{array}{c} 0 \ V < V_{IN} < \\ V_{CCIO} \end{array}$ | -   | 125     | _     | 175   | _       | 200               | _     | 300  | -   | 500  | _   | 500  | μA   |

| Bus-hold, high,<br>overdrive current     | I <sub>ODH</sub>  | 0 V <v<sub>IN<br/><v<sub>CCIO</v<sub></v<sub>               | _   | -125    | —     | -175  | _       | -200              | _     | -300 | _   | -500 | _   | -500 | μA   |

| Bus-hold trip<br>point                   | V <sub>TRIP</sub> | -                                                           | 0.3 | 0.9     | 0.375 | 1.125 | 0.68    | 1.07              | 0.7   | 1.7  | 0.8 | 2    | 0.8 | 2    | V    |

The bus-hold trip points are based on calculated input voltages from the JEDEC standard.

### **OCT Calibration Accuracy Specifications**

If you enable on-chip termination (OCT) calibration, calibration is automatically performed at power up for I/Os connected to the calibration block.

- $\Delta V$  is the variation of voltage with respect to the V<sub>CCIO</sub> at power up.

- dR/dT is the percentage change of R<sub>SCAL</sub> with temperature.

- dR/dV is the percentage change of  $R_{SCAL}$  with voltage.

### **OCT Variation after Power-Up Calibration**

### Table 11. OCT Variation after Power-Up Calibration for Cyclone V Devices

This table lists OCT variation with temperature and voltage after power-up calibration. The OCT variation is valid for a  $V_{CCIO}$  range of ±5% and a temperature range of 0°C to 85°C.

| Symbol | Description                                          | V <sub>CCIO</sub> (V) | Value | Unit |

|--------|------------------------------------------------------|-----------------------|-------|------|

| dR/dV  | OCT variation with voltage without recalibration     | 3.0                   | 0.100 | %/mV |

|        |                                                      | 2.5                   | 0.100 |      |

|        |                                                      | 1.8                   | 0.100 |      |

|        |                                                      | 1.5                   | 0.100 |      |

|        |                                                      | 1.35                  | 0.150 |      |

|        |                                                      | 1.25                  | 0.150 |      |

|        |                                                      | 1.2                   | 0.150 |      |

| dR/dT  | OCT variation with temperature without recalibration | 3.0                   | 0.189 | %/°C |

|        |                                                      | 2.5                   | 0.208 |      |

|        |                                                      | 1.8                   | 0.266 |      |

|        |                                                      | 1.5                   | 0.273 |      |

|        |                                                      | 1.35                  | 0.200 |      |

|        |                                                      | 1.25                  | 0.200 |      |

|        |                                                      | 1.2                   | 0.317 |      |

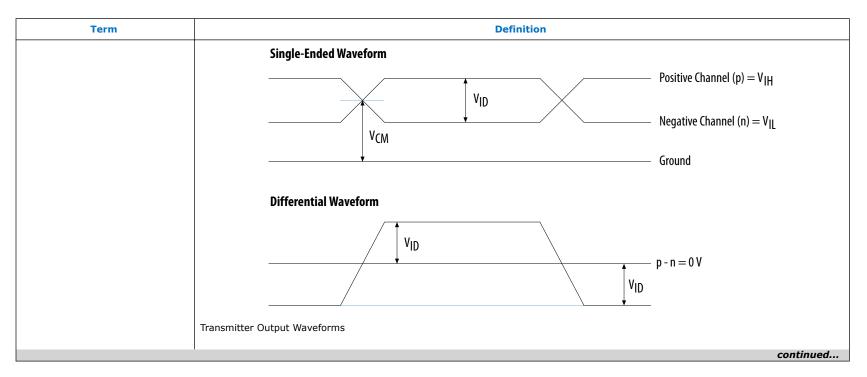

### **Differential I/O Standard Specifications**

### Table 20. Differential I/O Standard Specifications for Cyclone V Devices

Differential inputs are powered by  $V_{CCPD}$  which requires 2.5 V.

| I/O Standard                                                                                                                                                                                                                                                                       | ,     | V <sub>CCIO</sub> (V) |       | V <sub>ID</sub> (mV) <sup>(21)</sup> |                             |     | V <sub>ICM(DC)</sub> (V) |                                | V     | OD (V) <sup>(22</sup> | !)  | V <sub>OCM</sub> (V) <sup>(22)(23)</sup> |       |      |       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------|-------|--------------------------------------|-----------------------------|-----|--------------------------|--------------------------------|-------|-----------------------|-----|------------------------------------------|-------|------|-------|

|                                                                                                                                                                                                                                                                                    | Min   | Тур                   | Мах   | Min                                  | Condition                   | Мах | Min                      | Condition                      | Мах   | Min                   | Тур | Мах                                      | Min   | Тур  | Мах   |

| PCML Transmitter, receiver, and input reference clock pins of high-speed transceivers use the PCML I/O standard. For transmitter, receiver, and reference clock I/O pin specifications, refer to <i>Transceiver Specifications for Cyclone V GX, GT, SX, and ST Devices</i> table. |       |                       |       |                                      |                             |     |                          |                                |       |                       |     |                                          |       |      |       |

| 2.5 V LVDS <sup>(24)</sup>                                                                                                                                                                                                                                                         | 2.375 | 2.5                   | 2.625 | 100                                  | V <sub>CM</sub> = 1.25<br>V | _   | 0.05                     | D <sub>MAX</sub> ≤ 700<br>Mbps | 1.80  | 0.247                 | _   | 0.6                                      | 1.125 | 1.25 | 1.375 |

|                                                                                                                                                                                                                                                                                    |       |                       |       |                                      |                             |     | 1.05                     | D <sub>MAX</sub> > 700<br>Mbps | 1.55  |                       |     |                                          |       |      |       |

| BLVDS <sup>(25)(26)</sup>                                                                                                                                                                                                                                                          | 2.375 | 2.5                   | 2.625 | 100                                  | _                           | _   | -                        | _                              | _     | _                     | _   | _                                        | -     | _    | -     |

| RSDS (HIO) <sup>(27)</sup>                                                                                                                                                                                                                                                         | 2.375 | 2.5                   | 2.625 | 100                                  | V <sub>CM</sub> = 1.25<br>V | _   | 0.25                     | _                              | 1.45  | 0.1                   | 0.2 | 0.6                                      | 0.5   | 1.2  | 1.4   |

| Mini-LVDS (HIO)<br>(28)                                                                                                                                                                                                                                                            | 2.375 | 2.5                   | 2.625 | 200                                  | _                           | 600 | 0.300                    | _                              | 1.425 | 0.25                  | _   | 0.6                                      | 1     | 1.2  | 1.4   |

|                                                                                                                                                                                                                                                                                    |       |                       |       |                                      | •                           |     |                          | •                              | •     |                       | •   |                                          |       | cont | inued |

$^{(21)}$  The minimum V<sub>ID</sub> value is applicable over the entire common mode range, V<sub>CM</sub>.

<sup>(22)</sup>  $R_L$  range:  $90 \le R_L \le 110 \Omega$ .

- <sup>(23)</sup> This applies to default pre-emphasis setting only.

- (24) For optimized LVDS receiver performance, the receiver voltage input range must be within 1.0 V to 1.6 V for data rate above 700 Mbps and 0.00 V to 1.85 V for data rate below 700 Mbps.

- (25) There are no fixed V<sub>ICM</sub>, V<sub>OD</sub>, and V<sub>OCM</sub> specifications for BLVDS. They depend on the system topology.

- <sup>(26)</sup> For more information about BLVDS interface support in Intel devices, refer to AN522: Implementing Bus LVDS Interface in Supported Intel Device Families.

- <sup>(27)</sup> For optimized RSDS receiver performance, the receiver voltage input range must be within 0.25 V to 1.45 V.

- <sup>(28)</sup> For optimized mini-LVDS receiver performance, the receiver voltage input range must be within 0.300 V to 1.425 V.

| Symbol/Description                                                                 | Condition                       | Transceiv                                        | er Speed G | rade 5 <sup>(30)</sup> | Transce | iver Speed   | Grade 6 | Transce | iver Speed              | Grade 7 | Unit    |

|------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------|------------|------------------------|---------|--------------|---------|---------|-------------------------|---------|---------|

|                                                                                    |                                 | Min                                              | Тур        | Max                    | Min     | Тур          | Max     | Min     | Тур                     | Max     |         |

| Minimum differential eye opening at the receiver serial input pins <sup>(40)</sup> | -                               | 110                                              | -          | -                      | 110     | -            | -       | 110     | _                       | -       | mV      |

| Differential on-chip                                                               | 85-Ω setting                    | -                                                | 85         | -                      | -       | 85           | -       | -       | 85                      | -       | Ω       |

| termination resistors                                                              | 100-Ω setting                   | -                                                | 100        | _                      | _       | 100          | _       | -       | 100                     | _       | Ω       |

|                                                                                    | 120-Ω setting                   | -                                                | 120        | _                      | _       | 120          | -       | -       | 120                     | _       | Ω       |

|                                                                                    | 150-Ω setting                   | -                                                | 150        | _                      | _       | 150          | _       | -       | 150                     | _       | Ω       |

| $V_{\text{ICM}}$ (AC coupled)                                                      | 2.5 V PCML, LVPECL,<br>and LVDS | V <sub>CCE_GXBL</sub> supply <sup>(34)(35)</sup> |            |                        | Vo      | CCE_GXBL SUP | bly     | Vo      | <sub>CCE_GXBL</sub> sup | ply     | V       |

|                                                                                    | 1.5 V PCML                      |                                                  |            |                        | 0.6     | 55/0.75/0.8  | (41)    |         |                         |         | V       |

| t <sub>LTR</sub> <sup>(42)</sup>                                                   | _                               | -                                                | -          | 10                     | _       | _            | 10      | -       | -                       | 10      | μs      |

| t <sub>LTD</sub> <sup>(43)</sup>                                                   | -                               | -                                                | -          | 4                      | _       | -            | 4       | -       | -                       | 4       | μs      |

| t <sub>LTD_manual</sub> (44)                                                       | -                               | _                                                | _          | 4                      | _       | _            | 4       | -       | -                       | 4       | μs      |

| t <sub>LTR_LTD_manual</sub> (45)                                                   | _                               | 15                                               | -          | _                      | 15      | _            | _       | 15      | -                       | _       | μs      |

|                                                                                    |                                 |                                                  |            | •                      |         |              |         |         |                         | со      | ntinued |

- $^{(43)}$  t<sub>LTD</sub> is time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high.

- $t_{LTD\_manual}$  is the time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high when the CDR is functioning in the manual mode.

<sup>(40)</sup> The differential eye opening specification at the receiver input pins assumes that you have disabled the Receiver Equalization feature. If you enable the Receiver Equalization feature, the receiver circuitry can tolerate a lower minimum eye opening, depending on the equalization level.

<sup>&</sup>lt;sup>(41)</sup> The AC coupled  $V_{ICM}$  = 650 mV for Cyclone V GX and SX in PCIe mode only. The AC coupled  $V_{ICM}$  = 750mV for Cyclone V GT and ST in PCIe mode only.

$<sup>^{(42)}</sup>$  t<sub>LTR</sub> is the time required for the receive clock data recovery (CDR) to lock to the input reference clock frequency after coming out of reset.

#### Cyclone V Device Datasheet

CV-51002 | 2018.05.07

| Symbol/Description                          | Condition                                                            | Transceiv | er Speed G                                                                                                                                                                                                                                                         | rade 5 <sup>(30)</sup> | Transce | iver Speed | Grade 6 | Transceiver Speed Grade 7 |     |     | Unit |

|---------------------------------------------|----------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------|------------|---------|---------------------------|-----|-----|------|

|                                             |                                                                      | Min       | Тур                                                                                                                                                                                                                                                                | Max                    | Min     | Тур        | Max     | Min                       | Тур | Max |      |

| Programmable ppm detector <sup>(46)</sup>   | _                                                                    |           | ±62.5, 100, 125, 200, 250, 300, 500, and 1000                                                                                                                                                                                                                      |                        |         |            |         |                           |     | ppm |      |

| Run length                                  | _                                                                    | -         | -                                                                                                                                                                                                                                                                  | 200                    | _       | -          | 200     | -                         | -   | 200 | UI   |

| Programmable equalization<br>AC and DC gain | AC gain setting = 0<br>to 3 $^{(47)}$<br>DC gain setting = 0<br>to 1 |           | Refer to CTLE Response at Data Rates > 3.25 Gbps across Supported AC Gain and DC Gain for Cyclone V GX, GT, SX, and ST Devices and CTLE Response at Data Rates ≤ 3.25 Gbps across Supported AC Gain and DC Gain for Cyclone V GX, GT, SX, and ST Devices diagrams. |                        |         |            |         |                           |     | dB  |      |

## Table 24. Transmitter Specifications for Cyclone V GX, GT, SX, and ST Devices

| Symbol/Description            | Condition     | Transceiv | er Speed G | rade 5 <sup>(30)</sup>        | Transce | iver Speed | Grade 6 | Transce | iver Speed | Grade 7 | Unit |  |

|-------------------------------|---------------|-----------|------------|-------------------------------|---------|------------|---------|---------|------------|---------|------|--|

|                               |               | Min       | Тур        | Мах                           | Min     | Тур        | Max     | Min     | Тур        | Max     | -    |  |

| Supported I/O standards       |               |           |            |                               | 1.5 V   | PCML       | •       |         |            | ·       |      |  |

| Data rate                     | _             | 614       | -          | 5000/614<br>4 <sup>(35)</sup> | 614     | _          | 3125    | 614     | _          | 2500    | Mbps |  |

| V <sub>OCM</sub> (AC coupled) | -             | -         | 650        | -                             | _       | 650        | -       | _       | 650        | -       | mV   |  |

| Differential on-chip          | 85-Ω setting  | -         | 85         | _                             | _       | 85         | -       | _       | 85         | -       | Ω    |  |

| termination resistors         | 100-Ω setting | -         | 100        | -                             | _       | 100        | -       | _       | 100        | -       | Ω    |  |

|                               | 120-Ω setting | -         | 120        | _                             | _       | 120        | -       | _       | 120        | -       | Ω    |  |

|                               | 150-Ω setting | -         | 150        | -                             | _       | 150        | -       | _       | 150        | _       | Ω    |  |

|                               | continued     |           |            |                               |         |            |         |         |            |         |      |  |

$<sup>^{(45)}</sup>$  t<sub>LTR\_LTD\_manual</sub> is the time the receiver CDR must be kept in lock to reference (LTR) mode after the rx\_is\_lockedtoref signal goes high when the CDR is functioning in the manual mode.

<sup>&</sup>lt;sup>(46)</sup> The rate matcher supports only up to  $\pm 300$  parts per million (ppm).

<sup>(47)</sup> The Intel Quartus Prime software allows AC gain setting = 3 for design with data rate between 614 Mbps and 1.25 Gbps only.

6.144-Gbps Support Capability in Cyclone V GT Devices

Provides more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices for CPRI 6.144 Gbps.

## **Transceiver Compliance Specification**

The following table lists the physical medium attachment (PMA) specification compliance of all supported protocol for Cyclone V GX, GT, SX, and ST devices. For more information about the protocol parameter details and compliance specifications, contact your Intel Sales Representative.

### Table 29. Transceiver Compliance Specification for All Supported Protocol for Cyclone V GX, GT, SX, and ST Devices

| Protocol                             | Sub-protocol              | Data Rate (Mbps) |

|--------------------------------------|---------------------------|------------------|

| PCIe                                 | PCIe Gen1                 | 2,500            |

|                                      | PCIe Gen2 <sup>(50)</sup> | 5,000            |

|                                      | PCIe Cable                | 2,500            |

| XAUI                                 | XAUI 2135                 | 3,125            |

| Serial RapidIO <sup>®</sup> (SRIO)   | SRIO 1250 SR              | 1,250            |

|                                      | SRIO 1250 LR              | 1,250            |

|                                      | SRIO 2500 SR              | 2,500            |

|                                      | SRIO 2500 LR              | 2,500            |

|                                      | SRIO 3125 SR              | 3,125            |

|                                      | SRIO 3125 LR              | 3,125            |

|                                      | SRIO 5000 SR              | 5,000            |

|                                      | SRIO 5000 MR              | 5,000            |

|                                      | SRIO 5000 LR              | 5,000            |

| Common Public Radio Interface (CPRI) | CPRI E6LV                 | 614.4            |

|                                      | CPRI E6HV                 | 614.4            |

|                                      | CPRI E6LVII               | 614.4            |

|                                      |                           | continued        |

<sup>(50)</sup> For PCIe Gen2 sub-protocol, Intel recommends increasing the V<sub>CCE\_GXBL</sub> and V<sub>CCL\_GXBL</sub> typical value from 1.1 V to 1.2 V for Cyclone V GT and ST FPGA systems which ensure full compliance to the PCIe Gen2 transmit jitter specification. For more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices under this condition, refer to the *Transceiver Protocol Configurations in Cyclone V Devices* chapter.

### Cyclone V Device Datasheet

CV-51002 | 2018.05.07

| Memory     | Mode                                                                                                    | Resourc | es Used |     | Performance |          | Unit |

|------------|---------------------------------------------------------------------------------------------------------|---------|---------|-----|-------------|----------|------|

|            |                                                                                                         | ALUTs   | Memory  | -C6 | -C7, -I7    | -C8, -A7 |      |

|            | ROM, all supported width                                                                                | 0       | 1       | 420 | 350         | 300      | MHz  |

| M10K Block | Single-port, all supported widths                                                                       | 0       | 1       | 315 | 275         | 240      | MHz  |

|            | Simple dual-port, all supported widths                                                                  | 0       | 1       | 315 | 275         | 240      | MHz  |

|            | Simple dual-port with the <b>read-during-write</b> option set to <b>Old Data</b> , all supported widths | 0       | 1       | 275 | 240         | 180      | MHz  |

|            | True dual port, all supported widths                                                                    | 0       | 1       | 315 | 275         | 240      | MHz  |

|            | ROM, all supported widths                                                                               | 0       | 1       | 315 | 275         | 240      | MHz  |

# **Periphery Performance**

This section describes the periphery performance, high-speed I/O, and external memory interface.

Actual achievable frequency depends on design and system specific factors. Ensure proper timing closure in your design and perform HSPICE/IBIS simulations based on your specific design and system setup to determine the maximum achievable frequency in your system.

# **High-Speed I/O Specifications**

### Table 34. High-Speed I/O Specifications for Cyclone V Devices

When J = 1 or 2, bypass the serializer/deserializer (SERDES) block.

For LVDS applications, you must use the PLLs in integer PLL mode. This is achieved by using the LVDS clock network.

The Cyclone V devices support the following output standards using true LVDS output buffer types on all I/O banks.

- True RSDS output standard with data rates of up to 360 Mbps

- True mini-LVDS output standard with data rates of up to 400 Mbps

| Symbol                                                                         |                      | Condition                                     |      | - <b>C6</b> |       |      | -C7, -I7 |     | -C8, -A7 |     |      | Unit  |

|--------------------------------------------------------------------------------|----------------------|-----------------------------------------------|------|-------------|-------|------|----------|-----|----------|-----|------|-------|

|                                                                                |                      |                                               | Min  | Тур         | Max   | Min  | Тур      | Мах | Min      | Тур | Max  | ]     |

| $f_{\text{HSCLK\_in}}$ (input clock frequency) True Differential I/O Standards |                      | Clock boost<br>factor W = 1 to<br>$40^{(63)}$ | 5    | _           | 437.5 | 5    | _        | 420 | 5        | _   | 320  | MHz   |

| f <sub>HSCLK_in</sub> (input clock frequency) Single-Ended I/O<br>Standards    |                      | Clock boost<br>factor W = 1 to<br>$40^{(63)}$ | 5    | _           | 320   | 5    | _        | 320 | 5        | _   | 275  | MHz   |

| f <sub>HSCLK_OUT</sub> (outp                                                   | out clock frequency) | _                                             | 5    | _           | 420   | 5    | _        | 370 | 5        | _   | 320  | MHz   |

| Transmitter True Differential I/O Standards -<br>f <sub>HSDR</sub> (data rate) |                      | SERDES factor J<br>=4 to $10^{(64)}$          | (65) | _           | 840   | (65) | _        | 740 | (65)     | -   | 640  | Mbps  |

|                                                                                |                      |                                               |      |             |       |      |          | ,   |          |     | cont | inued |

<sup>(65)</sup> The minimum specification depends on the clock source (for example, the PLL and clock pin) and the clock routing resource (global, regional, or local) that you use. The I/O differential buffer and input register do not have a minimum toggle rate.

<sup>&</sup>lt;sup>(63)</sup> Clock boost factor (W) is the ratio between the input data rate and the input clock rate.

<sup>&</sup>lt;sup>(64)</sup> The  $F_{max}$  specification is based on the fast clock used for serial data. The interface  $F_{max}$  is also dependent on the parallel clock domain which is design dependent and requires timing analysis.

#### Cyclone V Device Datasheet

CV-51002 | 2018.05.07

| Symbol                                                                                                                                   | Condition                                               |      | - <b>C6</b> |      |      | -C7, -I7 |      |      | -C8, -A7 |      | Unit  |

|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------|-------------|------|------|----------|------|------|----------|------|-------|

|                                                                                                                                          |                                                         | Min  | Тур         | Max  | Min  | Тур      | Max  | Min  | Тур      | Max  |       |

|                                                                                                                                          | SERDES factor J<br>= 1 to 2, uses<br>DDR registers      | (65) | -           | (66) | (65) | _        | (66) | (65) | _        | (66) | Mbps  |

| Emulated Differential I/O<br>Standards with Three External<br>Output Resistor Networks- f <sub>HSDR</sub><br>(data rate) <sup>(67)</sup> | SERDES factor J<br>= 4 to 10                            | (65) | _           | 640  | (65) | _        | 640  | (65) | _        | 550  | Mbps  |

| Emulated Differential I/O<br>Standards with One External<br>Output Resistor Network - f <sub>HSDR</sub><br>(data rate)                   | SERDES factor J<br>= 4 to 10                            | (65) | _           | 170  | (65) | _        | 170  | (65) | _        | 170  | Mbps  |

| t <sub>x Jitter</sub> -True Differential I/O<br>Standards <sup>(67)</sup>                                                                | Total Jitterfor<br>Data Rate, 600<br>Mbps – 840<br>Mbps | _    | _           | 350  | _    | _        | 380  | _    | _        | 500  | ps    |

|                                                                                                                                          | Total Jitter for<br>Data Rate <<br>600Mbps              | _    | -           | 0.21 | -    | -        | 0.23 | -    | -        | 0.30 | UI    |

| t <sub>x Jitter</sub> -Emulated Differential I/O<br>Standards with Three External<br>Output Resistor Networks                            | Total Jitter for<br>Data Rate <<br>640Mbps              | _    | -           | 500  | _    | _        | 500  | _    | _        | 500  | ps    |

| t <sub>x Jitter</sub> -Emulated Differential I/O<br>Standards with One External<br>Output Resistor Network                               | Total Jitter for<br>Data Rate <<br>640Mbps              | _    | -           | 0.15 | -    | -        | 0.15 | -    | -        | 0.15 | UI    |

| τ <sub>duty</sub>                                                                                                                        | TX output clock<br>duty cycle for<br>both True and      | 45   | 50          | 55   | 45   | 50       | 55   | 45   | 50       | 55   | %     |

|                                                                                                                                          |                                                         | ·    |             |      | 1    |          | 1    | 1    | 1        | cont | inued |

<sup>(66)</sup> The maximum ideal data rate is the SERDES factor (J) × PLL max output frequency (f<sub>out</sub>), provided you can close the design timing and the signal integrity simulation is clean. You can estimate the achievable maximum data rate by performing link timing closure analysis. You must consider the board skew margin, transmitter delay margin, and receiver sampling margin to determine the maximum data rate supported.

<sup>&</sup>lt;sup>(67)</sup> You must calculate the leftover timing margin in the receiver by performing link timing closure analysis. You must consider the board skew margin, transmitter channel-to-channel skew, and receiver sampling margin to determine the leftover timing margin.

# **HPS PLL Specifications**

### **HPS PLL VCO Frequency Range**

### Table 41. HPS PLL VCO Frequency Range for Cyclone V Devices

| Description | Speed Grade        | Minimum | Maximum | Unit |

|-------------|--------------------|---------|---------|------|

| VCO range   | -C7, -I7, -A7, -C8 | 320     | 1,600   | MHz  |

|             | -C6                | 320     | 1,850   | MHz  |

### **HPS PLL Input Clock Range**

The HPS PLL input clock range is 10 – 50 MHz. This clock range applies to both HPS\_CLK1 and HPS\_CLK2 inputs.

### **Related Information**

#### Clock Select, Booting and Configuration chapter

Provides more information about the clock range for different values of clock select (CSEL).

#### **HPS PLL Input Jitter**

Use the following equation to determine the maximum input jitter (peak-to-peak) the HPS PLLs can tolerate. The divide value (N) is the value programmed into the denominator field of the VCO register for each PLL. The PLL input reference clock is divided by this value. The range of the denominator is 1 to 64.

Maximum input jitter = Input clock period  $\times$  Divide value (N)  $\times$  0.02

#### Table 42. Examples of Maximum Input Jitter

| Input Reference Clock Period | Divide Value (N) | Maximum Jitter | Unit |

|------------------------------|------------------|----------------|------|

| 40 ns                        | 1                | 0.8            | ns   |

| 40 ns                        | 2                | 1.6            | ns   |

| 40 ns                        | 4                | 3.2            | ns   |

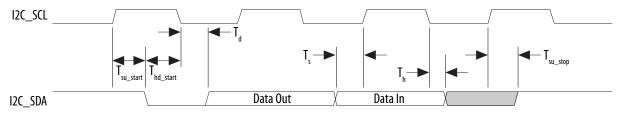

# Figure 14. I<sup>2</sup>C Timing Diagram

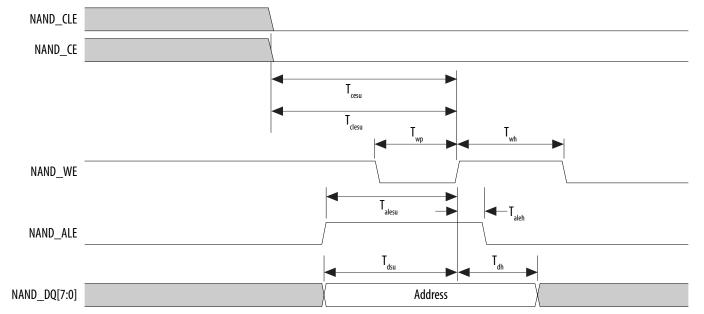

# **NAND Timing Characteristics**

### Table 52. NAND ONFI 1.0 Timing Requirements for Cyclone V Devices

The NAND controller supports Open NAND FLASH Interface (ONFI) 1.0 Mode 5 timing as well as legacy NAND devices. This table lists the requirements for ONFI 1.0 mode 5 timing. The HPS NAND controller can meet this timing by programming the C4 output of the main HPS PLL and timing registers provided in the NAND controller.

| Symbol                             | Description                                     | Min | Мах | Unit      |

|------------------------------------|-------------------------------------------------|-----|-----|-----------|

| T <sub>wp</sub> <sup>(72)</sup>    | Write enable pulse width                        | 10  | -   | ns        |

| T <sub>wh</sub> <sup>(72)</sup>    | Write enable hold time                          | 7   | -   | ns        |

| T <sub>rp</sub> <sup>(72)</sup>    | Read enable pulse width                         | 10  | -   | ns        |

| T <sub>reh</sub> (72)              | Read enable hold time                           | 7   | -   | ns        |

| T <sub>clesu</sub> <sup>(72)</sup> | Command latch enable to write enable setup time | 10  | -   | ns        |

| T <sub>cleh</sub> <sup>(72)</sup>  | Command latch enable to write enable hold time  | 5   | -   | ns        |

| T <sub>cesu</sub> (72)             | Chip enable to write enable setup time          | 15  | -   | ns        |

| T <sub>ceh</sub> <sup>(72)</sup>   | Chip enable to write enable hold time           | 5   | _   | ns        |

| T <sub>alesu</sub> <sup>(72)</sup> | Address latch enable to write enable setup time | 10  | -   | ns        |

| T <sub>aleh</sub> <sup>(72)</sup>  | Address latch enable to write enable hold time  | 5   | -   | ns        |

| T <sub>dsu</sub> <sup>(72)</sup>   | Data to write enable setup time                 | 10  | -   | ns        |

| T <sub>dh</sub> (72)               | Data to write enable hold time                  | 5   | -   | ns        |

|                                    |                                                 | 1   |     | continued |

<sup>(72)</sup> Timing of the NAND interface is controlled through the NAND configuration registers.

# Figure 16. NAND Address Latch Timing Diagram

| Symbol            | Description                              | Min | Мах                | Unit |

|-------------------|------------------------------------------|-----|--------------------|------|

| t <sub>JPCO</sub> | JTAG port clock to output                | —   | 11 <sup>(76)</sup> | ns   |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output | —   | 14 <sup>(76)</sup> | ns   |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance | _   | 14 <sup>(76)</sup> | ns   |

# **FPP Configuration Timing**

# DCLK-to-DATA[] Ratio (r) for FPP Configuration

Fast passive parallel (FPP) configuration requires a different DCLK-to-DATA[] ratio when you turn on encryption or the compression feature.

Depending on the DCLK-to-DATA[] ratio, the host must send a DCLK frequency that is r times the DATA[] rate in byte per second (Bps) or word per second (Wps). For example, in FPP ×16 where the r is 2, the DCLK frequency must be 2 times the DATA[] rate in Wps.

Cyclone V devices use additional clock cycles to decrypt and decompress the configuration data. If the DCLK-to-DATA[] ratio is greater than 1, at the end of configuration, you can only stop the DCLK (DCLK-to-DATA[] ratio – 1) clock cycles after the last data is latched into the Cyclone V device.

## Table 57. DCLK-to-DATA[] Ratio for Cyclone V Devices

| Configuration Scheme | Encryption | Compression | DCLK-to-DATA[] Ratio (r) |

|----------------------|------------|-------------|--------------------------|

| FPP (8-bit wide)     | Off        | Off         | 1                        |

|                      | On         | Off         | 1                        |

|                      | Off        | On          | 2                        |

|                      | On         | On          | 2                        |

| FPP (16-bit wide)    | Off        | Off         | 1                        |

|                      |            | •           | continued                |

<sup>(76)</sup> A 1-ns adder is required for each VCCIO voltage step down from 3.0 V. For example, tJPCO= 13 ns if VCCIO of the TDO I/O bank = 2.5 V, or 14 ns if it equals 1.8 V.

| Symbol                             | Parameter                                                 | Minimum                                                  | Maximum | Unit   |

|------------------------------------|-----------------------------------------------------------|----------------------------------------------------------|---------|--------|

| t <sub>CF2CK</sub> <sup>(83)</sup> | nCONFIG high to first rising edge on DCLK                 | 1506                                                     | -       | μs     |

| t <sub>ST2CK</sub> <sup>(83)</sup> | nSTATUS high to first rising edge of DCLK                 | 2                                                        | _       | μs     |

| t <sub>DSU</sub>                   | DATA[] setup time before rising edge on DCLK              | 5.5                                                      | —       | ns     |

| t <sub>DH</sub>                    | DATA[] hold time after rising edge on DCLK                | $N - 1/f_{\rm DCLK}^{(84)}$                              | -       | S      |

| t <sub>CH</sub>                    | DCLK high time                                            | $0.45 \times 1/f_{MAX}$                                  | —       | S      |

| t <sub>CL</sub>                    | DCLK low time                                             | $0.45 \times 1/f_{MAX}$                                  | -       | S      |

| t <sub>CLK</sub>                   | DCLK period                                               | 1/f <sub>MAX</sub>                                       | —       | S      |

| f <sub>MAX</sub>                   | DCLK frequency (FPP ×8/ ×16)                              | -                                                        | 125     | MHz    |

| t <sub>R</sub>                     | Input rise time                                           | -                                                        | 40      | ns     |

| t <sub>F</sub>                     | Input fall time                                           | -                                                        | 40      | ns     |

| t <sub>CD2UM</sub>                 | CONF_DONE high to user mode <sup>(85)</sup>               | 175                                                      | 437     | μs     |

| t <sub>CD2CU</sub>                 | CONF_DONE high to CLKUSR enabled                          | 4 × maximum DCLK period                                  | _       | _      |

| t <sub>CD2UMC</sub>                | CONF_DONE high to user mode with CLKUSR option on         | t <sub>CD2CU</sub> + (T <sub>init</sub> × CLKUSR period) | _       | _      |

| T <sub>init</sub>                  | Number of clock cycles required for device initialization | 8,576                                                    | _       | Cycles |

## **Related Information**

FPP Configuration Timing Provides the FPP configuration timing waveforms.

<sup>(85)</sup> The minimum and maximum numbers apply only if you chose the internal oscillator as the clock source for initializing the device.

<sup>&</sup>lt;sup>(82)</sup> This value can be obtained if you do not delay configuration by externally holding nSTATUS low.

<sup>&</sup>lt;sup>(83)</sup> If nSTATUS is monitored, follow the  $t_{ST2CK}$  specification. If nSTATUS is not monitored, follow the  $t_{CF2CK}$  specification.

<sup>&</sup>lt;sup>(84)</sup> N is the DCLK-to-DATA[] ratio and  $f_{DCLK}$  is the DCLK frequency of the system.

| Variant      | Member Code | Configuration .rbf Size (bits) | IOCSR .rbf Size (bits) | Recommended EPCQ Serial<br>Configuration Device <sup>(94)</sup> |

|--------------|-------------|--------------------------------|------------------------|-----------------------------------------------------------------|

|              | A4          | 33,958,560                     | 322,072                | EPCQ128                                                         |

|              | A5          | 56,057,632                     | 324,888                | EPCQ128                                                         |

|              | A6          | 56,057,632                     | 324,888                | EPCQ128                                                         |

| Cyclone V SX | C2          | 33,958,560                     | 322,072                | EPCQ128                                                         |

|              | C4          | 33,958,560                     | 322,072                | EPCQ128                                                         |

|              | C5          | 56,057,632                     | 324,888                | EPCQ128                                                         |

|              | C6          | 56,057,632                     | 324,888                | EPCQ128                                                         |

| Cyclone V ST | D5          | 56,057,632                     | 324,888                | EPCQ128                                                         |

|              | D6          | 56,057,632                     | 324,888                | EPCQ128                                                         |

# **Minimum Configuration Time Estimation**

# Table 65. Minimum Configuration Time Estimation for Cyclone V Devices

The estimated values are based on the configuration .rbf sizes in Uncompressed .rbf Sizes for Cyclone V Devices table.

| Variant     | Member Code | Active Serial <sup>(96)</sup> |            |                                    | Fast Passive Parallel <sup>(97)</sup> |            |                                    |  |

|-------------|-------------|-------------------------------|------------|------------------------------------|---------------------------------------|------------|------------------------------------|--|

|             |             | Width                         | DCLK (MHz) | Minimum Configuration<br>Time (ms) | Width                                 | DCLK (MHz) | Minimum Configuration<br>Time (ms) |  |

| Cyclone V E | A2          | 4                             | 100        | 53                                 | 16                                    | 125        | 11                                 |  |

|             | A4          | 4                             | 100        | 53                                 | 16                                    | 125        | 11                                 |  |

|             | A5          | 4                             | 100        | 85                                 | 16                                    | 125        | 17                                 |  |

|             | A7          | 4                             | 100        | 140                                | 16                                    | 125        | 28                                 |  |

|             | -           |                               | •          | •                                  |                                       | -          | continued                          |  |

<sup>(94)</sup> The recommended EPCQ serial configuration devices are able to store more than one image.

- <sup>(96)</sup> DCLK frequency of 100 MHz using external CLKUSR.

- <sup>(97)</sup> Maximum FPGA FPP bandwidth may exceed bandwidth available from some external storage or control logic.

| Variant      | Member Code |       | Active Seria | al <sup>(96)</sup>                 |       | Fast Passive Pa | rallel <sup>(97)</sup>             |

|--------------|-------------|-------|--------------|------------------------------------|-------|-----------------|------------------------------------|

|              |             | Width | DCLK (MHz)   | Minimum Configuration<br>Time (ms) | Width | DCLK (MHz)      | Minimum Configuration<br>Time (ms) |

|              | A9          | 4     | 100          | 257                                | 16    | 125             | 51                                 |

| Cyclone V GX | C3          | 4     | 100          | 36                                 | 16    | 125             | 7                                  |

|              | C4          | 4     | 100          | 85                                 | 16    | 125             | 17                                 |

|              | C5          | 4     | 100          | 85                                 | 16    | 125             | 17                                 |

|              | C7          | 4     | 100          | 140                                | 16    | 125             | 28                                 |

|              | C9          | 4     | 100          | 257                                | 16    | 125             | 51                                 |

| Cyclone V GT | D5          | 4     | 100          | 85                                 | 16    | 125             | 17                                 |

|              | D7          | 4     | 100          | 140                                | 16    | 125             | 28                                 |

|              | D9          | 4     | 100          | 257                                | 16    | 125             | 51                                 |

| Cyclone V SE | A2          | 4     | 100          | 85                                 | 16    | 125             | 17                                 |

|              | A4          | 4     | 100          | 85                                 | 16    | 125             | 17                                 |

|              | A5          | 4     | 100          | 140                                | 16    | 125             | 28                                 |

|              | A6          | 4     | 100          | 140                                | 16    | 125             | 28                                 |

| Cyclone V SX | C2          | 4     | 100          | 85                                 | 16    | 125             | 17                                 |

|              | C4          | 4     | 100          | 85                                 | 16    | 125             | 17                                 |

|              | C5          | 4     | 100          | 140                                | 16    | 125             | 28                                 |

|              | C6          | 4     | 100          | 140                                | 16    | 125             | 28                                 |

| Cyclone V ST | D5          | 4     | 100          | 140                                | 16    | 125             | 28                                 |

|              | D6          | 4     | 100          | 140                                | 16    | 125             | 28                                 |

<sup>(96)</sup> DCLK frequency of 100 MHz using external CLKUSR.

<sup>(97)</sup> Maximum FPGA FPP bandwidth may exceed bandwidth available from some external storage or control logic.