Welcome to **E-XFL.COM**

**Embedded - System On Chip (SoC):** The Heart of Modern Embedded Systems

Embedded - System On Chip (SoC) refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

What are **Embedded - System On Chip (SoC)?**

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

| Details                 |                                                                                    |

|-------------------------|------------------------------------------------------------------------------------|

| Product Status          | Active                                                                             |

| Architecture            | MCU, FPGA                                                                          |

| Core Processor          | Dual ARM® Cortex®-A9 MPCore™ with CoreSight™                                       |

| Flash Size              | -                                                                                  |

| RAM Size                | 64KB                                                                               |

| Peripherals             | DMA, POR, WDT                                                                      |

| Connectivity            | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Speed                   | 800MHz                                                                             |

| Primary Attributes      | FPGA - 110K Logic Elements                                                         |

| Operating Temperature   | -40°C ~ 100°C (TJ)                                                                 |

| Package / Case          | 672-FBGA                                                                           |

| Supplier Device Package | 672-UBGA (23x23)                                                                   |

| Purchase URL            | https://www.e-xfl.com/product-detail/intel/5csema6u23i7n                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Maximum Allowed Overshoot and Undershoot Voltage**

During transitions, input signals may overshoot to the voltage listed in the following table and undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

The maximum allowed overshoot duration is specified as a percentage of high time over the lifetime of the device. A DC signal is equivalent to 100% duty cycle.

For example, a signal that overshoots to 4.00 V can only be at 4.00 V for  $\sim 15\%$  over the lifetime of the device; for a device lifetime of 10 years, this amounts to 1.5 years.

## Table 3. Maximum Allowed Overshoot During Transitions for Cyclone V Devices

This table lists the maximum allowed input overshoot voltage and the duration of the overshoot voltage as a percentage of device lifetime.

| Symbol  | Description      | Condition (V) | Overshoot Duration as % of High Time | Unit      |

|---------|------------------|---------------|--------------------------------------|-----------|

| Vi (AC) | AC input voltage | 3.8           | 100                                  | %         |

|         |                  | 3.85          | 68                                   | %         |

|         |                  | 3.9           | 45                                   | %         |

|         |                  | 3.95          | 28                                   | %         |

|         |                  | 4             | 15                                   | %         |

|         |                  | 4.05          | 13                                   | %         |

|         |                  | 4.1           | 11                                   | %         |

|         |                  | 4.15          | 9                                    | %         |

|         |                  | 4.2           | 8                                    | %         |

|         |                  | 4.25          | 7                                    | %         |

|         |                  | 4.3           | 5.4                                  | %         |

|         |                  | 4.35          | 3.2                                  | %         |

|         |                  | 4.4           | 1.9                                  | %         |

|         |                  | 4.45          | 1.1                                  | %         |

|         | ·                |               | ·                                    | continued |

## **Transceiver Power Supply Operating Conditions**

#### Table 5. Transceiver Power Supply Operating Conditions for Cyclone V GX, GT, SX, and ST Devices

| Symbol                        | Description                                | Minimum <sup>(8)</sup> | Typical | Typical Maximum <sup>(8)</sup> |   |

|-------------------------------|--------------------------------------------|------------------------|---------|--------------------------------|---|

| V <sub>CCH_GXBL</sub>         | Transceiver high voltage power (left side) | 2.375                  | 2.5     | 2.625                          | V |

| V <sub>CCE_GXBL</sub> (9)(10) | Transmitter and receiver power (left side) | 1.07/1.17              | 1.1/1.2 | 1.13/1.23                      | V |

| V <sub>CCL_GXBL</sub> (9)(10) | Clock network power (left side)            | 1.07/1.17              | 1.1/1.2 | 1.13/1.23                      | V |

#### **Related Information**

PCIe Supported Configurations and Placement Guidelines

Provides more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices which require full compliance to the PCIe Gen2 transmit jitter specification.

• 6.144-Gbps Support Capability in Cyclone V GT Devices

Provides more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices for CPRI 6.144 Gbps.

<sup>(8)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(9)</sup> Intel recommends increasing the V<sub>CCE\_GXBL</sub> and V<sub>CCL\_GXBL</sub> typical value from 1.1 V to 1.2 V for Cyclone V GT and ST FPGA systems which require full compliance to the PCIe Gen2 transmit jitter specification. For more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices under this condition, refer to the *Transceiver Protocol Configurations in Cyclone V Devices* chapter.

<sup>(10)</sup> Intel recommends increasing the V<sub>CCE\_GXBL</sub> and V<sub>CCL\_GXBL</sub> typical value from 1.1 V to 1.2 V for full compliance to CPRI transmit jitter specification at 4.9152 Gbps (Cyclone V GT and ST devices) and 6.144Gbps (Cyclone V GT and ST devices only). For more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices for CPRI 6.144 Gbps, refer to the *Transceiver Protocol Configurations in Cyclone V Devices* chapter.

- $\Delta V$  is the variation of voltage with respect to the  $V_{CCIO}$  at power up.

- dR/dT is the percentage change of  $R_{SCAL}$  with temperature.

- $\bullet$  dR/dV is the percentage change of R<sub>SCAL</sub> with voltage.

# **OCT Variation after Power-Up Calibration**

## Table 11. OCT Variation after Power-Up Calibration for Cyclone V Devices

This table lists OCT variation with temperature and voltage after power-up calibration. The OCT variation is valid for a  $V_{\text{CCIO}}$  range of  $\pm 5\%$  and a temperature range of  $0^{\circ}\text{C}$  to  $85^{\circ}\text{C}$ .

| Symbol | Description                                          | V <sub>CCIO</sub> (V) | Value | Unit |

|--------|------------------------------------------------------|-----------------------|-------|------|

| dR/dV  | OCT variation with voltage without recalibration     | 3.0                   | 0.100 | %/mV |

|        |                                                      | 2.5                   | 0.100 |      |

|        |                                                      | 1.8                   | 0.100 |      |

|        |                                                      | 1.5                   | 0.100 |      |

|        |                                                      | 1.35                  | 0.150 |      |

|        |                                                      | 1.25                  | 0.150 |      |

|        |                                                      | 1.2                   | 0.150 |      |

| dR/dT  | OCT variation with temperature without recalibration | 3.0                   | 0.189 | %/°C |

|        |                                                      | 2.5                   | 0.208 |      |

|        |                                                      | 1.8                   | 0.266 |      |

|        |                                                      | 1.5                   | 0.273 |      |

|        |                                                      | 1.35                  | 0.200 |      |

|        |                                                      | 1.25                  | 0.200 |      |

|        |                                                      | 1.2                   | 0.317 |      |

## **Pin Capacitance**

**Table 12.** Pin Capacitance for Cyclone V Devices

| Symbol             | Description                                                      | Maximum | Unit |

|--------------------|------------------------------------------------------------------|---------|------|

| C <sub>IOTB</sub>  | Input capacitance on top and bottom I/O pins                     | 6       | pF   |

| C <sub>IOLR</sub>  | Input capacitance on left and right I/O pins                     | 6       | pF   |

| C <sub>OUTFB</sub> | Input capacitance on dual-purpose clock output and feedback pins | 6       | pF   |

## **Hot Socketing**

**Table 13.** Hot Socketing Specifications for Cyclone V Devices

| Symbol                    | Description                                     | Maximum           | Unit |

|---------------------------|-------------------------------------------------|-------------------|------|

| I <sub>IOPIN (DC)</sub>   | DC current per I/O pin                          | 300               | μΑ   |

| I <sub>IOPIN (AC)</sub>   | AC current per I/O pin                          | 8 <sup>(15)</sup> | mA   |

| I <sub>XCVR-TX</sub> (DC) | DC current per transceiver transmitter (TX) pin | 100               | mA   |

| I <sub>XCVR-RX</sub> (DC) | DC current per transceiver receiver (RX) pin    | 50                | mA   |

# **Internal Weak Pull-Up Resistor**

All I/O pins, except configuration, test, and JTAG pins, have an option to enable weak pull-up.

<sup>(15)</sup> The I/O ramp rate is 10 ns or more. For ramp rates faster than 10 ns,  $|I_{IOPIN}| = C dv/dt$ , in which C is the I/O pin capacitance and dv/dt is the slew rate.

| Symbol/Description                                                 | Condition                                          | Transceiver Speed Grade 5 <sup>(30)</sup> |     | Transce | Transceiver Speed Grade 6 |     |     | Transceiver Speed Grade 7 |     |     |    |

|--------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------|-----|---------|---------------------------|-----|-----|---------------------------|-----|-----|----|

|                                                                    |                                                    | Min                                       | Тур | Max     | Min                       | Тур | Max | Min                       | Тур | Max |    |

| Intra-differential pair skew                                       | TX V <sub>CM</sub> = 0.65 V and slew rate of 15 ps | _                                         | _   | 15      | _                         | _   | 15  | _                         | _   | 15  | ps |

| Intra-transceiver block<br>transmitter channel-to-<br>channel skew | ×6 PMA bonded<br>mode                              | _                                         | _   | 180     | _                         | _   | 180 | _                         | _   | 180 | ps |

| Inter-transceiver block<br>transmitter channel-to-<br>channel skew | ×N PMA bonded<br>mode                              | _                                         | -   | 500     | -                         | _   | 500 | -                         | -   | 500 | ps |

## Table 25. CMU PLL Specifications for Cyclone V GX, GT, SX, and ST Devices

| Symbol/Description        | Condition | Transceiv | Transceiver Speed Grade 5 <sup>(30)</sup> |                               |     | <b>Transceiver Speed Grade 6</b> |      |     | Transceiver Speed Grade 7 |      |      |  |

|---------------------------|-----------|-----------|-------------------------------------------|-------------------------------|-----|----------------------------------|------|-----|---------------------------|------|------|--|

|                           |           | Min       | Тур                                       | Max                           | Min | Тур                              | Max  | Min | Тур                       | Max  |      |  |

| Supported data range      | _         | 614       | _                                         | 5000/614<br>4 <sup>(35)</sup> | 614 | _                                | 3125 | 614 | _                         | 2500 | Mbps |  |

| fPLL supported data range | _         | 614       | -                                         | 3125                          | 614 | _                                | 3125 | 614 | _                         | 2500 | Mbps |  |

### Table 26. Transceiver-FPGA Fabric Interface Specifications for Cyclone V GX, GT, SX, and ST Devices

| Symbol/Description                      | Condition | Transceiver Speed Grade 5 <sup>(30)</sup> |     |        | Transce | <b>Transceiver Speed Grade 6</b> |        |     | Transceiver Speed Grade 7 |        |     |  |

|-----------------------------------------|-----------|-------------------------------------------|-----|--------|---------|----------------------------------|--------|-----|---------------------------|--------|-----|--|

|                                         |           | Min                                       | Тур | Max    | Min     | Тур                              | Max    | Min | Тур                       | Max    |     |  |

| Interface speed (single-<br>width mode) | _         | 25                                        | _   | 187.5  | 25      | _                                | 187.5  | 25  | _                         | 163.84 | MHz |  |

| Interface speed (double-<br>width mode) | _         | 25                                        | _   | 163.84 | 25      | _                                | 163.84 | 25  | _                         | 156.25 | MHz |  |

#### **Related Information**

- CTLE Response at Data Rates > 3.25 Gbps across Supported AC Gain and DC Gain on page 32

- CTLE Response at Data Rates ≤ 3.25 Gbps across Supported AC Gain and DC Gain on page 33

- PCIe Supported Configurations and Placement Guidelines

Provides more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices which require full compliance to the PCIe Gen2 transmit jitter specification.

# **Transceiver Compliance Specification**

The following table lists the physical medium attachment (PMA) specification compliance of all supported protocol for Cyclone V GX, GT, SX, and ST devices. For more information about the protocol parameter details and compliance specifications, contact your Intel Sales Representative.

Table 29. Transceiver Compliance Specification for All Supported Protocol for Cyclone V GX, GT, SX, and ST Devices

| Protocol                             | Sub-protocol              | Data Rate (Mbps) |

|--------------------------------------|---------------------------|------------------|

| PCIe                                 | PCIe Gen1                 | 2,500            |

|                                      | PCIe Gen2 <sup>(50)</sup> | 5,000            |

|                                      | PCIe Cable                | 2,500            |

| XAUI                                 | XAUI 2135                 | 3,125            |

| Serial RapidIO® (SRIO)               | SRIO 1250 SR              | 1,250            |

|                                      | SRIO 1250 LR              | 1,250            |

|                                      | SRIO 2500 SR              | 2,500            |

|                                      | SRIO 2500 LR              | 2,500            |

|                                      | SRIO 3125 SR              | 3,125            |

|                                      | SRIO 3125 LR              | 3,125            |

|                                      | SRIO 5000 SR              | 5,000            |

| erial RapidIO® (SRIO)                | SRIO 5000 MR              | 5,000            |

|                                      | SRIO 5000 LR              | 5,000            |

| Common Public Radio Interface (CPRI) | CPRI E6LV                 | 614.4            |

|                                      | CPRI E6HV                 | 614.4            |

|                                      | CPRI E6LVII               | 614.4            |

|                                      |                           | continued        |

<sup>(50)</sup> For PCIe Gen2 sub-protocol, Intel recommends increasing the V<sub>CCE\_GXBL</sub> and V<sub>CCL\_GXBL</sub> typical value from 1.1 V to 1.2 V for Cyclone V GT and ST FPGA systems which ensure full compliance to the PCIe Gen2 transmit jitter specification. For more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices under this condition, refer to the *Transceiver Protocol Configurations in Cyclone V Devices* chapter.

## **High-Speed I/O Specifications**

#### Table 34. High-Speed I/O Specifications for Cyclone V Devices

When J = 1 or 2, bypass the serializer/deserializer (SERDES) block.

For LVDS applications, you must use the PLLs in integer PLL mode. This is achieved by using the LVDS clock network.

The Cyclone V devices support the following output standards using true LVDS output buffer types on all I/O banks.

- True RSDS output standard with data rates of up to 360 Mbps

- True mini-LVDS output standard with data rates of up to 400 Mbps

|                                               | Symbol                                                          | Condition                                      |      | -C6 |       |      | -C7, -I7 |     |      | -C8, -A7 |      | Unit  |

|-----------------------------------------------|-----------------------------------------------------------------|------------------------------------------------|------|-----|-------|------|----------|-----|------|----------|------|-------|

|                                               |                                                                 |                                                | Min  | Тур | Max   | Min  | Тур      | Max | Min  | Тур      | Max  |       |

| f <sub>HSCLK_in</sub> (input clo<br>Standards | ck frequency) True Differential I/O                             | Clock boost factor W = 1 to 40 <sup>(63)</sup> | 5    | _   | 437.5 | 5    | _        | 420 | 5    | _        | 320  | MHz   |

| f <sub>HSCLK_in</sub> (input clo<br>Standards | ck frequency) Single-Ended I/O                                  | Clock boost factor $W = 1$ to $40^{(63)}$      | 5    | _   | 320   | 5    | _        | 320 | 5    | _        | 275  | MHz   |

| f <sub>HSCLK_OUT</sub> (output                | clock frequency)                                                | _                                              | 5    | _   | 420   | 5    | _        | 370 | 5    | _        | 320  | MHz   |

| Transmitter                                   | True Differential I/O Standards - f <sub>HSDR</sub> (data rate) | SERDES factor J<br>=4 to 10 <sup>(64)</sup>    | (65) | _   | 840   | (65) | _        | 740 | (65) | _        | 640  | Mbps  |

|                                               | ·                                                               |                                                |      | ,   | •     |      | •        | •   |      | •        | cont | inued |

<sup>(63)</sup> Clock boost factor (W) is the ratio between the input data rate and the input clock rate.

The  $F_{max}$  specification is based on the fast clock used for serial data. The interface  $F_{max}$  is also dependent on the parallel clock domain which is design dependent and requires timing analysis.

<sup>(65)</sup> The minimum specification depends on the clock source (for example, the PLL and clock pin) and the clock routing resource (global, regional, or local) that you use. The I/O differential buffer and input register do not have a minimum toggle rate.

#### Cyclone V Device Datasheet

| Symbol                                                                                                                                   | Condition                                               |      | -C6 |      |      | -C7, -I7 |      |      | -C8, -A7 |      | Unit  |

|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------|-----|------|------|----------|------|------|----------|------|-------|

|                                                                                                                                          |                                                         | Min  | Тур | Max  | Min  | Тур      | Max  | Min  | Тур      | Max  |       |

|                                                                                                                                          | SERDES factor J<br>= 1 to 2, uses<br>DDR registers      | (65) | _   | (66) | (65) | _        | (66) | (65) | _        | (66) | Mbps  |

| Emulated Differential I/O<br>Standards with Three External<br>Output Resistor Networks- f <sub>HSDR</sub><br>(data rate) <sup>(67)</sup> | SERDES factor J<br>= 4 to 10                            | (65) | _   | 640  | (65) | -        | 640  | (65) | _        | 550  | Mbps  |

| Emulated Differential I/O<br>Standards with One External<br>Output Resistor Network - f <sub>HSDR</sub><br>(data rate)                   | SERDES factor J<br>= 4 to 10                            | (65) | _   | 170  | (65) | _        | 170  | (65) | -        | 170  | Mbps  |

| t <sub>x Jitter</sub> -True Differential I/O<br>Standards <sup>(67)</sup>                                                                | Total Jitterfor<br>Data Rate, 600<br>Mbps – 840<br>Mbps | _    | _   | 350  | _    | _        | 380  | _    | _        | 500  | ps    |

|                                                                                                                                          | Total Jitter for<br>Data Rate <<br>600Mbps              | _    | _   | 0.21 | _    | _        | 0.23 | _    | _        | 0.30 | UI    |

| t <sub>x Jitter</sub> -Emulated Differential I/O<br>Standards with Three External<br>Output Resistor Networks                            | Total Jitter for<br>Data Rate <<br>640Mbps              | _    | _   | 500  | _    | _        | 500  | _    | _        | 500  | ps    |

| t <sub>x Jitter</sub> -Emulated Differential I/O<br>Standards with One External<br>Output Resistor Network                               | Total Jitter for<br>Data Rate <<br>640Mbps              | _    | _   | 0.15 | _    | _        | 0.15 | _    | _        | 0.15 | UI    |

| t <sub>DUTY</sub>                                                                                                                        | TX output clock<br>duty cycle for<br>both True and      | 45   | 50  | 55   | 45   | 50       | 55   | 45   | 50       | 55   | %     |

| <b>'</b>                                                                                                                                 |                                                         |      |     |      | ·    | 1        | 1    |      | 1        | cont | inued |

The maximum ideal data rate is the SERDES factor (J)  $\times$  PLL max output frequency ( $f_{out}$ ), provided you can close the design timing and the signal integrity simulation is clean. You can estimate the achievable maximum data rate by performing link timing closure analysis. You must consider the board skew margin, transmitter delay margin, and receiver sampling margin to determine the maximum data rate supported.

<sup>(67)</sup> You must calculate the leftover timing margin in the receiver by performing link timing closure analysis. You must consider the board skew margin, transmitter channel-to-channel skew, and receiver sampling margin to determine the leftover timing margin.

# **DLL Frequency Range Specifications**

## **Table 35.** DLL Frequency Range Specifications for Cyclone V Devices

| Parameter                     | -C6       | -C7, -I7  | -C8       | Unit |

|-------------------------------|-----------|-----------|-----------|------|

| DLL operating frequency range | 167 – 400 | 167 - 400 | 167 - 333 | MHz  |

# **DQS Logic Block Specifications**

## Table 36. DQS Phase Shift Error Specification for DLL-Delayed Clock (t<sub>DOS PSERR</sub>) for Cyclone V Devices

This error specification is the absolute maximum and minimum error.

| Number of DQS Delay Buffer | -C6 | -C7, -I7 | -C8 | Unit |

|----------------------------|-----|----------|-----|------|

| 2                          | 40  | 80       | 80  | ps   |

## **Memory Output Clock Jitter Specifications**

### Table 37. Memory Output Clock Jitter Specifications for Cyclone V Devices

The memory output clock jitter measurements are for 200 consecutive clock cycles, as specified in the JEDEC DDR2/DDR3 SDRAM standard.

The memory output clock jitter is applicable when an input jitter of 30 ps (p-p) is applied with bit error rate (BER) 10<sup>-12</sup>, equivalent to 14 sigma.

Intel recommends using the UniPHY intellectual property (IP) with PHYCLK connections for better jitter performance.

| Parameter                    | Clock Network | Symbol                | -(  | C6  | -C7, | -17 | -(  | <b>C8</b> | Unit |

|------------------------------|---------------|-----------------------|-----|-----|------|-----|-----|-----------|------|

|                              |               |                       | Min | Max | Min  | Max | Min | Max       |      |

| Clock period jitter          | PHYCLK        | t <sub>JIT(per)</sub> | -60 | 60  | -70  | 70  | -70 | 70        | ps   |

| Cycle-to-cycle period jitter | PHYCLK        | t <sub>JIT(cc)</sub>  | _   | 90  | _    | 100 | _   | 100       | ps   |

#### **Related Information**

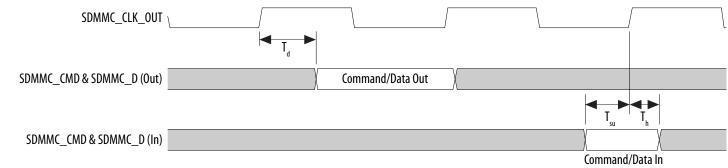

Booting and Configuration Chapter, Cyclone V Hard Processor System Technical Reference Manual Provides more information about CSEL pin settings in the SD/MMC Controller CSEL Pin Settings table.

# **USB Timing Characteristics**

PHYs that support LPM mode may not function properly with the USB controller due to a timing issue. It is recommended that designers use the MicroChip USB3300 PHY device that has been proven to be successful on the development board.

**Table 47. USB Timing Requirements for Cyclone V Devices**

| Symbol           | Description                                  | Min | Тур   | Max | Unit |

|------------------|----------------------------------------------|-----|-------|-----|------|

| T <sub>clk</sub> | USB CLK clock period                         |     | 16.67 | _   | ns   |

| T <sub>d</sub>   | CLK to USB_STP/USB_DATA[7:0] output delay    | 4.4 | _     | 11  | ns   |

| T <sub>su</sub>  | Setup time for USB_DIR/USB_NXT/USB_DATA[7:0] | 2   | _     | _   | ns   |

| T <sub>h</sub>   | Hold time for USB_DIR/USB_NXT/USB_DATA[7:0]  | 1   |       | _   | ns   |

| Symbol           | Description                        | Min | Max | Unit |

|------------------|------------------------------------|-----|-----|------|

| T <sub>cea</sub> | Chip enable to data access time    | _   | 25  | ns   |

| T <sub>rea</sub> | Read enable to data access time    | _   | 16  | ns   |

| T <sub>rhz</sub> | Read enable to data high impedance | _   | 100 | ns   |

| T <sub>rr</sub>  | Ready to read enable low           | 20  | _   | ns   |

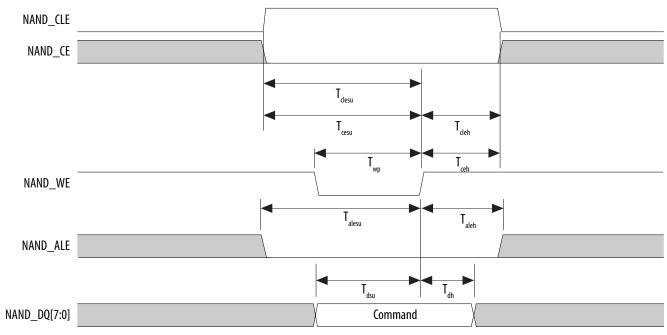

Figure 15. NAND Command Latch Timing Diagram

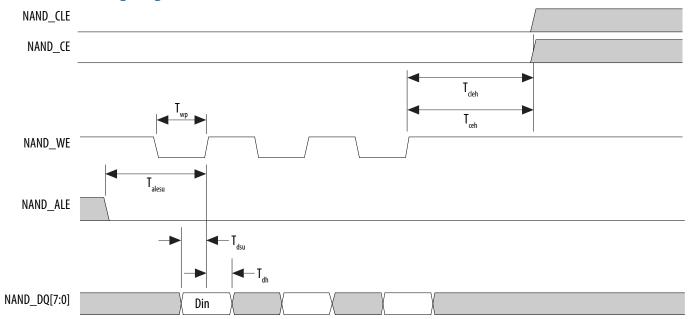

Figure 17. NAND Data Write Timing Diagram

| Symbol            | Description                              | Min | Max                | Unit |

|-------------------|------------------------------------------|-----|--------------------|------|

| t <sub>JPCO</sub> | JTAG port clock to output                | _   | 11 <sup>(76)</sup> | ns   |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output | _   | 14 <sup>(76)</sup> | ns   |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance | _   | 14 <sup>(76)</sup> | ns   |

# **FPP Configuration Timing**

# DCLK-to-DATA[] Ratio (r) for FPP Configuration

Fast passive parallel (FPP) configuration requires a different DCLK-to-DATA[] ratio when you turn on encryption or the compression feature.

Depending on the DCLK-to-DATA[] ratio, the host must send a DCLK frequency that is r times the DATA[] rate in byte per second (Bps) or word per second (Wps). For example, in FPP  $\times 16$  where the r is 2, the DCLK frequency must be 2 times the DATA[] rate in Wps.

Cyclone V devices use additional clock cycles to decrypt and decompress the configuration data. If the DCLK-to-DATA[] ratio is greater than 1, at the end of configuration, you can only stop the DCLK (DCLK-to-DATA[] ratio - 1) clock cycles after the last data is latched into the Cyclone V device.

**Table 57. DCLK-to-DATA[] Ratio for Cyclone V Devices**

| Configuration Scheme | Encryption | Compression | DCLK-to-DATA[] Ratio (r) |

|----------------------|------------|-------------|--------------------------|

| FPP (8-bit wide)     | Off        | Off         | 1                        |

|                      | On         | Off         | 1                        |

|                      | Off        | On          | 2                        |

|                      | On         | On          | 2                        |

| FPP (16-bit wide)    | Off        | Off         | 1                        |

|                      |            |             | continued                |

<sup>(76)</sup> A 1-ns adder is required for each VCCIO voltage step down from 3.0 V. For example, tJPCO= 13 ns if VCCIO of the TDO I/O bank = 2.5 V, or 14 ns if it equals 1.8 V.

| Symbol                             | Parameter                                                 | Minimum                                       | Maximum | Unit   |

|------------------------------------|-----------------------------------------------------------|-----------------------------------------------|---------|--------|

| t <sub>CF2CK</sub> <sup>(83)</sup> | nCONFIG high to first rising edge on DCLK                 | 1506                                          | _       | μs     |

| t <sub>ST2CK</sub> <sup>(83)</sup> | nSTATUS high to first rising edge of DCLK                 | 2                                             | _       | μs     |

| t <sub>DSU</sub>                   | DATA[] setup time before rising edge on DCLK              | 5.5                                           | _       | ns     |

| t <sub>DH</sub>                    | DATA[] hold time after rising edge on DCLK                | N - 1/f <sub>DCLK</sub> <sup>(84)</sup>       | _       | S      |

| t <sub>CH</sub>                    | DCLK high time                                            | 0.45 × 1/f <sub>MAX</sub>                     | _       | S      |

| t <sub>CL</sub>                    | DCLK low time                                             | 0.45 × 1/f <sub>MAX</sub>                     | _       | S      |

| t <sub>CLK</sub>                   | DCLK period                                               | 1/f <sub>MAX</sub>                            | _       | S      |

| f <sub>MAX</sub>                   | DCLK frequency (FPP ×8/ ×16)                              | _                                             | 125     | MHz    |

| t <sub>R</sub>                     | Input rise time                                           | _                                             | 40      | ns     |

| t <sub>F</sub>                     | Input fall time                                           | _                                             | 40      | ns     |

| t <sub>CD2UM</sub>                 | CONF_DONE high to user mode <sup>(85)</sup>               | 175                                           | 437     | μs     |

| t <sub>CD2CU</sub>                 | CONF_DONE high to CLKUSR enabled                          | 4 × maximum DCLK period                       | _       | _      |

| t <sub>CD2UMC</sub>                | CONF_DONE high to user mode with CLKUSR option on         | $t_{CD2CU} + (T_{init} \times CLKUSR period)$ | _       | _      |

| T <sub>init</sub>                  | Number of clock cycles required for device initialization | 8,576                                         | _       | Cycles |

#### **Related Information**

**FPP Configuration Timing**

Provides the FPP configuration timing waveforms.

<sup>(82)</sup> This value can be obtained if you do not delay configuration by externally holding nSTATUS low.

$<sup>^{(83)}</sup>$  If nSTATUS is monitored, follow the  $t_{ST2CK}$  specification. If nSTATUS is not monitored, follow the  $t_{CF2CK}$  specification.

$<sup>^{(84)}</sup>$  N is the DCLK-to-DATA[] ratio and  $f_{DCLK}$  is the DCLK frequency of the system.

<sup>(85)</sup> The minimum and maximum numbers apply only if you chose the internal oscillator as the clock source for initializing the device.

# **Active Serial (AS) Configuration Timing**

#### Table 60. AS Timing Parameters for AS ×1 and ×4 Configurations in Cyclone V Devices

The minimum and maximum numbers apply to both the internal oscillator and CLKUSR when either one is used as the clock source for device configuration.

The  $t_{CF2ST0}$ ,  $t_{CF2ST0}$ ,  $t_{CF2ST0}$ ,  $t_{CF2ST0}$ ,  $t_{CF2ST1}$  timing parameters are identical to the timing parameters for passive serial (PS) mode listed in PS Timing Parameters for Cyclone V Devices table. You can obtain the  $t_{CF2ST1}$  value if you do not delay configuration by externally holding nSTATUS low.

| Symbol                          | Parameter                                                 | Minimum                                       | Maximum | Unit   |

|---------------------------------|-----------------------------------------------------------|-----------------------------------------------|---------|--------|

| t <sub>co</sub>                 | DCLK falling edge to the AS_DATAO/ASDO output             | _                                             | 2       | ns     |

| t <sub>SU</sub>                 | Data setup time before the falling edge on DCLK           | 1.5                                           | _       | ns     |

| t <sub>DH</sub> <sup>(86)</sup> | Data hold time after the falling edge on DCLK             | 2.5 <sup>(87)</sup> /2.9 <sup>(88)</sup>      | _       | ns     |

| t <sub>CD2UM</sub>              | CONF_DONE high to user mode                               | 175                                           | 437     | μs     |

| t <sub>CD2CU</sub>              | CONF_DONE high to CLKUSR enabled                          | 4 × maximum DCLK period                       | _       | _      |

| t <sub>CD2UMC</sub>             | CONF_DONE high to user mode with CLKUSR option on         | $t_{CD2CU} + (T_{init} \times CLKUSR period)$ | _       | _      |

| T <sub>init</sub>               | Number of clock cycles required for device initialization | 8,576                                         | _       | Cycles |

#### **Related Information**

- Passive Serial (PS) Configuration Timing on page 74

- AS Configuration Timing

Provides the AS configuration timing waveform.

- AN822: Intel FPGA Configuration Device Migration Guideline

<sup>(86)</sup> Note: To evaluate the data setup (t<sub>SU</sub>) and data hold time (t<sub>DH</sub>) slack on your board in order to ensure you are meeting the t<sub>SU</sub> and t<sub>DH</sub> requirement, you are recommended to follow the guideline in the "Evaluating Data Setup and Hold Timing Slack" chapter in AN822: Intel FPGA Configuration Device Migration Guideline.

<sup>(87)</sup> Specification for -6 speed grade

<sup>(88)</sup> Specification for -7 and -8 speed grade

# **DCLK Frequency Specification in the AS Configuration Scheme**

## Table 61. DCLK Frequency Specification in the AS Configuration Scheme

This table lists the internal clock frequency specification for the AS configuration scheme. The DCLK frequency specification applies when you use the internal oscillator as the configuration clock source. The AS multi-device configuration scheme does not support DCLK frequency of 100 MHz.

| Parameter                                 | Minimum | Typical | Maximum | Unit |

|-------------------------------------------|---------|---------|---------|------|

| DCLK frequency in AS configuration scheme | 5.3     | 7.9     | 12.5    | MHz  |

|                                           | 10.6    | 15.7    | 25.0    | MHz  |

|                                           | 21.3    | 31.4    | 50.0    | MHz  |

|                                           | 42.6    | 62.9    | 100.0   | MHz  |

# **Passive Serial (PS) Configuration Timing**

### Table 62. PS Timing Parameters for Cyclone V Devices

| Symbol                             | Parameter                                    | Minimum | Maximum              | Unit      |

|------------------------------------|----------------------------------------------|---------|----------------------|-----------|

| t <sub>CF2CD</sub>                 | nCONFIG low to CONF_DONE low                 | _       | 600                  | ns        |

| t <sub>CF2ST0</sub>                | nCONFIG low to nSTATUS low                   | _       | 600                  | ns        |

| t <sub>CFG</sub>                   | nCONFIG low pulse width                      | 2       | _                    | μs        |

| t <sub>STATUS</sub>                | nstatus low pulse width                      | 268     | 1506 <sup>(89)</sup> | μs        |

| t <sub>CF2ST1</sub>                | nCONFIG high to nSTATUS high                 | _       | 1506 <sup>(90)</sup> | μs        |

| t <sub>CF2CK</sub> <sup>(91)</sup> | nCONFIG high to first rising edge on DCLK    | 1506    | _                    | μs        |

| t <sub>ST2CK</sub> <sup>(91)</sup> | nSTATUS high to first rising edge of DCLK    | 2       | _                    | μs        |

| t <sub>DSU</sub>                   | DATA[] setup time before rising edge on DCLK | 5.5     | _                    | ns        |

|                                    |                                              |         |                      | continued |

<sup>(89)</sup> You can obtain this value if you do not delay configuration by extending the nCONFIG or nSTATUS low pulse width.

$<sup>^{(90)}</sup>$  You can obtain this value if you do not delay configuration by externally holding nSTATUS low.

<sup>(91)</sup> If nSTATUS is monitored, follow the  $t_{ST2CK}$  specification. If nSTATUS is not monitored, follow the  $t_{CF2CK}$  specification.

#### Cyclone V Device Datasheet

CV-51002 | 2018.05.07

| Symbol              | Parameter                                                 | Minimum                                       | Maximum | Unit   |

|---------------------|-----------------------------------------------------------|-----------------------------------------------|---------|--------|

| t <sub>DH</sub>     | DATA[] hold time after rising edge on DCLK                | 0                                             | _       | ns     |

| t <sub>CH</sub>     | DCLK high time                                            | 0.45 × 1/f <sub>MAX</sub>                     | _       | s      |

| t <sub>CL</sub>     | DCLK low time                                             | 0.45 × 1/f <sub>MAX</sub>                     | _       | S      |

| t <sub>CLK</sub>    | DCLK period                                               | 1/f <sub>MAX</sub>                            | _       | S      |

| f <sub>MAX</sub>    | DCLK frequency                                            | _                                             | 125     | MHz    |

| t <sub>CD2UM</sub>  | CONF_DONE high to user mode <sup>(92)</sup>               | 175                                           | 437     | μs     |

| t <sub>CD2CU</sub>  | CONF_DONE high to CLKUSR enabled                          | 4 × maximum DCLK period                       | _       | _      |

| t <sub>CD2UMC</sub> | CONF_DONE high to user mode with CLKUSR option on         | $t_{CD2CU} + (T_{init} \times CLKUSR period)$ | _       | _      |

| T <sub>init</sub>   | Number of clock cycles required for device initialization | 8,576                                         | _       | Cycles |

#### **Related Information**

**PS** Configuration Timing

Provides the PS configuration timing waveform.

## **Initialization**

Table 63. Initialization Clock Source Option and the Maximum Frequency for Cyclone V Devices

| Initialization Clock Source | Configuration Scheme | Maximum Frequency (MHz) | Minimum Number of Clock Cycles |

|-----------------------------|----------------------|-------------------------|--------------------------------|

| Internal Oscillator         | AS, PS, and FPP      | 12.5                    | T <sub>init</sub>              |

| CLKUSR <sup>(93)</sup>      | PS and FPP           | 125                     |                                |

|                             | AS                   | 100                     |                                |

| DCLK                        | PS and FPP           | 125                     |                                |

<sup>(92)</sup> The minimum and maximum numbers apply only if you chose the internal oscillator as the clock source for initializing the device.

<sup>(93)</sup> To enable CLKUSR as the initialization clock source, turn on the **Enable user-supplied start-up clock (CLKUSR)** option in the Intel Quartus Prime software from the **General** panel of the **Device and Pin Options** dialog box.

| Date          | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 2015 | 2015.12.04 | <ul> <li>Updated Quad Serial Peripheral Interface (SPI) Flash Timing Requirements for Cyclone V Devices table.         <ul> <li>Updated F<sub>clk</sub>, T<sub>dutycycle</sub>, and T<sub>dssfrst</sub> specifications.</li> <li>Added T<sub>qspi_clk</sub>, T<sub>din_start</sub>, and T<sub>din_end</sub> specifications.</li> <li>Removed T<sub>dinmax</sub> specifications.</li> </ul> </li> <li>Updated the minimum specification for T<sub>clk</sub> to 16.67 ns and removed the maximum specification in SPI Master Timing Requirements for Cyclone V Devices table.</li> <li>Updated Secure Digital (SD)/MultiMediaCard (MMC) Timing Requirements for Cyclone V Devices table.</li> <li>Updated T <sub>clk</sub> to T<sub>sdmmc_clk_out</sub> symbol.</li> <li>Updated T<sub>sdmmc_clk_out</sub> and T<sub>d</sub> specifications.</li> <li>Added T<sub>sdmmc_clk</sub>, T<sub>su</sub>, and T<sub>h</sub> specifications.</li> <li>Removed T<sub>dinmax</sub> specifications.</li> <li>Updated the following diagrams:         <ul> <li>Quad SPI Flash Timing Diagram</li> <li>Updated configuration .rbf sizes for Cyclone V devices.</li> </ul> </li> <li>Changed instances of <i>Quartus II</i> to <i>Quartus Prime</i>.</li> </ul> |

| June 2015     | 2015.06.12 | <ul> <li>Updated the supported data rates for the following output standards using true LVDS output buffer types in the High-Speed I/O Specifications for Cyclone V Devices table:         <ul> <li>True RSDS output standard: data rates of up to 360 Mbps</li> <li>True mini-LVDS output standard: data rates of up to 400 Mbps</li> </ul> </li> <li>Changed Queued Serial Peripheral Interface (QSPI) to Quad Serial Peripheral Interface (SPI) Flash.</li> <li>Updated T<sub>n</sub> location in I<sup>2</sup>C Timing Diagram.</li> <li>Updated T<sub>wp</sub> location in NAND Address Latch Timing Diagram.</li> <li>Updated the maximum value for t<sub>CO</sub> from 4 ns to 2 ns in AS Timing Parameters for AS ×1 and ×4 Configurations in Cyclone V Devices table.</li> <li>Moved the following timing diagrams to the Configuration, Design Security, and Remote System Upgrades in Cyclone V Devices chapter.</li> <li>FPP Configuration Timing Waveform When DCLK-to-DATA[] Ratio is 1</li> <li>FPP Configuration Timing Waveform When DCLK-to-DATA[] Ratio is &gt;1</li> <li>AS Configuration Timing Waveform</li> <li>PS Configuration Timing Waveform</li> </ul>                                                              |

| March 2015    | 2015.03.31 | <ul> <li>Added V<sub>CC</sub> specifications for devices with internal scrubbing feature (with SC suffix) in Recommended Operating Conditions table.</li> <li>Corrected the unit for t<sub>DH</sub> from ns to s in FPP Timing Parameters When DCLK-to-DATA[] Ratio is &gt;1 for Cyclone V Devices table.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|               |            | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

## Cyclone V Device Datasheet

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                            |  |

|---------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| July 2014     | 3.9     | Added a note in Table 3, Table 4, and Table 5: The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.                                                                                                             |  |

|               |         | Added a note in Table 19: Differential inputs are powered by V <sub>CCPD</sub> which requires 2.5 V.                                                                                                                                                                                                                                                                                               |  |

|               |         | Updated "Minimum differential eye opening at the receiver serial input pins" specification in Table 20.                                                                                                                                                                                                                                                                                            |  |

|               |         | Updated h2f_user2_clk specification for -C6, -C7, and -I7 speed grades in Table 34.                                                                                                                                                                                                                                                                                                                |  |

|               |         | Updated description in "HPS PLL Specifications" section.                                                                                                                                                                                                                                                                                                                                           |  |

|               |         | Updated VCO range maximum specification in Table 35.                                                                                                                                                                                                                                                                                                                                               |  |

|               |         | ullet Updated T <sub>d</sub> and T <sub>h</sub> specifications in Table 41.                                                                                                                                                                                                                                                                                                                        |  |

|               |         | Added T <sub>h</sub> specification in Table 43 and Figure 10.                                                                                                                                                                                                                                                                                                                                      |  |

|               |         | Updated a note in Figure 17, Figure 18, and Figure 20 as follows: Do not leave DCLK floating after configuration. DCLK is ignored after configuration is complete. It can toggle high or low if required.                                                                                                                                                                                          |  |

|               |         | Removed "Remote update only in AS mode" specification in Table 54.                                                                                                                                                                                                                                                                                                                                 |  |

|               |         | Added DCLK device initialization clock source specification in Table 56.                                                                                                                                                                                                                                                                                                                           |  |

|               |         | • Added description in "Configuration Files" section: The IOCSR .rbf size is specifically for the Configuration via Protocol (CvP) feature.                                                                                                                                                                                                                                                        |  |

|               |         | Added "Recommended EPCQ Serial Configuration Device" values in Table 57.                                                                                                                                                                                                                                                                                                                           |  |

|               |         | Removed f <sub>MAX_RU_CLK</sub> specification in Table 59.                                                                                                                                                                                                                                                                                                                                         |  |

| February 2014 | 3.8     | Updated V <sub>CCRSTCLK HPS</sub> maximum specification in Table 1.                                                                                                                                                                                                                                                                                                                                |  |

|               |         | Added V <sub>CC_AUX_SHARED</sub> specification in Table 1.                                                                                                                                                                                                                                                                                                                                         |  |

| December 2013 | 3.7     | • Updated Table 1, Table 3, Table 19, Table 20, Table 23, Table 25, Table 27, Table 34, Table 44, Table 51, Table 52, Table 55, and Table 61.                                                                                                                                                                                                                                                      |  |

|               |         | • Removed Preliminary tags for Table 1, Table 2, Table 3, Table 4, Table 5, Table 6, Table 7, Table 9, Table 12, Table 13, Table 14, Table 15, Table 16, Table 17, Table 18, Table 19, Table 20, Table 24, Table 25, Table 26, Table 27, Table 28, Table 32, Table 33, Table 49, Table 50, Table 51, Table 52, Table 53, Table 54, Table 55, Table 57, Table 58, Table 59, Table 60, and Table 62. |  |

| November 2013 | 3.6     | Updated Table 23, Table 30, and Table 31.                                                                                                                                                                                                                                                                                                                                                          |  |

| October 2013  | 3.5     | Added "HPS PLL Specifications".                                                                                                                                                                                                                                                                                                                                                                    |  |

|               |         | Added Table 23, Table 35, and Table 36.                                                                                                                                                                                                                                                                                                                                                            |  |

|               |         | • Updated Table 1, Table 5, Table 11, Table 19, Table 20, Table 21, Table 22, Table 25, Table 28, Table 34, Table 37, Table 38, Table 39, Table 40, Table 41, Table 42, Table 43, Table 44, Table 45, Table 46, Table 47, and Table 53.                                                                                                                                                            |  |

|               |         | Updated Figure 1, Figure 2, Figure 4, Figure 10, Figure 12, Figure 13, and Figure 16.                                                                                                                                                                                                                                                                                                              |  |

|               |         | Removed table: GPIO Pulse Width for Cyclone V Devices.                                                                                                                                                                                                                                                                                                                                             |  |

|               |         | continued                                                                                                                                                                                                                                                                                                                                                                                          |  |