# Intel - 5CSXFC5C6U23I7N Datasheet

Welcome to E-XFL.COM

#### Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

### What are Embedded - System On Chip (SoC)?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

| Product Status          | Active                                                                             |

|-------------------------|------------------------------------------------------------------------------------|

| Architecture            | MCU, FPGA                                                                          |

| Core Processor          | Dual ARM® Cortex®-A9 MPCore <sup>™</sup> with CoreSight <sup>™</sup>               |

| Flash Size              | -                                                                                  |

| RAM Size                | 64KB                                                                               |

| Peripherals             | DMA, POR, WDT                                                                      |

| Connectivity            | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Speed                   | 800MHz                                                                             |

| Primary Attributes      | FPGA - 85K Logic Elements                                                          |

| Operating Temperature   | -40°C ~ 100°C (TJ)                                                                 |

| Package / Case          | 672-FBGA                                                                           |

| Supplier Device Package | 672-UBGA (23x23)                                                                   |

| Purchase URL            | https://www.e-xfl.com/product-detail/intel/5csxfc5c6u23i7n                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 2. **Absolute Maximum Ratings for Cyclone V Devices**

| Symbol                                    | Description                                                            | Minimum | Maximum | Unit |

|-------------------------------------------|------------------------------------------------------------------------|---------|---------|------|

| V <sub>CC</sub>                           | Core voltage and periphery circuitry power supply                      | -0.5    | 1.43    | v    |

| V <sub>CCPGM</sub>                        | Configuration pins power supply                                        | -0.5    | 3.90    | v    |

| V <sub>CC_AUX</sub>                       | Auxiliary supply                                                       | -0.5    | 3.25    | v    |

| V <sub>CCBAT</sub>                        | Battery back-up power supply for design security volatile key register | -0.5    | 3.90    | v    |

| V <sub>CCPD</sub>                         | I/O pre-driver power supply                                            | -0.5    | 3.90    | v    |

| V <sub>CCIO</sub>                         | I/O power supply                                                       | -0.5    | 3.90    | v    |

| V <sub>CCA_FPLL</sub>                     | Phase-locked loop (PLL) analog power supply                            | -0.5    | 3.25    | v    |

| V <sub>CCH_GXB</sub>                      | Transceiver high voltage power                                         | -0.5    | 3.25    | V    |

| V <sub>CCE_GXB</sub>                      | Transceiver power                                                      | -0.5    | 1.50    | V    |

| V <sub>CCL_GXB</sub>                      | Transceiver clock network power                                        | -0.5    | 1.50    | V    |

| V <sub>I</sub>                            | DC input voltage                                                       | -0.5    | 3.80    | v    |

| V <sub>CC_HPS</sub>                       | HPS core voltage and periphery circuitry power supply                  | -0.5    | 1.43    | V    |

| V <sub>CCPD_HPS</sub>                     | HPS I/O pre-driver power supply                                        | -0.5    | 3.90    | v    |

| V <sub>CCIO_HPS</sub>                     | HPS I/O power supply                                                   | -0.5    | 3.90    | V    |

| V <sub>CCRSTCLK_HPS</sub>                 | HPS reset and clock input pins power supply                            | -0.5    | 3.90    | V    |

| V <sub>CCPLL_HPS</sub>                    | HPS PLL analog power supply                                            | -0.5    | 3.25    | V    |

| V <sub>CC_AUX_SHARED</sub> <sup>(1)</sup> | HPS auxiliary power supply                                             | -0.5    | 3.25    | V    |

| I <sub>OUT</sub>                          | DC output current per pin                                              | -25     | 40      | mA   |

| Tj                                        | Operating junction temperature                                         | -55     | 125     | °C   |

| T <sub>STG</sub>                          | Storage temperature (no bias)                                          | -65     | 150     | °C   |

<sup>(1)</sup> V<sub>CC\_AUX\_SHARED</sub> must be powered by the same source as V<sub>CC\_AUX</sub> for Cyclone V SX C5, C6, D5, and D6 devices, and Cyclone V SE A5 and A6 devices.

### **Maximum Allowed Overshoot and Undershoot Voltage**

During transitions, input signals may overshoot to the voltage listed in the following table and undershoot to -2.0 V for input currents less than 100 mA and periods shorter than 20 ns.

The maximum allowed overshoot duration is specified as a percentage of high time over the lifetime of the device. A DC signal is equivalent to 100% duty cycle.

For example, a signal that overshoots to 4.00 V can only be at 4.00 V for  $\sim$ 15% over the lifetime of the device; for a device lifetime of 10 years, this amounts to 1.5 years.

#### Table 3. Maximum Allowed Overshoot During Transitions for Cyclone V Devices

| Symbol  | Description      | Condition (V) | Overshoot Duration as % of High Time | Unit      |

|---------|------------------|---------------|--------------------------------------|-----------|

| Vi (AC) | AC input voltage | 3.8           | 100                                  | %         |

|         |                  | 3.85          | 68                                   | %         |

|         |                  | 3.9           | 45                                   | %         |

|         |                  | 3.95          | 28                                   | %         |

|         |                  | 4             | 15                                   | %         |

|         |                  | 4.05          | 13                                   | %         |

|         |                  | 4.1           | 11                                   | %         |

|         |                  | 4.15          | 9                                    | %         |

|         |                  | 4.2           | 8                                    | %         |

|         |                  | 4.25          | 7                                    | %         |

|         |                  | 4.3           | 5.4                                  | %         |

|         |                  | 4.35          | 3.2                                  | %         |

|         |                  | 4.4           | 1.9                                  | %         |

|         |                  | 4.45          | 1.1                                  | %         |

|         | 1                |               |                                      | continued |

This table lists the maximum allowed input overshoot voltage and the duration of the overshoot voltage as a percentage of device lifetime.

| Symbol                                     | Description                                   | Condition | Minimum <sup>(11)</sup> | Typical | Maximum <sup>(11)</sup> | Unit |

|--------------------------------------------|-----------------------------------------------|-----------|-------------------------|---------|-------------------------|------|

|                                            |                                               | 1.8 V     | 1.71                    | 1.8     | 1.89                    | V    |

| V <sub>CCPLL_HPS</sub>                     | HPS PLL analog voltage regulator power supply | —         | 2.375                   | 2.5     | 2.625                   | V    |

| V <sub>CC_AUX_SHARED</sub> <sup>(14)</sup> | HPS auxiliary power supply                    | _         | 2.375                   | 2.5     | 2.625                   | V    |

### **Related Information**

Recommended Operating Conditions on page 8 Provides the steady-state voltage values for the FPGA portion of the device.

# **DC Characteristics**

#### **Supply Current and Power Consumption**

Intel offers two ways to estimate power for your design—the Excel-based EPE and the Intel<sup>®</sup> Quartus<sup>®</sup> Prime Power Analyzer feature.

Use the Excel-based EPE before you start your design to estimate the supply current for your design. The EPE provides a magnitude estimate of the device power because these currents vary greatly with the resources you use.

The Intel Quartus Prime Power Analyzer provides better quality estimates based on the specifics of the design after you complete place-and-route. The Power Analyzer can apply a combination of user-entered, simulation-derived, and estimated signal activities that, when combined with detailed circuit models, yields very accurate power estimates.

#### **Related Information**

- Early Power Estimator User Guide Provides more information about power estimation tools.

- Power Analysis chapter, Intel Quartus Prime Handbook Provides more information about power estimation tools.

<sup>&</sup>lt;sup>(11)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(14)</sup> V<sub>CC\_AUX\_SHARED</sub> must be powered by the same source as V<sub>CC\_AUX</sub> for Cyclone V SX C5, C6, D5, and D6 devices, and Cyclone V SE A5 and A6 devices.

| I/O Standard            |       | V <sub>CCIO</sub> (V) |       |                          | V <sub>REF</sub> (V)  |                        |                          | V <sub>TT</sub> (V)   |                        |

|-------------------------|-------|-----------------------|-------|--------------------------|-----------------------|------------------------|--------------------------|-----------------------|------------------------|

|                         | Min   | Тур                   | Мах   | Min                      | Тур                   | Max                    | Min                      | Тур                   | Max                    |

| SSTL-15 Class I,<br>II  | 1.425 | 1.5                   | 1.575 | 0.49 × V <sub>CCIO</sub> | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ | $0.49 \times V_{CCIO}$   | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ |

| SSTL-135 Class<br>I, II | 1.283 | 1.35                  | 1.418 | 0.49 × V <sub>CCIO</sub> | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ | $0.49 \times V_{CCIO}$   | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ |

| SSTL-125 Class<br>I, II | 1.19  | 1.25                  | 1.26  | 0.49 × V <sub>CCIO</sub> | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ | 0.49 × V <sub>CCIO</sub> | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ |

| HSTL-18 Class I,<br>II  | 1.71  | 1.8                   | 1.89  | 0.85                     | 0.9                   | 0.95                   | _                        | V <sub>CCIO</sub> /2  | _                      |

| HSTL-15 Class I,<br>II  | 1.425 | 1.5                   | 1.575 | 0.68                     | 0.75                  | 0.9                    | _                        | V <sub>CCIO</sub> /2  | _                      |

| HSTL-12 Class I,<br>II  | 1.14  | 1.2                   | 1.26  | $0.47 \times V_{CCIO}$   | $0.5 \times V_{CCIO}$ | $0.53 \times V_{CCIO}$ | -                        | V <sub>CCIO</sub> /2  | _                      |

| HSUL-12                 | 1.14  | 1.2                   | 1.3   | $0.49 \times V_{CCIO}$   | $0.5 \times V_{CCIO}$ | $0.51 \times V_{CCIO}$ | _                        | -                     | _                      |

# Single-Ended SSTL, HSTL, and HSUL I/O Standards Signal Specifications

### Table 17. Single-Ended SSTL, HSTL, and HSUL I/O Standards Signal Specifications for Cyclone V Devices

| I/O Standard        | VIL  | (DC) <b>(V)</b>          | V <sub>IH(DC</sub>       | c) <b>(V)</b>           | V <sub>IL(AC)</sub> (V) | V <sub>IH(AC)</sub> (V) | V <sub>OL</sub> (V)     | V <sub>он</sub> (V)      | I <sub>OL</sub> <sup>(19)</sup> | I <sub>OH</sub> <sup>(19)</sup> |

|---------------------|------|--------------------------|--------------------------|-------------------------|-------------------------|-------------------------|-------------------------|--------------------------|---------------------------------|---------------------------------|

|                     | Min  | Max                      | Min                      | Max                     | Max                     | Min                     | Max                     | Min                      | (mA)                            | (mA)                            |

| SSTL-2 Class I      | -0.3 | V <sub>REF</sub> - 0.15  | $V_{REF} + 0.15$         | $V_{CCIO} + 0.3$        | V <sub>REF</sub> - 0.31 | V <sub>REF</sub> + 0.31 | V <sub>TT</sub> - 0.608 | V <sub>TT</sub> + 0.608  | 8.1                             | -8.1                            |

| SSTL-2 Class<br>II  | -0.3 | V <sub>REF</sub> - 0.15  | V <sub>REF</sub> + 0.15  | V <sub>CCI0</sub> + 0.3 | V <sub>REF</sub> - 0.31 | V <sub>REF</sub> + 0.31 | V <sub>TT</sub> - 0.81  | V <sub>TT</sub> + 0.81   | 16.2                            | -16.2                           |

| SSTL-18 Class<br>I  | -0.3 | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 | V <sub>CCI0</sub> + 0.3 | V <sub>REF</sub> – 0.25 | V <sub>REF</sub> + 0.25 | V <sub>TT</sub> – 0.603 | V <sub>TT</sub> + 0.603  | 6.7                             | -6.7                            |

| SSTL-18 Class<br>II | -0.3 | V <sub>REF</sub> - 0.125 | V <sub>REF</sub> + 0.125 | V <sub>CCI0</sub> + 0.3 | V <sub>REF</sub> - 0.25 | V <sub>REF</sub> + 0.25 | 0.28                    | V <sub>CCIO</sub> – 0.28 | 13.4                            | -13.4                           |

|                     | •    | •                        |                          |                         |                         |                         |                         |                          | со                              | ntinued                         |

<sup>&</sup>lt;sup>(19)</sup> To meet the  $I_{OL}$  and  $I_{OH}$  specifications, you must set the current strength settings accordingly. For example, to meet the SSTL15CI specification (8 mA), you should set the current strength settings to 8 mA. Setting at lower current strength may not meet the  $I_{OL}$  and  $I_{OH}$  specifications in the datasheet.

#### **Differential I/O Standard Specifications**

#### Table 20. Differential I/O Standard Specifications for Cyclone V Devices

Differential inputs are powered by  $V_{CCPD}$  which requires 2.5 V.

| I/O Standard               | ,         | V <sub>CCIO</sub> (V) |       |     | V <sub>ID</sub> (mV) <sup>(21)</sup> |     |       | V <sub>ICM(DC)</sub> (V)       |       | V     | OD (V) <sup>(22</sup> | !)  | V <sub>OCM</sub> (V) <sup>(22)(23)</sup> |            |          |

|----------------------------|-----------|-----------------------|-------|-----|--------------------------------------|-----|-------|--------------------------------|-------|-------|-----------------------|-----|------------------------------------------|------------|----------|

|                            | Min       | Тур                   | Мах   | Min | Condition                            | Мах | Min   | Condition                      | Мах   | Min   | Тур                   | Мах | Min                                      | Тур        | Мах      |

| PCML                       | Transm    | itter, rece           |       |     | ence clock pins<br>fications, refer  |     |       |                                |       |       |                       |     |                                          | nd referen | ce clock |

| 2.5 V LVDS <sup>(24)</sup> | 2.375     | 2.5                   | 2.625 | 100 | V <sub>CM</sub> = 1.25<br>V          | _   | 0.05  | D <sub>MAX</sub> ≤ 700<br>Mbps | 1.80  | 0.247 | _                     | 0.6 | 1.125                                    | 1.25       | 1.375    |

|                            |           |                       |       |     |                                      |     | 1.05  | D <sub>MAX</sub> > 700<br>Mbps | 1.55  |       |                       |     |                                          |            |          |

| BLVDS <sup>(25)(26)</sup>  | 2.375     | 2.5                   | 2.625 | 100 | _                                    | _   | -     | -                              | _     | _     | _                     | _   | -                                        | _          | -        |

| RSDS (HIO) <sup>(27)</sup> | 2.375     | 2.5                   | 2.625 | 100 | V <sub>CM</sub> = 1.25<br>V          | _   | 0.25  | _                              | 1.45  | 0.1   | 0.2                   | 0.6 | 0.5                                      | 1.2        | 1.4      |

| Mini-LVDS (HIO)<br>(28)    | 2.375     | 2.5                   | 2.625 | 200 | _                                    | 600 | 0.300 | _                              | 1.425 | 0.25  | _                     | 0.6 | 1                                        | 1.2        | 1.4      |

|                            | continued |                       |       |     |                                      |     |       |                                |       |       |                       |     |                                          |            |          |

$^{(21)}$  The minimum V<sub>ID</sub> value is applicable over the entire common mode range, V<sub>CM</sub>.

<sup>(22)</sup>  $R_L$  range:  $90 \le R_L \le 110 \Omega$ .

- <sup>(23)</sup> This applies to default pre-emphasis setting only.

- (24) For optimized LVDS receiver performance, the receiver voltage input range must be within 1.0 V to 1.6 V for data rate above 700 Mbps and 0.00 V to 1.85 V for data rate below 700 Mbps.

- (25) There are no fixed V<sub>ICM</sub>, V<sub>OD</sub>, and V<sub>OCM</sub> specifications for BLVDS. They depend on the system topology.

- <sup>(26)</sup> For more information about BLVDS interface support in Intel devices, refer to AN522: Implementing Bus LVDS Interface in Supported Intel Device Families.

- <sup>(27)</sup> For optimized RSDS receiver performance, the receiver voltage input range must be within 0.25 V to 1.45 V.

- <sup>(28)</sup> For optimized mini-LVDS receiver performance, the receiver voltage input range must be within 0.300 V to 1.425 V.

| I/O Standard           | ,     | V <sub>CCIO</sub> (V) |       |     | V <sub>ID</sub> (mV) <sup>(21)</sup> |     |      | V <sub>ICM(DC)</sub> (V)       |      | V   | <sup>/</sup> OD (V) <sup>(22</sup> | 2)  | V <sub>OCM</sub> (V) <sup>(22)(23)</sup> |     |     |

|------------------------|-------|-----------------------|-------|-----|--------------------------------------|-----|------|--------------------------------|------|-----|------------------------------------|-----|------------------------------------------|-----|-----|

|                        | Min   | Тур                   | Мах   | Min | Condition                            | Мах | Min  | Condition                      | Мах  | Min | Тур                                | Max | Min                                      | Тур | Max |

| LVPECL <sup>(29)</sup> | -     | -                     | _     | 300 | -                                    | -   | 0.60 | D <sub>MAX</sub> ≤ 700<br>Mbps | 1.80 | -   | -                                  | -   | -                                        | -   | -   |

|                        |       |                       |       |     |                                      |     | 1.00 | D <sub>MAX</sub> > 700<br>Mbps | 1.60 |     |                                    |     |                                          |     |     |

| SLVS                   | 2.375 | 2.5                   | 2.625 | 100 | V <sub>CM</sub> = 1.25<br>V          | _   | 0.05 | _                              | 1.80 | _   | _                                  | -   | -                                        | -   | -   |

| Sub-LVDS               | 2.375 | 2.5                   | 2.625 | 100 | V <sub>CM</sub> = 1.25<br>V          | _   | 0.05 | -                              | 1.80 | _   | _                                  | -   | -                                        | -   | -   |

| НіЅрі                  | 2.375 | 2.5                   | 2.625 | 100 | V <sub>CM</sub> = 1.25<br>V          | _   | 0.05 | _                              | 1.80 | _   | _                                  | -   | -                                        | -   | -   |

### **Related Information**

- AN522: Implementing Bus LVDS Interface in Supported Intel Device Families Provides more information about BLVDS interface support in Intel devices.

- Transceiver Specifications for Cyclone V GX, GT, SX, and ST Devices on page 25 Provides the specifications for transmitter, receiver, and reference clock I/O pin.

# **Switching Characteristics**

This section provides performance characteristics of Cyclone V core and periphery blocks.

(29) For optimized LVPECL receiver performance, the receiver voltage input range must be within 0.85 V to 1.75 V for data rate above 700 Mbps and 0.45 V to 1.95 V for data rate below 700 Mbps.

$<sup>^{(21)}</sup>$  The minimum V<sub>ID</sub> value is applicable over the entire common mode range, V<sub>CM</sub>.

<sup>(22)</sup>  $R_L$  range: 90 ≤  $R_L$  ≤ 110 Ω.

<sup>&</sup>lt;sup>(23)</sup> This applies to default pre-emphasis setting only.

# **Transceiver Performance Specifications**

# Transceiver Specifications for Cyclone V GX, GT, SX, and ST Devices

# Table 21. Reference Clock Specifications for Cyclone V GX, GT, SX, and ST Devices

| Symbol/Description                                        | Condition                                                | Transceiv | er Speed G     | rade 5 <sup>(30)</sup> | Transce     | iver Speed     | Grade 6                   | Transce     | iver Speed     | Grade 7 | Unit    |

|-----------------------------------------------------------|----------------------------------------------------------|-----------|----------------|------------------------|-------------|----------------|---------------------------|-------------|----------------|---------|---------|

|                                                           |                                                          | Min       | Тур            | Max                    | Min         | Тур            | Мах                       | Min         | Тур            | Max     |         |

| Supported I/O standards                                   |                                                          | 1.2       | 2 V PCML, 1.   | 5 V PCML, 2.           | 5 V PCML, I | Differential L | VPECL <sup>(31)</sup> , H | CSL, and LV | DS             | •       |         |

| Input frequency from<br>REFCLK input pins <sup>(32)</sup> | _                                                        | 27        | -              | 550                    | 27          | -              | 550                       | 27          | -              | 550     | MHz     |

| Rise time                                                 | Measure at ±60 mV of differential signal <sup>(33)</sup> | _         | -              | 400                    | _           | -              | 400                       | -           | -              | 400     | ps      |

| Fall time                                                 | Measure at ±60 mV of differential signal <sup>(33)</sup> | _         | -              | 400                    | _           | -              | 400                       | -           | -              | 400     | ps      |

| Duty cycle                                                | -                                                        | 45        | -              | 55                     | 45          | -              | 55                        | 45          | -              | 55      | %       |

| Peak-to-peak differential input voltage                   | _                                                        | 200       | -              | 2000                   | 200         | -              | 2000                      | 200         | -              | 2000    | mV      |

| Spread-spectrum<br>modulating clock frequency             | PCIe                                                     | 30        | -              | 33                     | 30          | -              | 33                        | 30          | -              | 33      | kHz     |

| Spread-spectrum<br>downspread                             | PCIe                                                     | -         | 0 to -<br>0.5% | -                      | _           | 0 to -<br>0.5% | -                         | -           | 0 to -<br>0.5% | -       | -       |

| On-chip termination resistors                             | _                                                        | -         | 100            | —                      | _           | 100            | -                         | -           | 100            | -       | Ω       |

|                                                           | 1                                                        | 1         | 1              | 1                      |             |                |                           | 1           | 1              | CO      | ntinued |

<sup>(30)</sup> Transceiver Speed Grade 5 covers specifications for Cyclone V GT and ST devices.

<sup>(31)</sup> Differential LVPECL signal levels must comply to the minimum and maximum peak-to-peak differential input voltage specified in this table.

(32) The reference clock frequency must be ≥ 307.2 MHz to be fully compliance to CPRI transmit jitter specification at 6.144 Gbps. For more information about CPRI 6.144 Gbps, refer to the *Transceiver Protocol Configurations in Cyclone V Devices* chapter.

<sup>(33)</sup> REFCLK performance requires to meet transmitter REFCLK phase noise specification.

| Symbol/Description                                                 | Condition                                          | Transceiver Speed Grade 5 <sup>(30)</sup> |     |     | Transce | iver Speed | Grade 6 | Transce | Unit |     |    |

|--------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------|-----|-----|---------|------------|---------|---------|------|-----|----|

|                                                                    |                                                    | Min                                       | Тур | Max | Min     | Тур        | Max     | Min     | Тур  | Max |    |

| Intra-differential pair skew                                       | TX V <sub>CM</sub> = 0.65 V and slew rate of 15 ps | -                                         | _   | 15  | _       | _          | 15      | _       | _    | 15  | ps |

| Intra-transceiver block<br>transmitter channel-to-<br>channel skew | ×6 PMA bonded<br>mode                              | -                                         | -   | 180 | -       | -          | 180     | -       | -    | 180 | ps |

| Inter-transceiver block<br>transmitter channel-to-<br>channel skew | ×N PMA bonded<br>mode                              | -                                         | _   | 500 | _       | -          | 500     | -       | —    | 500 | ps |

### Table 25. CMU PLL Specifications for Cyclone V GX, GT, SX, and ST Devices

| Symbol/Description        | Condition | Transceiv | er Speed G | rade 5 <sup>(30)</sup>        | Transce | iver Speed | Grade 6 | Transce | Grade 7 | Unit |      |

|---------------------------|-----------|-----------|------------|-------------------------------|---------|------------|---------|---------|---------|------|------|

|                           |           | Min       | Тур        | Max                           | Min     | Тур        | Max     | Min     | Тур     | Max  |      |

| Supported data range      | _         | 614       | _          | 5000/614<br>4 <sup>(35)</sup> | 614     | _          | 3125    | 614     | _       | 2500 | Mbps |

| fPLL supported data range | _         | 614       | —          | 3125                          | 614     | —          | 3125    | 614     | _       | 2500 | Mbps |

### Table 26. Transceiver-FPGA Fabric Interface Specifications for Cyclone V GX, GT, SX, and ST Devices

| Symbol/Description                      | Condition | Transceiv | er Speed G | r <b>ade 5</b> (30) | Transce | iver Speed | Grade 6 | Transce | Unit |        |     |

|-----------------------------------------|-----------|-----------|------------|---------------------|---------|------------|---------|---------|------|--------|-----|

|                                         |           | Min       | Тур        | Max                 | Min     | Тур        | Max     | Min     | Тур  | Мах    |     |

| Interface speed (single-<br>width mode) | _         | 25        | _          | 187.5               | 25      | _          | 187.5   | 25      | -    | 163.84 | MHz |

| Interface speed (double-<br>width mode) | _         | 25        | _          | 163.84              | 25      | _          | 163.84  | 25      | _    | 156.25 | MHz |

#### **Related Information**

- CTLE Response at Data Rates > 3.25 Gbps across Supported AC Gain and DC Gain on page 32

- CTLE Response at Data Rates  $\leq$  3.25 Gbps across Supported AC Gain and DC Gain on page 33

- PCIe Supported Configurations and Placement Guidelines

Provides more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices

which require full compliance to the PCIe Gen2 transmit jitter specification.

### **Transceiver Compliance Specification**

The following table lists the physical medium attachment (PMA) specification compliance of all supported protocol for Cyclone V GX, GT, SX, and ST devices. For more information about the protocol parameter details and compliance specifications, contact your Intel Sales Representative.

#### Table 29. Transceiver Compliance Specification for All Supported Protocol for Cyclone V GX, GT, SX, and ST Devices

| Protocol                             | Sub-protocol              | Data Rate (Mbps) |

|--------------------------------------|---------------------------|------------------|

| PCIe                                 | PCIe Gen1                 | 2,500            |

|                                      | PCIe Gen2 <sup>(50)</sup> | 5,000            |

|                                      | PCIe Cable                | 2,500            |

| XAUI                                 | XAUI 2135                 | 3,125            |

| Serial RapidIO <sup>®</sup> (SRIO)   | SRIO 1250 SR              | 1,250            |

|                                      | SRIO 1250 LR              | 1,250            |

|                                      | SRIO 2500 SR              | 2,500            |

|                                      | SRIO 2500 LR              | 2,500            |

|                                      | SRIO 3125 SR              | 3,125            |

|                                      | SRIO 3125 LR              | 3,125            |

|                                      | SRIO 5000 SR              | 5,000            |

|                                      | SRIO 5000 MR              | 5,000            |

|                                      | SRIO 5000 LR              | 5,000            |

| Common Public Radio Interface (CPRI) | CPRI E6LV                 | 614.4            |

|                                      | CPRI E6HV                 | 614.4            |

|                                      | CPRI E6LVII               | 614.4            |

|                                      |                           | continued        |

<sup>(50)</sup> For PCIe Gen2 sub-protocol, Intel recommends increasing the V<sub>CCE\_GXBL</sub> and V<sub>CCL\_GXBL</sub> typical value from 1.1 V to 1.2 V for Cyclone V GT and ST FPGA systems which ensure full compliance to the PCIe Gen2 transmit jitter specification. For more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices under this condition, refer to the *Transceiver Protocol Configurations in Cyclone V Devices* chapter.

# **Duty Cycle Distortion (DCD) Specifications**

#### Table 39. Worst-Case DCD on Cyclone V I/O Pins

The output DCD cycle only applies to the I/O buffer. It does not cover the system DCD.

| Symbol            | -C6 |     | -C7, -I7 |     | -C8, -A7 |     | Unit |

|-------------------|-----|-----|----------|-----|----------|-----|------|

|                   | Min | Мах | Min      | Max | Min      | Мах |      |

| Output Duty Cycle | 45  | 55  | 45       | 55  | 45       | 55  | %    |

# **HPS Specifications**

This section provides HPS specifications and timing for Cyclone V devices.

For HPS reset, the minimum reset pulse widths for the HPS cold and warm reset signals (HPS\_nRST and HPS\_nPOR) are six clock cycles of HPS\_CLK1.

## **HPS Clock Performance**

#### Table 40. HPS Clock Performance for Cyclone V Devices

| Symbol/Description                       | -C6 | -C7, -I7 | -A7 | -C8 | Unit |

|------------------------------------------|-----|----------|-----|-----|------|

| mpu_base_clk (microprocessor unit clock) | 925 | 800      | 700 | 600 | MHz  |

| main_base_clk (L3/L4 interconnect clock) | 400 | 400      | 350 | 300 | MHz  |

| h2f_user0_clk                            | 100 | 100      | 100 | 100 | MHz  |

| h2f_user1_clk                            | 100 | 100      | 100 | 100 | MHz  |

| h2f_user2_clk                            | 200 | 200      | 160 | 160 | MHz  |

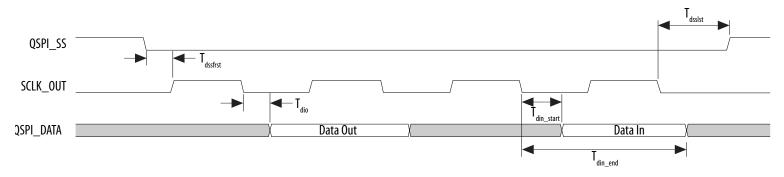

# **Quad SPI Flash Timing Characteristics**

# Table 43. Quad Serial Peripheral Interface (SPI) Flash Timing Requirements for Cyclone V Devices

| Symbol                 | Description                                        | Min                                               | Тур                      | Мах                                                                         | Unit |

|------------------------|----------------------------------------------------|---------------------------------------------------|--------------------------|-----------------------------------------------------------------------------|------|

| F <sub>clk</sub>       | SCLK_OUT clock frequency (External clock)          | -                                                 | _                        | 108                                                                         | MHz  |

| T <sub>qspi_clk</sub>  | QSPI_CLK clock period (Internal reference clock)   | 2.32                                              | -                        | —                                                                           | ns   |

| T <sub>dutycycle</sub> | SCLK_OUT duty cycle                                | 45                                                | _                        | 55                                                                          | %    |

| T <sub>dssfrst</sub>   | Output delay QSPI_SS valid before first clock edge | -                                                 | 1/2 cycle of<br>SCLK_OUT | _                                                                           | ns   |

| T <sub>dsslst</sub>    | Output delay QSPI_SS valid after last clock edge   | -1                                                | _                        | 1                                                                           | ns   |

| T <sub>dio</sub>       | I/O data output delay                              | -1                                                | -                        | 1                                                                           | ns   |

| T <sub>din_start</sub> | Input data valid start                             | -                                                 | _                        | (2 + R <sub>delay</sub> ) ×<br>T <sub>qspi_clk</sub> - 7.52 <sup>(68)</sup> | ns   |

| T <sub>din_end</sub>   | Input data valid end                               | $(2 + R_{delay}) \times T_{qspi_clk} - 1.21$ (68) | _                        | _                                                                           | ns   |

## Figure 6. Quad SPI Flash Timing Diagram

This timing diagram illustrates clock polarity mode 0 and clock phase mode 0.

<sup>(68)</sup> R<sub>delay</sub> is set by programming the register gspiregs.rddatacap. For the SoC EDS software version 13.1 and later, Intel provides automatic Quad SPI calibration in the preloader. For more information about R<sub>delay</sub>, refer to the Quad SPI Flash Controller chapter in the Cyclone V Hard Processor System Technical Reference Manual.

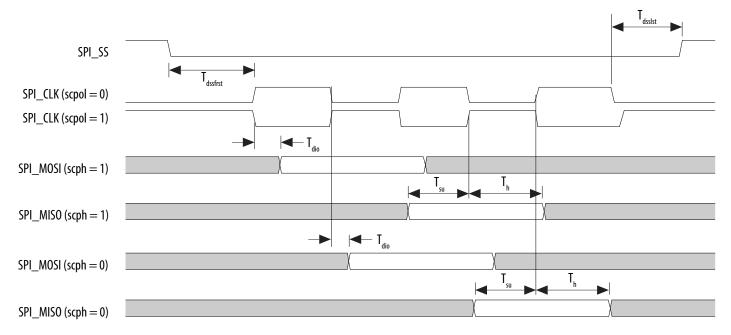

# Figure 7. SPI Master Timing Diagram

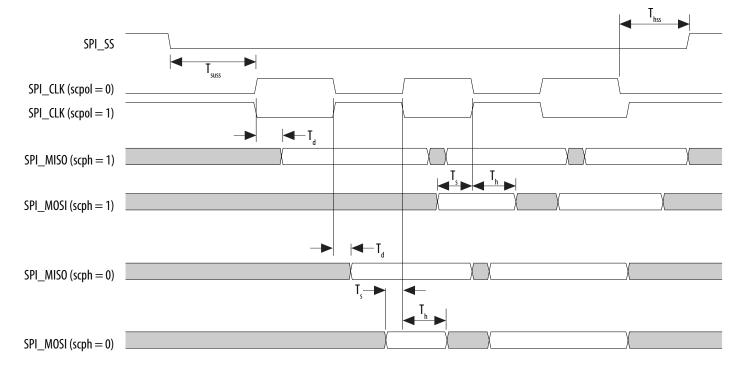

#### Table 45. SPI Slave Timing Requirements for Cyclone V Devices

The setup and hold times can be used for Texas Instruments SSP mode and National Semiconductor Microwire mode.

| Symbol            | Description                                     | Min | Мах | Unit |

|-------------------|-------------------------------------------------|-----|-----|------|

| T <sub>clk</sub>  | CLK clock period                                | 20  | —   | ns   |

| T <sub>s</sub>    | MOSI Setup time                                 | 5   | _   | ns   |

| T <sub>h</sub>    | MOSI Hold time                                  | 5   | _   | ns   |

| T <sub>suss</sub> | Setup time SPI_SS valid before first clock edge | 8   | —   | ns   |

| T <sub>hss</sub>  | Hold time SPI_SS valid after last clock edge    | 8   | _   | ns   |

| T <sub>d</sub>    | MISO output delay                               | _   | 6   | ns   |

# Figure 8. SPI Slave Timing Diagram

### **Related Information**

SPI Controller, Cyclone V Hard Processor System Technical Reference Manual Provides more information about rx\_sample\_delay.

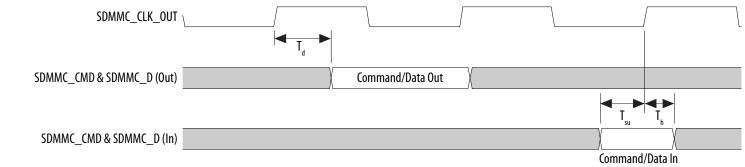

# **SD/MMC Timing Characteristics**

### Table 46. Secure Digital (SD)/MultiMediaCard (MMC) Timing Requirements for Cyclone V Devices

After power up or cold reset, the Boot ROM uses drvsel = 3 and smplsel = 0 to execute the code. At the same time, the SD/MMC controller enters the Identification Phase followed by the Data Phase. During this time, the value of interface output clock SDMMC\_CLK\_OUT changes from a maximum of 400 kHz (Identification Phase) up to a maximum of 12.5 MHz (Data Phase), depending on the internal reference clock SDMMC\_CLK and the CSEL setting. The value of SDMMC\_CLK is based on the external oscillator frequency and has a maximum value of 50 MHz.

After the Boot ROM code exits and control is passed to the preloader, software can adjust the value of drvsel and smplsel via the system manager. drvsel can be set from 1 to 7 and smplsel can be set from 0 to 7. While the preloader is executing, the values for SDMMC\_CLK and SDMMC\_CLK\_OUT increase to a maximum of 200 MHz and 50 MHz respectively.

| Symbol                                              | Description                                         | Min                                                | Мах                                                           | Unit |

|-----------------------------------------------------|-----------------------------------------------------|----------------------------------------------------|---------------------------------------------------------------|------|

| T <sub>sdmmc_clk</sub> (internal reference clock)   | SDMMC_CLK clock period (Identification mode)        | 20                                                 | _                                                             | ns   |

|                                                     | SDMMC_CLK clock period (Default speed mode)         | 5                                                  | _                                                             | ns   |

|                                                     | SDMMC_CLK clock period (High speed mode)            | 5                                                  | _                                                             | ns   |

| T <sub>sdmmc_clk_out</sub> (interface output clock) | SDMMC_CLK_OUT clock period<br>(Identification mode) | 2500                                               | _                                                             | ns   |

|                                                     | SDMMC_CLK_OUT clock period (Default speed mode)     | 40                                                 | _                                                             | ns   |

|                                                     | SDMMC_CLK_OUT clock period (High speed mode)        | 20                                                 | _                                                             | ns   |

| T <sub>dutycycle</sub>                              | SDMMC_CLK_OUT duty cycle                            | 45                                                 | 55                                                            | %    |

| T <sub>d</sub>                                      | SDMMC_CMD/SDMMC_D output delay                      | (T <sub>sdmmc_clk</sub> × drvsel)/2 - 1.23<br>(70) | (T <sub>sdmmc_clk</sub> × drvsel)/2<br>+ 1.69 <sup>(70)</sup> | ns   |

| T <sub>su</sub>                                     | Input setup time                                    | $1.05 - (T_{sdmmc_clk} \times smplsel)/2$          | _                                                             | ns   |

| T <sub>h</sub>                                      | Input hold time                                     | $(T_{sdmmc_{clk}} \times smplsel)/2$ (71)          | _                                                             | ns   |

<sup>(70)</sup> drvsel is the drive clock phase shift select value.

<sup>(71)</sup> smplsel is the sample clock phase shift select value.

# Figure 9. SD/MMC Timing Diagram

#### **Related Information**

Booting and Configuration Chapter, Cyclone V Hard Processor System Technical Reference Manual Provides more information about CSEL pin settings in the *SD/MMC Controller CSEL Pin Settings* table.

# **USB Timing Characteristics**

PHYs that support LPM mode may not function properly with the USB controller due to a timing issue. It is recommended that designers use the MicroChip USB3300 PHY device that has been proven to be successful on the development board.

## Table 47. USB Timing Requirements for Cyclone V Devices

| Symbol           | Description                                  | Min | Тур   | Max | Unit |

|------------------|----------------------------------------------|-----|-------|-----|------|

| T <sub>clk</sub> | USB CLK clock period                         | —   | 16.67 | —   | ns   |

| T <sub>d</sub>   | CLK to USB_STP/USB_DATA[7:0] output delay    | 4.4 | —     | 11  | ns   |

| T <sub>su</sub>  | Setup time for USB_DIR/USB_NXT/USB_DATA[7:0] | 2   | _     | _   | ns   |

| T <sub>h</sub>   | Hold time for USB_DIR/USB_NXT/USB_DATA[7:0]  | 1   | _     | _   | ns   |

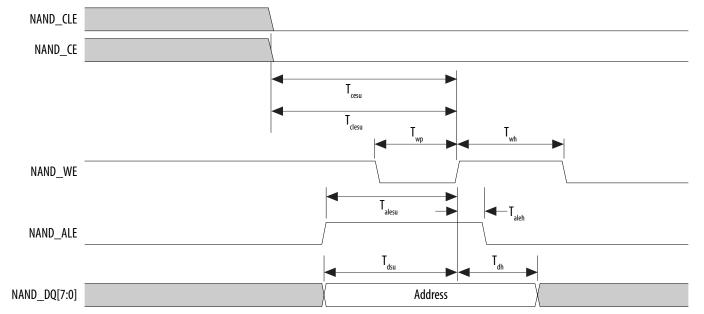

# Figure 16. NAND Address Latch Timing Diagram

| Symbol            | Description                                | Min | Мах                | Unit |

|-------------------|--------------------------------------------|-----|--------------------|------|

| t <sub>JPCO</sub> | JTAG port clock to output                  | —   | 11 <sup>(76)</sup> | ns   |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output - |     | 14 <sup>(76)</sup> | ns   |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance   | _   | 14 <sup>(76)</sup> | ns   |

# **FPP Configuration Timing**

# DCLK-to-DATA[] Ratio (r) for FPP Configuration

Fast passive parallel (FPP) configuration requires a different DCLK-to-DATA[] ratio when you turn on encryption or the compression feature.

Depending on the DCLK-to-DATA[] ratio, the host must send a DCLK frequency that is r times the DATA[] rate in byte per second (Bps) or word per second (Wps). For example, in FPP ×16 where the r is 2, the DCLK frequency must be 2 times the DATA[] rate in Wps.

Cyclone V devices use additional clock cycles to decrypt and decompress the configuration data. If the DCLK-to-DATA[] ratio is greater than 1, at the end of configuration, you can only stop the DCLK (DCLK-to-DATA[] ratio – 1) clock cycles after the last data is latched into the Cyclone V device.

### Table 57. DCLK-to-DATA[] Ratio for Cyclone V Devices

| Configuration Scheme | Encryption | Compression | DCLK-to-DATA[] Ratio (r) |

|----------------------|------------|-------------|--------------------------|

| FPP (8-bit wide)     | Off        | Off         | 1                        |

|                      | On         | Off         | 1                        |

|                      | Off        | On          | 2                        |

|                      | On         | On          | 2                        |

| FPP (16-bit wide)    | Off        | Off         | 1                        |

|                      |            | •           | continued                |

<sup>(76)</sup> A 1-ns adder is required for each VCCIO voltage step down from 3.0 V. For example, tJPCO= 13 ns if VCCIO of the TDO I/O bank = 2.5 V, or 14 ns if it equals 1.8 V.

| Term                 | Definition                                                                                                                                                                                                                                                                                              |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | CLKOUT Pins<br>CLKOUT Pins<br>four_Ext<br>CLKOUT Pins<br>CLKOUT Pins<br>four_Ext<br>Core Clock<br>Legend<br>Reconfigurable in User Mode<br>External Feedback<br>Note:<br>(1) Core Clock can only be fed by dedicated clock input pins or PLL outputs.                                                   |

| RL                   | Receiver differential input discrete resistor (external to the Cyclone V device).                                                                                                                                                                                                                       |

| Sampling window (SW) | Timing diagram—The period of time during which the data must be valid in order to capture it correctly. The setup and hold times determine the ideal strobe position in the sampling window, as shown:         Bit Time         0.5 x TCCS       RSKM       Sampling Window       RSKM       0.5 x TCCS |

|                      | continued                                                                                                                                                                                                                                                                                               |

| Term                                            |                                                                                                                                                                                                                                                                                | Definition                                                                  |                                                                                                          |                            |                                                                                     |  |  |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------------------|--|--|

| Single-ended voltage referenced<br>I/O standard | The JEDEC standard for the SSTL and<br>levels at which the receiver must meet<br>the receiver is unambiguously defined.<br>The new logic state is then maintained<br>predictable receiver timing in the press<br>Single-Ended Voltage Referenced I/O S                         | t its timing spe<br>. After the rece<br>I as long as the<br>ence of input v | ecifications. The DC values indic<br>eiver input has crossed the AC v<br>e input stays beyond the DC thr | ate the volta alue, the re | age levels at which the final logic state of ceiver changes to the new logic state. |  |  |

|                                                 |                                                                                                                                                                                                                                                                                |                                                                             |                                                                                                          |                            | V <sub>CCI0</sub>                                                                   |  |  |

|                                                 |                                                                                                                                                                                                                                                                                |                                                                             |                                                                                                          |                            |                                                                                     |  |  |

|                                                 | V <sub>0H</sub>                                                                                                                                                                                                                                                                | <u> </u>                                                                    |                                                                                                          | /                          | V <sub>IH(AC)</sub>                                                                 |  |  |

|                                                 |                                                                                                                                                                                                                                                                                |                                                                             | <br>                                                                                                     |                            | V IH (DC )                                                                          |  |  |

|                                                 |                                                                                                                                                                                                                                                                                |                                                                             | V <sub>REF</sub>                                                                                         |                            | V <sub>IL(DC)</sub>                                                                 |  |  |

|                                                 |                                                                                                                                                                                                                                                                                |                                                                             |                                                                                                          | /                          | Vil(AC)                                                                             |  |  |

|                                                 | V <sub>0L</sub>                                                                                                                                                                                                                                                                |                                                                             | /-                                                                                                       |                            |                                                                                     |  |  |

|                                                 |                                                                                                                                                                                                                                                                                |                                                                             |                                                                                                          |                            | V <sub>SS</sub>                                                                     |  |  |

| с                                               | High-speed receiver/transmitter input                                                                                                                                                                                                                                          | and output clo                                                              | ock period.                                                                                              |                            |                                                                                     |  |  |

| CCS (channel-to-channel-skew)                   | The timing difference between the fastest and slowest output edges, including the t <sub>CO</sub> variation and clock skew, across channels driven by the same PLL. The clock is included in the TCCS measurement (refer to the Timing Diagram figure under SW in this table). |                                                                             |                                                                                                          |                            |                                                                                     |  |  |

| DUTY                                            | High-speed I/O block—Duty cycle on high-speed transmitter output clock.                                                                                                                                                                                                        |                                                                             |                                                                                                          |                            |                                                                                     |  |  |

| FALL                                            | Signal high-to-low transition time (80–20%)                                                                                                                                                                                                                                    |                                                                             |                                                                                                          |                            |                                                                                     |  |  |

| INCCJ                                           | Cycle-to-cycle jitter tolerance on the P                                                                                                                                                                                                                                       | LL clock input                                                              |                                                                                                          |                            |                                                                                     |  |  |

#### Cyclone V Device Datasheet

CV-51002 | 2018.05.07

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                               |

|---------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 2012 | 1.2     | <ul> <li>Added automotive speed grade information.</li> <li>Added Figure 2–1.</li> <li>Updated Table 2–3, Table 2–8, Table 2–9, Table 2–19, Table 2–20, Table 2–21, Table 2–22, Table 2–23, Table 2–24, Table 2–25, Table 2–26, Table 2–27, Table 2–28, Table 2–30, Table 2–35, and Table 2–43.</li> <li>Minor text edits.</li> </ul> |

| November 2011 | 1.1     | <ul> <li>Added Table 2–5.</li> <li>Updated Table 2–3, Table 2–4, Table 2–11, Table 2–13, Table 2–20, and Table 2–21.</li> </ul>                                                                                                                                                                                                       |

| October 2011  | 1.0     | Initial release.                                                                                                                                                                                                                                                                                                                      |