## Intel - 5CSXFC5D6F31I7N Datasheet

Welcome to E-XFL.COM

#### Embedded - System On Chip (SoC): The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

## What are Embedded - System On Chip (SoC)?

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

#### Details

| Betuils                 |                                                                                               |

|-------------------------|-----------------------------------------------------------------------------------------------|

| Product Status          | Active                                                                                        |

| Architecture            | MCU, FPGA                                                                                     |

| Core Processor          | Dual ARM <sup>®</sup> Cortex <sup>®</sup> -A9 MPCore <sup>™</sup> with CoreSight <sup>™</sup> |

| Flash Size              | -                                                                                             |

| RAM Size                | 64КВ                                                                                          |

| Peripherals             | DMA, POR, WDT                                                                                 |

| Connectivity            | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, MMC/SD/SDIO, SPI, UART/USART, USB OTG            |

| Speed                   | 800MHz                                                                                        |

| Primary Attributes      | FPGA - 85K Logic Elements                                                                     |

| Operating Temperature   | -40°C ~ 100°C (TJ)                                                                            |

| Package / Case          | 896-BGA                                                                                       |

| Supplier Device Package | 896-FBGA (31x31)                                                                              |

| Purchase URL            | https://www.e-xfl.com/product-detail/intel/5csxfc5d6f31i7n                                    |

|                         |                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| yclone V Device Datasheet                                   |    |

|-------------------------------------------------------------|----|

| Electrical Characteristics                                  |    |

| Operating Conditions                                        |    |

| Switching Characteristics                                   | 24 |

| Transceiver Performance Specifications                      |    |

| Core Performance Specifications                             | 40 |

| Periphery Performance                                       | 45 |

| HPS Specifications                                          | 51 |

| Configuration Specifications                                | 67 |

| POR Specifications                                          |    |

| FPGA JTAG Configuration Timing                              |    |

| FPP Configuration Timing                                    |    |

| Active Serial (AS) Configuration Timing                     | 73 |

| DCLK Frequency Specification in the AS Configuration Scheme | 74 |

| Passive Serial (PS) Configuration Timing                    |    |

| Initialization                                              | 75 |

| Configuration Files                                         |    |

| Minimum Configuration Time Estimation                       | 77 |

| Remote System Upgrades                                      |    |

| User Watchdog Internal Oscillator Frequency Specifications  |    |

| I/O Timing                                                  |    |

| Programmable IOE Delay                                      |    |

| Programmable Output Buffer Delay                            |    |

| Glossary                                                    |    |

| Document Revision History for Cyclone V Device Datasheet    |    |

| Density | Ordering Part Number (OPN) | Static Power Reduction |

|---------|----------------------------|------------------------|

| 110K LE | 5CSEBA6U19I7LN             |                        |

|         | 5CSEBA6U23I7LN             |                        |

|         | 5CSXFC6C6U23I7LN           |                        |

To estimate total power consumption for a low-power device, listed in Table 1 on page 3:

- 1. Multiply the Total Static Power reported by the Early Power Estimator (EPE) by the appropriate scale factor:

- For 25K LE and 40K LE devices, use 0.7

- For 85K LE and 110K LE devices, use 0.8

- 2. Add the result from Step 1 on page 4 to the Total Dynamic Power reported by the EPE.

#### **Related Information**

#### Cyclone V Device Overview

Provides more information about the densities and packages of devices in the Cyclone V family.

# **Electrical Characteristics**

The following sections describe the operating conditions and power consumption of Cyclone V devices.

## **Operating Conditions**

Cyclone V devices are rated according to a set of defined parameters. To maintain the highest possible performance and reliability of the Cyclone V devices, you must consider the operating requirements described in this section.

## **Absolute Maximum Ratings**

This section defines the maximum operating conditions for Cyclone V devices. The values are based on experiments conducted with the devices and theoretical modeling of breakdown and damage mechanisms.

The functional operation of the device is not implied for these conditions.

**Caution:** Conditions outside the range listed in the following table may cause permanent damage to the device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse effects on the device.

## **Transceiver Power Supply Operating Conditions**

#### Table 5. Transceiver Power Supply Operating Conditions for Cyclone V GX, GT, SX, and ST Devices

| Symbol                                   | Description                                | Minimum <sup>(8)</sup> | Typical | Maximum <sup>(8)</sup> | Unit |

|------------------------------------------|--------------------------------------------|------------------------|---------|------------------------|------|

| V <sub>CCH_GXBL</sub>                    | Transceiver high voltage power (left side) | 2.375                  | 2.5     | 2.625                  | V    |

| V <sub>CCE_GXBL</sub> <sup>(9)(10)</sup> | Transmitter and receiver power (left side) | 1.07/1.17              | 1.1/1.2 | 1.13/1.23              | V    |

| V <sub>CCL_GXBL</sub> <sup>(9)(10)</sup> | Clock network power (left side)            | 1.07/1.17              | 1.1/1.2 | 1.13/1.23              | V    |

#### **Related Information**

• PCIe Supported Configurations and Placement Guidelines

Provides more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices which require full compliance to the PCIe Gen2 transmit jitter specification.

6.144-Gbps Support Capability in Cyclone V GT Devices

Provides more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices for

CPRI 6.144 Gbps.

<sup>&</sup>lt;sup>(8)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(9)</sup> Intel recommends increasing the V<sub>CCE\_GXBL</sub> and V<sub>CCL\_GXBL</sub> typical value from 1.1 V to 1.2 V for Cyclone V GT and ST FPGA systems which require full compliance to the PCIe Gen2 transmit jitter specification. For more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices under this condition, refer to the *Transceiver Protocol Configurations in Cyclone V Devices* chapter.

<sup>(10)</sup> Intel recommends increasing the V<sub>CCE\_GXBL</sub> and V<sub>CCL\_GXBL</sub> typical value from 1.1 V to 1.2 V for full compliance to CPRI transmit jitter specification at 4.9152 Gbps (Cyclone V GT and ST devices) and 6.144Gbps (Cyclone V GT and ST devices only). For more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices for CPRI 6.144 Gbps, refer to the *Transceiver Protocol Configurations in Cyclone V Devices* chapter.

# **Transceiver Performance Specifications**

# Transceiver Specifications for Cyclone V GX, GT, SX, and ST Devices

## Table 21. Reference Clock Specifications for Cyclone V GX, GT, SX, and ST Devices

| Symbol/Description                                        | Condition                                                | Transceiv | er Speed G     | rade 5 <sup>(30)</sup> | Transce     | iver Speed     | Grade 6                   | Transceiver Speed Grade 7 |                |      | Unit    |

|-----------------------------------------------------------|----------------------------------------------------------|-----------|----------------|------------------------|-------------|----------------|---------------------------|---------------------------|----------------|------|---------|

|                                                           |                                                          | Min       | Тур            | Max                    | Min         | Тур            | Max                       | Min                       | Тур            | Max  |         |

| Supported I/O standards                                   |                                                          | 1.2       | 2 V PCML, 1.   | 5 V PCML, 2.           | 5 V PCML, I | Differential L | VPECL <sup>(31)</sup> , H | CSL, and LV               | DS             | •    |         |

| Input frequency from<br>REFCLK input pins <sup>(32)</sup> | _                                                        | 27        | -              | 550                    | 27          | -              | 550                       | 27                        | -              | 550  | MHz     |

| Rise time                                                 | Measure at ±60 mV of differential signal <sup>(33)</sup> | _         | -              | 400                    | _           | -              | 400                       | -                         | -              | 400  | ps      |

| Fall time                                                 | Measure at ±60 mV of differential signal <sup>(33)</sup> | _         | -              | 400                    | _           | -              | 400                       | -                         | -              | 400  | ps      |

| Duty cycle                                                | -                                                        | 45        | -              | 55                     | 45          | -              | 55                        | 45                        | -              | 55   | %       |

| Peak-to-peak differential input voltage                   | _                                                        | 200       | -              | 2000                   | 200         | -              | 2000                      | 200                       | -              | 2000 | mV      |

| Spread-spectrum<br>modulating clock frequency             | PCIe                                                     | 30        | -              | 33                     | 30          | -              | 33                        | 30                        | -              | 33   | kHz     |

| Spread-spectrum<br>downspread                             | PCIe                                                     | -         | 0 to -<br>0.5% | -                      | _           | 0 to -<br>0.5% | -                         | -                         | 0 to -<br>0.5% | -    | -       |

| On-chip termination resistors                             | _                                                        | -         | 100            | —                      | _           | 100            | -                         | -                         | 100            | -    | Ω       |

|                                                           | 1                                                        | 1         | 1              | 1                      |             |                |                           | 1                         | 1              | CO   | ntinued |

<sup>(30)</sup> Transceiver Speed Grade 5 covers specifications for Cyclone V GT and ST devices.

<sup>(31)</sup> Differential LVPECL signal levels must comply to the minimum and maximum peak-to-peak differential input voltage specified in this table.

(32) The reference clock frequency must be ≥ 307.2 MHz to be fully compliance to CPRI transmit jitter specification at 6.144 Gbps. For more information about CPRI 6.144 Gbps, refer to the *Transceiver Protocol Configurations in Cyclone V Devices* chapter.

<sup>(33)</sup> REFCLK performance requires to meet transmitter REFCLK phase noise specification.

| Symbol/Description                                                                       | Condition                       | Transceiv                                        | er Speed G | rade 5 <sup>(30)</sup> | Transce                      | iver Speed                    | Grade 6 | Transce | iver Speed              | Grade 7 | Unit    |

|------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------|------------|------------------------|------------------------------|-------------------------------|---------|---------|-------------------------|---------|---------|

|                                                                                          |                                 | Min                                              | Тур        | Max                    | Min                          | Тур                           | Max     | Min     | Тур                     | Max     |         |

| Minimum differential eye<br>opening at the receiver<br>serial input pins <sup>(40)</sup> | -                               | 110                                              | -          | -                      | 110                          | -                             | -       | 110     | _                       | -       | mV      |

| Differential on-chip<br>termination resistors                                            | 85-Ω setting                    | -                                                | 85         | -                      | -                            | 85                            | -       | -       | 85                      | -       | Ω       |

|                                                                                          | 100-Ω setting                   | -                                                | 100        | _                      | _                            | 100                           | _       | -       | 100                     | _       | Ω       |

|                                                                                          | 120-Ω setting                   | -                                                | 120        | _                      | _                            | 120                           | -       | -       | 120                     | _       | Ω       |

|                                                                                          | 150-Ω setting                   | -                                                | 150        | _                      | _                            | 150                           | _       | -       | 150                     | _       | Ω       |

| $V_{\text{ICM}}$ (AC coupled)                                                            | 2.5 V PCML, LVPECL,<br>and LVDS | V <sub>CCE_GXBL</sub> supply <sup>(34)(35)</sup> |            |                        | V <sub>CCE_GXBL</sub> supply |                               |         | Vo      | <sub>CCE_GXBL</sub> sup | V       |         |

|                                                                                          | 1.5 V PCML                      |                                                  |            |                        | 0.6                          | 0.65/0.75/0.8 <sup>(41)</sup> |         |         |                         |         | V       |

| t <sub>LTR</sub> <sup>(42)</sup>                                                         | _                               | -                                                | -          | 10                     | _                            | _                             | 10      | -       | -                       | 10      | μs      |

| t <sub>LTD</sub> <sup>(43)</sup>                                                         | -                               | -                                                | -          | 4                      | _                            | -                             | 4       | -       | -                       | 4       | μs      |

| t <sub>LTD_manual</sub> (44)                                                             | -                               | _                                                | _          | 4                      | _                            | _                             | 4       | -       | -                       | 4       | μs      |

| t <sub>LTR_LTD_manual</sub> (45)                                                         | _                               | 15                                               | -          | _                      | 15                           | _                             | _       | 15      | -                       | _       | μs      |

|                                                                                          |                                 |                                                  |            | •                      |                              |                               |         |         |                         | со      | ntinued |

- $^{(43)}$  t<sub>LTD</sub> is time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high.

- $t_{LTD\_manual}$  is the time required for the receiver CDR to start recovering valid data after the rx\_is\_lockedtodata signal goes high when the CDR is functioning in the manual mode.

<sup>(40)</sup> The differential eye opening specification at the receiver input pins assumes that you have disabled the Receiver Equalization feature. If you enable the Receiver Equalization feature, the receiver circuitry can tolerate a lower minimum eye opening, depending on the equalization level.

<sup>&</sup>lt;sup>(41)</sup> The AC coupled  $V_{ICM}$  = 650 mV for Cyclone V GX and SX in PCIe mode only. The AC coupled  $V_{ICM}$  = 750mV for Cyclone V GT and ST in PCIe mode only.

$<sup>^{(42)}</sup>$  t<sub>LTR</sub> is the time required for the receive clock data recovery (CDR) to lock to the input reference clock frequency after coming out of reset.

Exceptions for PCIe Gen2 design:

- V<sub>OD</sub> setting = 50 and pre-emphasis setting = 22 are allowed for PCIe Gen2 design with transmit de-emphasis -6dB setting (pipe\_txdeemp = 1'b0) using Intel PCIe Hard IP and PIPE IP cores.

- V<sub>OD</sub> setting = 50 and pre-emphasis setting = 12 are allowed for PCIe Gen2 design with transmit de-emphasis -3.5dB setting (pipe\_txdeemp = 1'b1) using Intel PCIe Hard IP and PIPE IP cores.

For example, when  $V_{OD}$  = 800 mV, the corresponding  $V_{OD}$  value setting is 40. The following conditions show that the 1st post tap pre-emphasis setting = 2 is valid:

- $|B| + |C| \le 60 \rightarrow 40 + 2 = 42$

- |B| |C| > 5→ 40 2 = 38

- $(V_{MAX}/V_{MIN} 1)\% < 600\% \rightarrow (42/38 1)\% = 10.52\%$

To predict the pre-emphasis level for your specific data rate and pattern, run simulations using the Cyclone V HSSI HSPICE models.

| Intel Quartus Prime 1st          |             |             | Intel Qu    | u <mark>artus Prime V<sub>OD</sub></mark> | Setting     |             |              | Unit     |

|----------------------------------|-------------|-------------|-------------|-------------------------------------------|-------------|-------------|--------------|----------|

| Post Tap Pre-Emphasis<br>Setting | 10 (200 mV) | 20 (400 mV) | 30 (600 mV) | 35 (700 mV)                               | 40 (800 mV) | 45 (900 mV) | 50 (1000 mV) |          |

| 0                                | 0           | 0           | 0           | 0                                         | 0           | 0           | 0            | dB       |

| 1                                | 1.97        | 0.88        | 0.43        | 0.32                                      | 0.24        | 0.19        | 0.13         | dB       |

| 2                                | 3.58        | 1.67        | 0.95        | 0.76                                      | 0.61        | 0.5         | 0.41         | dB       |

| 3                                | 5.35        | 2.48        | 1.49        | 1.2                                       | 1           | 0.83        | 0.69         | dB       |

| 4                                | 7.27        | 3.31        | 2           | 1.63                                      | 1.36        | 1.14        | 0.96         | dB       |

| 5                                | _           | 4.19        | 2.55        | 2.1                                       | 1.76        | 1.49        | 1.26         | dB       |

| 6                                | _           | 5.08        | 3.11        | 2.56                                      | 2.17        | 1.83        | 1.56         | dB       |

| 7                                | _           | 5.99        | 3.71        | 3.06                                      | 2.58        | 2.18        | 1.87         | dB       |

| 8                                | _           | 6.92        | 4.22        | 3.47                                      | 2.93        | 2.48        | 2.11         | dB       |

| 9                                | _           | 7.92        | 4.86        | 4                                         | 3.38        | 2.87        | 2.46         | dB       |

| 10                               | _           | 9.04        | 5.46        | 4.51                                      | 3.79        | 3.23        | 2.77         | dB       |

|                                  |             |             | •           |                                           |             | •           |              | continue |

## Table 28. Transmitter Pre-Emphasis Levels for Cyclone V Devices

| Symbol                                         | Parameter                                                         | Condition                     | Min | Тур | Max                                       | Unit      |

|------------------------------------------------|-------------------------------------------------------------------|-------------------------------|-----|-----|-------------------------------------------|-----------|

| t <sub>ARESET</sub>                            | Minimum pulse width on the areset signal                          | _                             | 10  | -   | _                                         | ns        |

| t <sub>INCCJ</sub> <sup>(56)(57)</sup>         | Input clock cycle-to-cycle jitter                                 | $F_{REF} \ge 100 \text{ MHz}$ | -   | -   | 0.15                                      | UI (p-p)  |

|                                                |                                                                   | $F_{REF} < 100 \text{ MHz}$   | _   | _   | ±750                                      | ps (p-p)  |

| t <sub>OUTPJ_DC</sub> <sup>(58)</sup>          | Period jitter for dedicated clock output in                       | $F_{OUT} \ge 100 \text{ MHz}$ | _   | -   | 300                                       | ps (p-p)  |

|                                                | integer PLL                                                       | F <sub>OUT</sub> < 100 MHz    | _   | -   | 30                                        | mUI (p-p) |

| t <sub>FOUTPJ_DC</sub> <sup>(58)</sup>         | Period jitter for dedicated clock output in                       | $F_{OUT} \ge 100 \text{ MHz}$ | _   | -   | 425 <sup>(61)</sup> , 300 <sup>(59)</sup> | ps (p-p)  |

|                                                | fractional PLL                                                    | F <sub>OUT</sub> < 100 MHz    | -   | -   | 42.5 <sup>(61)</sup> , 30 <sup>(59)</sup> | mUI (p-p) |

| t <sub>OUTCCJ_DC</sub> <sup>(58)</sup>         | Cycle-to-cycle jitter for dedicated clock output                  | $F_{OUT} \ge 100 \text{ MHz}$ | _   | _   | 300                                       | ps (p-p)  |

|                                                | in integer PLL                                                    | F <sub>OUT</sub> < 100 MHz    | _   | -   | 30                                        | mUI (p-p) |

| t <sub>FOUTCCJ_DC</sub> <sup>(58)</sup>        | Cycle-to-cycle jitter for dedicated clock output                  | $F_{OUT} \ge 100 \text{ MHz}$ | -   | -   | 425 <sup>(61)</sup> , 300 <sup>(59)</sup> | ps (p-p)  |

|                                                | in fractional PLL                                                 | F <sub>OUT</sub> < 100 MHz    | _   | -   | 42.5 <sup>(61)</sup> , 30 <sup>(59)</sup> | mUI (p-p) |

| t <sub>OUTPJ_IO</sub> <sup>(58)(60)</sup>      | Period jitter for clock output on a regular I/O                   | $F_{OUT} \ge 100 \text{ MHz}$ | -   | -   | 650                                       | ps (p-p)  |

|                                                | in integer PLL                                                    | F <sub>OUT</sub> < 100 MHz    | _   | _   | 65                                        | mUI (p-p) |

| t <sub>FOUTPJ_IO</sub> <sup>(58)(60)(61)</sup> | Period jitter for clock output on a regular I/O in fractional PLL | $F_{OUT} \ge 100 \text{ MHz}$ | -   | -   | 650                                       | ps (p-p)  |

|                                                | · · ·                                                             |                               | I   | 1   |                                           | continued |

(56) A high input jitter directly affects the PLL output jitter. To have low PLL output clock jitter, you must provide a clean clock source with jitter < 120 ps.</p>

- <sup>(57)</sup>  $F_{REF}$  is  $f_{IN}/N$ , specification applies when N = 1.

- (58) Peak-to-peak jitter with a probability level of 10<sup>-12</sup> (14 sigma, 99.999999999974404% confidence level). The output jitter specification applies to the intrinsic jitter of the PLL, when an input jitter of 30 ps is applied. The external memory interface clock output jitter specifications use a different measurement method and are available in *Memory Output Clock Jitter Specification for Cyclone V Devices* table.

- <sup>(59)</sup> This specification only covers fractional PLL for low bandwidth. The  $f_{VCO}$  for fractional value range 0.20–0.80 must be  $\geq$  1200 MHz.

- <sup>(60)</sup> External memory interface clock output jitter specifications use a different measurement method, which are available in *Memory Output Clock Jitter Specification for Cyclone V Devices* table.

#### Cyclone V Device Datasheet

CV-51002 | 2018.05.07

| Symbol                                         | Parameter                                                              | Condition                     | Min    | Тур     | Max        | Unit      |

|------------------------------------------------|------------------------------------------------------------------------|-------------------------------|--------|---------|------------|-----------|

|                                                |                                                                        | $F_{OUT}$ < 100 MHz           | -      | -       | 65         | mUI (p-p) |

| t <sub>OUTCCJ_IO</sub> <sup>(58)(60)</sup>     | Cycle-to-cycle jitter for clock output on                              | $F_{OUT} \ge 100 \text{ MHz}$ | —      | —       | 650        | ps (p-p)  |

|                                                | regular I/O in integer PLL                                             | $F_{OUT} < 100 \text{ MHz}$   | _      | —       | 65         | mUI (p-p) |

|                                                | Cycle-to-cycle jitter for clock output on                              | $F_{OUT} \ge 100 \text{ MHz}$ | -      | -       | 650        | ps (p-p)  |

|                                                | regular I/O in fractional PLL                                          | $F_{OUT}$ < 100 MHz           | -      | -       | 65         | mUI (p-p) |

| t <sub>CASC_OUTPJ_DC</sub> <sup>(58)(62)</sup> | Period jitter for dedicated clock output in                            | $F_{OUT} \ge 100 \text{ MHz}$ | _      | _       | 300        | ps (p-p)  |

|                                                | cascaded PLLs                                                          | F <sub>OUT</sub> < 100 MHz    | _      | _       | 30         | mUI (p-p) |

| t <sub>DRIFT</sub>                             | Frequency drift after PFDENA is disabled for a duration of 100 $\mu s$ | _                             | _      | _       | ±10        | %         |

| dK <sub>BIT</sub>                              | Bit number of Delta Sigma Modulator (DSM)                              | _                             | 8      | 24      | 32         | Bits      |

| kvalue                                         | Numerator of fraction                                                  | _                             | 128    | 8388608 | 2147483648 | _         |

| f <sub>RES</sub>                               | Resolution of VCO frequency                                            | $f_{INPFD} = 100 \text{ MHz}$ | 390625 | 5.96    | 0.023      | Hz        |

## **Related Information**

Memory Output Clock Jitter Specifications on page 49

Provides more information about the external memory interface clock output jitter specifications.

- Upstream PLL: 0.59 MHz  $\leq$  Upstream PLL BW < 1 MHz

- Downstream PLL: Downstream PLL BW > 2 MHz

<sup>&</sup>lt;sup>(61)</sup> This specification only covers fractional PLL for low bandwidth. The  $f_{VCO}$  for fractional value range 0.05–0.95 must be  $\geq$  1000 MHz.

<sup>&</sup>lt;sup>(62)</sup> The cascaded PLL specification is only applicable with the following conditions:

## **DSP Block Performance Specifications**

## Table 32. DSP Block Performance Specifications for Cyclone V Devices

|                            | Mode                                                     |     |          | Unit     |     |

|----------------------------|----------------------------------------------------------|-----|----------|----------|-----|

|                            |                                                          | -C6 | -C7, -I7 | -C8, -A7 |     |

| Modes using One DSP Block  | Independent 9 $\times$ 9 multiplication                  | 340 | 300      | 260      | MHz |

|                            | Independent 18 × 19 multiplication                       | 287 | 250      | 200      | MHz |

|                            | Independent 18 × 18 multiplication                       | 287 | 250      | 200      | MHz |

|                            | Independent 27 × 27 multiplication                       | 250 | 200      | 160      | MHz |

|                            | Independent 18 × 25 multiplication                       | 310 | 250      | 200      | MHz |

|                            | Independent 20 × 24 multiplication                       | 310 | 250      | 200      | MHz |

|                            | Two 18 $\times$ 19 multiplier adder mode                 | 310 | 250      | 200      | MHz |

|                            | $18 \times 18$ multiplier added summed with 36-bit input | 310 | 250      | 200      | MHz |

| Modes using Two DSP Blocks | Complex 18 × 19 multiplication                           | 310 | 250      | 200      | MHz |

## **Memory Block Performance Specifications**

To achieve the maximum memory block performance, use a memory block clock that comes through global clock routing from an on-chip PLL and set to 50% output duty cycle. Use the Intel Quartus Prime software to report timing for the memory block clocking schemes.

When you use the error detection cyclical redundancy check (CRC) feature, there is no degradation in f<sub>MAX</sub>.

## Table 33. Memory Block Performance Specifications for Cyclone V Devices

| Memory | Mode                                                     | Resources Used |        |     | Unit     |          |     |  |  |

|--------|----------------------------------------------------------|----------------|--------|-----|----------|----------|-----|--|--|

|        |                                                          | ALUTs          | Memory | -C6 | -C7, -I7 | -C8, -A7 |     |  |  |

| MLAB   | Single port, all supported widths                        | 0              | 1      | 420 | 350      | 300      | MHz |  |  |

|        | Simple dual-port, all supported widths                   | 0              | 1      | 420 | 350      | 300      | MHz |  |  |

|        | Simple dual-port with read and write at the same address | 0              | 1      | 340 | 290      | 240      | MHz |  |  |

|        | conti                                                    |                |        |     |          |          |     |  |  |

#### Cyclone V Device Datasheet

CV-51002 | 2018.05.07

| Memory     | Mode                                                                                                    | Resources Used |        |     | Unit     |          |     |

|------------|---------------------------------------------------------------------------------------------------------|----------------|--------|-----|----------|----------|-----|

|            |                                                                                                         | ALUTs          | Memory | -C6 | -C7, -I7 | -C8, -A7 |     |

|            | ROM, all supported width                                                                                | 0              | 1      | 420 | 350      | 300      | MHz |

| M10K Block | Single-port, all supported widths                                                                       | 0              | 1      | 315 | 275      | 240      | MHz |

|            | Simple dual-port, all supported widths                                                                  | 0              | 1      | 315 | 275      | 240      | MHz |

|            | Simple dual-port with the <b>read-during-write</b> option set to <b>Old Data</b> , all supported widths | 0              | 1      | 275 | 240      | 180      | MHz |

|            | True dual port, all supported widths                                                                    | 0              | 1      | 315 | 275      | 240      | MHz |

|            | ROM, all supported widths                                                                               | 0              | 1      | 315 | 275      | 240      | MHz |

## **Periphery Performance**

This section describes the periphery performance, high-speed I/O, and external memory interface.

Actual achievable frequency depends on design and system specific factors. Ensure proper timing closure in your design and perform HSPICE/IBIS simulations based on your specific design and system setup to determine the maximum achievable frequency in your system.

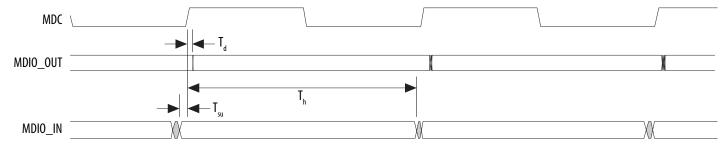

## Figure 13. MDIO Timing Diagram

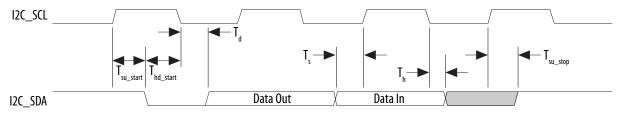

# I<sup>2</sup>C Timing Characteristics

| Table 51. I | <sup>2</sup> C Timing | <b>Requirements for</b> | Cyclone V Devices |

|-------------|-----------------------|-------------------------|-------------------|

|-------------|-----------------------|-------------------------|-------------------|

| Symbol                | Description                                       | Standa | rd Mode | Fast | Mode | Unit |

|-----------------------|---------------------------------------------------|--------|---------|------|------|------|

|                       |                                                   | Min    | Мах     | Min  | Мах  |      |

| T <sub>clk</sub>      | Serial clock (SCL) clock period                   | 10     | -       | 2.5  | -    | μs   |

| T <sub>clkhigh</sub>  | SCL high time                                     | 4.7    | -       | 0.6  | -    | μs   |

| T <sub>clklow</sub>   | SCL low time                                      | 4      | -       | 1.3  | -    | μs   |

| Ts                    | Setup time for serial data line (SDA) data to SCL | 0.25   | -       | 0.1  | -    | μs   |

| T <sub>h</sub>        | Hold time for SCL to SDA data                     | 0      | 3.45    | 0    | 0.9  | μs   |

| T <sub>d</sub>        | SCL to SDA output data delay                      | -      | 0.2     | -    | 0.2  | μs   |

| T <sub>su_start</sub> | Setup time for a repeated start condition         | 4.7    | -       | 0.6  | -    | μs   |

| T <sub>hd_start</sub> | Hold time for a repeated start condition          | 4      | -       | 0.6  | -    | μs   |

| T <sub>su_stop</sub>  | Setup time for a stop condition                   | 4      | -       | 0.6  | _    | μs   |

## Figure 14. I<sup>2</sup>C Timing Diagram

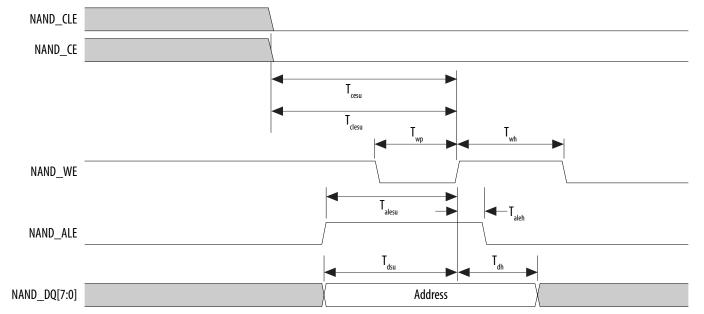

## **NAND Timing Characteristics**

#### Table 52. NAND ONFI 1.0 Timing Requirements for Cyclone V Devices

The NAND controller supports Open NAND FLASH Interface (ONFI) 1.0 Mode 5 timing as well as legacy NAND devices. This table lists the requirements for ONFI 1.0 mode 5 timing. The HPS NAND controller can meet this timing by programming the C4 output of the main HPS PLL and timing registers provided in the NAND controller.

| Symbol                             | Description                                     | Min | Мах | Unit      |

|------------------------------------|-------------------------------------------------|-----|-----|-----------|

| T <sub>wp</sub> <sup>(72)</sup>    | Write enable pulse width                        | 10  | -   | ns        |

| T <sub>wh</sub> <sup>(72)</sup>    | Write enable hold time                          | 7   | -   | ns        |

| T <sub>rp</sub> <sup>(72)</sup>    | Read enable pulse width                         | 10  | -   | ns        |

| T <sub>reh</sub> (72)              | Read enable hold time                           | 7   | -   | ns        |

| T <sub>clesu</sub> <sup>(72)</sup> | Command latch enable to write enable setup time | 10  | -   | ns        |

| T <sub>cleh</sub> <sup>(72)</sup>  | Command latch enable to write enable hold time  | 5   | -   | ns        |

| T <sub>cesu</sub> (72)             | Chip enable to write enable setup time          | 15  | -   | ns        |

| T <sub>ceh</sub> <sup>(72)</sup>   | Chip enable to write enable hold time           | 5   | _   | ns        |

| T <sub>alesu</sub> <sup>(72)</sup> | Address latch enable to write enable setup time | 10  | -   | ns        |

| T <sub>aleh</sub> <sup>(72)</sup>  | Address latch enable to write enable hold time  | 5   | -   | ns        |

| T <sub>dsu</sub> <sup>(72)</sup>   | Data to write enable setup time                 | 10  | _   | ns        |

| T <sub>dh</sub> (72)               | Data to write enable hold time                  | 5   | -   | ns        |

|                                    | •                                               |     |     | continued |

<sup>(72)</sup> Timing of the NAND interface is controlled through the NAND configuration registers.

## Figure 16. NAND Address Latch Timing Diagram

#### Cyclone V Device Datasheet CV-51002 | 2018.05.07

| Symbol              | Parameter                                                 | Minimum                                                  | Maximum | Unit   |

|---------------------|-----------------------------------------------------------|----------------------------------------------------------|---------|--------|

| t <sub>DH</sub>     | DATA[] hold time after rising edge on DCLK                | 0                                                        | -       | ns     |

| t <sub>CH</sub>     | DCLK high time                                            | $0.45 \times 1/f_{MAX}$                                  | -       | s      |

| t <sub>CL</sub>     | DCLK low time                                             | $0.45 \times 1/f_{MAX}$                                  | -       | S      |

| t <sub>CLK</sub>    | DCLK period                                               | 1/f <sub>MAX</sub>                                       | -       | S      |

| f <sub>MAX</sub>    | DCLK frequency                                            | -                                                        | 125     | MHz    |

| t <sub>CD2UM</sub>  | CONF_DONE high to user mode <sup>(92)</sup>               | 175                                                      | 437     | μs     |

| t <sub>CD2CU</sub>  | CONF_DONE high to CLKUSR enabled                          | 4 × maximum DCLK period                                  | _       | —      |

| t <sub>CD2UMC</sub> | CONF_DONE high to user mode with CLKUSR option on         | t <sub>CD2CU</sub> + (T <sub>init</sub> × CLKUSR period) | -       | _      |

| T <sub>init</sub>   | Number of clock cycles required for device initialization | 8,576                                                    | _       | Cycles |

## **Related Information**

## PS Configuration Timing

Provides the PS configuration timing waveform.

# Initialization

## Table 63. Initialization Clock Source Option and the Maximum Frequency for Cyclone V Devices

| Initialization Clock Source | Configuration Scheme | Maximum Frequency (MHz) | Minimum Number of Clock Cycles |

|-----------------------------|----------------------|-------------------------|--------------------------------|

| Internal Oscillator         | AS, PS, and FPP      | 12.5                    | T <sub>init</sub>              |

| CLKUSR <sup>(93)</sup>      | PS and FPP           | 125                     |                                |

|                             | AS                   | 100                     |                                |

| DCLK                        | PS and FPP           | 125                     |                                |

<sup>&</sup>lt;sup>(92)</sup> The minimum and maximum numbers apply only if you chose the internal oscillator as the clock source for initializing the device.

<sup>&</sup>lt;sup>(93)</sup> To enable CLKUSR as the initialization clock source, turn on the **Enable user-supplied start-up clock (CLKUSR)** option in the Intel Quartus Prime software from the **General** panel of the **Device and Pin Options** dialog box.

# **Configuration Files**

## Table 64. Uncompressed .rbf Sizes for Cyclone V Devices

Use this table to estimate the file size before design compilation. Different configuration file formats, such as a hexadecimal file (.hex) or tabular text file (.ttf) format, have different file sizes.

For the different types of configuration file and file sizes, refer to the Intel Quartus Prime software. However, for a specific version of the Intel Quartus Prime software, any design targeted for the same device has the same uncompressed configuration file size.

| Variant                      | Member Code | Configuration .rbf Size (bits) | IOCSR .rbf Size (bits) | <b>Recommended EPCQ Serial</b><br><b>Configuration Device</b> <sup>(94)</sup> |

|------------------------------|-------------|--------------------------------|------------------------|-------------------------------------------------------------------------------|

| Cyclone V E <sup>(95)</sup>  | A2          | 21,061,280                     | 275,608                | EPCQ64                                                                        |

|                              | A4          | 21,061,280                     | 275,608                | EPCQ64                                                                        |

|                              | A5          | 33,958,560                     | 322,072                | EPCQ128                                                                       |

|                              | Α7          | 56,167,552                     | 435,288                | EPCQ128                                                                       |

|                              | A9          | 102,871,776                    | 400,408                | EPCQ256                                                                       |

| Cyclone V GX                 | C3          | 14,510,912                     | 320,280                | EPCQ32                                                                        |

|                              | C4          | 33,958,560                     | 322,072                | EPCQ128                                                                       |

|                              | C5          | 33,958,560                     | 322,072                | EPCQ128                                                                       |

|                              | C7          | 56,167,552                     | 435,288                | EPCQ128                                                                       |

|                              | С9          | 102,871,776                    | 400,408                | EPCQ256                                                                       |

| Cyclone V GT                 | D5          | 33,958,560                     | 322,072                | EPCQ128                                                                       |

|                              | D7          | 56,167,552                     | 435,288                | EPCQ128                                                                       |

|                              | D9          | 102,871,776                    | 400,408                | EPCQ256                                                                       |

| Cyclone V SE <sup>(95)</sup> | A2          | 33,958,560                     | 322,072                | EPCQ128                                                                       |

|                              |             | · ·                            |                        | continue                                                                      |

The IOCSR raw binary file (.rbf) size is specifically for the Configuration via Protocol (CvP) feature.

<sup>(94)</sup> The recommended EPCQ serial configuration devices are able to store more than one image.

<sup>(95)</sup> No PCIe hard IP, configuration via protocol (CvP) is not supported in this family.

| Variant      | Member Code | Configuration .rbf Size (bits) | IOCSR .rbf Size (bits) | Recommended EPCQ Serial<br>Configuration Device <sup>(94)</sup> |

|--------------|-------------|--------------------------------|------------------------|-----------------------------------------------------------------|

|              | A4          | 33,958,560                     | 322,072                | EPCQ128                                                         |

|              | A5          | 56,057,632                     | 324,888                | EPCQ128                                                         |

|              | A6          | 56,057,632                     | 324,888                | EPCQ128                                                         |

| Cyclone V SX | C2          | 33,958,560                     | 322,072                | EPCQ128                                                         |

|              | C4          | 33,958,560                     | 322,072                | EPCQ128                                                         |

|              | C5          | 56,057,632                     | 324,888                | EPCQ128                                                         |

|              | C6          | 56,057,632                     | 324,888                | EPCQ128                                                         |

| Cyclone V ST | D5          | 56,057,632                     | 324,888                | EPCQ128                                                         |

|              | D6          | 56,057,632                     | 324,888                | EPCQ128                                                         |

# **Minimum Configuration Time Estimation**

## Table 65. Minimum Configuration Time Estimation for Cyclone V Devices

The estimated values are based on the configuration .rbf sizes in Uncompressed .rbf Sizes for Cyclone V Devices table.

| Variant     | Member Code | Active Serial <sup>(96)</sup> |            |                                    |       | Fast Passive Pa | rallel <sup>(97)</sup>             |

|-------------|-------------|-------------------------------|------------|------------------------------------|-------|-----------------|------------------------------------|

|             |             | Width                         | DCLK (MHz) | Minimum Configuration<br>Time (ms) | Width | DCLK (MHz)      | Minimum Configuration<br>Time (ms) |

| Cyclone V E | A2          | 4                             | 100        | 53                                 | 16    | 125             | 11                                 |

|             | A4          | 4                             | 100        | 53                                 | 16    | 125             | 11                                 |

|             | A5          | 4                             | 100        | 85                                 | 16    | 125             | 17                                 |

|             | A7          | 4                             | 100        | 140                                | 16    | 125             | 28                                 |

|             | -           |                               | •          | •                                  |       | -               | continued                          |

<sup>(94)</sup> The recommended EPCQ serial configuration devices are able to store more than one image.

- <sup>(96)</sup> DCLK frequency of 100 MHz using external CLKUSR.

- <sup>(97)</sup> Maximum FPGA FPP bandwidth may exceed bandwidth available from some external storage or control logic.

| Variant      | Member Code |       | Active Serial <sup>(96)</sup> |                                    |       | Fast Passive Parallel <sup>(97)</sup> |                                    |  |  |  |

|--------------|-------------|-------|-------------------------------|------------------------------------|-------|---------------------------------------|------------------------------------|--|--|--|

|              |             | Width | DCLK (MHz)                    | Minimum Configuration<br>Time (ms) | Width | DCLK (MHz)                            | Minimum Configuration<br>Time (ms) |  |  |  |

|              | A9          | 4     | 100                           | 257                                | 16    | 125                                   | 51                                 |  |  |  |

| Cyclone V GX | C3          | 4     | 100                           | 36                                 | 16    | 125                                   | 7                                  |  |  |  |

|              | C4          | 4     | 100                           | 85                                 | 16    | 125                                   | 17                                 |  |  |  |

|              | C5          | 4     | 100                           | 85                                 | 16    | 125                                   | 17                                 |  |  |  |

|              | C7          | 4     | 100                           | 140                                | 16    | 125                                   | 28                                 |  |  |  |

|              | C9          | 4     | 100                           | 257                                | 16    | 125                                   | 51                                 |  |  |  |

| Cyclone V GT | D5          | 4     | 100                           | 85                                 | 16    | 125                                   | 17                                 |  |  |  |

|              | D7          | 4     | 100                           | 140                                | 16    | 125                                   | 28                                 |  |  |  |

|              | D9          | 4     | 100                           | 257                                | 16    | 125                                   | 51                                 |  |  |  |

| Cyclone V SE | A2          | 4     | 100                           | 85                                 | 16    | 125                                   | 17                                 |  |  |  |

|              | A4          | 4     | 100                           | 85                                 | 16    | 125                                   | 17                                 |  |  |  |

|              | A5          | 4     | 100                           | 140                                | 16    | 125                                   | 28                                 |  |  |  |

|              | A6          | 4     | 100                           | 140                                | 16    | 125                                   | 28                                 |  |  |  |

| Cyclone V SX | C2          | 4     | 100                           | 85                                 | 16    | 125                                   | 17                                 |  |  |  |

|              | C4          | 4     | 100                           | 85                                 | 16    | 125                                   | 17                                 |  |  |  |

|              | C5          | 4     | 100                           | 140                                | 16    | 125                                   | 28                                 |  |  |  |

|              | C6          | 4     | 100                           | 140                                | 16    | 125                                   | 28                                 |  |  |  |

| Cyclone V ST | D5          | 4     | 100                           | 140                                | 16    | 125                                   | 28                                 |  |  |  |

|              | D6          | 4     | 100                           | 140                                | 16    | 125                                   | 28                                 |  |  |  |

<sup>(96)</sup> DCLK frequency of 100 MHz using external CLKUSR.

<sup>(97)</sup> Maximum FPGA FPP bandwidth may exceed bandwidth available from some external storage or control logic.

Excel-based I/O timing provides pin timing performance for each device density and speed grade. The data is typically used prior to designing the FPGA to get an estimate of the timing budget as part of the link timing analysis.

The Intel Quartus Prime Timing Analyzer provides a more accurate and precise I/O timing data based on the specifics of the design after you complete place-and-route.

## **Related Information**

#### Cyclone V I/O Timing Spreadsheet

Provides the Cyclone V Excel-based I/O timing spreadsheet.

# **Programmable IOE Delay**

| Parameter <sup>(100</sup> | Parameter <sup>(100</sup> Available Minimum<br>) Settings Offset <sup>(101)</sup> |            |            | 1odel Slow Model |       |       |       |       | Unit  |    |

|---------------------------|-----------------------------------------------------------------------------------|------------|------------|------------------|-------|-------|-------|-------|-------|----|

| ,                         |                                                                                   | Industrial | Commercial | -C6              | -C7   | -C8   | -17   | -A7   |       |    |

| D1                        | 32                                                                                | 0          | 0.508      | 0.517            | 0.971 | 1.187 | 1.194 | 1.179 | 1.160 | ns |

| D3                        | 8                                                                                 | 0          | 1.761      | 1.793            | 3.291 | 4.022 | 3.961 | 3.999 | 3.929 | ns |

| D4                        | 32                                                                                | 0          | 0.510      | 0.519            | 1.180 | 1.187 | 1.195 | 1.180 | 1.160 | ns |

| D5                        | 32                                                                                | 0          | 0.508      | 0.517            | 0.970 | 1.186 | 1.194 | 1.179 | 1.179 | ns |

#### Table 68. I/O element (IOE) Programmable Delay for Cyclone V Devices

<sup>(101</sup> Minimum offset does not include the intrinsic delay.

<sup>(100</sup> You can set this value in the Intel Quartus Prime software by selecting D1, D3, D4, and D5 in the Assignment Name column of

) Assignment Editor.

<sup>)</sup>

# **Document Revision History for Cyclone V Device Datasheet**

| Document<br>Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2018.05.07          | <ul> <li>Added description about the low-power option ("L" suffix) for Cyclone V SE and SX devices.</li> <li>Added the <i>Cyclone V Devices Overshoot Duration</i> diagram.</li> <li>Removed the description on SD/MMC interface calibration support in the <i>Secure Digital (SD)/MultiMediaCard (MMC) Timing Requirements for Cyclone V Devices</i> table. This feature is currently supported in the preloader.</li> <li>Removed the note to Cyclone V SE A2 and A4 devices, and Cyclone V SX C2 and C4 devices in the <i>Uncompressed .rbf Sizes for Cyclone V Devices</i> table. These devices are currently supported in the Intel Quartus Prime software.</li> <li>Removed PowerPlay text from tool name.</li> <li>Updated the IP name from ALTREMOTE_UPDATE to Remote Update Intel FPGA IP.</li> <li>Rebranded as Intel.</li> <li>Added the Low Power Variants table and the estimating power consumption steps to the "Cyclone V Device Datasheet" Overview section.</li> <li>Updated the minimum value for t<sub>DH</sub> to 2.5 for -6 speed grade/2.9 for -7 and -8 speed grade.</li> </ul> |

| Date          | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 2016 | 2016.12.09 | <ul> <li>Updated V<sub>ICM</sub> (AC coupled) specifications for 1.5 V PCML in Receiver Specifications for Cyclone V GX, GT, SX, and ST Devices table.</li> <li>Added maximum specification for T<sub>d</sub> in Management Data Input/Output (MDIO) Timing Requirements for Cyclone V Devices table.</li> <li>Updated T<sub>init</sub> specifications in the following tables:         <ul> <li>FPP Timing Parameters When DCLK-to-DATA[] Ratio is 1 for Cyclone V Devices</li> <li>FPP Timing Parameters When DCLK-to-DATA[] Ratio is &gt;1 for Cyclone V Devices</li> <li>AS Timing Parameters for AS ×1 and ×4 Configurations in Cyclone V Devices</li> <li>PS Timing Parameters for Cyclone V Devices</li> </ul> </li> </ul> |

| June 2016     | 2016.06.10 | <ul> <li>Changed pin capacitance to maximum values.</li> <li>Updated SPI Master Timing Requirements for Cyclone V Devices table.         <ul> <li>Added T<sub>su</sub> and T<sub>h</sub> specifications.</li> <li>Removed T<sub>dinmax</sub> specifications.</li> </ul> </li> <li>Updated SPI Master Timing Diagram.</li> <li>Updated T<sub>clk</sub> spec from maximum to minimum in I<sup>2</sup>C Timing Requirements for Cyclone V Devices table.</li> </ul>                                                                                                                                                                                                                                                                  |

|               |            | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### Cyclone V Device Datasheet

CV-51002 | 2018.05.07

| Date          | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 2015 | 2015.12.04 | <ul> <li>Updated Quad Serial Peripheral Interface (SPI) Flash Timing Requirements for Cyclone V Devices table.</li> <li>Updated F<sub>clk</sub>, T<sub>dutycycle</sub>, and T<sub>dssfrst</sub> specifications.</li> <li>Added T<sub>qspi_clk</sub>, T<sub>din_start</sub>, and T<sub>din_end</sub> specifications.</li> <li>Removed T<sub>dinmax</sub> specification for T<sub>clk</sub> to 16.67 ns and removed the maximum specification in SPI Master Timing Requirements for Cyclone V Devices table.</li> <li>Updated Secure Digital (SD)/MultiMediaCard (MMC) Timing Requirements for Cyclone V Devices table.</li> <li>Updated T<sub>clk</sub> to T<sub>sdmmc_clk_out</sub> symbol.</li> <li>Updated T<sub>sdmmc_clk_out</sub> and T<sub>d</sub> specifications.</li> <li>Added T<sub>sdmmc_clk</sub>, T<sub>su</sub>, and T<sub>h</sub> specifications.</li> <li>Removed T<sub>dinmax</sub> specifications.</li> <li>Updated the following diagrams:</li> <li>Quad SPI Flash Timing Diagram</li> <li>SD/MMC Timing Diagram</li> <li>Updated configuration .rbf sizes for Cyclone V devices.</li> <li>Changed instances of <i>Quartus II</i> to <i>Quartus Prime</i>.</li> </ul> |

| June 2015     | 2015.06.12 | <ul> <li>Updated the supported data rates for the following output standards using true LVDS output buffer types in the High-Speed I/O Specifications for Cyclone V Devices table: <ul> <li>True RSDS output standard: data rates of up to 360 Mbps</li> <li>True mini-LVDS output standard: data rates of up to 400 Mbps</li> </ul> </li> <li>Changed Queued Serial Peripheral Interface (QSPI) to Quad Serial Peripheral Interface (SPI) Flash.</li> <li>Updated T<sub>h</sub> location in I<sup>2</sup>C Timing Diagram.</li> <li>Updated the maximum value for t<sub>CO</sub> from 4 ns to 2 ns in AS Timing Parameters for AS ×1 and ×4 Configurations in Cyclone V Devices table.</li> <li>Moved the following timing diagrams to the Configuration, Design Security, and Remote System Upgrades in Cyclone V Devices chapter.</li> <li>FPP Configuration Timing Waveform When DCLK-to-DATA[] Ratio is 1</li> <li>FPP Configuration Timing Waveform When DCLK-to-DATA[] Ratio is &gt;1</li> <li>AS Configuration Timing Waveform</li> <li>PS Configuration Timing Waveform</li> </ul>                                                                                              |

| March 2015    | 2015.03.31 | <ul> <li>Added V<sub>CC</sub> specifications for devices with internal scrubbing feature (with SC suffix) in Recommended Operating Conditions table.</li> <li>Corrected the unit for t<sub>DH</sub> from ns to s in FPP Timing Parameters When DCLK-to-DATA[] Ratio is &gt;1 for Cyclone V Devices table.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|               |            | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |