Welcome to **E-XFL.COM**

**Embedded - System On Chip (SoC):** The Heart of Modern Embedded Systems

**Embedded - System On Chip (SoC)** refers to an integrated circuit that consolidates all the essential components of a computer system into a single chip. This includes a microprocessor, memory, and other peripherals, all packed into one compact and efficient package. SoCs are designed to provide a complete computing solution, optimizing both space and power consumption, making them ideal for a wide range of embedded applications.

What are **Embedded - System On Chip (SoC)?**

**System On Chip (SoC)** integrates multiple functions of a computer or electronic system onto a single chip. Unlike traditional multi-chip solutions. SoCs combine a central

| Details                 |                                                                                    |

|-------------------------|------------------------------------------------------------------------------------|

| Product Status          | Active                                                                             |

| Architecture            | MCU, FPGA                                                                          |

| Core Processor          | Dual ARM® Cortex®-A9 MPCore™ with CoreSight™                                       |

| Flash Size              | -                                                                                  |

| RAM Size                | 64KB                                                                               |

| Peripherals             | DMA, POR, WDT                                                                      |

| Connectivity            | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, MMC/SD/SDIO, SPI, UART/USART, USB OTG |

| Speed                   | 600MHz                                                                             |

| Primary Attributes      | FPGA - 110K Logic Elements                                                         |

| Operating Temperature   | 0°C ~ 85°C (TJ)                                                                    |

| Package / Case          | 896-BGA                                                                            |

| Supplier Device Package | 896-FBGA (31x31)                                                                   |

| Purchase URL            | https://www.e-xfl.com/product-detail/intel/5csxfc6d6f31c8n                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Contents**

| clone V Device Datasheet                                    | 3  |

|-------------------------------------------------------------|----|

| Electrical Characteristics                                  |    |

| Operating Conditions                                        |    |

| Switching Characteristics                                   | 24 |

| Transceiver Performance Specifications                      | 25 |

| Core Performance Specifications                             | 40 |

| Periphery Performance                                       | 45 |

| HPS Specifications                                          | 51 |

| Configuration Specifications                                | 67 |

| POR Specifications                                          | 68 |

| FPGA JTAG Configuration Timing                              | 68 |

| FPP Configuration Timing                                    | 69 |

| Active Serial (AS) Configuration Timing                     | 73 |

| DCLK Frequency Specification in the AS Configuration Scheme | 74 |

| Passive Serial (PS) Configuration Timing                    |    |

| Initialization                                              | 75 |

| Configuration Files                                         | 76 |

| Minimum Configuration Time Estimation                       |    |

| Remote System Upgrades                                      |    |

| User Watchdog Internal Oscillator Frequency Specifications  |    |

| I/O Timing                                                  |    |

| Programmable IOE Delay                                      |    |

| Programmable Output Buffer Delay                            |    |

| Glossary                                                    |    |

| Document Revision History for Cyclone V Device Datasheet    | 88 |

# **Cyclone V Device Datasheet**

This datasheet describes the electrical characteristics, switching characteristics, configuration specifications, and I/O timing for Cyclone® V devices.

Cyclone V devices are offered in commercial and industrial grades. Commercial devices are offered in -C6 (fastest), -C7, and -C8 speed grades. Industrial grade devices are offered in the -I7 speed grade. Automotive devices are offered in the -A7 speed grade.

Cyclone V SoC devices are also offered in a low-power variant, as indicated by the L power option in the device part number. These devices have 30% static power reduction for devices with 25K LE and 40K LE, and 20% static power reduction for devices with 85K LE and 110K LE. Note that the L power option devices are only available in –I7 speed grade, and have the equivalent operating conditions and timing specifications as the standard –I7 speed grade devices.

**Table 1.** Low Power Variants

| Density | Ordering Part Number (OPN) | Static Power Reduction |  |

|---------|----------------------------|------------------------|--|

| 25K LE  | 5K LE 5CSEBA2U19I7LN       |                        |  |

|         | 5CSEBA2U23I7LN             |                        |  |

|         | 5CSXFC2C6U23I7LN           |                        |  |

| 40K LE  | 5CSEBA4U19I7LN             |                        |  |

|         | 5CSEBA4U23I7LN             |                        |  |

|         | 5CSXFC4C6U23I7LN           |                        |  |

| 85K LE  | 5CSEBA5U19I7LN             | 20%                    |  |

|         | 5CSEBA5U23I7LN             |                        |  |

|         | 5CSXC5C6U23I7LN            |                        |  |

|         |                            | continued              |  |

Intel Corporation. All rights reserved. Intel, the Intel logo, Altera, Arria, Cyclone, Enpirion, MAX, Nios, Quartus and Stratix words and logos are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. Intel warrants performance of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2008 Registered

| Symbol                          | <b>Description</b> Condition                  |       | Minimum <sup>(11)</sup> | Typical | Maximum <sup>(11)</sup> | Unit |

|---------------------------------|-----------------------------------------------|-------|-------------------------|---------|-------------------------|------|

|                                 |                                               | 1.8 V | 1.71                    | 1.8     | 1.89                    | V    |

| V <sub>CCPLL_HPS</sub>          | HPS PLL analog voltage regulator power supply | _     | 2.375                   | 2.5     | 2.625                   | V    |

| V <sub>CC_AUX_SHARED</sub> (14) | HPS auxiliary power supply                    | _     | 2.375                   | 2.5     | 2.625                   | V    |

#### **Related Information**

Recommended Operating Conditions on page 8

Provides the steady-state voltage values for the FPGA portion of the device.

#### **DC Characteristics**

#### **Supply Current and Power Consumption**

Intel offers two ways to estimate power for your design—the Excel-based EPE and the Intel® Quartus® Prime Power Analyzer feature.

Use the Excel-based EPE before you start your design to estimate the supply current for your design. The EPE provides a magnitude estimate of the device power because these currents vary greatly with the resources you use.

The Intel Quartus Prime Power Analyzer provides better quality estimates based on the specifics of the design after you complete place-and-route. The Power Analyzer can apply a combination of user-entered, simulation-derived, and estimated signal activities that, when combined with detailed circuit models, yields very accurate power estimates.

#### **Related Information**

- Early Power Estimator User Guide

Provides more information about power estimation tools.

- Power Analysis chapter, Intel Quartus Prime Handbook Provides more information about power estimation tools.

<sup>(11)</sup> The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.

<sup>(14)</sup> V<sub>CC\_AUX\_SHARED</sub> must be powered by the same source as V<sub>CC\_AUX</sub> for Cyclone V SX C5, C6, D5, and D6 devices, and Cyclone V SE A5 and A6 devices.

## **Pin Capacitance**

**Table 12.** Pin Capacitance for Cyclone V Devices

| Symbol             | Description                                                      | Maximum | Unit |

|--------------------|------------------------------------------------------------------|---------|------|

| C <sub>IOTB</sub>  | Input capacitance on top and bottom I/O pins                     | 6       | pF   |

| C <sub>IOLR</sub>  | Input capacitance on left and right I/O pins                     | 6       | pF   |

| C <sub>OUTFB</sub> | Input capacitance on dual-purpose clock output and feedback pins | 6       | pF   |

## **Hot Socketing**

**Table 13.** Hot Socketing Specifications for Cyclone V Devices

| Symbol                    | Description                                                   | Maximum           | Unit |

|---------------------------|---------------------------------------------------------------|-------------------|------|

| I <sub>IOPIN (DC)</sub>   | DC current per I/O pin                                        | 300               | μΑ   |

| I <sub>IOPIN (AC)</sub>   | AC current per I/O pin                                        | 8 <sup>(15)</sup> | mA   |

| I <sub>XCVR-TX</sub> (DC) | CCVR-TX (DC)  DC current per transceiver transmitter (TX) pin |                   | mA   |

| I <sub>XCVR-RX</sub> (DC) | DC current per transceiver receiver (RX) pin                  | 50                | mA   |

# **Internal Weak Pull-Up Resistor**

All I/O pins, except configuration, test, and JTAG pins, have an option to enable weak pull-up.

<sup>(15)</sup> The I/O ramp rate is 10 ns or more. For ramp rates faster than 10 ns,  $|I_{IOPIN}| = C dv/dt$ , in which C is the I/O pin capacitance and dv/dt is the slew rate.

## **Differential I/O Standard Specifications**

#### Table 20. Differential I/O Standard Specifications for Cyclone V Devices

Differential inputs are powered by  $V_{\text{CCPD}}$  which requires 2.5 V.

| I/O Standard               | ,      | V <sub>CCIO</sub> (V) |       |     | $V_{ID} (mV)^{(21)}$ $V_{ICM(DC)} (V)$ $V_{OD} (V)^{(22)}$ |     | $V_{ID} (mV)^{(21)}$ $V_{ICM(DC)} (V)$ $V_{OD} (V)^{(22)}$ |                                | $V_{ID} (mV)^{(21)}$ $V_{ICM(DC)} (V)$ $V_{OD} (V)^{(22)}$ |       | $V_{ID} (mV)^{(21)}$ $V_{ICM(DC)} (V)$ $V_{OD} (V)^{(22)}$ |     | V <sub>ID</sub> (mV) <sup>(21)</sup> |            | V <sub>ICM(DC)</sub> (V) V <sub>OD</sub> (V) <sup>(22)</sup> V |  | $V_{ICM(DC)}(V)$ $V_{OD}(V)^{(22)}$ $V_{OCM}(V)^{(22)}$ |  | $V_{OD}(V)^{(22)}$ |  | <sub>M</sub> (V) <sup>(22)</sup> | (23) |

|----------------------------|--------|-----------------------|-------|-----|------------------------------------------------------------|-----|------------------------------------------------------------|--------------------------------|------------------------------------------------------------|-------|------------------------------------------------------------|-----|--------------------------------------|------------|----------------------------------------------------------------|--|---------------------------------------------------------|--|--------------------|--|----------------------------------|------|

|                            | Min    | Тур                   | Max   | Min | Condition                                                  | Max | Min                                                        | Condition                      | Max                                                        | Min   | Тур                                                        | Max | Min                                  | Тур        | Max                                                            |  |                                                         |  |                    |  |                                  |      |

| PCML                       | Transm | itter, rece           |       |     | ence clock pins<br>fications, refer                        |     |                                                            |                                |                                                            |       |                                                            |     |                                      | nd referen | ce clock                                                       |  |                                                         |  |                    |  |                                  |      |

| 2.5 V LVDS <sup>(24)</sup> | 2.375  | 2.5                   | 2.625 | 100 | V <sub>CM</sub> = 1.25<br>V                                | _   | 0.05                                                       | D <sub>MAX</sub> ≤ 700<br>Mbps | 1.80                                                       | 0.247 | _                                                          | 0.6 | 1.125                                | 1.25       | 1.375                                                          |  |                                                         |  |                    |  |                                  |      |

|                            |        |                       |       |     |                                                            |     | 1.05                                                       | D <sub>MAX</sub> > 700<br>Mbps | 1.55                                                       |       |                                                            |     |                                      |            |                                                                |  |                                                         |  |                    |  |                                  |      |

| BLVDS <sup>(25)(26)</sup>  | 2.375  | 2.5                   | 2.625 | 100 | _                                                          | _   | -                                                          | _                              | _                                                          | _     | _                                                          | _   | _                                    | -          | _                                                              |  |                                                         |  |                    |  |                                  |      |

| RSDS (HIO) <sup>(27)</sup> | 2.375  | 2.5                   | 2.625 | 100 | V <sub>CM</sub> = 1.25<br>V                                | _   | 0.25                                                       | _                              | 1.45                                                       | 0.1   | 0.2                                                        | 0.6 | 0.5                                  | 1.2        | 1.4                                                            |  |                                                         |  |                    |  |                                  |      |

| Mini-LVDS (HIO)            | 2.375  | 2.5                   | 2.625 | 200 | _                                                          | 600 | 0.300                                                      | _                              | 1.425                                                      | 0.25  | _                                                          | 0.6 | 1                                    | 1.2        | 1.4                                                            |  |                                                         |  |                    |  |                                  |      |

|                            | •      |                       |       |     |                                                            |     | •                                                          |                                |                                                            |       |                                                            |     |                                      | cont       | inued                                                          |  |                                                         |  |                    |  |                                  |      |

$<sup>^{(21)}</sup>$  The minimum  $V_{\text{ID}}$  value is applicable over the entire common mode range,  $V_{\text{CM}}.$

<sup>&</sup>lt;sup>(22)</sup>  $R_L$  range:  $90 \le R_L \le 110 \Omega$ .

<sup>(23)</sup> This applies to default pre-emphasis setting only.

<sup>(24)</sup> For optimized LVDS receiver performance, the receiver voltage input range must be within 1.0 V to 1.6 V for data rate above 700 Mbps and 0.00 V to 1.85 V for data rate below 700 Mbps.

<sup>(25)</sup> There are no fixed  $V_{ICM}$ ,  $V_{OD}$ , and  $V_{OCM}$  specifications for BLVDS. They depend on the system topology.

<sup>(26)</sup> For more information about BLVDS interface support in Intel devices, refer to AN522: Implementing Bus LVDS Interface in Supported Intel Device Families.

<sup>(27)</sup> For optimized RSDS receiver performance, the receiver voltage input range must be within 0.25 V to 1.45 V.

<sup>(28)</sup> For optimized mini-LVDS receiver performance, the receiver voltage input range must be within 0.300 V to 1.425 V.

# Typical TX $V_{OD}$ Setting for Cyclone V Transceiver Channels with termination of 100 $\Omega$

# Table 27. Typical TX $V_{OD}$ Setting for Cyclone V Transceiver Channels with termination of 100 $\Omega$

| Symbol                               | V <sub>OD</sub> Setting <sup>(48)</sup> | V <sub>OD</sub> Value (mV) | V <sub>OD</sub> Setting <sup>(48)</sup> | V <sub>OD</sub> Value (mV) |

|--------------------------------------|-----------------------------------------|----------------------------|-----------------------------------------|----------------------------|

| OD differential peak-to-peak typical | 6(49)                                   | 120                        | 34                                      | 680                        |

|                                      | 7 <sup>(49)</sup>                       | 140                        | 35                                      | 700                        |

|                                      | 8(49)                                   | 160                        | 36                                      | 720                        |

|                                      | 9                                       | 180                        | 37                                      | 740                        |

|                                      | 10                                      | 200                        | 38                                      | 760                        |

|                                      | 11                                      | 220                        | 39                                      | 780                        |

|                                      | 12                                      | 240                        | 40                                      | 800                        |

|                                      | 13                                      | 260                        | 41                                      | 820                        |

|                                      | 14                                      | 280                        | 42                                      | 840                        |

|                                      | 15                                      | 300                        | 43                                      | 860                        |

|                                      | 16                                      | 320                        | 44                                      | 880                        |

|                                      | 17                                      | 340                        | 45                                      | 900                        |

|                                      | 18                                      | 360                        | 46                                      | 920                        |

|                                      | 19                                      | 380                        | 47                                      | 940                        |

|                                      | 20                                      | 400                        | 48                                      | 960                        |

|                                      | 21                                      | 420                        | 49                                      | 980                        |

|                                      | 22                                      | 440                        | 50                                      | 1000                       |

|                                      | 23                                      | 460                        | 51                                      | 1020                       |

|                                      | 24                                      | 480                        | 52                                      | 1040                       |

|                                      |                                         | •                          |                                         | continu                    |

<sup>(48)</sup> Convert these values to their binary equivalent form if you are using the dynamic reconfiguration mode for PMA analog controls.

<sup>(49)</sup> Only valid for data rates  $\leq$  5 Gbps.

#### Cyclone V Device Datasheet

CV-51002 | 2018.05.07

| Protocol                       | Sub-protocol                 | Data Rate (Mbps) |

|--------------------------------|------------------------------|------------------|

|                                | CPRI E12LV                   | 1,228.8          |

|                                | CPRI E12HV                   | 1,228.8          |

|                                | CPRI E12LVII                 | 1,228.8          |

|                                | CPRI E24LV                   | 2,457.6          |

|                                | CPRI E24LVII                 | 2,457.6          |

|                                | CPRI E30LV                   | 3,072            |

|                                | CPRI E30LVII                 | 3,072            |

|                                | CPRI E48LVII <sup>(51)</sup> | 4,915.2          |

|                                | CPRI E60LVII <sup>(51)</sup> | 6,144            |

| Gbps Ethernet (GbE)            | GbE 1250                     | 1,250            |

| OBSAI                          | OBSAI 768                    | 768              |

|                                | OBSAI 1536                   | 1,536            |

|                                | OBSAI 3072                   | 3,072            |

| Serial digital interface (SDI) | SDI 270 SD                   | 270              |

|                                | SDI 1485 HD                  | 1,485            |

|                                | SDI 2970 3G                  | 2,970            |

| VbyOne                         | VbyOne 3750                  | 3,750            |

| HiGig+                         | HIGIG 3750                   | 3,750            |

#### **Related Information**

• PCIe Supported Configurations and Placement Guidelines

Provides more information about the maximum full duplex channels recommended in Cyclone V GT and ST devices which require full compliance to the PCIe Gen2 transmit jitter specification.

<sup>(51)</sup> For CPRI E48LVII and E60LVII, Intel recommends increasing the V<sub>CCE\_GXBL</sub> and V<sub>CCL\_GXBL</sub> typical value from 1.1 V to 1.2 V for full compliance to CPRI transmit jitter specification at 4.9152 Gbps (Cyclone V GT and ST devices) and 6.144 Gbps (Cyclone V GT and ST devices for CPRI 6.144 Gbps, refer to the *Transceiver Protocol Configurations in Cyclone V Devices* chapter.

|                 | Symbol                                  | Condition                                                                        |      | -C6 |                     |      | -C7, -I7 |                     |      | -C8, -A7 |                     |      |

|-----------------|-----------------------------------------|----------------------------------------------------------------------------------|------|-----|---------------------|------|----------|---------------------|------|----------|---------------------|------|

|                 |                                         |                                                                                  | Min  | Тур | Max                 | Min  | Тур      | Max                 | Min  | Тур      | Max                 |      |

|                 |                                         | Emulated<br>Differential I/O<br>Standards                                        |      |     |                     |      |          |                     |      |          |                     |      |

|                 | t <sub>RISE</sub> and t <sub>FALL</sub> | True Differential I/O Standards                                                  | _    | _   | 200                 | _    | _        | 200                 | _    | _        | 200                 | ps   |

|                 |                                         | Emulated Differential I/O Standards with Three External Output Resistor Networks | _    | _   | 250                 | _    | _        | 250                 | _    | _        | 300                 | ps   |

|                 |                                         | Emulated Differential I/O Standards with One External Output Resistor Network    | _    | _   | 300                 | _    | _        | 300                 | _    | _        | 300                 | ps   |

|                 | TCCS                                    | True Differential I/O Standards                                                  | _    | _   | 200                 | _    | _        | 250                 | _    | _        | 250                 | ps   |

|                 |                                         | Emulated Differential I/O Standards with Three External Output Resistor Networks | _    | _   | 300                 | _    | _        | 300                 | _    | _        | 300                 | ps   |

|                 |                                         | Emulated Differential I/O Standards with One External Output Resistor Network    | _    | _   | 300                 | _    | _        | 300                 | _    | _        | 300                 | ps   |

| Receiver        | f <sub>HSDR</sub> (data rate)           | SERDES factor J<br>=4 to 10 <sup>(64)</sup>                                      | (65) | _   | 875 <sup>(67)</sup> | (65) | _        | 840 <sup>(67)</sup> | (65) | _        | 640 <sup>(67)</sup> | Mbps |

|                 |                                         | SERDES factor J<br>= 1 to 2, uses<br>DDR registers                               | (65) | _   | (66)                | (65) | _        | (66)                | (65) | _        | (66)                | Mbps |

| Sampling Windov | V                                       | _                                                                                | _    | _   | 350                 | _    | _        | 350                 | _    | _        | 350                 | ps   |

## **HPS PLL Specifications**

#### **HPS PLL VCO Frequency Range**

Table 41. **HPS PLL VCO Frequency Range for Cyclone V Devices**

| Description | Speed Grade        | Minimum | Maximum   | Unit |

|-------------|--------------------|---------|-----------|------|

| VCO range   | -C7, -I7, -A7, -C8 | 320     | 320 1,600 |      |

|             | -C6                | 320     | 1,850     | MHz  |

#### **HPS PLL Input Clock Range**

The HPS PLL input clock range is 10 – 50 MHz. This clock range applies to both HPS CLK1 and HPS CLK2 inputs.

#### **Related Information**

Clock Select, Booting and Configuration chapter

Provides more information about the clock range for different values of clock select (CSEL).

#### **HPS PLL Input Jitter**

Use the following equation to determine the maximum input jitter (peak-to-peak) the HPS PLLs can tolerate. The divide value (N) is the value programmed into the denominator field of the VCO register for each PLL. The PLL input reference clock is divided by this value. The range of the denominator is 1 to 64.

Maximum input jitter = Input clock period  $\times$  Divide value (N)  $\times$  0.02

Table 42. **Examples of Maximum Input Jitter**

| Input Reference Clock Period | Divide Value (N) | Maximum Jitter | Unit |

|------------------------------|------------------|----------------|------|

| 40 ns                        | 1                | 0.8            | ns   |

| 40 ns                        | 2                | 1.6            | ns   |

| 40 ns                        | 4                | 3.2            | ns   |

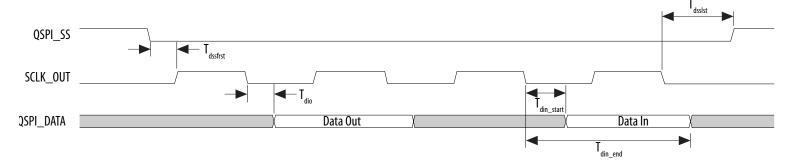

# **Quad SPI Flash Timing Characteristics**

Table 43. Quad Serial Peripheral Interface (SPI) Flash Timing Requirements for Cyclone V Devices

| Symbol                 | Description                                        | Min  | Тур                      | Max                                                | Unit |

|------------------------|----------------------------------------------------|------|--------------------------|----------------------------------------------------|------|

| F <sub>clk</sub>       | SCLK_OUT clock frequency (External clock)          | _    | _                        | 108                                                | MHz  |

| T <sub>qspi_clk</sub>  | QSPI_CLK clock period (Internal reference clock)   | 2.32 | _                        | _                                                  | ns   |

| T <sub>dutycycle</sub> | SCLK_OUT duty cycle                                | 45   | _                        | 55                                                 | %    |

| T <sub>dssfrst</sub>   | Output delay QSPI_SS valid before first clock edge | -    | 1/2 cycle of<br>SCLK_OUT | _                                                  | ns   |

| T <sub>dsslst</sub>    | Output delay QSPI_SS valid after last clock edge   | -1   | _                        | 1                                                  | ns   |

| T <sub>dio</sub>       | I/O data output delay                              | -1   | _                        | 1                                                  | ns   |

| T <sub>din_start</sub> | Input data valid start                             | _    | _                        | $(2 + R_{delay}) \times T_{qspi\_clk} - 7.52$ (68) | ns   |

| T <sub>din_end</sub>   | Input data valid end                               |      | _                        | _                                                  | ns   |

Figure 6. Quad SPI Flash Timing Diagram

This timing diagram illustrates clock polarity mode 0 and clock phase mode 0.

$R_{delay}$  is set by programming the register <code>qspiregs.rddatacap</code>. For the SoC EDS software version 13.1 and later, Intel provides automatic Quad SPI calibration in the preloader. For more information about  $R_{delay}$ , refer to the Quad SPI Flash Controller chapter in the Cyclone V Hard Processor System Technical Reference Manual.

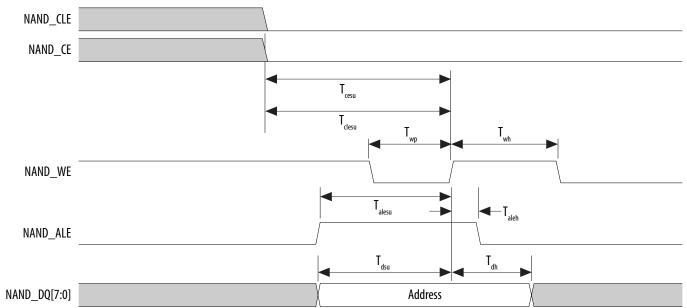

Figure 16. NAND Address Latch Timing Diagram

| Configuration Scheme | Encryption | Compression | DCLK-to-DATA[] Ratio (r) |

|----------------------|------------|-------------|--------------------------|

|                      | On         | Off         | 2                        |

|                      | Off        | On          | 4                        |

|                      | On         | On          | 4                        |

# **FPP** Configuration Timing when DCLK-to-DATA[] = 1

When you enable decompression or the design security feature, the DCLK-to-DATA[] ratio varies for FPP  $\times 8$  and FPP  $\times 16$ . For the respective DCLK-to-DATA[] ratio, refer to the DCLK-to-DATA[] Ratio for Cyclone V Devices table.

Table 58. FPP Timing Parameters When DCLK-to-DATA[] Ratio is 1 for Cyclone V Devices

| Symbol                             | Parameter                                    | Minimum                   | Maximum              | Unit      |

|------------------------------------|----------------------------------------------|---------------------------|----------------------|-----------|

| t <sub>CF2CD</sub>                 | nCONFIG low to CONF_DONE low                 | _                         | 600                  | ns        |

| t <sub>CF2ST0</sub>                | nCONFIG low to nSTATUS low                   | _                         | 600                  | ns        |

| t <sub>CFG</sub>                   | nCONFIG low pulse width                      | 2                         | _                    | μs        |

| t <sub>STATUS</sub>                | nSTATUS low pulse width                      | 268                       | 1506 <sup>(77)</sup> | μs        |

| t <sub>CF2ST1</sub>                | nCONFIG high to nSTATUS high                 | _                         | 1506 <sup>(78)</sup> | μs        |

| t <sub>CF2CK</sub> <sup>(79)</sup> | nCONFIG high to first rising edge on DCLK    | 1506                      | _                    | μs        |

| t <sub>ST2CK</sub> <sup>(79)</sup> | nSTATUS high to first rising edge of DCLK    | 2                         | _                    | μs        |

| t <sub>DSU</sub>                   | DATA[] setup time before rising edge on DCLK | 5.5                       | _                    | ns        |

| t <sub>DH</sub>                    | DATA[] hold time after rising edge on DCLK   | 0                         | _                    | ns        |

| t <sub>CH</sub>                    | DCLK high time                               | 0.45 × 1/f <sub>MAX</sub> | _                    | s         |

|                                    |                                              |                           |                      | continued |

<sup>(77)</sup> You can obtain this value if you do not delay configuration by extending the nCONFIG or the nSTATUS low pulse width.

$<sup>^{(78)}</sup>$  You can obtain this value if you do not delay configuration by externally holding the nSTATUS low.

$<sup>^{(79)}</sup>$  If nSTATUS is monitored, follow the  $t_{ST2CK}$  specification. If nSTATUS is not monitored, follow the  $t_{CF2CK}$  specification.

# **Configuration Files**

## Table 64. Uncompressed .rbf Sizes for Cyclone V Devices

Use this table to estimate the file size before design compilation. Different configuration file formats, such as a hexadecimal file (.hex) or tabular text file (.ttf) format, have different file sizes.

For the different types of configuration file and file sizes, refer to the Intel Quartus Prime software. However, for a specific version of the Intel Quartus Prime software, any design targeted for the same device has the same uncompressed configuration file size.

The IOCSR raw binary file (.rbf) size is specifically for the Configuration via Protocol (CvP) feature.

| Variant                     | Member Code | Configuration .rbf Size (bits) | IOCSR .rbf Size (bits) | Recommended EPCQ Serial Configuration Device <sup>(94)</sup> |

|-----------------------------|-------------|--------------------------------|------------------------|--------------------------------------------------------------|

| Cyclone V E <sup>(95)</sup> | A2          | 21,061,280                     | 275,608                | EPCQ64                                                       |

|                             | A4          | 21,061,280                     | 275,608                | EPCQ64                                                       |

|                             | A5          | 33,958,560                     | 322,072                | EPCQ128                                                      |

|                             | A7          | 56,167,552                     | 435,288                | EPCQ128                                                      |

|                             | A9          | 102,871,776                    | 400,408                | EPCQ256                                                      |

| Cyclone V GX                | C3          | 14,510,912                     | 320,280                | EPCQ32                                                       |

|                             | C4          | 33,958,560                     | 322,072                | EPCQ128                                                      |

|                             | C5          | 33,958,560                     | 322,072                | EPCQ128                                                      |

|                             | C7          | 56,167,552                     | 435,288                | EPCQ128                                                      |

|                             | C9          | 102,871,776                    | 400,408                | EPCQ256                                                      |

| Cyclone V GT                | D5          | 33,958,560                     | 322,072                | EPCQ128                                                      |

|                             | D7          | 56,167,552                     | 435,288                | EPCQ128                                                      |

|                             | D9          | 102,871,776                    | 400,408                | EPCQ256                                                      |

| Cyclone V SE (95)           | A2          | 33,958,560                     | 322,072                | EPCQ128                                                      |

| ·                           | ,           |                                |                        | continued                                                    |

<sup>(94)</sup> The recommended EPCQ serial configuration devices are able to store more than one image.

<sup>(95)</sup> No PCIe hard IP, configuration via protocol (CvP) is not supported in this family.

| Variant      | Member Code |       | Active Seria | al (96)                            |       | Fast Passive Pa | rallel <sup>(97)</sup>          |

|--------------|-------------|-------|--------------|------------------------------------|-------|-----------------|---------------------------------|

|              |             | Width | DCLK (MHz)   | Minimum Configuration<br>Time (ms) | Width | DCLK (MHz)      | Minimum Configuration Time (ms) |

|              | A9          | 4     | 100          | 257                                | 16    | 125             | 51                              |

| Cyclone V GX | C3          | 4     | 100          | 36                                 | 16    | 125             | 7                               |

|              | C4          | 4     | 100          | 85                                 | 16    | 125             | 17                              |

|              | C5          | 4     | 100          | 85                                 | 16    | 125             | 17                              |

|              | C7          | 4     | 100          | 140                                | 16    | 125             | 28                              |

|              | C9          | 4     | 100          | 257                                | 16    | 125             | 51                              |

| Cyclone V GT | D5          | 4     | 100          | 85                                 | 16    | 125             | 17                              |

|              | D7          | 4     | 100          | 140                                | 16    | 125             | 28                              |

|              | D9          | 4     | 100          | 257                                | 16    | 125             | 51                              |

| Cyclone V SE | A2          | 4     | 100          | 85                                 | 16    | 125             | 17                              |

|              | A4          | 4     | 100          | 85                                 | 16    | 125             | 17                              |

|              | A5          | 4     | 100          | 140                                | 16    | 125             | 28                              |

|              | A6          | 4     | 100          | 140                                | 16    | 125             | 28                              |

| Cyclone V SX | C2          | 4     | 100          | 85                                 | 16    | 125             | 17                              |

|              | C4          | 4     | 100          | 85                                 | 16    | 125             | 17                              |

|              | C5          | 4     | 100          | 140                                | 16    | 125             | 28                              |

|              | C6          | 4     | 100          | 140                                | 16    | 125             | 28                              |

| Cyclone V ST | D5          | 4     | 100          | 140                                | 16    | 125             | 28                              |

|              | D6          | 4     | 100          | 140                                | 16    | 125             | 28                              |

$<sup>^{(96)}\,</sup>$  DCLK frequency of 100 MHz using external CLKUSR.

<sup>(97)</sup> Maximum FPGA FPP bandwidth may exceed bandwidth available from some external storage or control logic.

Excel-based I/O timing provides pin timing performance for each device density and speed grade. The data is typically used prior to designing the FPGA to get an estimate of the timing budget as part of the link timing analysis.

The Intel Quartus Prime Timing Analyzer provides a more accurate and precise I/O timing data based on the specifics of the design after you complete place-and-route.

#### **Related Information**

Cyclone V I/O Timing Spreadsheet

Provides the Cyclone V Excel-based I/O timing spreadsheet.

# **Programmable IOE Delay**

I/O element (IOE) Programmable Delay for Cyclone V Devices Table 68.

| Parameter <sup>(100</sup> Available | Minimum<br>Offset <sup>(101)</sup> | Fast Model |            | Slow Model |       |       |       | Unit  |       |    |

|-------------------------------------|------------------------------------|------------|------------|------------|-------|-------|-------|-------|-------|----|

| ,                                   | Settings Offse                     |            | Industrial | Commercial | -C6   | -C7   | -C8   | -17   | -A7   |    |

| D1                                  | 32                                 | 0          | 0.508      | 0.517      | 0.971 | 1.187 | 1.194 | 1.179 | 1.160 | ns |

| D3                                  | 8                                  | 0          | 1.761      | 1.793      | 3.291 | 4.022 | 3.961 | 3.999 | 3.929 | ns |

| D4                                  | 32                                 | 0          | 0.510      | 0.519      | 1.180 | 1.187 | 1.195 | 1.180 | 1.160 | ns |

| D5                                  | 32                                 | 0          | 0.508      | 0.517      | 0.970 | 1.186 | 1.194 | 1.179 | 1.179 | ns |

<sup>(100</sup> You can set this value in the Intel Quartus Prime software by selecting **D1**, **D3**, **D4**, and **D5** in the **Assignment Name** column of ) Assignment Editor.

<sup>(101</sup> Minimum offset does not include the intrinsic delay.

## CV-51002 | 2018.05.07

| Date          | Version    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| December 2015 | 2015.12.04 | <ul> <li>Updated Quad Serial Peripheral Interface (SPI) Flash Timing Requirements for Cyclone V Devices table.         <ul> <li>Updated F<sub>clk</sub>, T<sub>dutycycle</sub>, and T<sub>dssfrst</sub> specifications.</li> <li>Added T<sub>qspi_clk</sub>, T<sub>din_start</sub>, and T<sub>din_end</sub> specifications.</li> <li>Removed T<sub>dinmax</sub> specifications.</li> </ul> </li> <li>Updated the minimum specification for T<sub>clk</sub> to 16.67 ns and removed the maximum specification in SPI Master Timing Requirements for Cyclone V Devices table.</li> <li>Updated Secure Digital (SD)/MultiMediaCard (MMC) Timing Requirements for Cyclone V Devices table.</li> <li>Updated T <sub>clk</sub> to T<sub>sdmmc_clk_out</sub> symbol.</li> <li>Updated T<sub>sdmmc_clk_out</sub> and T<sub>d</sub> specifications.</li> <li>Added T<sub>sdmmc_clk</sub>, T<sub>su</sub>, and T<sub>h</sub> specifications.</li> <li>Removed T<sub>dinmax</sub> specifications.</li> <li>Updated the following diagrams:         <ul> <li>Quad SPI Flash Timing Diagram</li> <li>Updated configuration .rbf sizes for Cyclone V devices.</li> </ul> </li> <li>Changed instances of <i>Quartus II</i> to <i>Quartus Prime</i>.</li> </ul> |

| June 2015     | 2015.06.12 | <ul> <li>Updated the supported data rates for the following output standards using true LVDS output buffer types in the High-Speed I/O Specifications for Cyclone V Devices table:         <ul> <li>True RSDS output standard: data rates of up to 360 Mbps</li> <li>True mini-LVDS output standard: data rates of up to 400 Mbps</li> </ul> </li> <li>Changed Queued Serial Peripheral Interface (QSPI) to Quad Serial Peripheral Interface (SPI) Flash.</li> <li>Updated T<sub>n</sub> location in I<sup>2</sup>C Timing Diagram.</li> <li>Updated T<sub>wp</sub> location in NAND Address Latch Timing Diagram.</li> <li>Updated the maximum value for t<sub>CO</sub> from 4 ns to 2 ns in AS Timing Parameters for AS ×1 and ×4 Configurations in Cyclone V Devices table.</li> <li>Moved the following timing diagrams to the Configuration, Design Security, and Remote System Upgrades in Cyclone V Devices chapter.</li> <li>FPP Configuration Timing Waveform When DCLK-to-DATA[] Ratio is 1</li> <li>FPP Configuration Timing Waveform When DCLK-to-DATA[] Ratio is &gt;1</li> <li>AS Configuration Timing Waveform</li> <li>PS Configuration Timing Waveform</li> </ul>                                                              |

| March 2015    | 2015.03.31 | <ul> <li>Added V<sub>CC</sub> specifications for devices with internal scrubbing feature (with SC suffix) in Recommended Operating Conditions table.</li> <li>Corrected the unit for t<sub>DH</sub> from ns to s in FPP Timing Parameters When DCLK-to-DATA[] Ratio is &gt;1 for Cyclone V Devices table.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|               |            | continued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Date         | Version    | Changes                                                                                                                                                                                                                                                                                                                         |

|--------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| January 2015 | 2015.01.23 | Updated the transceiver specification for Cyclone V ST from 5 Gbps to 6.144 Gbps. Updated the note in the following tables:                                                                                                                                                                                                     |

|              |            | <ul> <li>Transceiver Power Supply Operating Conditions for Cyclone V GX, GT, SX, and ST Devices</li> </ul>                                                                                                                                                                                                                      |

|              |            | Transceiver Specifications for Cyclone V GX, GT, SX, and ST Devices                                                                                                                                                                                                                                                             |

|              |            | Transceiver Compliance Specification for All Supported Protocol for Cyclone V Devices                                                                                                                                                                                                                                           |

|              |            | <ul> <li>Updated the description for V<sub>CC_AUX_SHARED</sub> to "HPS auxiliary power supply". Added a note to state that V<sub>CC_AUX_SHARED</sub> must be powered by the same source as VCC_AUX for Cyclone V SX C5, C6, D5, and D6 devices, and Cyclone V SE A5 and A6 devices. Updated in the following tables:</li> </ul> |

|              |            | Absolute Maximum Ratings for Cyclone V Devices                                                                                                                                                                                                                                                                                  |

|              |            | HPS Power Supply Operating Conditions for Cyclone V SE, SX, and ST Devices                                                                                                                                                                                                                                                      |

|              |            | Added statement in I/O Standard Specifications: You must perform timing closure analysis to determine the maximum achievable frequency for general purpose I/O standards.                                                                                                                                                       |

|              |            | Updated the conditions for transceiver reference clock rise time and fall time: Measure at ±60 mV of differential signal.  Added a note to the conditions: REFCLK performance requires to meet transmitter REFCLK phase noise specification.                                                                                    |

|              |            | • Updated f <sub>VCO</sub> maximum value from 1400 MHz to 1600 MHz for -C7 and -I7 speed grades in the PLL specifications table.                                                                                                                                                                                                |

|              |            | Updated the description in Periphery Performance Specifications to mention that proper timing closure is required in design.                                                                                                                                                                                                    |

|              |            | Added the following notes in the High-Speed I/O Specifications for Cyclone V Devices table:                                                                                                                                                                                                                                     |

|              |            | <ul> <li>The Cyclone V devices support true RSDS output standard with data rates of up to 230 Mbps using true LVDS output<br/>buffer types on all I/O banks.</li> </ul>                                                                                                                                                         |

|              |            | <ul> <li>The Cyclone V devices support true mini-LVDS output standard with data rates of up to 340 Mbps using true LVDS output buffer types on all I/O banks.</li> </ul>                                                                                                                                                        |

|              |            | Updated HPS Clock Performance main_base_clk specifications from 462 MHz to 400 MHz for -C6 speed grade.                                                                                                                                                                                                                         |

|              |            | • Updated HPS PLL VCO maximum frequency to 1,600 MHz (for -C7, -I7, -A7, and -C8 speed grades) and 1,850 MHz (for -C6 speed grade).                                                                                                                                                                                             |

|              |            | Changed the symbol for HPS PLL input jitter divide value from NR to N.                                                                                                                                                                                                                                                          |

|              |            | Removed "Slave select pulse width (Texas Instruments SSP mode)" parameter from the following tables:                                                                                                                                                                                                                            |

|              |            | SPI Master Timing Requirements for Cyclone V Devices                                                                                                                                                                                                                                                                            |

|              |            | SPI Slave Timing Requirements for Cyclone V Devices                                                                                                                                                                                                                                                                             |

|              |            | Added descriptions to USB Timing Characteristics section in HPS Specifications: PHYs that support LPM mode may not function properly with the USB controller due to a timing issue. It is recommended that designers use the MicroChip USB3300 PHY device that has been proven to be successful on the development board.       |

|              |            | Added HPS JTAG timing specifications.                                                                                                                                                                                                                                                                                           |

|              |            | Updated the configuration .rbf size (bits) for Cyclone V devices.                                                                                                                                                                                                                                                               |

|              |            | Added a note to Uncompressed .rbf Sizes for Cyclone V Devices table: The recommended EPCQ serial configuration devices are able to store more than one image.                                                                                                                                                                   |

|              |            | continued                                                                                                                                                                                                                                                                                                                       |

## Cyclone V Device Datasheet

## CV-51002 | 2018.05.07

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| July 2014     | 3.9     | Added a note in Table 3, Table 4, and Table 5: The power supply value describes the budget for the DC (static) power supply tolerance and does not include the dynamic tolerance requirements. Refer to the PDN tool for the additional budget for the dynamic tolerance requirements.                                                                                                             |

|               |         | Added a note in Table 19: Differential inputs are powered by V <sub>CCPD</sub> which requires 2.5 V.                                                                                                                                                                                                                                                                                               |

|               |         | Updated "Minimum differential eye opening at the receiver serial input pins" specification in Table 20.                                                                                                                                                                                                                                                                                            |

|               |         | Updated h2f_user2_clk specification for -C6, -C7, and -I7 speed grades in Table 34.                                                                                                                                                                                                                                                                                                                |

|               |         | Updated description in "HPS PLL Specifications" section.                                                                                                                                                                                                                                                                                                                                           |

|               |         | Updated VCO range maximum specification in Table 35.                                                                                                                                                                                                                                                                                                                                               |

|               |         | ullet Updated T <sub>d</sub> and T <sub>h</sub> specifications in Table 41.                                                                                                                                                                                                                                                                                                                        |

|               |         | Added T <sub>h</sub> specification in Table 43 and Figure 10.                                                                                                                                                                                                                                                                                                                                      |

|               |         | Updated a note in Figure 17, Figure 18, and Figure 20 as follows: Do not leave DCLK floating after configuration. DCLK is ignored after configuration is complete. It can toggle high or low if required.                                                                                                                                                                                          |

|               |         | Removed "Remote update only in AS mode" specification in Table 54.                                                                                                                                                                                                                                                                                                                                 |

|               |         | Added DCLK device initialization clock source specification in Table 56.                                                                                                                                                                                                                                                                                                                           |

|               |         | • Added description in "Configuration Files" section: The IOCSR .rbf size is specifically for the Configuration via Protocol (CvP) feature.                                                                                                                                                                                                                                                        |

|               |         | Added "Recommended EPCQ Serial Configuration Device" values in Table 57.                                                                                                                                                                                                                                                                                                                           |

|               |         | Removed f <sub>MAX_RU_CLK</sub> specification in Table 59.                                                                                                                                                                                                                                                                                                                                         |

| February 2014 | 3.8     | Updated V <sub>CCRSTCLK HPS</sub> maximum specification in Table 1.                                                                                                                                                                                                                                                                                                                                |

|               |         | Added V <sub>CC_AUX_SHARED</sub> specification in Table 1.                                                                                                                                                                                                                                                                                                                                         |

| December 2013 | 3.7     | • Updated Table 1, Table 3, Table 19, Table 20, Table 23, Table 25, Table 27, Table 34, Table 44, Table 51, Table 52, Table 55, and Table 61.                                                                                                                                                                                                                                                      |

|               |         | • Removed Preliminary tags for Table 1, Table 2, Table 3, Table 4, Table 5, Table 6, Table 7, Table 9, Table 12, Table 13, Table 14, Table 15, Table 16, Table 17, Table 18, Table 19, Table 20, Table 24, Table 25, Table 26, Table 27, Table 28, Table 32, Table 33, Table 49, Table 50, Table 51, Table 52, Table 53, Table 54, Table 55, Table 57, Table 58, Table 59, Table 60, and Table 62. |

| November 2013 | 3.6     | Updated Table 23, Table 30, and Table 31.                                                                                                                                                                                                                                                                                                                                                          |

| October 2013  | 3.5     | Added "HPS PLL Specifications".                                                                                                                                                                                                                                                                                                                                                                    |

|               |         | Added Table 23, Table 35, and Table 36.                                                                                                                                                                                                                                                                                                                                                            |

|               |         | • Updated Table 1, Table 5, Table 11, Table 19, Table 20, Table 21, Table 22, Table 25, Table 28, Table 34, Table 37, Table 38, Table 39, Table 40, Table 41, Table 42, Table 43, Table 44, Table 45, Table 46, Table 47, and Table 53.                                                                                                                                                            |

|               |         | Updated Figure 1, Figure 2, Figure 4, Figure 10, Figure 12, Figure 13, and Figure 16.                                                                                                                                                                                                                                                                                                              |

|               |         | Removed table: GPIO Pulse Width for Cyclone V Devices.                                                                                                                                                                                                                                                                                                                                             |

|               |         | continued                                                                                                                                                                                                                                                                                                                                                                                          |

| Date          | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2013     | 3.4     | <ul> <li>Updated Table 20, Table 27, and Table 34.</li> <li>Updated "UART Interface" and "CAN Interface" sections.</li> <li>Removed the following tables:   — Table 45: UART Baud Rate for Cyclone V Devices  — Table 47: CAN Pulse Width for Cyclone V Devices</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| May 2013      | 3.3     | <ul> <li>Added Table 33.</li> <li>Updated Figure 5, Figure 6, Figure 17, Figure 19, and Figure 20.</li> <li>Updated Table 1, Table 4, Table 5, Table 10, Table 13, Table 19, Table 20, Table 26, Table 32, Table 35, Table 36, Table 43, Table 53, Table 57, and Table 61.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| March 2013    | 3.2     | <ul> <li>Added HPS reset information in the "HPS Specifications" section.</li> <li>Added Table 57.</li> <li>Updated Table 1, Table 2, Table 17, Table 20, Table 52, and Table 56.</li> <li>Updated Figure 18.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |