Welcome to E-XFL.COM

#### Understanding <u>Embedded - CPLDs (Complex</u> <u>Programmable Logic Devices)</u>

Embedded - CPLDs, or Complex Programmable Logic Devices, are highly versatile digital logic devices used in electronic systems. These programmable components are designed to perform complex logical operations and can be customized for specific applications. Unlike fixedfunction ICs, CPLDs offer the flexibility to reprogram their configuration, making them an ideal choice for various embedded systems. They consist of a set of logic gates and programmable interconnects, allowing designers to implement complex logic circuits without needing custom hardware.

#### **Applications of Embedded - CPLDs**

#### Details

| Product Status                  | Obsolete                                                                    |

|---------------------------------|-----------------------------------------------------------------------------|

| Programmable Type               | In System Programmable (min 10K program/erase cycles)                       |

| Delay Time tpd(1) Max           | 15 ns                                                                       |

| Voltage Supply - Internal       | 3V ~ 3.6V                                                                   |

| Number of Logic Elements/Blocks | -                                                                           |

| Number of Macrocells            | 64                                                                          |

| Number of Gates                 | -                                                                           |

| Number of I/O                   | 64                                                                          |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                           |

| Mounting Type                   | Surface Mount                                                               |

| Package / Case                  | 84-LCC (J-Lead)                                                             |

| Supplier Device Package         | 84-PLCC (29.31x29.31)                                                       |

| Purchase URL                    | https://www.e-xfl.com/product-detail/microchip-technology/atf1504asv-15ji84 |

|                                 |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Description

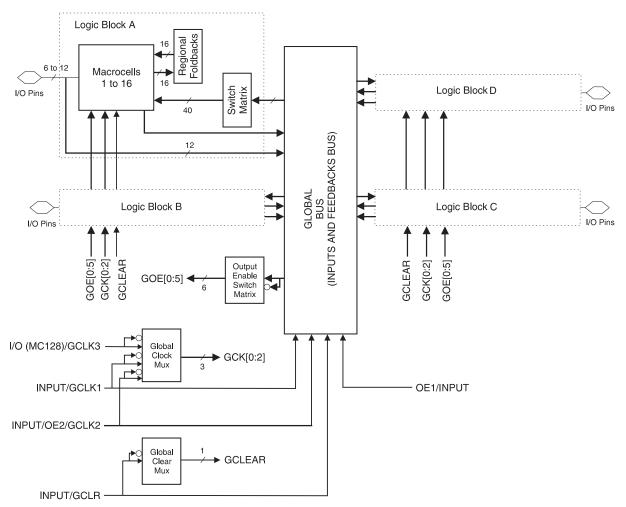

The ATF1504ASV(L) is a high-performance, high-density complex programmable logic device (CPLD) that utilizes Atmel's proven electrically-erasable memory technology. With 64 logic macrocells and up to 68 inputs, it easily integrates logic from several TTL, SSI, MSI, LSI and classic PLDs. The ATF1504ASV(L)'s enhanced routing switch matrices increase usable gate count and the odds of successful pin-locked design modifications.

The ATF1504ASV(L) has up to 68 bi-directional I/O pins and four dedicated input pins, depending on the type of device package selected. Each dedicated pin can also serve as a global control signal, register clock, register reset or output enable. Each of these control signals can be selected for use individually within each macrocell.

Each of the 64 macrocells generates a buried feedback that goes to the global bus. Each input and I/O pin also feeds into the global bus. The switch matrix in each logic block then selects 40 individual signals from the global bus. Each macrocell also generates a foldback logic term that goes to a regional bus. Cascade logic between macrocells in the ATF1504ASV(L) allows fast, efficient generation of complex logic functions. The ATF1504ASV(L) contains four such logic chains, each capable of creating sum term logic with a fan-in of up to 40 product terms.

The ATF1504ASV(L) macrocell, shown in Figure 1, is flexible enough to support highlycomplex logic functions operating at high speed. The macrocell consists of five sections: product terms and product term select multiplexer, OR/XOR/CASCADE logic, a flip-flop, output select and enable, and logic array inputs.

## 4 **ATF1504ASV(L)**

### **Block Diagram**

Unused product terms are automatically disabled by the compiler to decrease power consumption. A security fuse, when programmed, protects the contents of the ATF1504ASV(L). Two bytes (16 bits) of User Signature are accessible to the user for purposes such as storing project name, part number, revision or date. The User Signature is accessible regardless of the state of the security fuse.

The ATF1504ASV(L) device is an in-system programmable (ISP) device. It uses the industry-standard 4-pin JTAG interface (IEEE Std. 1149.1), and is fully-compliant with JTAG's Boundary-scan Description Language (BSDL). ISP allows the device to be programmed without removing it from the printed circuit board. In addition to simplifying the manufacturing flow, ISP also allows design modifications to be made in the field via software.

Product Terms and SelectEach ATF1504ASV(L) macrocell has five product terms. Each product term receives as<br/>its inputs all signals from both the global bus and regional bus.

The product term select multiplexer (PTMUX) allocates the five product terms as needed to the macrocell logic gates and control signals. The PTMUX programming is determined by the design compiler, which selects the optimum macrocell configuration.

#### Figure 1. ATF1504ASV(L) Macrocell

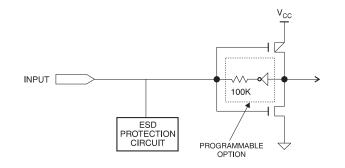

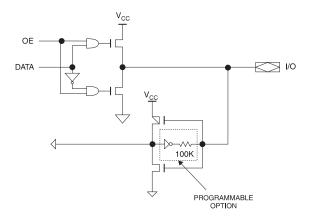

### Programmable Pin-keeper Option for Inputs and I/Os

The ATF1504ASV(L) offers the option of programming all input and I/O pins so that pin keeper circuits can be utilized. When any pin is driven high or low and then subsequently left floating, it will stay at that previous high- or low-level. This circuitry prevents unused input and I/O lines from floating to intermediate voltage levels, which causes unnecessary power consumption and system noise. The keeper circuits eliminate the need for external pull-up resistors and eliminate their DC power consumption.

### **Input Diagram**

#### I/O Diagram

### Speed/Power Management

The ATF1504ASV(L) has several built-in speed and power management features. The ATF1504ASV(L) contains circuitry that automatically puts the device into a low power standby mode when no logic transitions are occurring. This not only reduces power consumption during inactive periods, but also provides proportional power savings for most applications running at system speeds below 5 MHz. This feature may be selected as a device option.

To further reduce power, each ATF1504ASV(L) macrocell has a reduced-power bit feature. This feature allows individual macrocells to be configured for maximum power savings. This feature may be selected as a design option.

All ATF1504ASV(L) also have an optional power-down mode. In this mode, current drops to below 5 mA. When the power-down option is selected, either PD1 or PD2 pins (or both) can be used to power down the part. The power-down option is selected in the design source file. When enabled, the device goes into power down when either PD1 or PD2 is high. In the power-down mode, all internal logic signals are latched and held, as are any enabled outputs.

All pin transitions are ignored until the PD pin is brought low. When the power-down feature is enabled, the PD1 or PD2 pin cannot be used as a logic input or output. However, the pin's macrocell may still be used to generate buried foldback and cascade logic signals.

ATF1504ASV(L)

|  | R |

|--|---|

| Programming                   | ATF1504ASV(L) devices are in-system programmable (ISP) devices utilizing the 4-pin JTAG protocol. This capability eliminates package handling normally required for pro-<br>gramming and facilitates rapid design iterations and field changes.                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                               | Atmel provides ISP hardware and software to allow programming of the ATF1504ASV(L) via the PC. ISP is performed by using either a download cable, a comparable board tester or a simple microprocessor interface.                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                               | To facilitate ISP programming by the Automated Test Equipment (ATE) vendors. Serial<br>Vector Format (SVF) files can be created by Atmel provided software utilities.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

|                               | ATF1504ASV(L) devices can also be programmed using standard third-party program-<br>mers. With third-party programmer the JTAG ISP port can be disabled thereby allowing four additional I/O pins to be used for logic.                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |

|                               | Contact your local Atmel representatives or Atmel PLD applications for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| ISP Programming<br>Protection | The ATF1504ASV(L) has a special feature that locks the device and prevents the inputs<br>and I/O from driving if the programming process is interrupted for any reason. The<br>inputs and I/O default to high-Z state during such a condition. In addition the pin keeper<br>option preserves the former state during device programming, if this circuit were previ-<br>ously programmed on the device. This prevents disturbing the operation of other circuits<br>in the system while the ATF1504ASV(L) is being programmed via ISP. |  |  |  |  |  |  |

|                               | All ATF1504ASV(L) devices are initially shipped in the erased state thereby making them ready to use for ISP.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|                               | Note: For more information refer to the "Designing for In-System Programmability with Atmel CPLDs" application note.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

### **DC and AC Operating Conditions**

|                                     | Commercial  | Industrial   |

|-------------------------------------|-------------|--------------|

| Operating Temperature (Ambient))    | 0°C - 70°C  | -40°C - 85°C |

| V <sub>CC</sub> (3.3V) Power Supply | 3.0V - 3.6V | 3.0V - 3.6V  |

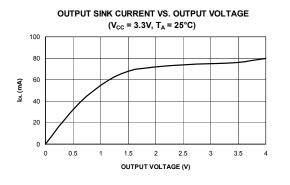

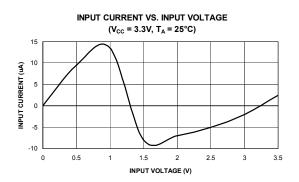

### **DC Characteristics**

| Symbol                          | Parameter                                                                                                  | Condition                                                      |                                              |      | Min                     | Тур | Max                     | Units |

|---------------------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------------------------------------------|------|-------------------------|-----|-------------------------|-------|

| I <sub>IL</sub>                 | Input or I/O Low<br>Leakage Current                                                                        | $V_{IN} = V_{CC}$                                              |                                              |      |                         | -2  | -10                     | μA    |

| I <sub>IH</sub>                 | Input or I/O High<br>Leakage Current                                                                       |                                                                |                                              |      |                         | 2   | 10                      |       |

| I <sub>OZ</sub>                 | Tri-State Output<br>Off-State Current                                                                      | $V_{O} = V_{CC}$ or G                                          | ND                                           |      | -40                     |     | 40                      | μA    |

|                                 |                                                                                                            |                                                                | Obd Maida                                    | Com. |                         | 60  |                         | mA    |

| 1                               | Power Supply Current,                                                                                      | V <sub>CC</sub> = Max                                          | Std Mode                                     | Ind. |                         | 75  |                         | mA    |

| I <sub>CC1</sub>                | Standby                                                                                                    | $V_{IN} = 0, V_{CC}$                                           | <b>((1.2) N A - - 1 -</b>                    | Com. |                         | 5   |                         | μA    |

|                                 |                                                                                                            |                                                                | "L" Mode                                     | Ind. |                         | 5   |                         | μA    |

| I <sub>CC2</sub>                | Power Supply Current,<br>Power-down Mode                                                                   | $V_{CC} = Max$<br>$V_{IN} = 0, V_{CC}$                         | "PD" Mode                                    |      |                         | 0.1 | 5                       | mA    |

| . (2)                           | Reduced-power Mode                                                                                         | V <sub>CC</sub> = Max                                          |                                              | Com  |                         | 40  |                         | ma    |

| I <sub>CC3</sub> <sup>(2)</sup> | Supply Current, Standby                                                                                    | $V_{IN} = 0, V_{CC}$                                           | Std Power                                    | Ind  |                         | 55  |                         |       |

| V <sub>IL</sub>                 | Input Low Voltage                                                                                          |                                                                |                                              |      | -0.3                    |     | 0.8                     | V     |

| V <sub>IH</sub>                 | Input High Voltage                                                                                         |                                                                |                                              |      | 1.7                     |     | V <sub>CCIO</sub> + 0.3 | V     |

|                                 |                                                                                                            | $V_{IN} = V_{IH} \text{ or } V_{I}$                            | 1                                            | Com. |                         |     | 0.45                    | V     |

|                                 | Output Low Voltage (TTL)                                                                                   | $V_{\rm CCIO} = Min, I_{\rm C}$                                | <sub>DL</sub> = 8 mA                         | Ind. |                         |     | 0.45                    |       |

| V <sub>OL</sub>                 |                                                                                                            | $V_{IN} = V_{IH} \text{ or } V_{I}$                            | 1                                            | Com. |                         |     | 0.2                     | V     |

|                                 | Output Low Voltage (CMOS)                                                                                  |                                                                | $V_{CC} = Min, I_{OL} = 0.1 \text{ mA}$ Ind. |      |                         |     | 0.2                     | V     |

| .,                              | Output High Voltage<br>- 3.3V (TTL)                                                                        | $V_{IN} = V_{IH} \text{ or } V_{I}$<br>$V_{CCIO} = Min, I_{O}$ |                                              | - F  | 2.4                     |     |                         | V     |

| V <sub>OH</sub>                 | Output High Voltage $V_{IN} = V_{IH}$ or $V_{IL}$ - 3.3V (CMOS) $V_{CCIO} = Min, I_{OH} = -0.1 \text{ mA}$ |                                                                |                                              |      | V <sub>CCIO</sub> - 0.2 |     |                         | V     |

Notes: 1. Not more than one output at a time should be shorted. Duration of short circuit test should not exceed 30 sec. 2. When microcell reduced-power feature is enabled.

### **Pin Capacitance**

|                  | Тур | Max | Units | Conditions                        |

|------------------|-----|-----|-------|-----------------------------------|

| C <sub>IN</sub>  |     | 8   | pF    | V <sub>IN</sub> = 0V; f = 1.0 MHz |

| C <sub>I/O</sub> |     | 8   | pF    | $V_{OUT} = 0V$ ; f = 1.0 MHz      |

Note: Typical values for nominal supply voltage. This parameter is only sampled and is not 100% tested. The OGI pin (high-voltage pin during programming) has a maximum capacitance of 12 pF.

### **AC Characteristics**

|                   |                                                                                                 | -1   | 15  | -2   |      |       |

|-------------------|-------------------------------------------------------------------------------------------------|------|-----|------|------|-------|

| Symbol            | Parameter                                                                                       | Min  | Max | Min  | Max  | Units |

| t <sub>PD1</sub>  | Input or Feedback to Non-Registered Output                                                      | 3    | 15  |      | 20   | ns    |

| t <sub>PD2</sub>  | I/O Input or Feedback to Non-Registered Feedback                                                | 3    | 12  |      | 16   | ns    |

| t <sub>SU</sub>   | Global Clock Setup Time                                                                         | 11   |     | 13.5 |      | ns    |

| t <sub>H</sub>    | Global Clock Hold Time                                                                          | 0    |     | 0    |      | ns    |

| t <sub>FSU</sub>  | Global Clock Setup Time of Fast Input                                                           | 3    |     | 3    |      | ns    |

| t <sub>FH</sub>   | Global Clock Hold Time of Fast Input                                                            | 1.0  |     | 2    |      | MHz   |

| t <sub>COP</sub>  | Global Clock to Output Delay                                                                    |      | 9   |      | 12   | ns    |

| t <sub>CH</sub>   | Global Clock High Time                                                                          | 5    |     | 6    |      | ns    |

| t <sub>CL</sub>   | Global Clock Low Time                                                                           | 5    |     | 6    |      | ns    |

| t <sub>ASU</sub>  | Array Clock Setup Time                                                                          | 5    |     | 7    |      | ns    |

| t <sub>AH</sub>   | Array Clock Hold Time                                                                           | 4    |     | 4    |      | ns    |

| t <sub>ACOP</sub> | Array Clock Output Delay                                                                        |      | 15  |      | 18.5 | ns    |

| t <sub>ACH</sub>  | Array Clock High Time                                                                           | 6    |     | 8    |      | ns    |

| t <sub>ACL</sub>  | Array Clock Low Time                                                                            | 6    |     | 8    |      | ns    |

| t <sub>CNT</sub>  | Minimum Clock Global Period                                                                     |      | 13  |      | 17   | ns    |

| f <sub>CNT</sub>  | Maximum Internal Global Clock Frequency                                                         | 76.9 |     | 66   |      | MHz   |

| t <sub>ACNT</sub> | Minimum Array Clock Period                                                                      |      | 13  |      | 17   | ns    |

| f <sub>ACNT</sub> | Maximum Internal Array Clock Frequency                                                          | 76.9 |     | 58.8 |      | MHz   |

| f <sub>MAX</sub>  | Maximum Clock Frequency                                                                         | 100  |     | 83.3 |      | MHz   |

| t <sub>IN</sub>   | Input Pad and Buffer Delay                                                                      |      | 2   |      | 2.5  | ns    |

| t <sub>IO</sub>   | I/O Input Pad and Buffer Delay                                                                  |      | 2   |      | 2.5  | ns    |

| t <sub>FIN</sub>  | Fast Input Delay                                                                                |      | 2   |      | 2    | ns    |

| t <sub>SEXP</sub> | Foldback Term Delay                                                                             |      | 8   |      | 10   | ns    |

| t <sub>PEXP</sub> | Cascade Logic Delay                                                                             |      | 1   |      | 1    | ns    |

| t <sub>LAD</sub>  | Logic Array Delay                                                                               |      | 6   |      | 8    | ns    |

| t <sub>LAC</sub>  | Logic Control Delay                                                                             |      | 3.5 |      | 4.5  | ns    |

| t <sub>IOE</sub>  | Internal Output Enable Delay                                                                    |      | 3   |      | 3    | ns    |

| t <sub>OD1</sub>  | Output Buffer and Pad Delay<br>(Slow slew rate = OFF; $V_{CCIO} = 5V$ ; $C_L = 35 \text{ pF}$ ) |      | 3   |      | 4    | ns    |

| t <sub>OD2</sub>  | Output Buffer and Pad Delay (Slow slew rate = OFF; $V_{CCIO} = 3.3V$ ; $C_L = 35 \text{ pF}$ )  |      | 3   |      | 4    | ns    |

| t <sub>OD3</sub>  | Output Buffer and Pad Delay (Slow slew rate = ON; $V_{CCIO}$ = 5V or 3.3V; $C_L$ = 35 pF)       |      | 5   |      | 6    | ns    |

| t <sub>ZX1</sub>  | Output Buffer Enable Delay<br>(Slow slew rate = OFF; $V_{CCIO}$ = 5.0V; $C_L$ = 35 pF)          |      | 7   |      | 9    | ns    |

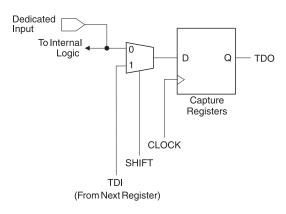

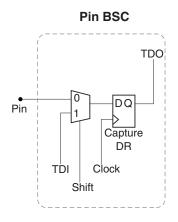

| JTAG-BST/ISP<br>Overview                 | The JTAG boundary-scan testing is controlled by the Test Access Port (TAP) controller<br>in the ATF1504ASV(L). The boundary-scan technique involves the inclusion of a shift-<br>register stage (contained in a boundary-scan cell) adjacent to each component so that<br>signals at component boundaries can be controlled and observed using scan testing<br>principles. Each input pin and I/O pin has its own boundary-scan cell (BSC) in order to<br>support boundary-scan testing. The ATF1504ASV(L) does not currently include a Test<br>Reset (TRST) input pin because the TAP controller is automatically reset at power-up.<br>The five JTAG modes supported include: SAMPLE/PRELOAD, EXTEST, BYPASS,<br>IDCODE and HIGHZ. The ATF1504ASV(L)'s ISP can be fully described using JTAG's<br>BSDL as described in IEEE Standard 1149.1b. This allows ATF1504ASV(L) program-<br>ming to be described and implemented using any one of the third-party development<br>tools supporting this standard. |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                          | The ATF1504ASV(L) has the option of using four JTAG-standard I/O pins for boundary-<br>scan testing (BST) and in-system programming (ISP) purposes. The ATF1504ASV(L) is<br>programmable through the four JTAG pins using the IEEE standard JTAG programming<br>protocol established by IEEE Standard 1149.1 using 5V TTL-level programming signals<br>from the ISP interface for in-system programming. The JTAG feature is a programmable<br>option. If JTAG (BST or ISP) is not needed, then the four JTAG control pins are avail-<br>able as I/O pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

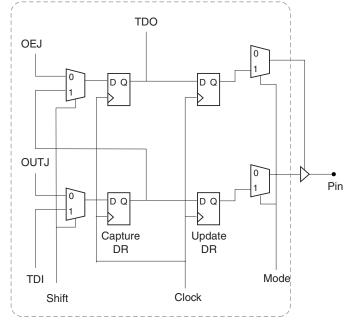

| JTAG Boundary-scan<br>Cell (BSC) Testing | The ATF1504ASV(L) contains up to 68 I/O pins and four input pins, depending on the device type and package type selected. Each input pin and I/O pin has its own bound-<br>ary-scan cell (BSC) in order to support boundary-scan testing as described in detail by IEEE Standard 1149.1. A typical BSC consists of three capture registers or scan regis-<br>ters and up to two update registers. There are two types of BSCs, one for input or I/O pin, and one for the macrocells. The BSCs in the device are chained together through the capture registers. Input to the capture register chain is fed in from the TDI pin while the output is directed to the TDO pin. Capture registers are used to capture active device data signals, to shift data in and out of the device and to load data into the update registers. Control signals are generated internally by the JTAG TAP controller. The BSC configuration for the input and I/O pins and macrocells are shown below.                     |

### BSC Configuration for Input and I/O Pins (Except JTAG TAP Pins)

Note: The ATF1504ASV(L) has pull-up option on TMS and TDI pins. This feature is selected as a design option.

### **BSC Configuration for Macrocell**

Macrocell BSC

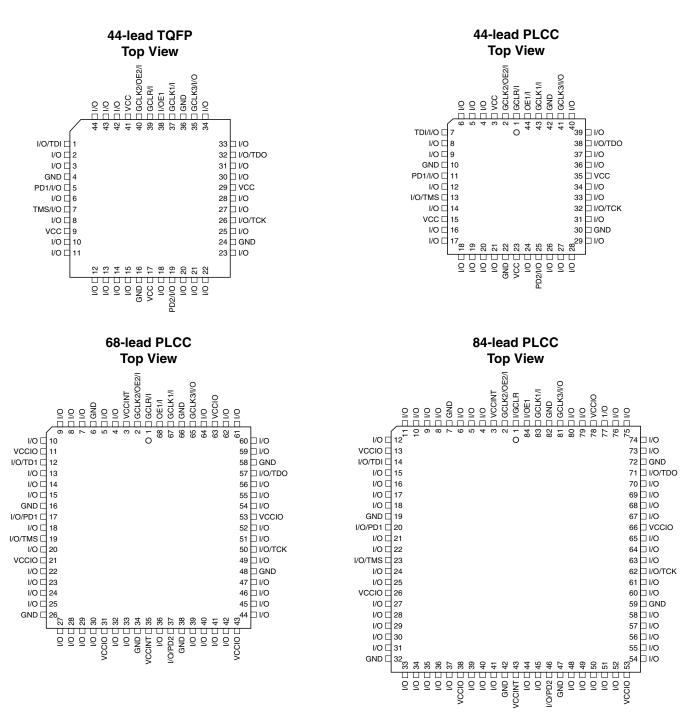

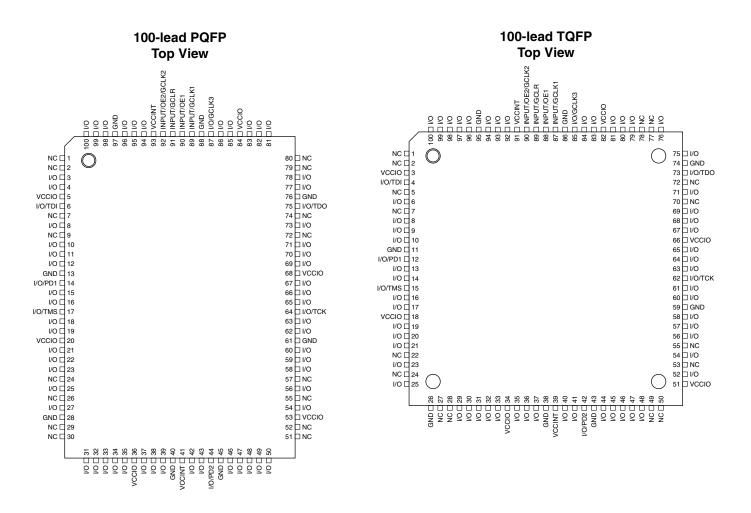

### ATF1504ASV I/O Pinouts

|            |           | 44-lead |      |      |      | 100-<br>lead | 100-<br>lead |                   |             | 44-lead |      | 68-lead |      | 100-<br>lead | 100-<br>lead |

|------------|-----------|---------|------|------|------|--------------|--------------|-------------------|-------------|---------|------|---------|------|--------------|--------------|

| MC         | PLC       | PLCC    | TQFP | PLCC | PLCC | PQFP         | TQFP         | MC                | PLC         | PLCC    | TQFP | PLCC    | PLCC | PQFP         | TQFP         |

| 1          | A         | 12      | 6    | 18   | 22   | 16           | 14           | 33                | С           | 24      | 18   | 36      | 44   | 42           | 40           |

| 2          | A         | -       | -    | -    | 21   | 15           | 13           | 34                | С           | -       | -    | -       | 45   | 43           | 41           |

| 3          | A/<br>PD1 | 11      | 5    | 17   | 20   | 14           | 12           | 35                | C/<br>PD2   | 25      | 19   | 37      | 46   | 44           | 42           |

| 4          | Α         | 9       | 3    | 15   | 18   | 12           | 10           | 36                | С           | 26      | 20   | 39      | 48   | 46           | 44           |

| 5          | А         | 8       | 2    | 14   | 17   | 11           | 9            | 37                | С           | 27      | 21   | 40      | 49   | 47           | 45           |

| 6          | А         | -       | -    | 13   | 16   | 10           | 8            | 38                | С           | -       | -    | 41      | 50   | 48           | 46           |

| 7          | А         | -       | -    | -    | 15   | 8            | 6            | 39                | С           | -       | -    | -       | 51   | 49           | 47           |

| 8/<br>TDI  | А         | 7       | 1    | 12   | 14   | 6            | 4            | 40                | С           | 28      | 22   | 42      | 52   | 50           | 48           |

| 9          | А         | -       | -    | 10   | 12   | 4            | 100          | 41                | С           | 29      | 23   | 44      | 54   | 54           | 52           |

| 10         | А         | -       | -    | -    | 11   | 3            | 99           | 42                | С           | -       | -    | -       | 55   | 56           | 54           |

| 11         | А         | 6       | 44   | 9    | 10   | 100          | 98           | 43                | С           | -       | -    | 45      | 56   | 58           | 56           |

| 12         | А         | -       | -    | 8    | 9    | 99           | 97           | 44                | С           | -       | -    | 46      | 57   | 59           | 57           |

| 13         | А         | -       | -    | 7    | 8    | 98           | 96           | 45                | С           | -       | -    | 47      | 58   | 60           | 58           |

| 14         | А         | 5       | 43   | 5    | 6    | 96           | 94           | 46                | С           | 31      | 25   | 49      | 60   | 62           | 60           |

| 15         | А         | -       | -    | -    | 5    | 95           | 93           | 47                | С           | -       | -    | -       | 61   | 63           | 61           |

| 16         | А         | 4       | 42   | 4    | 4    | 94           | 92           | 48/<br><b>TCK</b> | С           | 32      | 26   | 50      | 62   | 64           | 62           |

| 17         | В         | 21      | 15   | 33   | 41   | 39           | 37           | 49                | D           | 33      | 27   | 51      | 63   | 65           | 63           |

| 18         | В         | -       | -    | -    | 40   | 38           | 36           | 50                | D           | -       | -    | -       | 64   | 66           | 64           |

| 19         | В         | 20      | 14   | 32   | 39   | 37           | 35           | 51                | D           | 34      | 28   | 52      | 65   | 67           | 65           |

| 20         | В         | 19      | 13   | 30   | 37   | 35           | 33           | 52                | D           | 36      | 30   | 54      | 67   | 69           | 67           |

| 21         | В         | 18      | 12   | 29   | 36   | 34           | 32           | 53                | D           | 37      | 31   | 55      | 68   | 70           | 68           |

| 22         | В         | -       | -    | 28   | 35   | 33           | 31           | 54                | D           | -       | -    | 56      | 69   | 71           | 69           |

| 23         | В         | -       | -    | -    | 34   | 32           | 30           | 55                | D           | -       | -    | -       | 70   | 73           | 71           |

| 24         | В         | 17      | 11   | 27   | 33   | 31           | 29           | 56/<br><b>TDO</b> | D           | 38      | 32   | 57      | 71   | 75           | 73           |

| 25         | В         | 16      | 10   | 25   | 31   | 27           | 25           | 57                | D           | 39      | 33   | 59      | 73   | 77           | 75           |

| 26         | В         | -       | -    | -    | 30   | 25           | 23           | 58                | D           | -       | -    | -       | 74   | 78           | 76           |

| 27         | В         | -       | -    | 24   | 29   | 23           | 21           | 59                | D           | -       | -    | 60      | 75   | 81           | 79           |

| 28         | В         | -       | -    | 23   | 28   | 22           | 20           | 60                | D           | -       | -    | 61      | 76   | 82           | 80           |

| 29         | В         | -       | -    | 22   | 27   | 21           | 19           | 61                | D           | -       | -    | 62      | 77   | 83           | 81           |

| 30         | В         | 14      | 8    | 20   | 25   | 19           | 17           | 62                | D           | 40      | 34   | 64      | 79   | 85           | 83           |

| 31         | В         | -       | -    | -    | 24   | 18           | 16           | 63                | D           | -       | -    | -       | 80   | 86           | 84           |

| 32/<br>TMS | В         | 13      | 7    | 19   | 23   | 17           | 15           | 64                | D/<br>GCLK3 | 41      | 35   | 65      | 81   | 87           | 85           |

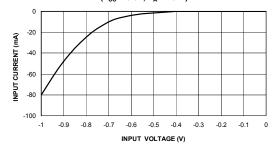

INPUT CLAMP CURRENT VS. INPUT VOLTAGE ( $V_{CC}$  = 3.3V,  $T_A$  = 25°C)

### **Ordering Information**

| t <sub>PD</sub><br>(ns) | t <sub>CO1</sub><br>(ns) | f <sub>MAX</sub><br>(MHz) | Ordering Code                       | Package | Operation Range  |

|-------------------------|--------------------------|---------------------------|-------------------------------------|---------|------------------|

|                         |                          |                           | ATF1504ASV-15 AC44                  | 44A     |                  |

|                         |                          |                           | ATF1504ASV-15 JC44                  | 44J     |                  |

| 15                      | 8                        | 100                       | ATF1504ASV-15 JC68 <sup>(2)</sup>   | 68J     | Commercial       |

| 15                      | 8                        | 100                       | ATF1504ASV-15 JC84 <sup>(3)</sup>   | 84J     | (0°C to 70°C)    |

|                         |                          |                           | ATF1504ASV-15 QC100 <sup>(2)</sup>  | 100Q1   |                  |

|                         |                          |                           | ATF1500ASV-15 AC100                 | 100A    |                  |

|                         |                          |                           | ATF1504ASV-15 AI44                  | 44A     |                  |

|                         |                          |                           | ATF1504ASV-15 JI44                  | 44J     |                  |

| 15                      | 8                        | 100                       | ATF1504ASV-15 JI68                  | 68J     | Industrial       |

| 10                      | 0                        |                           | ATF1504ASV-15 JI84                  | 84J     | (-40°C to +85°C) |

|                         |                          |                           | ATF1504ASV-15 QI100                 | 100Q1   |                  |

|                         |                          |                           | ATF1504ASV-15 AI100                 | 100A    |                  |

|                         |                          |                           | ATF1504ASVL-20 AC44                 | 44A     |                  |

|                         |                          | ATF1504ASVL-20 JC44 44J   |                                     |         |                  |

| 20                      | 12                       | 83.3                      | ATF1504ASVL-20 JC68 <sup>(2)</sup>  | 68J     | Commercial       |

| 20                      | 12                       | 03.3                      | ATF1504ASVL-20 JC84 <sup>(3)</sup>  | 84J     | (0°C to 70°C)    |

|                         |                          |                           | ATF1504ASVL-20 QC100 <sup>(2)</sup> | 100Q1   |                  |

|                         |                          |                           | ATF1504ASVL-20 AC100                | 100A    |                  |

|                         |                          |                           | ATF1504ASVL-20 AI44                 | 44A     |                  |

|                         |                          |                           | ATF1504ASVL-20 JI44                 | 44J     |                  |

| 20                      | 12                       | 83.3                      | ATF1504ASVL-20 JI68                 | 68J     | Industrial       |

| 20                      | 12                       | 00.0                      | ATF1504ASVL-20 JI84                 | 84J     | (-40°C to +85°C) |

|                         |                          |                           | ATF1504ASVL-20 QI100                | 100Q1   |                  |

|                         |                          |                           | ATF1504ASVL-20 AI100                | 100A    |                  |

#### ATF1504ASV(L) Standard Package Options

Note: 1. The last time buy is Sept. 30, 2005 for shaded parts.

2. The recommended migration for QC100 or JC68 packages is the AU100 or the smaller JU44 packages.

3. The recommended migration for the JC84 package is the ATF1508ASV-15JU84

#### Using "C" Product for Industrial

There is very little risk in using "C" devices for industrial applications because the  $V_{CC}$  conditions for 3.3V products are the same for commercial and industrial (there is only 15°C difference at the high end of the temperature range). To use commercial product for industrial temperature ranges, de-rate  $I_{CC}$  by 15%.

| t <sub>PD</sub><br>(ns) | t <sub>co1</sub><br>(ns) | f <sub>MAX</sub><br>(MHz) | Ordering Code       | Package                        | Operation Range  |                      |      |

|-------------------------|--------------------------|---------------------------|---------------------|--------------------------------|------------------|----------------------|------|

|                         |                          |                           | ATF1504ASV-15 AU44  | 44A                            | Induction        |                      |      |

| 15                      | 15 8 100                 | ATF1504ASV-15 JU44        | 44J                 | Industrial<br>(-40°C to +85°C) |                  |                      |      |

|                         |                          |                           | ATF1504ASV-15 AU100 | 100A                           | (-40 C t0 +85 C) |                      |      |

|                         |                          |                           | ATF1504ASVL-20 AU44 | 44A                            | Industrial       |                      |      |

| 20                      | 20 12                    | 83.3                      | ATF1504ASVL-20 JU44 | 44J                            | Industrial       |                      |      |

|                         |                          |                           |                     | ATF1504ASVL-20 AU100           |                  | ATF1504ASVL-20 AU100 | 100A |

### ATF1504ASV(L) Green Package Options (Pb/Halide-free/RoHS Compliant)

|             | Package Type                                                             |  |  |  |  |  |  |

|-------------|--------------------------------------------------------------------------|--|--|--|--|--|--|

| 44 <b>A</b> | 44A 44-lead, Thin Plastic Gull Wing Quad Flatpack (TQFP)                 |  |  |  |  |  |  |

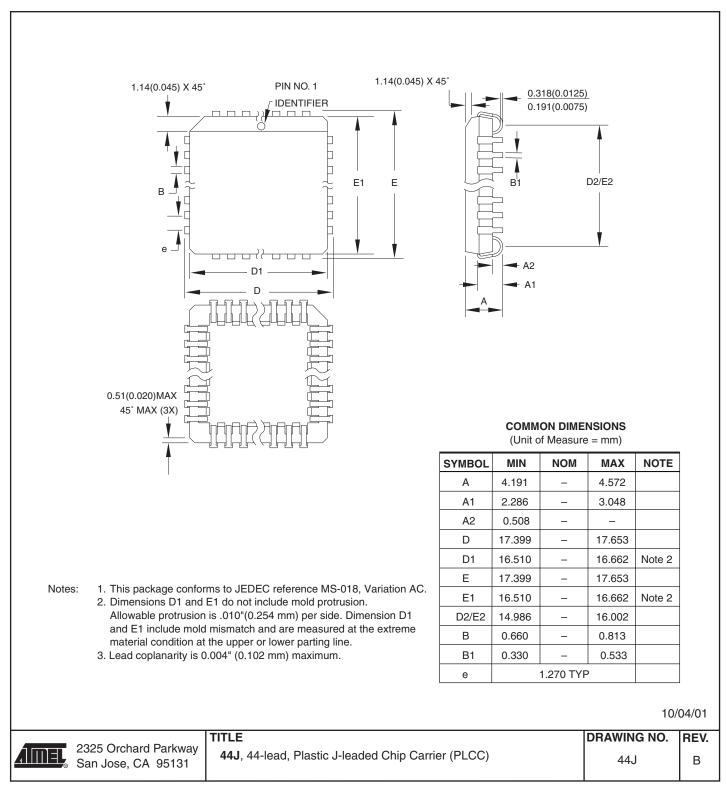

| 44J         | 44-lead, Plastic J-leaded Chip Carrier (PLCC)                            |  |  |  |  |  |  |

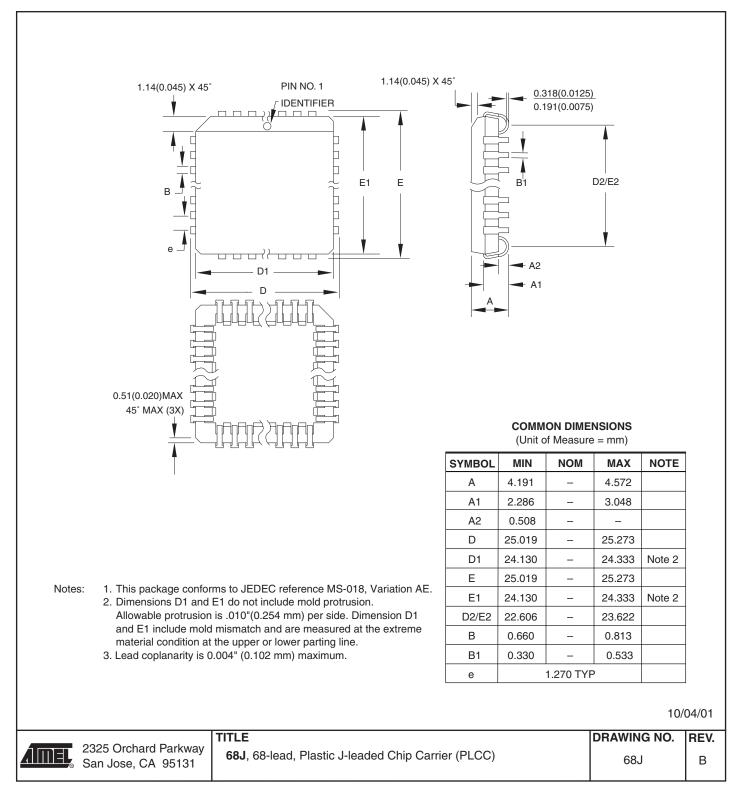

| 68J         | 68-lead, Plastic J-leaded Chip Carrier (PLCC)                            |  |  |  |  |  |  |

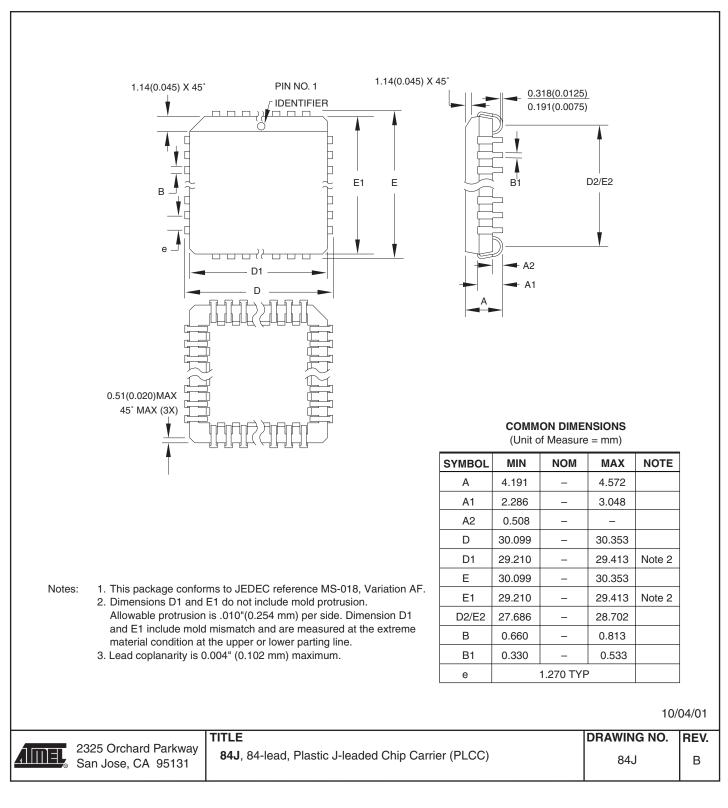

| 84J         | 84-lead, Plastic J-leaded Chip Carrier (PLCC)                            |  |  |  |  |  |  |

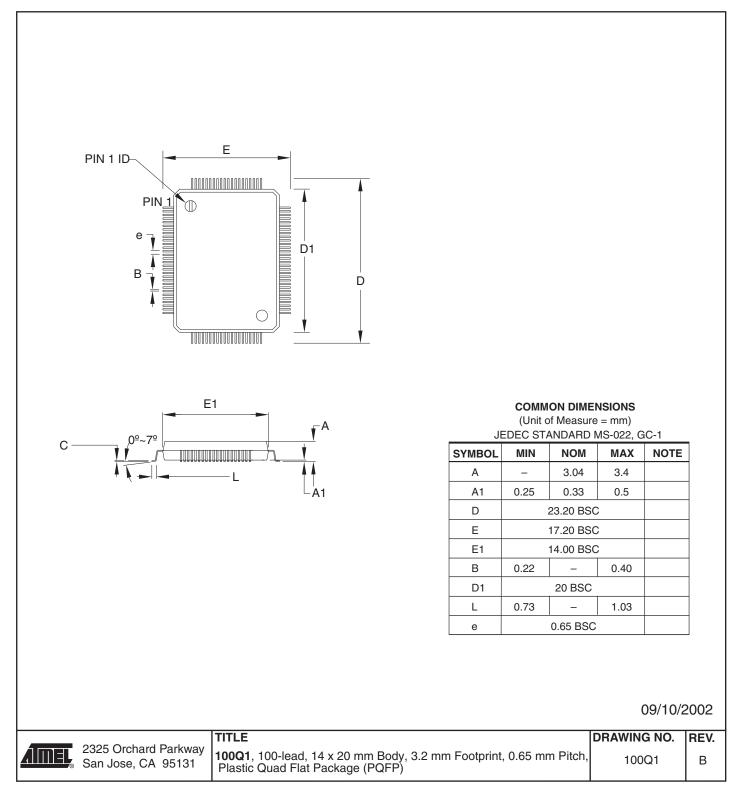

| 100Q1       | 100-lead, 14 x 20 mm Body, Plastic Quad Flat Package (PQFP)              |  |  |  |  |  |  |

| 100A        | 100-lead, 14 x 14 mm Body, Thin Profile Plastic Quad Flat Package (TQFP) |  |  |  |  |  |  |

#### 44J – PLCC

#### 68J – PLCC

#### 84J – PLCC

#### 100Q1 - PQFP

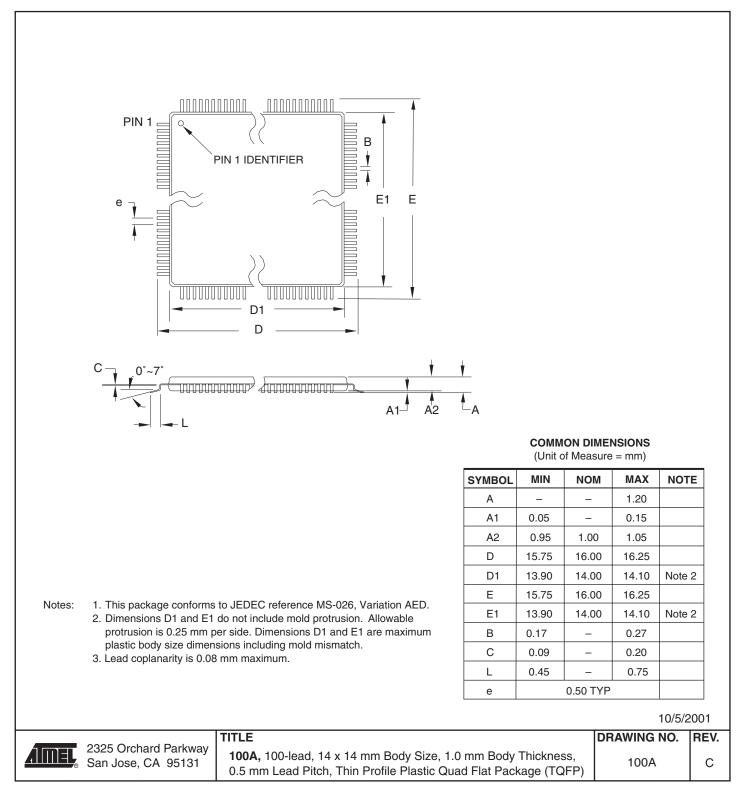

#### 100A – TQFP