Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | SPI                                                                   |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 17                                                                    |

| Program Memory Size        | 4KB (4K x 8)                                                          |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 256 x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 7x10b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 20-VQFN Exposed Pad                                                   |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7fli15bf1u6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Table of Contents**

| 2 PIN DI<br>3 REGIS | DUCTION<br>ESCRIPTION<br>TER & MEMORY MAP<br>I PROGRAM MEMORY | .5<br>.9 |

|---------------------|---------------------------------------------------------------|----------|

| 4.1                 |                                                               |          |

| 4.2                 | MAIN FEATURES                                                 |          |

| 4.3                 | PROGRAMMING MODES                                             |          |

| 4.4                 | ICC INTERFACE                                                 |          |

| 4.5                 | MEMORY PROTECTION                                             |          |

| 4.6                 | RELATED DOCUMENTATION                                         |          |

| 4.7                 | REGISTER DESCRIPTION                                          |          |

|                     | EEPROM                                                        |          |

| 5.1                 |                                                               |          |

| 5.2                 | MAIN FEATURES                                                 |          |

| 5.3                 | MEMORY ACCESS                                                 | -        |

| 5.4                 | POWER SAVING MODES                                            |          |

| 5.5                 | ACCESS ERROR HANDLING                                         |          |

| 5.6                 | DATA EEPROM READ-OUT PROTECTION                               |          |

| 5.7                 | REGISTER DESCRIPTION                                          |          |

| 6 CENTI             | RAL PROCESSING UNIT                                           |          |

| 6.1                 |                                                               | 20       |

| 6.2                 | MAIN FEATURES                                                 | 20       |

| 6.3                 | CPU REGISTERS                                                 | 20       |

| 7 SUPPI             | LY, RESET AND CLOCK MANAGEMENT                                | 23       |

| 7.1                 | INTERNAL RC OSCILLATOR ADJUSTMENT                             |          |

| 7.2                 | PHASE LOCKED LOOP                                             | 23       |

| 7.3                 | REGISTER DESCRIPTION                                          | 25       |

| 7.4                 | MULTI-OSCILLATOR (MO)                                         | 27       |

| 7.5                 | RESET SEQUENCE MANAGER (RSM)                                  | 28       |

| 7.6                 | SYSTEM INTEGRITY MANAGEMENT (SI)                              | 31       |

| 8 INTER             | RUPTS                                                         | 36       |

| 8.1                 | NON MASKABLE SOFTWARE INTERRUPT                               |          |

| 8.2                 | EXTERNAL INTERRUPTS                                           | 36       |

| 8.3                 | PERIPHERAL INTERRUPTS                                         |          |

| 9 POWE              | R SAVING MODES                                                | -        |

| 9.1                 |                                                               | 40       |

| 9.2                 | SLOW MODE                                                     |          |

| 9.3                 | WAIT MODE                                                     |          |

| 9.4                 | HALT MODE                                                     |          |

| 9.5                 | ACTIVE-HALT MODE                                              |          |

| 9.6                 | AUTO WAKE UP FROM HALT MODE                                   |          |

|                     | ORTS                                                          |          |

| 10.1                |                                                               |          |

|                     |                                                               |          |

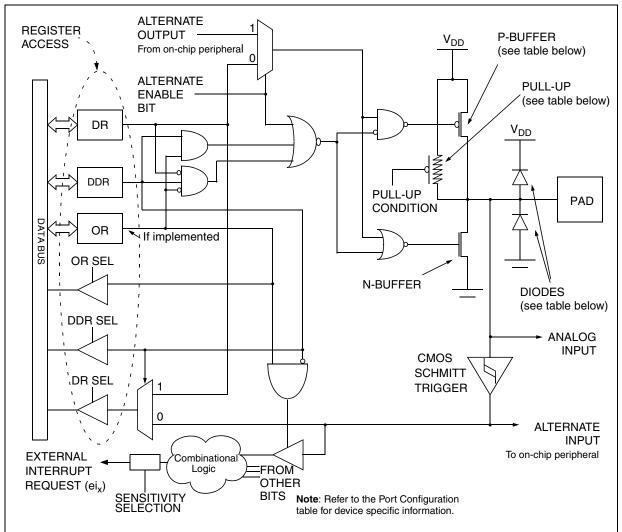

| 10.3                | I/O PORT IMPLEMENTATION                                       | 52       |

57

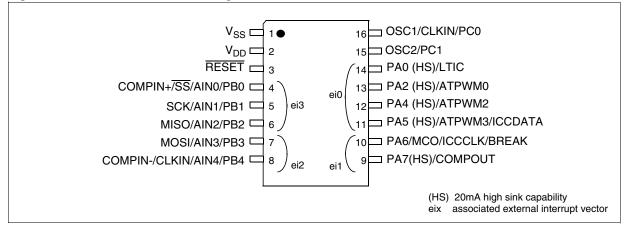

## PIN DESCRIPTION (Cont'd)

#### Figure 4. 16-Pin SO and DIP Package Pinout

# PIN DESCRIPTION (Cont'd)

#### Legend / Abbreviations for Table 1:

| Туре:            | I = input, O = output, S = supply                                      |

|------------------|------------------------------------------------------------------------|

| In/Output level: | $C_T$ = CMOS 0.3V <sub>DD</sub> /0.7V <sub>DD</sub> with input trigger |

| Output level:    | HS = 20mA high sink (on N-buffer only)                                 |

Port and control configuration:

- Input: float = floating, wpu = weak pull-up, int = interrupt, ana = analog

- Output: OD = open drain, PP = push-pull

The RESET configuration of each pin is shown in bold which is valid as long as the device is in reset state.

| Р          | in No | <b>)</b> . |                               |      | Le    | vel            |       | Po  | rt/C | Cont | trol |     |                  |                                                                                                                                                                                 |

|------------|-------|------------|-------------------------------|------|-------|----------------|-------|-----|------|------|------|-----|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 기20        | 0     | P16        | Pin Name                      | Type |       | ıt             |       | Inp | out  |      | Out  | put | Main<br>Function | Alternate Function                                                                                                                                                              |

| SO20/DP120 | QFN20 | SO16/DIP1  |                               | Тy   | Input | Output         | float | ndw | int  | ana  | ao   | dд  | (after<br>reset) |                                                                                                                                                                                 |

| 1          | 19    | 1          | V <sub>SS</sub> <sup>1)</sup> | S    |       |                |       |     |      |      |      |     | Ground           |                                                                                                                                                                                 |

| 2          | 20    | 2          | V <sub>DD</sub> <sup>1)</sup> | s    |       |                |       |     |      |      |      |     | Main power       | r supply                                                                                                                                                                        |

| 3          | 1     | 3          | RESET                         | I/O  | CT    |                |       | Х   |      |      | Х    |     | Top priority     | non maskable interrupt (active low)                                                                                                                                             |

| 4          | 2     | 4          | PB0/COMPIN+/<br>AIN0/SS       | I/O  | c     | ν              | x     | e   | i3   | x    | x    | x   | Port B0          | ADC Analog Input 0 <sup>2)</sup> or SPI Slave<br>Select (active low) or Analog Com-<br>parator Input<br><b>Caution:</b> No negative current in-<br>jection allowed on this pin. |

| 5          | 3     | 5          | PB1/AIN1/SCK                  | I/O  | C     | С <sub>т</sub> | x     |     |      | Х    | х    | х   | Port B1          | ADC Analog Input 1 <sup>2)</sup> or SPI Serial<br>Clock                                                                                                                         |

| 6          | 4     | 6          | PB2/AIN2/MISO                 | I/O  | C     | C <sub>T</sub> | х     |     |      | Х    | Х    | х   | Port B2          | ADC Analog Input 2 <sup>2)</sup> or SPI Mas-<br>ter In/ Slave Out Data                                                                                                          |

| 7          | 5     | 7          | PB3/AIN3/MOSI                 | I/O  | C     | C <sub>T</sub> | х     |     |      | Х    | Х    | х   | Port B3          | ADC Analog Input 3 <sup>2)</sup> or SPI Mas-<br>ter Out / Slave In Data                                                                                                         |

| 8          | 6     | 8          | PB4/AIN4/CLKIN/<br>COMPIN-    | I/O  | C     | Ът             | x     | e   | i2   | х    | х    | x   | Port B4          | ADC Analog Input 4 <sup>2)</sup> or External clock input or Analog Comparator External Reference Input                                                                          |

| 9          | 7     | -          | PB5/AIN5                      | I/O  | C     | ר <sub>ד</sub> | х     |     |      | Х    | Х    | Х   | Port B5          | ADC Analog Input 5 <sup>2)</sup>                                                                                                                                                |

| 10         | 8     | -          | PB6/AIN6                      | I/O  | C     | с, т           | Х     |     |      | Х    | Х    | Х   | Port B6          | ADC Analog Input 6 <sup>2)</sup>                                                                                                                                                |

| 11         | 9     | 9          | PA7/COMPOUT                   | I/O  | Ст    | HS             | Х     | e   | i1   |      | Х    | Х   | Port A7          | Analog Comparator Output                                                                                                                                                        |

# Table 1. Device Pin Description

57

## DATA EEPROM (Cont'd)

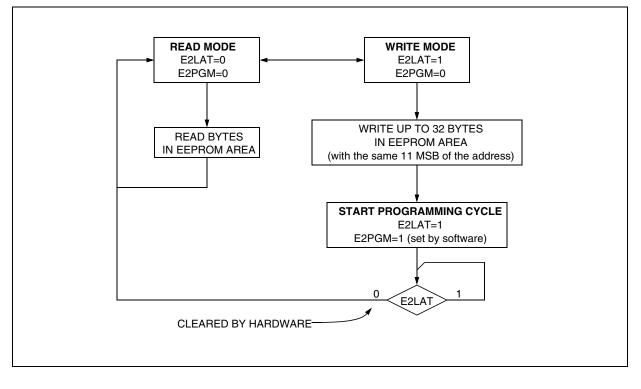

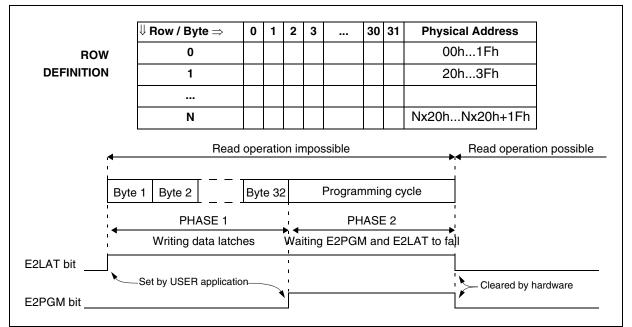

#### **5.3 MEMORY ACCESS**

The Data EEPROM memory read/write access modes are controlled by the E2LAT bit of the EEP-ROM Control/Status register (EECSR). The flowchart in Figure 8 describes these different memory access modes.

#### Read Operation (E2LAT=0)

The EEPROM can be read as a normal ROM location when the E2LAT bit of the EECSR register is cleared.

On this device, Data EEPROM can also be used to execute machine code. Take care not to write to the Data EEPROM while executing from it. This would result in an unexpected code being executed.

#### Write Operation (E2LAT=1)

To access the write mode, the E2LAT bit has to be set by software (the E2PGM bit remains cleared). When a write access to the EEPROM area occurs,

#### Figure 8. Data EEPROM Programming Flowchart

the value is latched inside the 32 data latches according to its address.

When PGM bit is set by the software, all the previous bytes written in the data latches (up to 32) are programmed in the EEPROM cells. The effective high address (row) is determined by the last EEP-ROM write sequence. To avoid wrong programming, the user must take care that all the bytes written between two programming sequences have the same high address: only the five Least Significant Bits of the address can change.

At the end of the programming cycle, the PGM and LAT bits are cleared simultaneously.

**Note**: Care should be taken during the programming cycle. Writing to the same memory location will over-program the memory (logical AND between the two write access data result) because the data latches are only cleared at the end of the programming cycle and by the falling edge of the E2LAT bit.

It is not possible to read the latched data. This note is illustrated by the Figure 10.

# DATA EEPROM (Cont'd)

57/

# Figure 9. Data E<sup>2</sup>PROM Write Operation

**Note:** If a programming cycle is interrupted (by a reset action), the integrity of the data in memory is not guaranteed.

## SYSTEM INTEGRITY MANAGEMENT (Cont'd)

#### 7.6.4 Register Description

#### SYSTEM INTEGRITY (SI) CONTROL/STATUS REGISTER (SICSR)

#### Read/Write

Reset Value: 0110 0xx0 (6xh)

| 7          |     |     |           |        |       |      | 0     |

|------------|-----|-----|-----------|--------|-------|------|-------|

| LOCK<br>32 | CR1 | CR0 | WDG<br>RF | LOCKED | LVDRF | AVDF | AVDIE |

#### Bit 7 = LOCK32 PLL 32Mhz Locked Flag

This bit is set and cleared by hardware. It is set automatically when the PLL 32Mhz reaches its operating frequency

- 0: PLL32 not locked

- 1: PLL32 locked

Bits 6:5 = **CR[1:0]** *RC* Oscillator Frequency Adjustment bits

These bits, as well as CR[9:2] bits in the RCCR register must be written immediately after reset to adjust the RC oscillator frequency and to obtain an accuracy of 1%. Refer to section 7.3 on page 25.

#### Bit 4 = WDGRF Watchdog Reset flag

This bit indicates that the last Reset was generated by the Watchdog peripheral. It is set by hardware (watchdog reset) and cleared by software (reading the SICSR register or writing 0 to this bit) or by an LVD Reset (to ensure a stable cleared state of the WDGRF flag when the CPU starts). Combined with the LVDRF flag information, the flag description is given by the following table.

| RESET Sources      | LVDRF | WDGRF |

|--------------------|-------|-------|

| External RESET pin | 0     | 0     |

| Watchdog           | 0     | 1     |

| LVD                | 1     | Х     |

#### Bit 3 = LOCKED PLL Locked Flag

This bit is set and cleared by hardware. It is set automatically when the PLL reaches its operating frequency.

0: PLL not locked

1: PLL locked

#### Bit 2 = LVDRF LVD reset flag

This bit indicates that the last Reset was generated by the LVD block. It is set by hardware (LVD reset) and cleared by software (by reading). When the LVD is disabled by OPTION BYTE, the LVDRF bit value is undefined.

#### Bit 1 = **AVDF** Voltage Detector Flag

This read-only bit is set and cleared by hardware. If the AVDIE bit is set, an interrupt request is generated when the AVDF bit is set. Refer to Figure 20 and to Section 7.6.2.1 for additional details.

0: V<sub>DD</sub> over AVD threshold

1: V<sub>DD</sub> under AVD threshold

#### Bit 0 = **AVDIE** Voltage Detector Interrupt Enable

This bit is set and cleared by software. It enables an interrupt to be generated when the AVDF flag is set. The pending interrupt information is automatically cleared when software enters the AVD interrupt routine.

0: AVD interrupt disabled

1: AVD interrupt enabled

#### **Application notes**

The LVDRF flag is not cleared when another RE-SET type occurs (external or watchdog), the LVDRF flag remains set to keep trace of the original failure.

In this case, a watchdog reset can be detected by software while an external reset can not.

#### PLL TEST REGISTER (PLLTST)

Read/Write

Reset Value: 0000 0000 (00h)

| 7       |   |   |   |   |   |   | 0 |

|---------|---|---|---|---|---|---|---|

| PLLdiv2 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### Bit 7 : PLLdiv2 PLL clock divide by 2

This bit is read or write by software and cleared by hardware after reset. This bit will divide the PLL output clock by 2.

0 : PLL output clock

1 : Divide by 2 of PLL output clock

Refer "Clock Management Block Diagram" on page 26

**Note :** Write of this bit will be effective after 2 Tcpu cycles (if system clock is 8mhz) else 1 cycle (if system clock is 4mhz) i.e. effective time is 250ns.

Bit 6:0 : Reserved , Must always be cleared

## INTERRUPTS (cont'd)

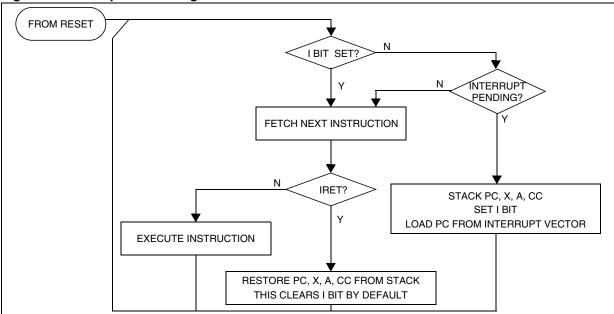

Figure 21. Interrupt Processing Flowchart

#### Table 5. Interrupt Mapping

**ل ح**ک

| N° | Source<br>Block | Description                                                     | Register<br>Label   | Priority<br>Order   | Exit<br>from<br>HALT or<br>AWUFH | Address<br>Vector |

|----|-----------------|-----------------------------------------------------------------|---------------------|---------------------|----------------------------------|-------------------|

|    | RESET           | Reset                                                           | N/A                 | Lighaat             | yes                              | FFFEh-FFFFh       |

|    | TRAP            | Software Interrupt                                              | N/A                 | Highest<br>Priority | no                               | FFFCh-FFFDh       |

| 0  | AWU             | Auto Wake Up Interrupt                                          | AWUCSR              |                     | yes <sup>1)</sup>                | FFFAh-FFFBh       |

| 1  | ei0             | External Interrupt 0                                            |                     |                     |                                  | FFF8h-FFF9h       |

| 2  | ei1             | External Interrupt 1                                            | N/A                 |                     | 1/00                             | FFF6h-FFF7h       |

| 3  | ei2             | External Interrupt 2                                            |                     |                     | yes                              | FFF4h-FFF5h       |

| 4  | ei3             | External Interrupt 3                                            |                     |                     |                                  | FFF2h-FFF3h       |

| 5  | LITE TIMER      | LITE TIMER RTC2 interrupt                                       | LTCSR2              |                     | no                               | FFF0h-FFF1h       |

| 6  | Comparator      | Comparator Interrupt                                            | CMPCR               |                     | no                               | FFEEh-FFEFh       |

| 7  | SI              | AVD interrupt                                                   | SICSR               |                     | no                               | FFECh-FFEDh       |

| 8  | AT TIMER        | AT TIMER Output Compare Interrupt<br>or Input Capture Interrupt | PWMxCSR<br>or ATCSR |                     | no                               | FFEAh-FFEBh       |

| 9  |                 | AT TIMER Overflow Interrupt                                     | ATCSR               |                     | yes <sup>2)</sup>                | FFE8h-FFE9h       |

| 10 | LITE TIMER      | LITE TIMER Input Capture Interrupt                              | LTCSR               |                     | no                               | FFE6h-FFE7h       |

| 11 |                 | LITE TIMER RTC1 Interrupt                                       | LTCSR               | V                   | yes <sup>2)</sup>                | FFE4h-FFE5h       |

| 12 | SPI             | SPI Peripheral Interrupts                                       | SPICSR              | Lowest              | yes                              | FFE2h-FFE3h       |

| 13 | AT TIMER        | AT TIMER Overflow Interrupt                                     | ATCSR2              | Priority            | no                               | FFE0h-FFE1h       |

Note 1: This interrupt exits the MCU from "Auto Wake-up from Halt" mode only.

**Note 2** : These interrupts exit the MCU from "ACTIVE-HALT" mode only.

# **9 POWER SAVING MODES**

#### 9.1 INTRODUCTION

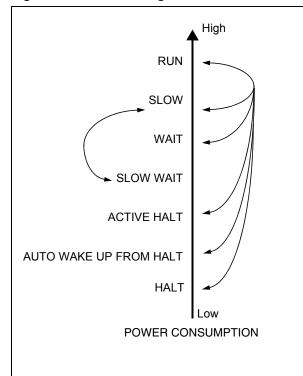

To give a large measure of flexibility to the application in terms of power consumption, five main power saving modes are implemented in the ST7 (see Figure 22):

- Slow

- Wait (and Slow-Wait)

- Active Halt

- Auto Wake up From Halt (AWUFH)

- Halt

After a RESET the normal operating mode is selected by default (RUN mode). This mode drives the device (CPU and embedded peripherals) by means of a master clock which is based on the main oscillator frequency divided or multiplied by 2 ( $f_{OSC2}$ ).

From RUN mode, the different power saving modes may be selected by setting the relevant register bits or by calling the specific ST7 software instruction whose action depends on the oscillator status.

#### Figure 22. Power Saving Mode Transitions

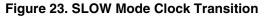

#### 9.2 SLOW MODE

This mode has two targets:

- To reduce power consumption by decreasing the internal clock in the device,

- To adapt the internal clock frequency (f<sub>CPU</sub>) to the available supply voltage.

SLOW mode is controlled by the SMS bit in the MCCSR register which enables or disables Slow mode.

In this mode, the oscillator frequency is divided by 32. The CPU and peripherals are clocked at this

lower frequency.

**Note**: SLOW-WAIT mode is activated when entering WAIT mode while the device is already in SLOW mode.

#### POWER SAVING MODES (Cont'd)

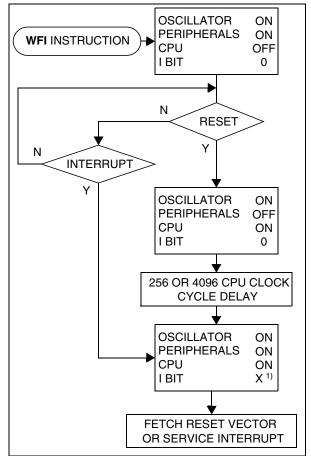

#### 9.3 WAIT MODE

WAIT mode places the MCU in a low power consumption mode by stopping the CPU.

This power saving mode is selected by calling the 'WFI' instruction.

All peripherals remain active. During WAIT mode, the I bit of the CC register is cleared, to enable all interrupts. All other registers and memory remain unchanged. The MCU remains in WAIT mode until an interrupt or RESET occurs, whereupon the Program Counter branches to the starting address of the interrupt or Reset service routine.

The MCU will remain in WAIT mode until a Reset or an Interrupt occurs, causing it to wake up.

Refer to Figure 24.

47/

#### Figure 24. WAIT Mode Flow-chart

#### Note:

**1.** Before servicing an interrupt, the CC register is pushed on the stack. The I bit of the CC register is set during the interrupt routine and cleared when the CC register is popped.

## POWER SAVING MODES (Cont'd)

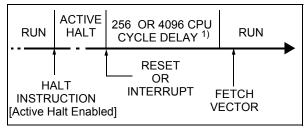

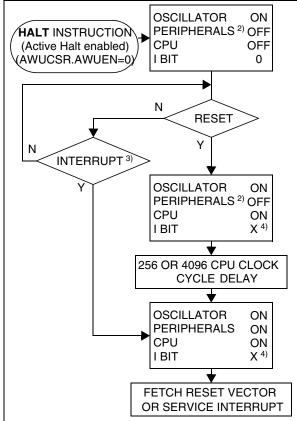

#### Figure 27. ACTIVE-HALT Timing Overview

#### Figure 28. ACTIVE-HALT Mode Flow-chart

#### Notes:

1. This delay occurs only if the MCU exits ACTIVE-HALT mode by means of a RESET.

2. Peripherals clocked with an external clock source can still be active.

3. Only the RTC1 interrupt and some specific interrupts can exit the MCU from ACTIVE-HALT mode. Refer to Table 5, "Interrupt Mapping," on page 37 for more details.

Before servicing an interrupt, the CC register is pushed on the stack. The I bit of the CC register is set during the interrupt routine and cleared when the CC register is popped.

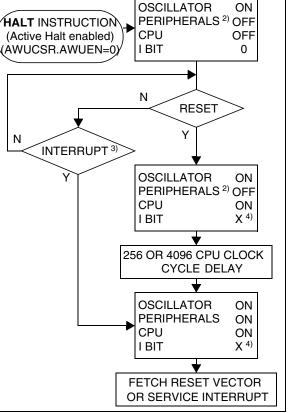

#### 9.6 AUTO WAKE UP FROM HALT MODE

Auto Wake Up From Halt (AWUFH) mode is similar to Halt mode with the addition of a specific internal RC oscillator for wake-up (Auto Wake Up from Halt Oscillator). Compared to ACTIVE-HALT mode, AWUFH has lower power consumption (the main clock is not kept running, but there is no accurate realtime clock available.

It is entered by executing the HALT instruction when the AWUEN bit in the AWUCSR register has been set.

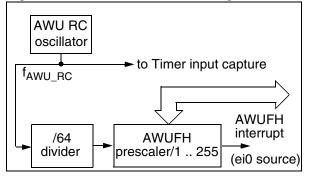

#### Figure 29. AWUFH Mode Block Diagram

As soon as HALT mode is entered, and if the AWUEN bit has been set in the AWUCSR register, the AWU RC oscillator provides a clock signal (fAWU RC). Its frequency is divided by a fixed divider and a programmable prescaler controlled by the AWUPR register. The output of this prescaler provides the delay time. When the delay has elapsed the AWUF flag is set by hardware and an interrupt wakes-up the MCU from Halt mode. At the same time the main oscillator is immediately turned on and a 256 or 4096 cycle delay is used to stabilize it. After this start-up delay, the CPU resumes operation by servicing the AWUFH interrupt. The AWU flag and its associated interrupt are cleared by software reading the AWUCSR register.

To compensate for any frequency dispersion of the AWU RC oscillator, it can be calibrated by measuring the clock frequency fAWU BC and then calculating the right prescaler value. Measurement mode is enabled by setting the AWUM bit in the AWUCSR register in Run mode. This connects fAWU BC to the input capture of the 12-bit Auto-Reload timer, allowing the fAWU RC to be measured using the main oscillator clock as a reference timebase.

# I/O PORTS (Cont'd)

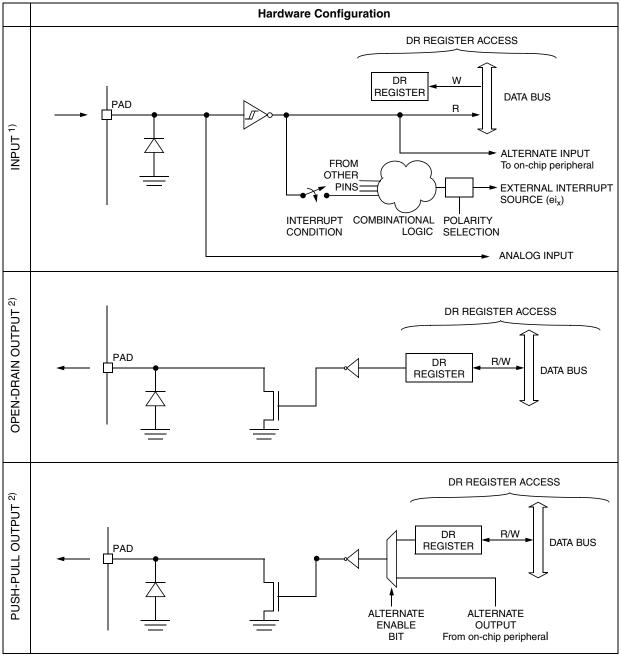

#### Table 8. I/O Port Mode Options

| Configuration Mode |                                 | Pull-Up | P-Buffer | Diodes             |                    |  |

|--------------------|---------------------------------|---------|----------|--------------------|--------------------|--|

|                    |                                 | Puil-Op | F-Builei | to V <sub>DD</sub> | to V <sub>SS</sub> |  |

| Input              | Floating with/without Interrupt | Off     | Off      |                    |                    |  |

| Input              | Pull-up with/without Interrupt  | On      | OII      | On                 | 05                 |  |

| Output             | Push-pull                       | Off     | On       |                    | On                 |  |

| Output             | Open Drain (logic level)        |         | Off      |                    |                    |  |

Legend: Off - implemented not activated On - implemented and activated

# I/O PORTS (Cont'd)

#### Table 9. I/O Configurations

#### Notes:

- 1. When the I/O port is in input configuration and the associated alternate function is enabled as an output, reading the DR register will read the alternate function output status.

- 2. When the I/O port is in output configuration and the associated alternate function is enabled as an input, the alternate function reads the pin status given by the DR register content.

#### DUAL 12-BIT AUTORELOAD TIMER 4 (Cont'd)

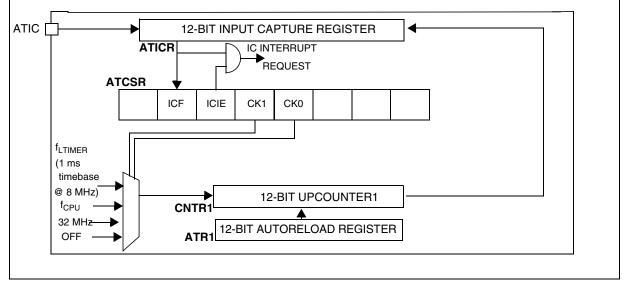

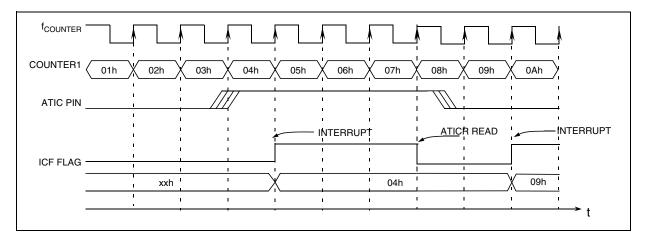

#### 11.2.3.5 Input Capture Mode

The 12-bit ATICR register is used to latch the value of the 12-bit free running upcounter CNTR1 after a rising or falling edge is detected on the ATIC pin. When an input capture occurs, the ICF bit is set and the ATICR register contains the value of the free running upcounter. An IC interrupt is generated if the ICIE bit is set. The ICF bit is reset by reading the ATICRH/ATICRL register when the ICF bit is set. The ATICR is a read only register and always contains the free running upcounter value which corresponds to the most recent input capture. Any further input capture is inhibited while the ICF bit is set.

#### Figure 43. Block Diagram of Input Capture Mode

Figure 44. Input Capture timing diagram

# DUAL 12-BIT AUTORELOAD TIMER 4 (Cont'd)

#### 11.2.6 Register Description

#### TIMER CONTROL STATUS REGISTER (ATCSR) Read / Write

Reset Value: 0x00 0000 (x0h)

| 7 |     |      |     |     |      |        | 0     |

|---|-----|------|-----|-----|------|--------|-------|

| 0 | ICF | ICIE | CK1 | CK0 | OVF1 | OVFIE1 | CMPIE |

Bit 7 = Reserved.

#### Bit 6 = **ICF** *Input Capture Flag.*

This bit is set by hardware and cleared by software by reading the ATICR register (a read access to ATICRH or ATICRL will clear this flag). Writing to this bit does not change the bit value.

0: No input capture

1: An input capture has occurred

Bit 5 = **ICIE** *IC* Interrupt Enable. This bit is set and cleared by software. 0: Input capture interrupt disabled 1: Input capture interrupt enabled

#### Bits 4:3 = **CK[1:0]** Counter Clock Selection.

These bits are set and cleared by software and cleared by hardware after a reset. They select the clock frequency of the counter.

| Counter Clock Selection                     | CK1 | СКО |

|---------------------------------------------|-----|-----|

| OFF                                         | 0   | 0   |

| 32 MHz                                      | 1   | 1   |

| f <sub>LTIMER</sub> (1 ms timebase @ 8 MHz) | 0   | 1   |

| f <sub>CPU</sub>                            | 1   | 0   |

#### Bit 2 = **OVF1** Overflow Flag.

This bit is set by hardware and cleared by software by reading the ATCSR register. It indicates the transition of the counter1 CNTR1 from FFFh to ATR1 value.

0: No counter overflow occurred

1: Counter overflow occurred

#### Bit 1 = **OVFIE1** Overflow Interrupt Enable.

This bit is read/write by software and cleared by hardware after a reset.

0: Overflow interrupt disabled.

1: Overflow interrupt enabled.

#### Bit 0 = **CMPIE** Compare Interrupt Enable.

This bit is read/write by software and cleared by hardware after a reset. It can be used to mask the interrupt generated when any of the CMPFx bit is set.

0: Output compare interrupt disabled.

1: Output Compare interrupt enabled.

#### **COUNTER REGISTER 1 HIGH (CNTR1H)**

Read only

Reset Value: 0000 0000 (00h)

| 15 |   |   |   |              |              |             | 8           |

|----|---|---|---|--------------|--------------|-------------|-------------|

| 0  | 0 | 0 | 0 | CNTR1_<br>11 | CNTR1_<br>10 | CNTR1_<br>9 | CNTR1_<br>8 |

# COUNTER REGISTER 1 LOW (CNTR1L)

Read only

7

Reset Value: 0000 0000 (00h)

| CNTR1 C | ONTR1 | CNTR1 | CNTR1 | CNTR1 | CNTR1 | CNTR1 | CNTR1 |

|---------|-------|-------|-------|-------|-------|-------|-------|

| 7       | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

Bits 15:12 = Reserved.

#### Bits 11:0 = CNTR1[11:0] Counter Value.

This 12-bit register is read by software and cleared by hardware after a reset. The counter CNTR1 increments continuously as soon as a counter clock is selected. To obtain the 12-bit value, software should read the counter value in two consecutive read operations. As there is no latch, it is recommended to read LSB first. In this case, CNTR1H can be incremented between the two read operations and to have an accurate result when  $f_{timer}=f_{CPU}$ , special care must be taken when CNTR1L values close to FFh are read.

When a counter overflow occurs, the counter restarts from the value specified in the ATR1 register.

0

## DUAL 12-BIT AUTORELOAD TIMER 4 (Cont'd)

# Table 14. Register Map and Reset Values

57

| Address<br>(Hex.) | Register<br>Label           | 7            | 6            | 5            | 4            | 3             | 2             | 1            | 0            |

|-------------------|-----------------------------|--------------|--------------|--------------|--------------|---------------|---------------|--------------|--------------|

| 0D                | ATCSR<br>Reset Value        | 0            | ICF<br>0     | ICIE<br>0    | CK1<br>0     | СК0<br>0      | OVF1<br>0     | OVFIE1<br>0  | CMPIE<br>0   |

| 0E                | CNTR1H<br>Reset Value       | 0            | 0            | 0            | 0            | CNTR1_11<br>0 | CNTR1_10<br>0 | CNTR1_9<br>0 | CNTR1_8<br>0 |

| 0F                | CNTR1L<br>Reset Value       | CNTR1_7<br>0 | CNTR1_8<br>0 | CNTR1_7<br>0 | CNTR1_6<br>0 | CNTR1_3<br>0  | CNTR1_2<br>0  | CNTR1_1<br>0 | CNTR1_0<br>0 |

| 10                | ATR1H<br>Reset Value        | 0            | 0            | 0            | 0            | ATR11<br>0    | ATR10<br>0    | ATR9<br>0    | ATR8<br>0    |

| 11                | ATR1L<br>Reset Value        | ATR7<br>0    | ATR6<br>0    | ATR5<br>0    | ATR4<br>0    | ATR3<br>0     | ATR2<br>0     | ATR1<br>0    | ATR0<br>0    |

| 12                | PWMCR<br>Reset Value        | 0            | OE3<br>0     | 0            | OE2<br>0     | 0             | OE1<br>0      | 0            | OE0<br>0     |

| 13                | PWM0CSR<br>Reset Value      | 0            | 0            | 0            | 0            | 0             | 0             | OP0<br>0     | CMPF0<br>0   |

| 14                | PWM1CSR<br>Reset Value      | 0            | 0            | 0            | 0            | 0             | 0             | OP1<br>0     | CMPF1<br>0   |

| 15                | PWM2CSR<br>Reset Value      | 0            | 0            | 0            | 0            | 0             | 0             | OP2<br>0     | CMPF2<br>0   |

| 16                | PWM3CSR<br>Reset Value      | 0            | 0            | 0            | 0            | OP_EN<br>0    | OPEDGE<br>0   | OP3<br>0     | CMPF3<br>0   |

| 17                | DCR0H<br>Reset Value        | 0            | 0            | 0            | 0            | DCR11<br>0    | DCR10<br>0    | DCR9<br>0    | DCR8<br>0    |

| 18                | DCR0L<br>Reset Value        | DCR7<br>0    | DCR6<br>0    | DCR5<br>0    | DCR4<br>0    | DCR3<br>0     | DCR2<br>0     | DCR1<br>0    | DCR0<br>0    |

| 19                | DCR1H<br>Reset Value        | 0            | 0            | 0            | 0            | DCR11<br>0    | DCR10<br>0    | DCR9<br>0    | DCR8<br>0    |

| 1A                | DCR1L<br>Reset Value        | DCR7<br>0    | DCR6<br>0    | DCR5<br>0    | DCR4<br>0    | DCR3<br>0     | DCR2<br>0     | DCR1<br>0    | DCR0<br>0    |

| 1B                | <b>DCR2H</b><br>Reset Value | 0            | 0            | 0            | 0            | DCR11<br>0    | DCR10<br>0    | DCR9<br>0    | DCR8<br>0    |

| 1C                | DCR2L<br>Reset Value        | DCR7<br>0    | DCR6<br>0    | DCR5<br>0    | DCR4<br>0    | DCR3<br>0     | DCR2<br>0     | DCR1<br>0    | DCR0<br>0    |

| 1D                | DCR3H<br>Reset Value        | 0            | 0            | 0            | 0            | DCR11<br>0    | DCR10<br>0    | DCR9<br>0    | DCR8<br>0    |

| 1E                | DCR3L<br>Reset Value        | DCR7<br>0    | DCR6<br>0    | DCR5<br>0    | DCR4<br>0    | DCR3<br>0     | DCR2<br>0     | DCR1<br>0    | DCR0<br>0    |

| 1F                | ATICRH<br>Reset Value       | 0            | 0            | 0            | 0            | ICR11<br>0    | ICR10<br>0    | ICR9<br>0    | ICR8<br>0    |

| 20                | ATICRL<br>Reset Value       | ICR7<br>0    | ICR6<br>0    | ICR5<br>0    | ICR4<br>0    | ICR3<br>0     | ICR2<br>0     | ICR1<br>0    | ICR0<br>0    |

## ANALOG COMPARATOR (Cont'd)

#### Bit 4 = CMPIF Comparator Interrupt Flag

This bit is set by hardware when interrupt is generated at the rising edge (CINV = 0) or falling edge (CINV = 1) of comparator output. This bit is cleared by reading the CMPCR register. Writing to this bit does not change the value.

0 : Comparator interrupt flag cleared

1 : Comparator interrupt flag set and can generate interrupt if CMPIE is set.

#### Bit 3 : CMPIE Comparator Interrupt Enable

This bit is set or reset by software and cleared by hardware reset. This bit enables or disables the interrupt generation depending on interrupt flag 0: Interrupt not generated

1: Interrupt generated if interrupt flag is set

#### Note:

57/

This bit should be set to enable interrupt only after the comparator has been switched ON, i.e. when CMPON is set.

Once CMPON bit is set, it is recommended to wait the specified stabilization time before setting CMPIE bit in order to avoid a spurious interrupt (see section 13.12 on page 143).

#### Bit 2 : CMP Comparator Output

This bit is set or reset by software and cleared by hardware reset. It stores the value of comparator output.

Bit 1 = COUT Comparator Output Enable on Port This bit is set or cleared by software. When this bit is set, the comparator output is available on PA7 port.

0 : Comparator output not connected to PA7

1 : Comparator output connected to PA7

#### Bit 0 : CMPON Comparator ON/OFF

This bit is set or cleared by software and reset by hardware reset. This bit is used to switch ON/OFF the comparator, internal voltage reference and current bias which provides  $4\mu$ A current to both. 0: Comparator, Internal Voltage Reference, Bias

- OFF (in power-down state).

- 1: Comparator, Internal Voltage Reference, Bias ON

**Note:** For the comparator interrupt generation, it takes 250ns delay from comparator output change to rising or falling edge of interrupt generated.

#### Table 21. Analog Comparator Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label | 7     | 6     | 5    | 4     | 3     | 2   | 1    | 0     |

|-------------------|-------------------|-------|-------|------|-------|-------|-----|------|-------|

| 002Ch             | VREFCR            | VCEXT | VCBGR | VR3  | VR2   | VR1   | VR0 | -    | -     |

|                   | Reset Value       | 0     | 0     | 0    | 0     | 0     | 0   | 0    | 0     |

| 002Dh             | CMPCR             | CHYST | -     | CINV | CMPIF | CMPIE | CMP | COUT | CMPON |

|                   | Reset value       | 1     | 0     | 0    | 0     | 0     | 0   | 0    | 0     |

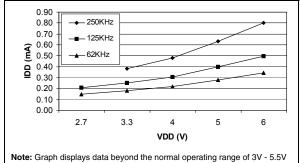

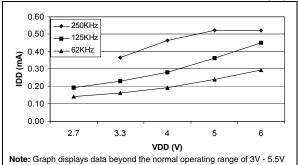

## Figure 73. Typical I<sub>DD</sub> in SLOW vs. f<sub>CPU</sub>

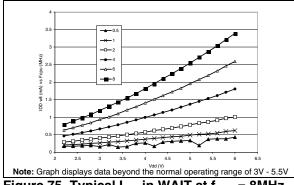

#### Figure 74. Typical I<sub>DD</sub> in WAIT vs. f<sub>CPU</sub>

Figure 75. Typical I<sub>DD</sub> in WAIT at f<sub>CPU</sub>= 8MHz

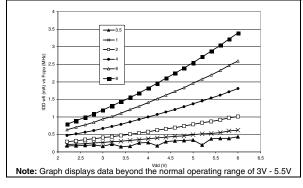

Figure 76. Typical I<sub>DD</sub> in SLOW-WAIT vs. f<sub>CPU</sub>

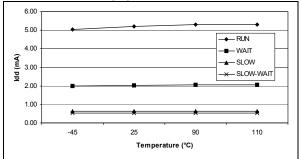

# Figure 77. Typical $I_{DD}$ vs. Temperature at $V_{DD}$ = 5V and $f_{CPU}$ = 8MHz

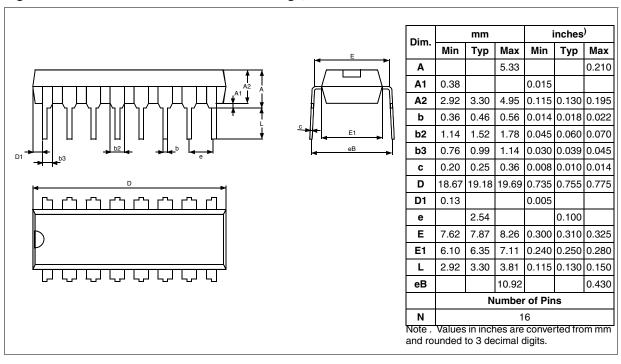

# **14 PACKAGE CHARACTERISTICS**

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a Lead-free second level interconnect. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard

JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label.

ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com.

#### 14.1 PACKAGE MECHANICAL DATA

#### Figure 113. 16-Pin Plastic Dual In-Line Package, 300-mil Width

## OPTION BYTES (Cont'd)

#### **OPTION BYTE 1**

OPT7 = **PLLx4x8** *PLL Factor selection.* 0: PLLx4 1: PLLx8

OPT6 = **PLLOFF** *PLL disable.* 0: PLL enabled 1: PLL disabled (by-passed)

OPT5 = **PLL32OFF** *32MHz PLL disable.* 0: PLL32 enabled 1: PLL32 disabled (by-passed)

OPT4 = **OSC** *RC* Oscillator selection 0: RC oscillator on 1: RC oscillator off

#### Notes:

- 1% RC oscillator available on ST7LITE15B and ST7LITE19B devices only

- If the RC oscillator is selected, then to improve clock stability and frequency accuracy, it is recommended to place a decoupling capacitor, typically 100nF, between the V<sub>DD</sub> and V<sub>SS</sub> pins as close as possible to the ST7 device.

# OPT3:2 = **LVD[1:0]** Low voltage detection selection

These option bits enable the LVD block with a selected threshold as shown in Table 26.

#### Table 26. LVD Threshold Configuration

| Configuration                     | LVD1 | LVD0 |

|-----------------------------------|------|------|

| LVD Off                           | 1    | 1    |

| Highest Voltage Threshold (~4.1V) | 1    | 0    |

| Medium Voltage Threshold (~3.5V)  | 0    | 1    |

| Lowest Voltage Threshold (~2.8V)  | 0    | 0    |

#### OPT1 = **WDG SW** Hardware or Software Watchdog

This option bit selects the watchdog type.

0: Hardware (watchdog always enabled)

1: Software (watchdog to be enabled by software)

OPT0 = **WDG HALT** *Watchdog Reset on Halt* This option bit determines if a RESET is generated when entering HALT mode while the Watchdog is active.

0: No Reset generation when entering Halt mode 1: Reset generation when entering Halt mode

| Operating conditions  |                              |     |                      | Option Bits |        |         |  |

|-----------------------|------------------------------|-----|----------------------|-------------|--------|---------|--|

| V <sub>DD</sub> range | Clock Source                 | PLL | Typ f <sub>CPU</sub> | OSC         | PLLOFF | PLLx4x8 |  |

|                       |                              | off | 1MHz @3.3V           | 0           | 1      | 1       |  |

|                       | Internal RC 1% <sup>1)</sup> | x4  | 4MHz @3.3V           | 0           | 0      | 0       |  |

| 2.7V - 3.3V           |                              | x8  | -                    | -           | -      | -       |  |

| 2.7 V - 3.3 V         |                              | off | 0-4MHz               | 1           | 1      | 1       |  |

|                       | External clock               | x4  | 4MHz                 | 1           | 0      | 0       |  |

|                       |                              | x8  | -                    | -           | -      | -       |  |

| 3.3V - 5.5V           |                              | off | 1MHz @5V             | 0           | 1      | 1       |  |

|                       | Internal RC 1% <sup>1)</sup> | x4  | -                    | -           | -      | -       |  |

|                       |                              | x8  | 8MHz @5V             | 0           | 0      | 1       |  |

|                       |                              | off | 0-8MHz               | 1           | 1      | 1       |  |

|                       | External clock               | x4  | -                    | -           | -      | -       |  |

|                       |                              | x8  | 8 MHz                | 1           | 0      | 1       |  |

#### Table 27. List of valid option combinations

Note 1: Configuration available on ST7LITE15B and ST7LITE19B devices only

Note: see Clock Management Block diagram in Figure 14

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com