Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ST7                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | SPI                                                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 17                                                                      |

| Program Memory Size        | 4KB (4K x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 128 x 8                                                                 |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 5x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                                          |

| Supplier Device Package    | -                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7fli19by1m3tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **2 PIN DESCRIPTION**

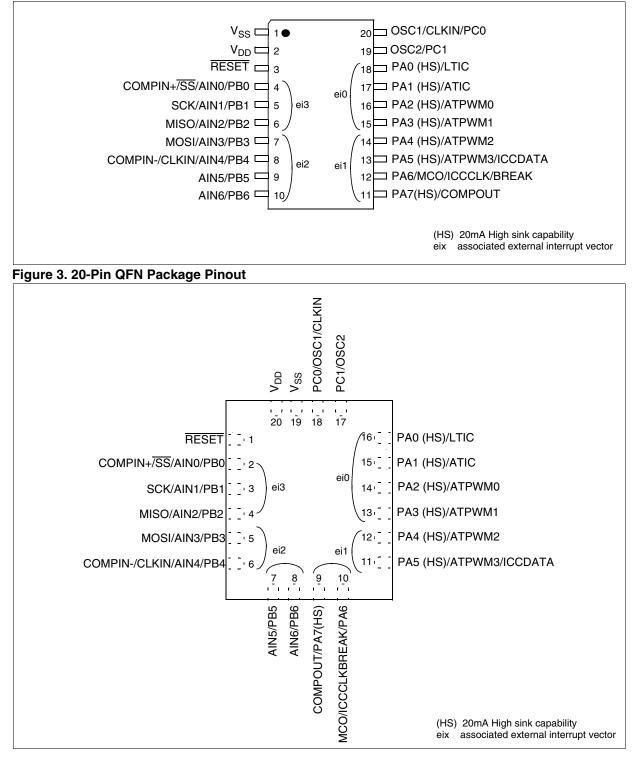

#### Figure 2. 20-Pin SO and DIP Package Pinout

# ST7LITE1xB

| Р          | in No | <b>o</b> . |                           |      | Le    | vel    |       | Po  | rt/C     | Cont | rol |     |                       |                                                                                                                                                                                                                                                                                                                                                              |

|------------|-------|------------|---------------------------|------|-------|--------|-------|-----|----------|------|-----|-----|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 120        | 0     | P16        | Pin Name                  | Type |       | ıt     |       | Inp | Input Ou |      | Out | put | Main<br>Function      | Alternate Function                                                                                                                                                                                                                                                                                                                                           |

| SO20/DPI20 | QFN20 | SO16/DIP16 | FIII Name                 | Ту   | Input | Output | float | ndm | int      | ana  | ОD  | ЬΡ  | (after<br>reset)      |                                                                                                                                                                                                                                                                                                                                                              |

|            |       |            |                           |      |       | •      |       |     | •        |      |     |     |                       | Main Clock Output or In Circuit<br>Communication Clock or External<br>BREAK                                                                                                                                                                                                                                                                                  |

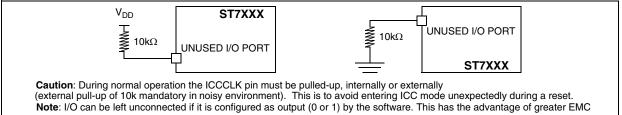

| 12         | 10    | 10         | PA6 /MCO/<br>ICCCLK/BREAK | I/O  | C     | Ст     | х     | ei  | i1       |      | х   | х   | Port A6               | <b>Caution:</b> During normal operation<br>this pin must be pulled- up, inter-<br>nally or externally (external pull-up<br>of 10k mandatory in noisy environ-<br>ment). This is to avoid entering ICC<br>mode unexpectedly during a reset.<br>In the application, even if the pin is<br>configured as output, any reset will<br>put it back in input pull-up |

| 13         | 11    | 11         | PA5 /ICCDATA/<br>ATPWM3   | I/O  | CT    | HS     | х     | e   | i1       |      | Х   | Х   | Port A5               | In Circuit Communication Data or<br>Auto-Reload Timer PWM3                                                                                                                                                                                                                                                                                                   |

| 14         | 12    | 12         | PA4/ATPWM2                | I/O  | CT    | HS     | Х     |     |          |      | Х   | Х   | Port A4               | Auto-Reload Timer PWM2                                                                                                                                                                                                                                                                                                                                       |

| 15         | 13    | -          | PA3/ATPWM1                | I/O  | Ст    | HS     | Х     |     |          |      | Х   | Х   | Port A3               | Auto-Reload Timer PWM1                                                                                                                                                                                                                                                                                                                                       |

| 16         | 14    | 13         | PA2/ATPWM0                | I/O  | CT    | HS     | X     | e   | i∩       |      | Х   | Х   | Port A2               | Auto-Reload Timer PWM0                                                                                                                                                                                                                                                                                                                                       |

| 17         | 15    | -          | PA1/ATIC                  | I/O  | CT    | HS     | Х     |     | 10       |      | Х   | Х   | Port A1               | Auto-Reload Timer Input Capture                                                                                                                                                                                                                                                                                                                              |

| 18         | 16    | 14         | PA0/LTIC                  | I/O  | CT    | HS     | Х     |     |          |      | Х   | Х   | Port A0               | Lite Timer Input Capture                                                                                                                                                                                                                                                                                                                                     |

| 19         | 17    | 15         | OSC2/PC1                  | I/O  |       |        | x     |     |          |      |     | х   | Port C1 <sup>3)</sup> | Resonator oscillator inverter out-<br>put                                                                                                                                                                                                                                                                                                                    |

| 20         | 18    | 16         | OSC1/CLKIN/PC0            | I/O  |       |        | X     |     |          |      |     | х   | Port C0 <sup>3)</sup> | Resonator oscillator inverter input<br>or External clock input                                                                                                                                                                                                                                                                                               |

## Notes:

1. It is mandatory to connect all available  $V_{DD}$  and  $V_{DDA}$  pins to the supply voltage and all  $V_{SS}$  and  $V_{SSA}$  pins to ground.

2. When the pin is configured as analog input, positive and negative current injections are not allowed.

3. PCOR not implemented but p-transistor always active in output mode (refer to Figure 32 on page 50).

## 7.3 REGISTER DESCRIPTION

#### MAIN CLOCK CONTROL/STATUS REGISTER (MCCSR)

Read / Write

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |     | 0   |

|---|---|---|---|---|---|-----|-----|

| 0 | 0 | 0 | 0 | 0 | 0 | мсо | SMS |

Bits 7:2 = Reserved, must be kept cleared.

#### Bit 1 = MCO Main Clock Out enable

This bit is read/write by software and cleared by hardware after a reset. This bit allows to enable the MCO output clock.

- 0: MCO clock disabled, I/O port free for general purpose I/O.

- 1: MCO clock enabled.

#### Bit 0 = SMS Slow Mode select

This bit is read/write by software and cleared by hardware after a reset. This bit selects the input clock  $f_{OSC}$  or  $f_{OSC}/32$ .

0: Normal mode ( $f_{CPU} = f_{OSC}$

1: Slow mode ( $f_{CPU} = f_{OSC}/32$ )

5/

#### **RC CONTROL REGISTER (RCCR)**

Read / Write

Reset Value: 1111 1111 (FFh)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| CR9 | CR8 | CR7 | CR6 | CR5 | CR4 | CR3 | CR2 |

Bits 7:0 = **CR[9:2]** *RC* Oscillator Frequency Adjustment Bits

These bits must be written immediately after reset to adjust the RC oscillator frequency and to obtain an accuracy of 1%. The application can store the correct value for each voltage range in EEPROM and write it to this register at start-up.

00h = maximum available frequency

FFh = lowest available frequency

These bits are used with the CR[1:0] bits in the SICSR register. Refer to section 7.6.4 on page 35.

**Note:** To tune the oscillator, write a series of different values in the register until the correct frequency is reached. The fastest method is to use a dichotomy starting with 80h.

- select rising edge

- reset the interrupt mask with the RIM instruction (in cases where a pin level change could occur)

#### 10.2.2 Output Modes

Setting the DDRx bit selects output mode. Writing to the DR bits applies a digital value to the I/O through the latch. Reading the DR bits returns the previously stored value.

If an OR bit is available, different output modes can be selected by software: push-pull or opendrain. Refer to I/O Port Implementation section for configuration.

DR Value and Output Pin Status

| DR | Push-Pull       | Open-Drain      |

|----|-----------------|-----------------|

| 0  | V <sub>OL</sub> | V <sub>OL</sub> |

| 1  | V <sub>OH</sub> | Floating        |

#### **10.2.3 Alternate Functions**

57/

Many ST7s I/Os have one or more alternate functions. These may include output signals from, or input signals to, on-chip peripherals. The Device Pin Description table describes which peripheral signals can be input/output to which ports.

A signal coming from an on-chip peripheral can be output on an I/O. To do this, enable the on-chip peripheral as an output (enable bit in the peripheral's control register). The peripheral configures the I/O as an output and takes priority over standard I/ O programming. The I/O's state is readable by addressing the corresponding I/O data register.

Configuring an I/O as floating enables alternate function input. It is not recommended to configure an I/O as pull-up as this will increase current consumption. Before using an I/O as an alternate input, configure it without interrupt. Otherwise spurious interrupts can occur.

Configure an I/O as input floating for an on-chip peripheral signal which can be input and output.

#### Caution:

I/Os which can be configured as both an analog and digital alternate function need special attention. The user must control the peripherals so that the signals do not arrive at the same time on the same pin. If an external clock is used, only the clock alternate function should be employed on that I/O pin and not the other alternate function.

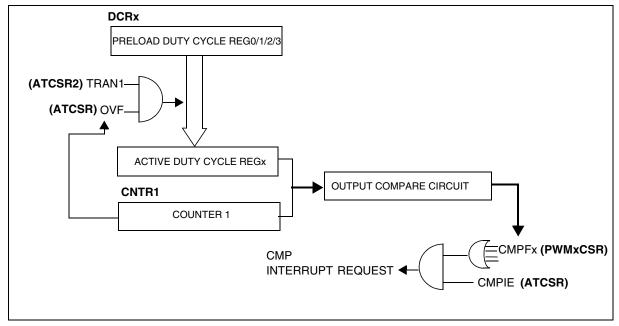

## DUAL 12-BIT AUTORELOAD TIMER 4 (Cont'd)

# 11.2.3.4 Output Compare Mode

5/

To use this function, load a 12-bit value in the Preload DCRxH and DCRxL registers.

When the 12-bit upcounter CNTR1 reaches the value stored in the Active DCRxH and DCRxL registers, the CMPFx bit in the PWMxCSR register is set and an interrupt request is generated if the CMPIE bit is set.

In single Timer mode the output compare function is performed only on CNTR1. The difference between both the modes is that, in Single Timer mode, CNTR1 can be compared with any of the four DCR registers, and in Dual Timer mode, CNTR1 is compared with DCR0 or DCR1 and CNTR2 is compared with DCR2 or DCR3.

#### Notes:

**1.** The output compare function is only available for DCRx values other than 0 (reset value).

**2.** Duty cycle registers are buffered internally. The CPU writes in Preload Duty Cycle Registers and these values are transferred in Active Duty Cycle Registers after an overflow event if the corresponding transfer bit (TRANx bit) is set. Output compare is done by comparing these active DCRx values with the counters.

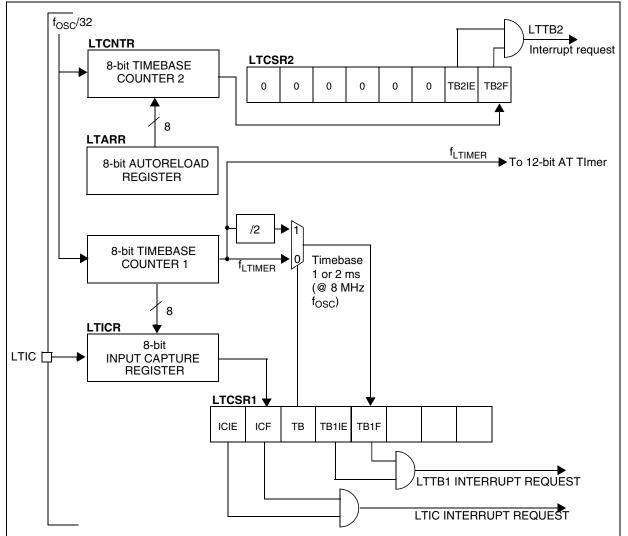

# 11.3 LITE TIMER 2 (LT2)

## 11.3.1 Introduction

The Lite Timer can be used for general-purpose timing functions. It is based on two free-running 8-bit upcounters and an 8-bit input capture register.

#### 11.3.2 Main Features

Realtime Clock

47/

– One 8-bit upcounter 1 ms or 2 ms timebase period (@ 8 MHz  $f_{OSC})$

#### Figure 51. Lite Timer 2 Block Diagram

- One 8-bit upcounter with autoreload and programmable timebase period from 4µs to 1.024ms in 4µs increments (@ 8 MHz f<sub>OSC</sub>)

- 2 Maskable timebase interrupts

- Input Capture

- 8-bit input capture register (LTICR)

- Maskable interrupt with wake-up from Halt mode capability

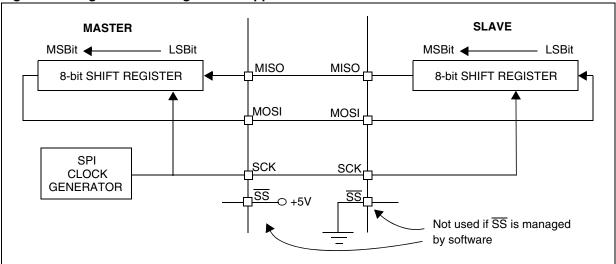

# SERIAL PERIPHERAL INTERFACE (cont'd)

#### 11.4.3.1 Functional Description

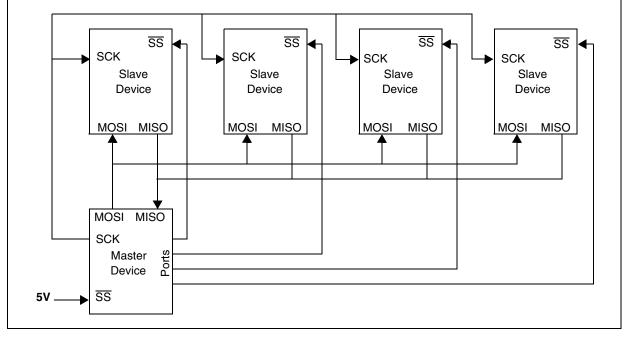

A basic example of interconnections between a single master and a single slave is illustrated in Figure 2.

The MOSI pins are connected together and the MISO pins are connected together. In this way data is transferred serially between master and slave (most significant bit first).

The communication is always initiated by the master. When the master device transmits data to a slave device via MOSI pin, the slave device responds by sending data to the master device via the MISO pin. This implies full duplex communication with both data out and data in synchronized with the same clock signal (which is provided by the master device via the SCK pin).

To use a single data line, the MISO and MOSI pins must be connected at each node (in this case only simplex communication is possible).

Four possible data/clock timing relationships may be chosen (see Figure 5 on page 7) but master and slave must be programmed with the same timing mode.

Figure 54. Single Master/ Single Slave Application

# SERIAL PERIPHERAL INTERFACE (cont'd)

# 11.4.5.4 Single Master and Multimaster Configurations

There are two types of SPI systems:

- Single Master System

- Multimaster System

57/

#### Single Master System

A typical single master system may be configured using a device as the master and four devices as slaves (see Figure 7).

The master device selects the individual slave devices by <u>using</u> four pins of a parallel port to control the four SS pins of the slave devices.

The  $\overline{SS}$  pins are pulled high during reset since the master device ports will be forced to be inputs at that time, thus disabling the slave devices.

**Note:** To prevent a bus conflict on the MISO line, the master allows only one active slave device during a transmission.

For more security, the slave device may respond to the master with the received data byte. Then the master will receive the previous byte back from the slave device if all MISO and MOSI pins are connected and the slave has not written to its SPIDR register.

Other transmission security methods can use ports for handshake lines or data bytes with command fields.

#### **Multimaster System**

A multimaster system may also be configured by the user. Transfer of master control could be implemented using a handshake method through the I/O ports or by an exchange of code messages through the serial peripheral interface system.

The multimaster system is principally handled by the MSTR bit in the SPICR register and the MODF bit in the SPICSR register.

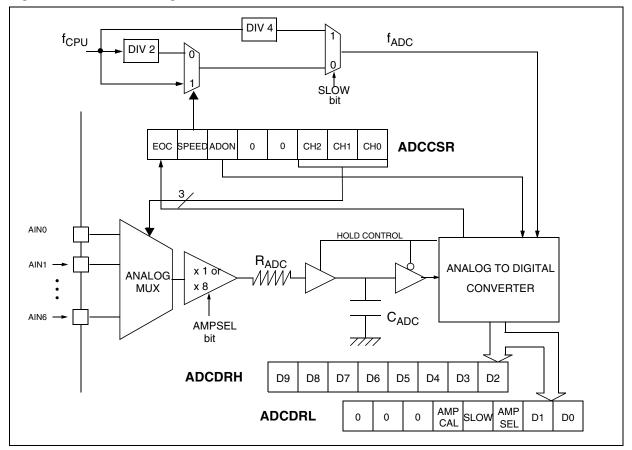

# 11.5 10-BIT A/D CONVERTER (ADC)

#### 11.5.1 Introduction

The on-chip Analog to Digital Converter (ADC) peripheral is a 10-bit, successive approximation converter with internal sample and hold circuitry. This peripheral has up to 7 multiplexed analog input channels (refer to device pin out description) that allow the peripheral to convert the analog voltage levels from up to 7 different sources.

The result of the conversion is stored in a 10-bit Data Register. The A/D converter is controlled through a Control/Status Register.

# 11.5.2 Main Features

- 10-bit conversion

- Up to 7 channels with multiplexed input

- Linear successive approximation

#### Figure 60. ADC Block Diagram

- Data register (DR) which contains the results

- Conversion complete status flag

- On/off bit (to reduce consumption)

The block diagram is shown in Figure 60.

## **11.5.3 Functional Description**

#### 11.5.3.1 Analog Power Supply

$V_{DDA}$  and  $V_{SSA}$  are the high and low level reference voltage pins. In some devices (refer to device pin out description) they are internally connected to the  $V_{DD}$  and  $V_{SS}$  pins.

Conversion accuracy may therefore be impacted by voltage drops and noise in the event of heavily loaded or badly decoupled power supply lines.

47/

# 10-BIT A/D CONVERTER (ADC) (Cont'd)

## 11.5.3.2 Input Voltage Amplifier

The input voltage can be amplified by a factor of 8 by enabling the AMPSEL bit in the ADCDRL register.

When the amplifier is enabled, the input range is 0V to  $V_{\mbox{\scriptsize DD}}/8.$

For example, if  $V_{DD} = 5V$ , then the ADC can convert voltages in the range 0V to 430mV with an ideal resolution of 0.6mV (equivalent to 13-bit resolution with reference to a  $V_{SS}$  to  $V_{DD}$  range).

For more details, refer to the Electrical characteristics section.

**Note:** The amplifier is switched on by the ADON bit in the ADCCSR register, so no additional startup time is required when the amplifier is selected by the AMPSEL bit.

## 11.5.3.3 Digital A/D Conversion Result

The conversion is monotonic, meaning that the result never decreases if the analog input does not and never increases if the analog input does not.

If the input voltage ( $V_{AIN}$ ) is greater than  $V_{DDA}$  (high-level voltage reference) then the conversion result is FFh in the ADCDRH register and 03h in the ADCDRL register (without overflow indication).

If the input voltage ( $V_{AIN}$ ) is lower than  $V_{SSA}$  (low-level voltage reference) then the conversion result in the ADCDRH and ADCDRL registers is 00 00h.

The A/D converter is linear and the digital result of the conversion is stored in the ADCDRH and AD-CDRL registers. The accuracy of the conversion is described in the Electrical Characteristics Section.

$R_{AIN}$  is the maximum recommended impedance for an analog input signal. If the impedance is too high, this will result in a loss of accuracy due to leakage and sampling not being completed in the alloted time.

## 11.5.3.4 A/D Conversion

The analog input ports must be configured as input, no pull-up, no interrupt. Refer to the «I/O ports» chapter. Using these pins as analog inputs does not affect the ability of the port to be read as a logic input.

In the ADCCSR register:

57/

Select the CH[2:0] bits to assign the analog channel to convert.

## ADC Conversion mode

In the ADCCSR register:

Set the ADON bit to enable the A/D converter and to start the conversion. From this time on, the ADC performs a continuous conversion of the selected channel.

When a conversion is complete:

- The EOC bit is set by hardware.

- The result is in the ADCDR registers.

A read to the ADCDRH or a write to any bit of the ADCCSR register resets the EOC bit.

To read the 10 bits, perform the following steps:

- 1. Poll the EOC bit

- 2. Read ADCDRL

- 3. Read ADCDRH. This clears EOC automatically.

To read only 8 bits, perform the following steps:

- 1. Poll EOC bit

- 2. Read ADCDRH. This clears EOC automatically.

#### 11.5.3.5 Changing the conversion channel

The application can change channels during conversion.

When software modifies the CH[2:0] bits in the ADCCSR register, the current conversion is stopped, the EOC bit is cleared, and the A/D converter starts converting the newly selected channel.

## 11.5.4 Low Power Modes

**Note:** The A/D converter may be disabled by resetting the ADON bit. This feature allows reduced power consumption when no conversion is needed and between single shot conversions.

| Mode | Description                                                                                                                                                            |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on A/D Converter                                                                                                                                             |

|      | A/D Converter disabled.                                                                                                                                                |

| HALT | After wakeup from Halt mode, the A/D Converter requires a stabilization time $t_{STAB}$ (see Electrical Characteristics) before accurate conversions can be performed. |

#### 11.5.5 Interrupts

None.

# **OPERATING CONDITIONS** (Cont'd)

The RC oscillator and PLL characteristics are temperature-dependent and are grouped in four tables. 13.3.5.1 Devices with ""6" or "3" order code suffix (tested for  $T_A = -40$  to +125°C) @  $V_{DD} = 5V$

| Symbol               | Parameter                                         | Conditions                                                               | Min  | Тур               | Max              | Unit |

|----------------------|---------------------------------------------------|--------------------------------------------------------------------------|------|-------------------|------------------|------|

| 4                    | Internal RC oscillator fre-                       | RCCR = FF (reset value), T <sub>A</sub> =25°C,V <sub>DD</sub> =5V        |      | 700               |                  |      |

| f <sub>RC</sub>      | quency <sup>1)</sup>                              | RCCR = RCCR0 <sup>2</sup> ),T <sub>A</sub> =25°C,V <sub>DD</sub> =5V     | 992  | 1000              | 1008             | kHz  |

|                      |                                                   | T <sub>A</sub> =25°C,V <sub>DD</sub> =5V                                 | -0.8 |                   | +0.8             | %    |

|                      |                                                   | T <sub>A</sub> =25°C, V <sub>DD</sub> =4.5 to 5.5V <sup>3)</sup>         | -1   |                   | +1               | %    |

|                      | Accuracy of Internal RC                           | T <sub>A</sub> =25°C to +85°C,V <sub>DD</sub> =5V                        | -3   |                   | +3               | %    |

| ACC <sub>RC</sub>    | oscillator with                                   | $T_A=25^{\circ}C$ to +85°C, $V_{DD}=4.5$ to 5.5 $V^{3}$                  | -3.5 |                   | +3.5             | %    |

|                      | RCCR=RCCR0 <sup>2)</sup>                          | T <sub>A</sub> =85°C to +125°C,V <sub>DD</sub> =5V                       | -3.5 |                   | +5               | %    |

|                      |                                                   | $T_A=85^{\circ}C$ to +125°C, $V_{DD}=4.5$ to 5.5 $V^{3}$                 | -3.5 |                   | +6               | %    |

|                      |                                                   | $T_A = -40 \text{ to } +25^{\circ}\text{C}, V_{DD} = 5V^{3)}$            | -3   |                   | +7               | %    |

| I <sub>DD(RC)</sub>  | RC oscillator current con-<br>sumption            | T <sub>A</sub> =25°C,V <sub>DD</sub> =5V                                 |      | 600 <sup>3)</sup> |                  | μA   |

| t <sub>su(RC)</sub>  | RC oscillator setup time                          | T <sub>A</sub> =25°C,V <sub>DD</sub> =5V                                 |      |                   | 10 <sup>2)</sup> | μs   |

| f <sub>PLL</sub>     | x8 PLL input clock                                |                                                                          |      | 1 <sup>3)</sup>   |                  | MHz  |

| t <sub>LOCK</sub>    | PLL Lock time <sup>5)</sup>                       |                                                                          |      | 2                 |                  | ms   |

| t <sub>STAB</sub>    | PLL Stabilization time <sup>5)</sup>              |                                                                          |      | 4                 |                  | ms   |

| 100                  |                                                   | f <sub>RC</sub> = 1MHz@T <sub>A</sub> =25°C,V <sub>DD</sub> =4.5 to 5.5V |      | 0.1 <sup>4)</sup> |                  | %    |

| ACC <sub>PLL</sub>   | x8 PLL Accuracy                                   | $f_{RC} = 1MHz@T_A = -40 \text{ to } +85^{\circ}C, V_{DD} = 5V$          |      | 0.1 <sup>4)</sup> |                  | %    |

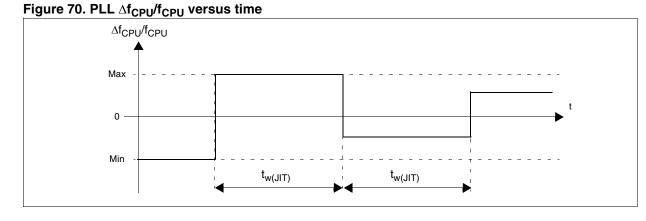

| t <sub>w(JIT)</sub>  | PLL jitter period 6)                              | f <sub>RC</sub> = 1MHz                                                   |      | 120               |                  | μs   |

| JIT <sub>PLL</sub>   | PLL jitter (∆f <sub>CPU</sub> /f <sub>CPU</sub> ) |                                                                          |      | 1 <sup>7)</sup>   |                  | %    |

| I <sub>DD(PLL)</sub> | PLL current consumption                           | T <sub>A</sub> =25°C                                                     |      | 600 <sup>3)</sup> |                  | μA   |

#### Notes:

5/

1. If the RC oscillator clock is selected, to improve clock stability and frequency accuracy, it is recommended to place a decoupling capacitor, typically 100nF, between the  $V_{DD}$  and  $V_{SS}$  pins as close as possible to the ST7 device.

2. See "INTERNAL RC OSCILLATOR ADJUSTMENT" on page 23

3. Data based on characterization results, not tested in production

4. Averaged over a 4ms period. After the LOCKED bit is set, a period of t<sub>STAB</sub> is required to reach ACC<sub>PLL</sub> accuracy.

- 5. After the LOCKED bit is set ACC<sub>PLL</sub> is max. 10% until t<sub>STAB</sub> has elapsed. See Figure 13 on page 24.

- 6. This period is the phase servo loop period. During this period, the frequency remains unchanged.

7. Guaranteed by design.

# **OPERATING CONDITIONS** (Cont'd)

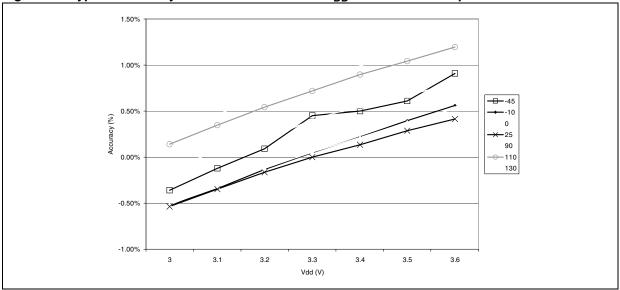

# Figure 68. Typical accuracy with RCCR=RCCR1 vs V<sub>DD</sub>= 3-3.6V and Temperature

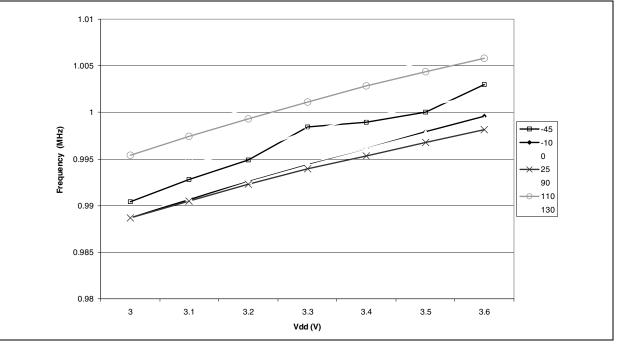

# Figure 69. Typical RCCR1 vs $V_{\text{DD}}$ and Temperature

57

# **OPERATING CONDITIONS** (Cont'd)

## 13.3.5.3 32MHz PLL

$T_A = -40$  to 125°C, unless otherwise specified

| Symbol             | Parameter               | Min | Тур | Max | Unit |

|--------------------|-------------------------|-----|-----|-----|------|

| V <sub>DD</sub>    | Voltage <sup>1)</sup>   | 4.5 | 5   | 5.5 | V    |

| f <sub>PLL32</sub> | Frequency <sup>1)</sup> |     | 32  |     | MHz  |

| f <sub>INPUT</sub> | Input Frequency         | 7   | 8   | 9   | MHz  |

#### Note:

**\$7**

**1.** 32 MHz is guaranteed within this voltage range.

# CLOCK AND TIMING CHARACTERISTICS (Cont'd)

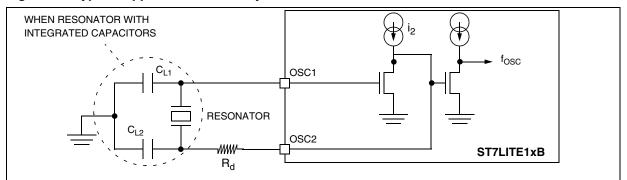

## 13.5.4 Crystal and Ceramic Resonator Oscillators

The ST7 internal clock can be supplied with ten different Crystal/Ceramic resonator oscillators. All the information given in this paragraph are based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal/ceramic resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol                             | Parameter                                                                                                                      | Conditions | Min | Тур         | Max | Unit |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------|-----|-------------|-----|------|

| f <sub>CrOSC</sub>                 | Crystal Oscillator Frequency                                                                                                   |            | 2   |             | 16  | MHz  |

| C <sub>L1</sub><br>C <sub>L2</sub> | Recommended load capacitance ver-<br>sus equivalent serial resistance of the<br>crystal or ceramic resonator (R <sub>S</sub> ) |            | Se  | e table bel | low | pF   |

| Supplier | f <sub>CrOSC</sub> | Туріса             | I Ceramic Resonators <sup>1)</sup> | CL1 <sup>3)</sup> | CL2 <sup>3)</sup> | Rd                  | Supply Voltage | Temperature |

|----------|--------------------|--------------------|------------------------------------|-------------------|-------------------|---------------------|----------------|-------------|

| Supplier | (MHz)              | Type <sup>2)</sup> | Reference                          | [pF]              | [pF]              | <b>[</b> Ω <b>]</b> | Range [V]      | Range [°C]  |

|          | 1                  | SMD                | CSBFB1M00J58-R0                    | 220               | 220               | 2.2k                | 3.3V to 5.5V   |             |

|          | I                  | LEAD               | CSBLA1M00J58-B0                    | 220               | 220               | 2.2k                | 5.50 10 5.50   |             |

|          | 2                  | SMD                | CSTCC2M00G56Z-R0                   | (47)              | (47)              | 0                   |                |             |

|          | 4                  | SMD                | CSTCR4M00G53Z-R0                   | (15)              | (15)              | 0                   | 3.0V to 5.5V   |             |

| Murata   | 4                  | LEAD               | CSTLS4M00G53Z-B0                   | (15)              | (15)              | 0                   | 3.00 10 3.30   | -40 to 85   |

| Mur      | 8                  | SMD                | CSTCE8M00G52Z-R0                   | (10)              | (10)              | 0                   |                | -40 10 85   |

|          | 0                  | LEAD               | CSTLS8M00G53Z-B0                   | (15)              | (15)              | 0                   |                |             |

|          | 12                 | SMD                | CSTCE12M0G52Z-R0                   | (10)              | (10)              | 0                   |                |             |

|          | 16                 | SMD                | CSTCE16M0V51Z-R0                   | (5)               | (5)               | 0                   | 3.3V to 5.5V   |             |

|          | 10                 | LEAD               | CSTLS16M0X51Z-B0                   | (5)               | (5)               | 0                   |                |             |

#### Notes:

57

1. Resonator characteristics given by the ceramic resonator manufacturer. For more information on these resonators, please consult www.murata.com

2. SMD = [-R0: Plastic tape package (Ø =180mm)]

LEAD = [-B0: Bulk]

3. () means load capacitor built in resonator

#### Figure 79. Typical Application with a Crystal or Ceramic Resonator

## **13.7 EMC CHARACTERISTICS**

Susceptibility tests are performed on a sample basis during product characterization.

# 13.7.1 Functional EMS (Electro Magnetic Susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electro magnetic events until a failure occurs (indicated by the LEDs).

- ESD: Electro-Static Discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

# 13.7.1.1 Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations:

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### Prequalification trials:

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the RE-SET pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behaviour is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol            | Parameter                                                                                                                                | Conditions                                                                                     | Level/<br>Class |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                           | $V_{DD}$ =5V, $T_A$ =+25°C, $f_{OSC}$ =8MHz conforms to IEC 1000-4-2                           | 2B              |

| V <sub>FFTB</sub> | Fast transient voltage burst limits to be applied through 100pF on $V_{\rm DD}$ and $V_{\rm SS}$ pins to induce a functional disturbance | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C, f <sub>OSC</sub> =8MHz<br>conforms to IEC 1000-4-4 | 3B              |

#### 13.7.2 Electro Magnetic Interference (EMI)

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm SAE J 1752/3 which specifies the board and the loading of each pin.

| Symbol           | Parameter  | Conditions                                                                                 | Monitored                                                                                          | Max vs. [1 | Unit |      |

|------------------|------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------|------|------|

| Symbol           | Farameter  | Conditions                                                                                 | Frequency Band 8/4MHz 16/8M   0.1MHz to 30MHz 15 21   30MHz to 130MHz 22 29   130MHz to 1GHz 17 22 | 16/8MHz    |      |      |

|                  |            | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C,<br>SO20 package,<br>conforming to SAE J 1752/3 | 0.1MHz to 30MHz                                                                                    | 15         | 21   |      |

| S                | Peak level |                                                                                            | 30MHz to 130MHz                                                                                    | 22         | 29   | dBμV |

| S <sub>EMI</sub> | I Carlevel |                                                                                            | 130MHz to 1GHz                                                                                     | 17         | 22   |      |

|                  |            |                                                                                            | SAE EMI Level                                                                                      | 3.5        | 3.5  | -    |

#### Note:

1. Data based on characterization results, not tested in production.

# **13.8 I/O PORT PIN CHARACTERISTICS**

## **13.8.1 General Characteristics**

Subject to general operating conditions for  $V_{DD}$ ,  $f_{OSC}$ , and  $T_A$  unless otherwise specified.

| Symbol                | Parameter                                                                        | Conditions                                        |                                            | Min                   | Тур | Max                             | Unit             |

|-----------------------|----------------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------|-----------------------|-----|---------------------------------|------------------|

| V <sub>IL</sub>       | Input low level voltage                                                          |                                                   |                                            | V <sub>SS</sub> - 0.3 |     | $0.3 \mathrm{xV}_{\mathrm{DD}}$ | V                |

| V <sub>IH</sub>       | Input high level voltage                                                         |                                                   |                                            | 0.7xV <sub>DD</sub>   |     | V <sub>DD</sub> + 0.3           | v                |

| V <sub>hys</sub>      | Schmitt trigger voltage                                                          |                                                   |                                            |                       | 400 |                                 | mV               |

| ΙL                    | Input leakage current                                                            | V <sub>SS</sub> ≤V <sub>IN</sub> ≤V <sub>DD</sub> |                                            |                       |     | ±1                              |                  |

| ۱ <sub>S</sub>        | Static current consumption in-<br>duced by each floating input pin <sup>2)</sup> | Floating input mode                               |                                            |                       | 400 |                                 | μA               |

| D                     | Weak pull-up equivalent                                                          | V _V                                              | V <sub>DD</sub> =5V<br>V <sub>DD</sub> =3V | 50                    | 120 | 250                             | kΩ               |

| R <sub>PU</sub>       | resistor <sup>3)</sup>                                                           | VIN-VSS                                           | V <sub>DD</sub> =3V                        |                       | 160 |                                 | K52              |

| C <sub>IO</sub>       | I/O pin capacitance                                                              |                                                   |                                            |                       | 5   |                                 | pF               |

| t <sub>f(IO)out</sub> | Output high to low level fall time <sup>1)</sup>                                 | C <sub>I</sub> =50pF                              |                                            |                       | 25  |                                 | 20               |

| t <sub>r(IO)out</sub> | Output low to high level rise time <sup>1)</sup>                                 | Between                                           | 10% and 90%                                |                       | 25  |                                 | ns               |

| t <sub>w(IT)in</sub>  | External interrupt pulse time 4)                                                 |                                                   |                                            | 1                     |     |                                 | t <sub>CPU</sub> |

#### Notes:

1. Data based on validation/design results.

**2.** Configuration not recommended, all unused pins must be kept at a fixed voltage: using the output mode of the I/O for example or an external pull-up or pull-down resistor (see Figure 80). Static peak current value taken at a fixed  $V_{IN}$  value, based on design simulation and technology characteristics, not tested in production. This value depends on  $V_{DD}$  and temperature values.

3. The R<sub>PU</sub> pull-up equivalent resistor is based on a resistive transistor.

4. To generate an external interrupt, a minimum pulse width has to be applied on an I/O port pin configured as an external interrupt source.

#### Figure 80. Two typical Applications with unused I/O Pin

robustness and lower cost.

## **13.12 ANALOG COMPARATOR CHARACTERISTICS**

| Symbol               | Parameter                                          | Conditions | Min | Тур <sup>1)</sup> | Max              | Unit |

|----------------------|----------------------------------------------------|------------|-----|-------------------|------------------|------|

| V <sub>DDA</sub>     | Supply range                                       |            | 4.5 |                   | 5.5              | V    |

| V <sub>IN</sub>      | Comparator input voltage range                     |            | 0   |                   | V <sub>DDA</sub> | V    |

| Temp                 | Temperature range                                  |            | -40 |                   | 125              | °C   |

| V <sub>offset</sub>  | Comparator offset error                            |            |     | 20                |                  | mV   |

|                      | Analog Comparator Consumption                      |            |     | 120               |                  | μA   |

| I <sub>DD(CMP)</sub> | Analog Comparator Consumption<br>during power-down |            |     | 200               |                  | pА   |

| t <sub>propag</sub>  | Comparator propagation delay                       |            |     | 40                |                  | ns   |

| t <sub>startup</sub> | Startup filter duration                            |            |     | 500 <sup>2)</sup> |                  | ns   |

| t <sub>stab</sub>    | Stabilisation time                                 |            |     | 500               |                  | ns   |

# **13.13 PROGRAMMABLE INTERNAL VOLTAGE REFERENCE CHARACTERISTICS**

| Symbol                   | Parameter                                                      | Conditions | Min | Typ <sup>1)</sup> | Max | Unit |

|--------------------------|----------------------------------------------------------------|------------|-----|-------------------|-----|------|

| V <sub>DDA</sub>         | Supply range                                                   |            | 4   | 5                 | 5.5 | V    |

| Temp                     | Temperature range                                              |            | -40 | 27                | 125 | °C   |

|                          | Internal Voltage<br>Reference Consumption                      |            |     | 50                |     | μA   |

| I <sub>DD(VOLTREF)</sub> | Internal Voltage<br>Reference Consumption<br>during power-down |            |     | 200               |     | pА   |

| t <sub>startup</sub>     | Startup duration                                               |            |     | 1 <sup>2)</sup>   |     | μs   |

#### 13.14 CURRENT BIAS CHARACTERISTICS (for Comparator and Internal Voltage Reference)

| Symbol               | Parameter                              | Conditions | Min | <b>Typ</b> <sup>1)</sup> | Max | Unit |

|----------------------|----------------------------------------|------------|-----|--------------------------|-----|------|

| V <sub>DDA</sub>     | Supply range                           |            | 4.5 | 5                        | 5.5 | V    |

| Temp                 | Temperature range                      |            | -40 | 27                       | 125 | °C   |

|                      | Bias Consumption in run mode           |            |     | 50                       |     | μA   |

| IDD (Bias)           | Bias Consumption during power-<br>down |            |     | 36                       |     | pА   |

| t <sub>startup</sub> | Startup time                           |            |     | 1 <sup>2)</sup>          |     | μs   |

#### Notes:

<u>(</u>ح)

1. Unless otherwise specified, typical data are based on  $T_A=25^{\circ}C$  and  $V_{DD}-V_{SS}=5V$ . They are given only as design guide-lines and are not tested.

**2.** Since startup time for internal voltage reference and bias is 1  $\mu$ s, comparator correct output should not be expected before 1  $\mu$ s during startup.

#### **14.2 SOLDERING INFORMATION**

In accordance with the RoHS European directive, all STMicroelectronics packages have been converted to lead-free technology, named ECO-PACK<sup>TM</sup>.

- ECOPACK<sup>TM</sup> packages are qualified according to the JEDEC STD-020C compliant soldering profile.

- Detailed information on the STMicroelectronics ECOPACK<sup>TM</sup> transition program is available on www.st.com/stonline/leadfree/, with specific technical Application notes covering the main technical aspects related to lead-free conversion (AN2033, AN2034, AN2035, AN2036).

#### Backward and forward compatibility:

The main difference between Pb and Pb-free soldering process is the temperature range.

- ECOPACK<sup>TM</sup> TQFP, SDIP, SO and QFN20 packages are fully compatible with Lead (Pb) containing soldering process (see application note AN2034)

- TQFP, SDIP and SO Pb-packages are compatible with Lead-free soldering process, nevertheless it's the customer's duty to verify that the Pb-packages maximum temperature (mentioned on the Inner box label) is compatible with their Lead-free soldering temperature.

#### Table 25. Soldering Compatibility (wave and reflow soldering process)

| Package     | Plating material devices       | Pb solder paste | Pb-free solder paste |

|-------------|--------------------------------|-----------------|----------------------|

| SDIP & PDIP | Sn (pure Tin)                  | Yes             | Yes *                |

| QFN         | Sn (pure Tin)                  | Yes             | Yes *                |

| TQFP and SO | NiPdAu (Nickel-palladium-Gold) | Yes             | Yes *                |

\* Assemblers must verify that the Pb-package maximum temperature (mentioned on the Inner box label) is compatible with their Lead-free soldering process.

## **15.2 DEVICE ORDERING INFORMATION**

### Figure 118. Ordering information scheme

| Example:                                    | ST7 | F | LIT1xB | F | 0 | Μ | 3 | TR |

|---------------------------------------------|-----|---|--------|---|---|---|---|----|

| <b>Family</b><br>ST7 Microcontroller Family |     |   |        |   |   |   |   |    |

| Memory type                                 |     |   |        |   |   |   |   |    |

| F: Flash                                    |     |   |        |   |   |   |   |    |

| P: FASTROM                                  |     |   |        |   |   |   |   |    |

| <b>Version</b><br>10B, 15B or 19B           |     |   |        |   |   |   |   |    |

| No. of pins                                 |     |   |        |   |   |   |   |    |

| F = 20                                      |     |   |        |   |   |   |   |    |

| Y = 16                                      |     |   |        |   |   |   |   |    |

| Memory size                                 |     |   |        |   |   |   |   |    |

| 0 = 2K<br>1 = 4K                            |     |   |        |   |   |   |   |    |

| Package                                     |     |   |        |   |   |   |   |    |

| B = DIP                                     |     |   |        |   |   |   |   |    |

| M = SO<br>U = VFQFPN                        |     |   |        |   |   |   |   |    |

|                                             |     |   |        |   |   |   |   |    |

| Temperature range                           |     |   |        |   |   |   |   |    |

| 6 = -40 °C to 85 °C                         |     |   |        |   |   |   |   |    |

| 3 = -40 °C to 125 °C                        |     |   |        |   |   |   |   |    |

| Shipping Option                             |     |   |        |   |   |   |   |    |

TR = Tape & Reel packing Blank = Tube (DIP or SO) or Tray (VFQFPN)

57

For a list of available options (e.g. data EEPROM, package) and orderable part numbers or for further information on any aspect of this device, please contact the ST Sales Office nearest to you.

# Table 29. ST7 Application Notes

| IDENTIFICATION | DESCRIPTION                                                                      |

|----------------|----------------------------------------------------------------------------------|

| AN1947         | ST7MC PMAC SINE WAVE MOTOR CONTROL SOFTWARE LIBRARY                              |

| GENERAL PURPO  | SE                                                                               |

| AN1476         | LOW COST POWER SUPPLY FOR HOME APPLIANCES                                        |

| AN1526         | ST7FLITE0 QUICK REFERENCE NOTE                                                   |

| AN1709         | EMC DESIGN FOR ST MICROCONTROLLERS                                               |

| AN1752         | ST72324 QUICK REFERENCE NOTE                                                     |

| PRODUCT EVALU  | ATION                                                                            |

| AN 910         | PERFORMANCE BENCHMARKING                                                         |

| AN 990         | ST7 BENEFITS VERSUS INDUSTRY STANDARD                                            |

| AN1077         | OVERVIEW OF ENHANCED CAN CONTROLLERS FOR ST7 AND ST9 MCUS                        |

| AN1086         | U435 CAN-DO SOLUTIONS FOR CAR MULTIPLEXING                                       |

| AN1103         | IMPROVED B-EMF DETECTION FOR LOW SPEED, LOW VOLTAGE WITH ST72141                 |

| AN1150         | BENCHMARK ST72 VS PC16                                                           |

| AN1151         | PERFORMANCE COMPARISON BETWEEN ST72254 & PC16F876                                |

| AN1278         | LIN (LOCAL INTERCONNECT NETWORK) SOLUTIONS                                       |

| PRODUCT MIGRA  | TION                                                                             |

| AN1131         | MIGRATING APPLICATIONS FROM ST72511/311/214/124 TO ST72521/321/324               |

| AN1322         | MIGRATING AN APPLICATION FROM ST7263 REV.B TO ST7263B                            |

| AN1365         | GUIDELINES FOR MIGRATING ST72C254 APPLICATIONS TO ST72F264                       |

| AN1604         | HOW TO USE ST7MDT1-TRAIN WITH ST72F264                                           |

| AN2200         | GUIDELINES FOR MIGRATING ST7LITE1X APPLICATIONS TO ST7FLITE1XB                   |

| PRODUCT OPTIM  | ZATION                                                                           |

| AN 982         | USING ST7 WITH CERAMIC RESONATOR                                                 |

| AN1014         | HOW TO MINIMIZE THE ST7 POWER CONSUMPTION                                        |

| AN1015         | SOFTWARE TECHNIQUES FOR IMPROVING MICROCONTROLLER EMC PERFORMANCE                |

| AN1040         | MONITORING THE VBUS SIGNAL FOR USB SELF-POWERED DEVICES                          |

| AN1070         | ST7 CHECKSUM SELF-CHECKING CAPABILITY                                            |

| AN1181         | ELECTROSTATIC DISCHARGE SENSITIVE MEASUREMENT                                    |

| AN1324         | CALIBRATING THE RC OSCILLATOR OF THE ST7FLITE0 MCU USING THE MAINS               |

| AN1502         | EMULATED DATA EEPROM WITH ST7 HDFLASH MEMORY                                     |

| AN1529         | EXTENDING THE CURRENT & VOLTAGE CAPABILITY ON THE ST7265 VDDF SUPPLY             |

| AN1530         | ACCURATE TIMEBASE FOR LOW-COST ST7 APPLICATIONS WITH INTERNAL RC OSCILLA-<br>TOR |

| AN1605         | USING AN ACTIVE RC TO WAKEUP THE ST7LITE0 FROM POWER SAVING MODE                 |

| AN1636         | UNDERSTANDING AND MINIMIZING ADC CONVERSION ERRORS                               |

| AN1828         | PIR (PASSIVE INFRARED) DETECTOR USING THE ST7FLITE05/09/SUPERLITE                |

| AN1946         | SENSORLESS BLDC MOTOR CONTROL AND BEMF SAMPLING METHODS WITH ST7MC               |

| AN1953         | PFC FOR ST7MC STARTER KIT                                                        |

| AN1971         | ST7LITE0 MICROCONTROLLED BALLAST                                                 |

| PROGRAMMING A  | ND TOOLS                                                                         |

| AN 978         | ST7 VISUAL DEVELOP SOFTWARE KEY DEBUGGING FEATURES                               |

| AN 983         | KEY FEATURES OF THE COSMIC ST7 C-COMPILER PACKAGE                                |

| AN 985         | EXECUTING CODE IN ST7 RAM                                                        |

| AN 986         | USING THE INDIRECT ADDRESSING MODE WITH ST7                                      |

| AN 987         | ST7 SERIAL TEST CONTROLLER PROGRAMMING                                           |

| AN 988         | STARTING WITH ST7 ASSEMBLY TOOL CHAIN                                            |

| AN 989         | GETTING STARTED WITH THE ST7 HIWARE C TOOLCHAIN                                  |

|                |                                                                                  |