Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | SPI                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 17                                                                     |

| Program Memory Size        | 4KB (4K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 7x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                         |

| Supplier Device Package    | 20-SO                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7flit10bf1m6 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

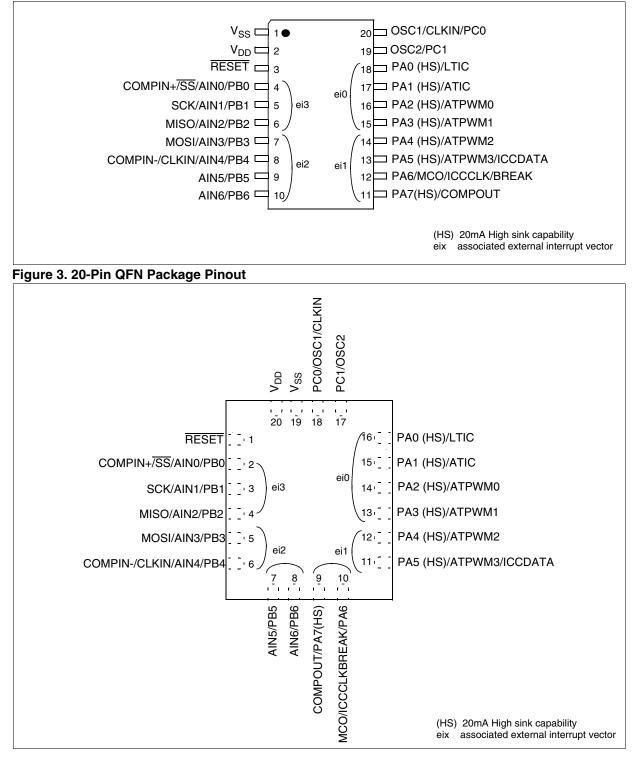

# **2 PIN DESCRIPTION**

#### Figure 2. 20-Pin SO and DIP Package Pinout

# PIN DESCRIPTION (Cont'd)

# Legend / Abbreviations for Table 1:

| Туре:            | I = input, O = output, S = supply                                      |

|------------------|------------------------------------------------------------------------|

| In/Output level: | $C_T$ = CMOS 0.3V <sub>DD</sub> /0.7V <sub>DD</sub> with input trigger |

| Output level:    | HS = 20mA high sink (on N-buffer only)                                 |

Port and control configuration:

- Input: float = floating, wpu = weak pull-up, int = interrupt, ana = analog

- Output: OD = open drain, PP = push-pull

The RESET configuration of each pin is shown in bold which is valid as long as the device is in reset state.

| Р          | in No | <b>)</b> . |                               |      | Le    | vel            |       | Po                                              | rt/C  | Cont                             | trol    |                                  |                  |                                                                                                                                                                                 |  |

|------------|-------|------------|-------------------------------|------|-------|----------------|-------|-------------------------------------------------|-------|----------------------------------|---------|----------------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 기20        | 0     | P16        | Pin Name                      | Type |       | ıt             |       | Inp                                             | Input |                                  | Outpu   |                                  | Main<br>Function | Alternate Function                                                                                                                                                              |  |

| SO20/DP120 | QFN20 | SO16/DIP1  |                               | Ту   | Input | Output         | float | ndw                                             | int   | ana                              | ao      | dд                               | (after<br>reset) |                                                                                                                                                                                 |  |

| 1          | 19    | 1          | V <sub>SS</sub> <sup>1)</sup> | S    |       |                |       |                                                 |       |                                  |         |                                  | Ground           |                                                                                                                                                                                 |  |

| 2          | 20    | 2          | V <sub>DD</sub> <sup>1)</sup> | S    |       |                |       |                                                 |       |                                  |         |                                  | Main power       | r supply                                                                                                                                                                        |  |

| 3          | 1     | 3          | RESET                         | I/O  | CT    |                |       | Х                                               |       |                                  | Х       |                                  | Top priority     | non maskable interrupt (active low)                                                                                                                                             |  |

| 4          | 2     | 4          | PB0/COMPIN+/<br>AIN0/SS       | I/O  | c     | ζ              | X ei3 |                                                 | i3    | x                                | x       | x                                | Port B0          | ADC Analog Input 0 <sup>2)</sup> or SPI Slave<br>Select (active low) or Analog Com-<br>parator Input<br><b>Caution:</b> No negative current in-<br>jection allowed on this pin. |  |

| 5          | 3     | 5          | PB1/AIN1/SCK                  | I/O  | C     | С <sub>т</sub> | x     |                                                 |       | Х                                | х       | х                                | Port B1          | ADC Analog Input 1 <sup>2)</sup> or SPI Seria<br>Clock                                                                                                                          |  |

| 6          | 4     | 6          | PB2/AIN2/MISO                 | I/O  | C     | C <sub>T</sub> | х     |                                                 |       | Х                                | Х       | х                                | Port B2          | ADC Analog Input 2 <sup>2)</sup> or SPI Mas-<br>ter In/ Slave Out Data                                                                                                          |  |

| 7          | 5     | 7          | PB3/AIN3/MOSI                 | I/O  | C     | C <sub>T</sub> | х     |                                                 |       | Х                                | Х       | х                                | Port B3          | ADC Analog Input 3 <sup>2)</sup> or SPI Mas-<br>ter Out / Slave In Data                                                                                                         |  |

| 8          | 6     | 8          | PB4/AIN4/CLKIN/<br>COMPIN-    | I/O  | C     | Ът             | X e   |                                                 | i2    | х                                | х       | x                                | Port B4          | ADC Analog Input 4 <sup>2)</sup> or External clock input or Analog Comparator External Reference Input                                                                          |  |

| 9          | 7     | -          | PB5/AIN5                      | I/O  | C     | ר <sub>ד</sub> | х     |                                                 | X X X |                                  | Port B5 | ADC Analog Input 5 <sup>2)</sup> |                  |                                                                                                                                                                                 |  |

| 10         | 8     | -          | PB6/AIN6                      | I/O  | C     | с, т           | Х     | X X X X Port B6 ADC Analog Input 6 <sup>2</sup> |       | ADC Analog Input 6 <sup>2)</sup> |         |                                  |                  |                                                                                                                                                                                 |  |

| 11         | 9     | 9          | PA7/COMPOUT                   | I/O  | Ст    | HS             | Х     | e                                               | i1    |                                  | Х       | Х                                | Port A7          | Analog Comparator Output                                                                                                                                                        |  |

# Table 1. Device Pin Description

| Address                                                     | Block               | Register Label                                                | Register Name                                                                                                                                                                                        | Reset Status                                  | Remarks                                |

|-------------------------------------------------------------|---------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------|

| 0002Fh                                                      | FLASH               | FCSR                                                          | Flash Control/Status Register                                                                                                                                                                        | 00h                                           | R/W                                    |

| 00030h                                                      | EEPROM              | EECSR                                                         | Data EEPROM Control/Status Register                                                                                                                                                                  | 00h                                           | R/W                                    |

| 0031h<br>0032h<br>0033h                                     | SPI                 | SPIDR<br>SPICR<br>SPICSR                                      | SPI Data I/O Register<br>SPI Control Register<br>SPI Control Status Register                                                                                                                         | xxh<br>0xh<br>00h                             | R/W<br>R/W<br>R/W                      |

| 0034h<br>0035h<br>0036h                                     | ADC                 | ADCCSR<br>ADCDRH<br>ADCDRL                                    | A/D Control Status Register<br>A/D Data Register High<br>A/D Amplifier Control/Data Low Register                                                                                                     | 00h<br>xxh<br>0xh                             | R/W<br>Read Only<br>R/W                |

| 0037h                                                       | ITC                 | EICR                                                          | External Interrupt Control Register                                                                                                                                                                  | 00h                                           | R/W                                    |

| 0038h                                                       | MCC                 | MCCSR                                                         | Main Clock Control/Status Register                                                                                                                                                                   | 00h                                           | R/W                                    |

| 0039h<br>003Ah                                              | Clock and<br>Reset  | RCCR<br>SICSR                                                 | RC oscillator Control Register<br>System Integrity Control/Status Register                                                                                                                           | FFh<br>0110 0xx0b                             | R/W<br>R/W                             |

| 003Bh                                                       | PLL clock<br>select | PLLTST                                                        | PLL test register                                                                                                                                                                                    | 00h                                           | R/W                                    |

| 003Ch                                                       | ITC                 | EISR                                                          | External Interrupt Selection Register                                                                                                                                                                | 0Ch                                           | R/W                                    |

| 003Dh to<br>0048h                                           |                     |                                                               | Reserved area (12 bytes)                                                                                                                                                                             |                                               | I                                      |

| 0049h<br>004Ah                                              | AWU                 | AWUPR<br>AWUCSR                                               | AWU Prescaler Register<br>AWU Control/Status Register                                                                                                                                                | FFh<br>00h                                    | R/W<br>R/W                             |

| 004Bh<br>004Ch<br>004Dh<br>004Eh<br>004Fh<br>0050h<br>0051h | DM <sup>3)</sup>    | DMCR<br>DMSR<br>DMBK1H<br>DMBK1L<br>DMBK2H<br>DMBK2L<br>DMCR2 | DM Control Register<br>DM Status Register<br>DM Breakpoint Register 1 High<br>DM Breakpoint Register 1 Low<br>DM Breakpoint Register 2 High<br>DM Breakpoint Register 2 Low<br>DM Control Register 2 | 00h<br>00h<br>00h<br>00h<br>00h<br>00h<br>00h | R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W |

| 0052h to<br>007Fh                                           |                     | 1                                                             | Reserved area (46 bytes)                                                                                                                                                                             |                                               | 1                                      |

Legend: x=undefined, R/W=read/write

# Notes:

57

**1.** The contents of the I/O port DR registers are readable only in output configuration. In input configuration, the values of the I/O pins are returned instead of the DR register contents.

2. The bits associated with unavailable pins must always keep their reset value.

3. For a description of the Debug Module registers, see ICC protocol reference manual.

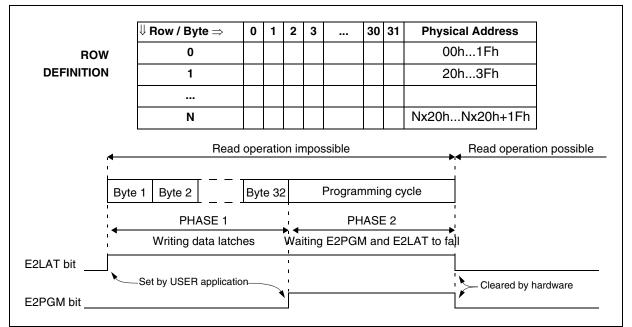

# DATA EEPROM (Cont'd)

57/

# Figure 9. Data E<sup>2</sup>PROM Write Operation

**Note:** If a programming cycle is interrupted (by a reset action), the integrity of the data in memory is not guaranteed.

# 7 SUPPLY, RESET AND CLOCK MANAGEMENT

The device includes a range of utility features for securing the application in critical situations (for example in case of a power brown-out), and reducing the number of external components.

## Main features

- Clock Management

- 1 MHz internal RC oscillator (enabled by option byte, available on ST7LITE15B and ST7LITE19B devices only)

- 1 to 16 MHz External crystal/ceramic resonator (selected by option byte)

- External Clock Input (enabled by option byte)

- PLL for multiplying the frequency by 8 or 4 (enabled by option byte)

- For clock ART counter only: PLL32 for multiplying the 8 MHz frequency by 4 (enabled by option byte). The 8 MHz input frequency is mandatory and can be obtained in the following ways:

- –1 MHz RC + PLLx8

- –16 MHz external clock (internally divided by 2)

- –2 MHz. external clock (internally divided by 2) + PLLx8

- -Crystal oscillator with 16 MHz output frequency (internally divided by 2)

- Reset Sequence Manager (RSM)

- System Integrity Management (SI)

- Main supply Low voltage detection (LVD) with reset generation (enabled by option byte)

- Auxiliary Voltage detector (AVD) with interrupt capability for monitoring the main supply (enabled by option byte)

# 7.1 INTERNAL RC OSCILLATOR ADJUSTMENT

The device contains an internal RC oscillator with an accuracy of 1% for a given device, temperature and voltage range (4.5V-5.5V). It must be calibrated to obtain the frequency required in the application. This is done by software writing a 10-bit calibration value in the RCCR (RC Control Register) and in the bits 6:5 in the SICSR (SI Control Status Register).

Whenever the microcontroller is reset, the RCCR returns to its default value (FFh), i.e. each time the device is reset, the calibration value must be loaded in the RCCR. Predefined calibration values are stored in EEPROM for 3 and 5V V<sub>DD</sub> supply voltages at 25°C, as shown in the following table.

| RCCR   | Conditions                                    | ST7LITE1xB<br>Address         |  |  |

|--------|-----------------------------------------------|-------------------------------|--|--|

| RCCRH0 | V <sub>DD</sub> =5V                           | DEE0h <sup>1)</sup> (CR[9:2]) |  |  |

| RCCRL0 | T <sub>A</sub> =25°C<br>f <sub>RC</sub> =1MHz | DEE1h <sup>1)</sup> (CR[1:0]) |  |  |

| RCCRH1 | V <sub>DD</sub> =3.3V                         | DEE2h <sup>1)</sup> (CR[9:2]) |  |  |

| RCCRL1 | T <sub>A</sub> =25°C<br>f <sub>RC</sub> =1MHz | DEE3h <sup>1)</sup> (CR[1:0]) |  |  |

1. DEE0h, DEE1h, DEE2h and DEE3h addresses are located in a reserved area of non-volatile memory. They are read-only bytes for the application code. This area cannot be erased or programmed by any ICC operation.

For compatibility reasons with the SICSR register, CR[1:0] bits are stored in the 5th and 6th position of DEE1 and DEE3 addresses.

## Notes:

- In 38-pulse ICC mode, the internal RC oscillator is forced as a clock source, regardless of the selection in the option byte. For ST7LITE10B devices which do not support the internal RC oscillator, the "option byte disabled" mode must be used (35-pulse ICC mode entry, clock provided by the tool).

- See "ELECTRICAL CHARACTERISTICS" on page 110. for more information on the frequency and accuracy of the RC oscillator.

- To improve clock stability and frequency accuracy, it is recommended to place a decoupling capacitor, typically 100nF, between the  $V_{DD}$  and  $V_{SS}$  pins as close as possible to the ST7 device.

- These bytes are systematically programmed by ST, including on FASTROM devices.

**Caution:** If the voltage or temperature conditions change in the application, the frequency may need to be recalibrated.

Refer to application note AN1324 for information on how to calibrate the RC frequency using an external reference signal.

# 7.2 PHASE LOCKED LOOP

The PLL can be used to multiply a 1MHz frequency from the RC oscillator or the external clock by 4 or 8 to obtain  $f_{OSC}$  of 4 or 8 MHz. The PLL is enabled and the multiplication factor of 4 or 8 is selected by 2 option bits.

– The x4 PLL is intended for operation with  $V_{DD}$  in the 2.7V to 3.3V range

# **8 INTERRUPTS**

The ST7 core may be interrupted by one of two different methods: Maskable hardware interrupts as listed in the "interrupt mapping" table and a nonmaskable software interrupt (TRAP). The Interrupt processing flowchart is shown in Figure 1.

The maskable interrupts must be enabled by clearing the I bit in order to be serviced. However, disabled interrupts may be latched and processed when they are enabled (see external interrupts subsection).

Note: After reset, all interrupts are disabled.

When an interrupt has to be serviced:

- Normal processing is suspended at the end of the current instruction execution.

- The PC, X, A and CC registers are saved onto the stack.

- The I bit of the CC register is set to prevent additional interrupts.

- The PC is then loaded with the interrupt vector of the interrupt to service and the first instruction of the interrupt service routine is fetched (refer to the Interrupt Mapping table for vector addresses).

The interrupt service routine should finish with the IRET instruction which causes the contents of the saved registers to be recovered from the stack.

**Note:** As a consequence of the IRET instruction, the I bit is cleared and the main program resumes.

#### **Priority Management**

By default, a servicing interrupt cannot be interrupted because the I bit is set by hardware entering in interrupt routine.

In the case when several interrupts are simultaneously pending, an hardware priority defines which one will be serviced first (see the Interrupt Mapping table).

#### Interrupts and Low Power Mode

All interrupts allow the processor to leave the WAIT low power mode. Only external and specifically mentioned interrupts allow the processor to leave the HALT low power mode (refer to the "Exit from HALT" column in the Interrupt Mapping table).

#### **8.1 NON MASKABLE SOFTWARE INTERRUPT**

This interrupt is entered when the TRAP instruction is executed regardless of the state of the I bit. It is serviced according to the flowchart in Figure 1.

## **8.2 EXTERNAL INTERRUPTS**

External interrupt vectors can be loaded into the PC register if the corresponding external interrupt occurred and if the I bit is cleared. These interrupts allow the processor to leave the HALT low power mode.

The external interrupt polarity is selected through the miscellaneous register or interrupt register (if available).

An external interrupt triggered on edge will be latched and the interrupt request automatically cleared upon entering the interrupt service routine.

**Caution:** The type of sensitivity defined in the Miscellaneous or Interrupt register (if available) applies to the ei source. In case of a NANDed source (as described in the I/O ports section), a low level on an I/O pin, configured as input with interrupt, masks the interrupt request even in case of rising-edge sensitivity.

# **8.3 PERIPHERAL INTERRUPTS**

Different peripheral interrupt flags in the status register are able to cause an interrupt when they are active if both:

- The I bit of the CC register is cleared.

- The corresponding enable bit is set in the control register.

If any of these two conditions is false, the interrupt is latched and thus remains pending.

Clearing an interrupt request is done by:

- Writing "0" to the corresponding bit in the status register or

- Access to the status register while the flag is set followed by a read or write of an associated register.

**Note**: The clearing sequence resets the internal latch. A pending interrupt (that is, waiting for being enabled) will therefore be lost if the clear sequence is executed.

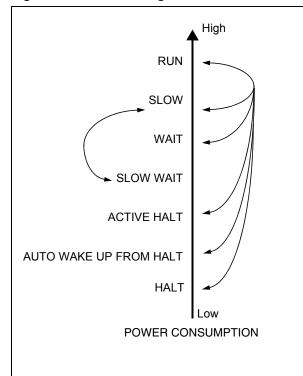

# **9 POWER SAVING MODES**

# 9.1 INTRODUCTION

To give a large measure of flexibility to the application in terms of power consumption, five main power saving modes are implemented in the ST7 (see Figure 22):

- Slow

- Wait (and Slow-Wait)

- Active Halt

- Auto Wake up From Halt (AWUFH)

- Halt

After a RESET the normal operating mode is selected by default (RUN mode). This mode drives the device (CPU and embedded peripherals) by means of a master clock which is based on the main oscillator frequency divided or multiplied by 2 ( $f_{OSC2}$ ).

From RUN mode, the different power saving modes may be selected by setting the relevant register bits or by calling the specific ST7 software instruction whose action depends on the oscillator status.

#### Figure 22. Power Saving Mode Transitions

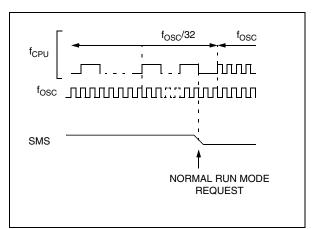

## 9.2 SLOW MODE

This mode has two targets:

- To reduce power consumption by decreasing the internal clock in the device,

- To adapt the internal clock frequency (f<sub>CPU</sub>) to the available supply voltage.

SLOW mode is controlled by the SMS bit in the MCCSR register which enables or disables Slow mode.

In this mode, the oscillator frequency is divided by 32. The CPU and peripherals are clocked at this

lower frequency.

**Note**: SLOW-WAIT mode is activated when entering WAIT mode while the device is already in SLOW mode.

0

# POWER SAVING MODES (Cont'd)

### 9.6.0.1 Register Description

### AWUFH CONTROL/STATUS REGISTER (AWUCSR)

Read/Write Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |          |          | 0         |

|---|---|---|---|---|----------|----------|-----------|

| 0 | 0 | 0 | 0 | 0 | AWU<br>F | AWU<br>M | AWU<br>EN |

Bits 7:3 = Reserved.

#### Bit 1= AWUF Auto Wake Up Flag

This bit is set by hardware when the AWU module generates an interrupt and cleared by software on reading AWUCSR. Writing to this bit does not change its value.

0: No AWU interrupt occurred

1: AWU interrupt occurred

#### Bit 1= **AWUM** Auto Wake Up Measurement

This bit enables the AWU RC oscillator and connects its output to the input capture of the 12-bit Auto-Reload timer. This allows the timer to be used to measure the AWU RC oscillator dispersion and then compensate this dispersion by providing the right value in the AWUPRE register.

0: Measurement disabled

1: Measurement enabled

5/

Bit 0 = **AWUEN** Auto Wake Up From Halt Enabled This bit enables the Auto Wake Up From Halt feature: once HALT mode is entered, the AWUFH wakes up the microcontroller after a time delay dependent on the AWU prescaler value. It is set and cleared by software.

- 0: AWUFH (Auto Wake Up From Halt) mode disabled

- 1: AWUFH (Auto Wake Up From Halt) mode enabled

#### AWUFH PRESCALER REGISTER (AWUPR) Read/Write

| 7 |  |

|---|--|

| 1 |  |

| AWU |

|-----|-----|-----|-----|-----|-----|-----|-----|

| PR7 | PR6 | PR5 | PR4 | PR3 | PR2 | PR1 | PR0 |

Bits 7:0= **AWUPR[7:0]** Auto Wake Up Prescaler These 8 bits define the AWUPR Dividing factor (as explained below:

| AWUPR[7:0] | Dividing factor |

|------------|-----------------|

| 00h        | Forbidden       |

| 01h        | 1               |

|            |                 |

| FEh        | 254             |

| FFh        | 255             |

In AWU mode, the period that the MCU stays in Halt Mode ( $t_{AWU}$  in Figure 30 on page 45) is defined by

$$^{t}AWU = 64 \times AWUPR \times \frac{1}{f_{AWURC}} + ^{t}RCSTRT$$

This prescaler register can be programmed to modify the time that the MCU stays in Halt mode before waking up automatically.

**Note:** If 00h is written to AWUPR, depending on the product, an interrupt is generated immediately after a HALT instruction, or the AWUPR remains unchanged.

| Address<br>(Hex.) | Register<br>Label     | 7           | 6           | 5           | 4           | 3           | 2           | 1           | 0           |

|-------------------|-----------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| 0049h             | AWUPR<br>Reset Value  | AWUPR7<br>1 | AWUPR6<br>1 | AWUPR5<br>1 | AWUPR4<br>1 | AWUPR3<br>1 | AWUPR2<br>1 | AWUPR1<br>1 | AWUPR0<br>1 |

| 004Ah             | AWUCSR<br>Reset Value | 0           | 0           | 0           | 0           | 0           | AWUF        | AWUM        | AWUEN       |

# 10 I/O PORTS

# **10.1 INTRODUCTION**

The I/O ports allow data transfer. An I/O port can contain up to 8 pins. Each pin can be programmed independently either as a digital input or digital output. In addition, specific pins may have several other functions. These functions can include external interrupt, alternate signal input/output for onchip peripherals or analog input.

# **10.2 FUNCTIONAL DESCRIPTION**

A Data Register (DR) and a Data Direction Register (DDR) are always associated with each port. The Option Register (OR), which allows input/output options, may or may not be implemented. The following description takes into account the OR register. Refer to the Port Configuration table for device specific information.

An I/O pin is programmed using the corresponding bits in the DDR, DR and OR registers: bit x corresponding to pin x of the port.

Figure 32 shows the generic I/O block diagram.

## 10.2.1 Input Modes

Clearing the DDRx bit selects input mode. In this mode, reading its DR bit returns the digital value from that I/O pin.

If an OR bit is available, different input modes can be configured by software: floating or pull-up. Refer to I/O Port Implementation section for configuration.

#### Notes:

1. Writing to the DR modifies the latch value but does not change the state of the input pin.

2. Do not use read/modify/write instructions (BSET/BRES) to modify the DR register.

# 10.2.1.1 External Interrupt Function

Depending on the device, setting the ORx bit while in input mode can configure an I/O as an input with interrupt. In this configuration, a signal edge or level input on the I/O generates an interrupt request via the corresponding interrupt vector (eix).

Falling or rising edge sensitivity is programmed independently for each interrupt vector. The External Interrupt Control Register (EICR) or the Miscellaneous Register controls this sensitivity, depending on the device.

Each external interrupt vector is linked to a dedicated group of I/O port pins (see pinout description and interrupt section). If several I/O interrupt pins on the same interrupt vector are selected simultaneously, they are logically combined. For this reason if one of the interrupt pins is tied low, it may mask the others.

External interrupts are hardware interrupts. Fetching the corresponding interrupt vector automatically clears the request latch. Changing the sensitivity of a particular external interrupt clears this pending interrupt. This can be used to clear unwanted pending interrupts.

#### Spurious interrupts

When enabling/disabling an external interrupt by setting/resetting the related OR register bit, a spurious interrupt is generated if the pin level is low and its edge sensitivity includes falling/rising edge. This is due to the edge detector input which is switched to '1' when the external interrupt is disabled by the OR register.

To avoid this unwanted interrupt, a "safe" edge sensitivity (rising edge for enabling and falling edge for disabling) has to be selected before changing the OR register bit and configuring the appropriate sensitivity again.

**Caution:** In case a pin level change occurs during these operations (asynchronous signal input), as interrupts are generated according to the current sensitivity, it is advised to disable all interrupts before and to reenable them after the complete previous sequence in order to avoid an external interrupt occurring on the unwanted edge.

This corresponds to the following steps:

- 1. To enable an external interrupt:

- set the interrupt mask with the SIM instruction (in cases where a pin level change could occur)

- select rising edge

- enable the external interrupt through the OR register

- select the desired sensitivity if different from rising edge

- reset the interrupt mask with the RIM instruction (in cases where a pin level change could occur)

- 2. To disable an external interrupt:

- set the interrupt mask with the SIM instruction SIM (in cases where a pin level change could occur)

- select falling edge

- disable the external interrupt through the OR register

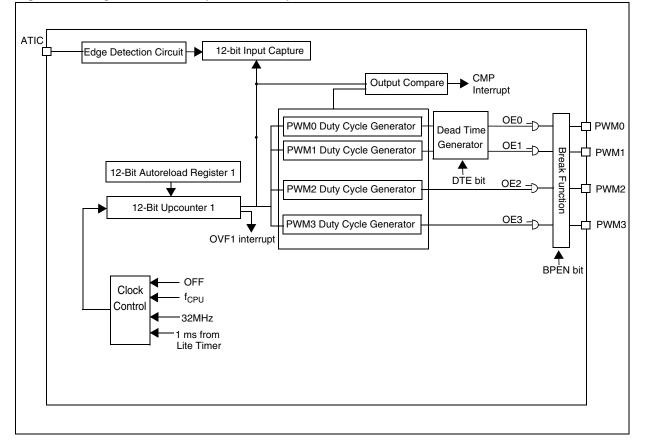

# 11.2 DUAL 12-BIT AUTORELOAD TIMER 4 (AT4)

# 11.2.1 Introduction

The 12-bit Autoreload Timer can be used for general-purpose timing functions. It is based on one or two free-running 12-bit upcounters with an input capture register and four PWM output channels. There are 7 external pins:

- Four PWM outputs

- ATIC/LTIC pins for the Input Capture function

- BREAK pin for forcing a break condition on the PWM outputs

#### 11.2.2 Main Features

- Single Timer or Dual Timer mode with two 12-bit upcounters (CNTR1/CNTR2) and two 12-bit autoreload registers (ATR1/ATR2)

- Maskable overflow interrupts

- PWM mode

47/

# Figure 35. Single Timer Mode (ENCNTR2=0)

- Generation of four independent PWMx signals

- Dead time generation for Half bridge driving mode with programmable dead time

- Frequency 2 kHz 4 MHz (@ 8 MHz f<sub>CPU</sub>)

- Programmable duty-cycles

- Polarity control

- Programmable output modes

- Output Compare Mode

- Input Capture Mode

- 12-bit input capture register (ATICR)

- Triggered by rising and falling edges

- Maskable IC interrupt

- Long range input capture

- Internal/External Break control

- Flexible Clock control

- One Pulse mode on PWM2/3

- Force Update

# DUAL 12-BIT AUTORELOAD TIMER 4 (Cont'd)

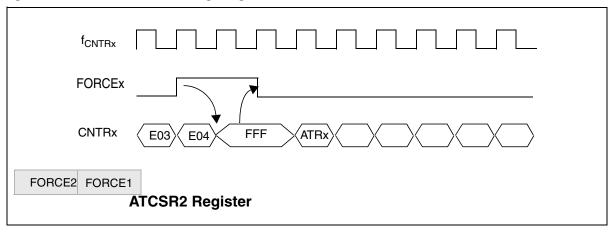

## 11.2.3.7 Force Update

In order not to wait for the counter<sub>x</sub> overflow to load the value into active DCRx registers, a programmable counter<sub>x</sub> overflow is provided. For both counters, a separate bit is provided which when set, make the counters start with the overflow value, i.e. FFFh. After overflow, the counters start counting from their respective auto reload register values.

These bits are FORCE1 and FORCE2 in the ATCSR2 register. FORCE1 is used to force an overflow on Counter 1 and, FORCE2 is used for Counter 2. These bits are set by software and re-

Figure 50. Force Overflow Timing Diagram

set by hardware after the respective counter overflow event has occurred.

This feature can be used at any time. All related features such as PWM generation, Output Compare, Input Capture, One-pulse (refer to Figure 15. Dynamic DCR2/3 update in One Pulse Mode) can be used this way.

# ST7LITE1xB

| Address<br>(Hex.) | Register<br>Label      | 7      | 6      | 5    | 4      | 3          | 2          | 1          | 0          |

|-------------------|------------------------|--------|--------|------|--------|------------|------------|------------|------------|

| 21                | ATCSR2                 | FORCE2 | FORCE1 | ICS  | OVFIE2 | OVF2       | ENCNTR2    | TRAN2      | TRAN1      |

|                   | Reset Value            | 0      | 0      | 0    | 0      | 0          | 0          | 1          | 1          |

| 22                | BREAKCR                | BRSEL  | BREDGE | BA   | BPEN   | PWM3       | PWM2       | PWM1       | PWM0       |

|                   | Reset Value            | 0      | 0      | 0    | 0      | 0          | 0          | 0          | 0          |

| 23                | ATR2H<br>Reset Value   | 0      | 0      | 0    | 0      | ATR11<br>0 | ATR10<br>0 | ATR9<br>0  | ATR8<br>0  |

| 24                | ATR2L                  | ATR7   | ATR6   | ATR5 | ATR4   | ATR3       | ATR2       | ATR1       | ATR0       |

|                   | Reset Value            | 0      | 0      | 0    | 0      | 0          | 0          | 0          | 0          |

| 25                | <b>DTGR</b>            | DTE    | DT6    | DT5  | DT4    | DT3        | DT2        | DT1        | DT0        |

|                   | Reset Value            | 0      | 0      | 0    | 0      | 0          | 0          | 0          | 0          |

| 26                | BREAKEN<br>Reset Value | 0      | 0      | 0    | 0      | 0          | 0          | BREN2<br>1 | BREN1<br>1 |

# **ON-CHIP PERIPHERALS** (cont'd)

# **11.4 SERIAL PERIPHERAL INTERFACE (SPI)**

#### 11.4.1 Introduction

The Serial Peripheral Interface (SPI) allows fullduplex, synchronous, serial communication with external devices. An SPI system may consist of a master and one or more slaves or a system in which devices may be either masters or slaves.

#### 11.4.2 Main Features

- Full duplex synchronous transfers (on three lines)

- Simplex synchronous transfers (on two lines)

- Master or slave operation

- 6 master mode frequencies (f<sub>CPU</sub>/4 max.)

- I f<sub>CPU</sub>/2 max. slave mode frequency (see note)

- SS Management by software or hardware

- Programmable clock polarity and phase

- End of transfer interrupt flag

- Write collision, Master Mode Fault and Overrun flags

**Note:** In slave mode, continuous transmission is not possible at maximum frequency due to the software overhead for clearing status flags and to initiate the next transmission sequence.

#### **11.4.3 General Description**

Figure 1 on page 3 shows the serial peripheral interface (SPI) block diagram. There are three registers:

- SPI Control Register (SPICR)

- SPI Control/Status Register (SPICSR)

- SPI Data Register (SPIDR)

The SPI is connected to external devices through four pins:

- MISO: Master In / Slave Out data

- MOSI: Master Out / Slave In data

- SCK: Serial Clock out by SPI masters and input by SPI slaves

- SS: Slave select:

This input signal acts as a 'chip select' to let the SPI master communicate with slaves individually and to avoid contention on the data lines. Slave SS inputs can be driven by standard I/O ports on the master Device.

# INSTRUCTION GROUPS (cont'd)

| Mnemo | Description            | Function/Example    | Dst     | Src     | н | I | Ν | z | С |

|-------|------------------------|---------------------|---------|---------|---|---|---|---|---|

| JRULE | Jump if $(C + Z = 1)$  | Unsigned <=         |         |         |   |   |   |   |   |

| LD    | Load                   | dst <= src          | reg, M  | M, reg  |   |   | Ν | Z |   |

| MUL   | Multiply               | X,A = X * A         | A, X, Y | X, Y, A | 0 |   |   |   | 0 |

| NEG   | Negate (2's compl)     | neg \$10            | reg, M  |         |   |   | Ν | Z | С |

| NOP   | No Operation           |                     |         |         |   |   |   |   |   |

| OR    | OR operation           | A = A + M           | А       | М       |   |   | Ν | Z |   |

| POP   | Pop from the Stack     | pop reg             | reg     | М       |   |   |   |   |   |

|       |                        | pop CC              | сс      | М       | Н | I | Ν | Z | С |

| PUSH  | Push onto the Stack    | push Y              | М       | reg, CC |   |   |   |   |   |

| RCF   | Reset carry flag       | C = 0               |         |         |   |   |   |   | 0 |

| RET   | Subroutine Return      |                     |         |         |   |   |   |   |   |

| RIM   | Enable Interrupts      | I = 0               |         |         |   | 0 |   |   |   |

| RLC   | Rotate left true C     | C <= Dst <= C       | reg, M  |         |   |   | Ν | Z | С |

| RRC   | Rotate right true C    | C => Dst => C       | reg, M  |         |   |   | Ν | Z | С |

| RSP   | Reset Stack Pointer    | S = Max allowed     |         |         |   |   |   |   |   |

| SBC   | Subtract with Carry    | A = A - M - C       | А       | М       |   |   | Ν | Z | С |

| SCF   | Set carry flag         | C = 1               |         |         |   |   |   |   | 1 |

| SIM   | Disable Interrupts     | l = 1               |         |         |   | 1 |   |   |   |

| SLA   | Shift left Arithmetic  | C <= Dst <= 0       | reg, M  |         |   |   | Ν | Z | С |

| SLL   | Shift left Logic       | C <= Dst <= 0       | reg, M  |         |   |   | Ν | Z | С |

| SRL   | Shift right Logic      | 0 => Dst => C       | reg, M  |         |   |   | 0 | Z | С |

| SRA   | Shift right Arithmetic | Dst7 => Dst => C    | reg, M  |         |   |   | Ν | Z | С |

| SUB   | Subtraction            | A = A - M           | А       | М       |   |   | Ν | Z | С |

| SWAP  | SWAP nibbles           | Dst[74] <=> Dst[30] | reg, M  |         |   |   | Ν | Z |   |

| TNZ   | Test for Neg & Zero    | tnz lbl1            |         |         |   |   | Ν | Z |   |

| TRAP  | S/W trap               | S/W interrupt       |         |         |   | 1 |   |   |   |

| WFI   | Wait for Interrupt     |                     |         |         |   | 0 |   |   |   |

| XOR   | Exclusive OR           | A = A XOR M         | A       | М       |   |   | Ν | Z |   |

|       |                        |                     |         |         |   | - |   |   |   |

# **13.2 ABSOLUTE MAXIMUM RATINGS**

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these condi-

## 13.2.1 Voltage Characteristics

tions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                                                   | Symbol Ratings                                  |                                                    | Unit    |

|--------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------|---------|

| V <sub>DD</sub> - V <sub>SS</sub>                                        | Supply voltage                                  | 7.0                                                | V       |

| V <sub>IN</sub>                                                          | Input voltage on any pin <sup>1) &amp; 2)</sup> | $V_{\rm SS}\mbox{-}0.3$ to $V_{\rm DD}\mbox{+}0.3$ | v       |

| V <sub>ESD(HBM)</sub> Electrostatic discharge voltage (Human Body Model) |                                                 | soo soction 1373 on n                              | 200 128 |

| V <sub>ESD(MM)</sub>                                                     | Electrostatic discharge voltage (Machine Model) | see section 13.7.3 on page 128                     |         |

#### **13.2.2 Current Characteristics**

| Symbol                        | Ratings                                                                                 | Maximum value | Unit |  |

|-------------------------------|-----------------------------------------------------------------------------------------|---------------|------|--|

| I <sub>VDD</sub>              | Total current into V <sub>DD</sub> power lines (source) 3)                              | 75            |      |  |

| I <sub>VSS</sub>              | I <sub>VSS</sub> Total current out of V <sub>SS</sub> ground lines (sink) <sup>3)</sup> |               |      |  |

|                               | Output current sunk by any standard I/O and control pin                                 | 20            |      |  |

| I <sub>IO</sub>               | Output current sunk by any high sink I/O pin                                            | 40            |      |  |

|                               | Output current source by any I/Os and control pin                                       | - 25          |      |  |

|                               | Injected current on ISPSEL pin                                                          | ± 5           | mA   |  |

|                               | Injected current on RESET pin                                                           | ± 5           |      |  |

| I <sub>INJ(PIN)</sub> 2) & 4) | Injected current on OSC1 and OSC2 pins                                                  | ± 5           |      |  |

|                               | Injected current on PB0 pin 5)                                                          | +5            |      |  |

|                               | Injected current on any other pin <sup>6)</sup>                                         | ± 5           |      |  |

| $\Sigma I_{INJ(PIN)}^{2)}$    | Total injected current (sum of all I/O and control pins) <sup>6)</sup>                  | ± 20          | 1    |  |

#### 13.2.3 Thermal Characteristics

| Symbol           | Ratings                                                       | Value               | Unit |

|------------------|---------------------------------------------------------------|---------------------|------|

| T <sub>STG</sub> | Storage temperature range                                     | -65 to +150         | °C   |

| TJ               | Maximum junction temperature (see Table 24, "THERM, page 147) | AL CHARACTERISTICS, | " on |

#### Notes:

1. Directly connecting the RESET and I/O pins to V<sub>DD</sub> or V<sub>SS</sub> could damage the device if an unintentional internal reset is generated or an unexpected change of the I/O configuration occurs (for example, due to a corrupted program counter). To guarantee safe operation, this connection has to be done through a pull-up or pull-down resistor (typical:  $4.7k\Omega$  for RESET,  $10k\Omega$  for I/Os). Unused I/O pins must be tied in the same way to V<sub>DD</sub> or V<sub>SS</sub> according to their reset configuration. 2. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub><V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected

3. All power  $(V_{DD})$  and ground  $(V_{SS})$  lines must always be connected to the external supply.

4. Negative injection disturbs the analog performance of the device. In particular, it induces leakage currents throughout the device including the analog inputs. To avoid undesirable effects on the analog functions, care must be taken:

- Analog input pins must have a negative injection less than 0.8 mA (assuming that the impedance of the analog voltage is lower than the specified limits)

- Pure digital pins must have a negative injection less than 1.6mA. In addition, it is recommended to inject the current as far as possible from the analog input pins.

5. No negative current injection allowed on PB0 pin.

6. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterisation with  $\Sigma I_{INJ(PIN)}$  maximum current injection on four I/O port pins of the device.

57

# 13.3.4 Auxiliary Voltage Detector (AVD) Thresholds $T_A$ = -40 to 125°C, unless otherwise specified

| Symbol                | Parameter                                                  | Conditions                                        | Тур                  | Unit |

|-----------------------|------------------------------------------------------------|---------------------------------------------------|----------------------|------|

| V <sub>IT+(AVD)</sub> | 1=>0 AVDF flag toggle threshold<br>(V <sub>DD</sub> rise)  | High Threshold<br>Med. Threshold<br>Low Threshold | 4.50<br>4.00<br>3.35 | V    |

| V <sub>IT-(AVD)</sub> | 0=>1 AVDF flag toggle threshold<br>(V <sub>DD</sub> fall)  | High Threshold<br>Med. Threshold<br>Low Threshold | 4.40<br>3.85<br>3.20 | v    |

| V <sub>hys</sub>      | AVD voltage threshold hysteresis                           | V <sub>IT+(AVD)</sub> -V <sub>IT-(AVD)</sub>      | 170                  | mV   |

| ΔV <sub>IT-</sub>     | Voltage drop between AVD flag set and LVD reset activation | V <sub>DD</sub> fall                              | 0.15                 | V    |

# 13.3.5 Internal RC Oscillator and PLL

The ST7 internal clock can be supplied by an internal RC oscillator and PLL (selectable by option byte).

| Symbol                 | Parameter                                | Conditions                                                            | Min | Тур | Max | Unit                                                   |

|------------------------|------------------------------------------|-----------------------------------------------------------------------|-----|-----|-----|--------------------------------------------------------|

| V <sub>DD(RC)</sub>    | Internal RC Oscillator operating voltage | Refer to operating range                                              | 2.7 |     | 5.5 |                                                        |

| V <sub>DD(x4PLL)</sub> | x4 PLL operating voltage                 | of V <sub>DD</sub> with T <sub>A,</sub> section<br>13.3.1 on page 112 | 2.7 |     | 3.7 | V                                                      |

| V <sub>DD(x8PLL)</sub> | x8 PLL operating voltage                 |                                                                       | 3.3 |     | 5.5 |                                                        |

| t <sub>STARTUP</sub>   | PLL Startup time                         |                                                                       |     | 60  |     | PLL<br>input<br>clock<br>(f <sub>PLL</sub> )<br>cycles |

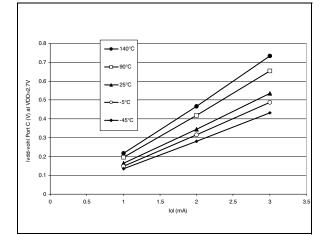

# I/O PORT PIN CHARACTERISTICS (Cont'd)

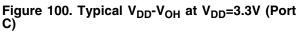

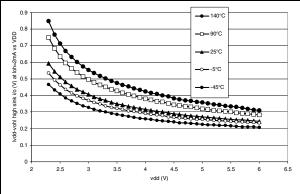

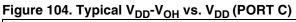

# Figure 99. Typical V<sub>DD</sub>-V<sub>OH</sub> at V<sub>DD</sub>=2.7V (Port C)

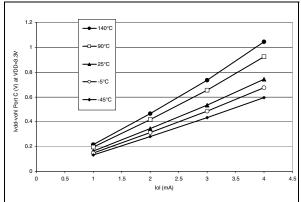

Figure 101. Typical V<sub>DD</sub>-V<sub>OH</sub> at V<sub>DD</sub>=5V (Port C)

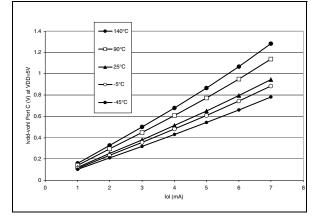

Figure 102. Typical V<sub>DD</sub>-V<sub>OH</sub> vs. V<sub>DD</sub> (Standard)

Figure 103. Typical  $V_{DD}\text{-}V_{OH}$  vs.  $V_{DD}$  (High Sink)

<u>ل</u>حک

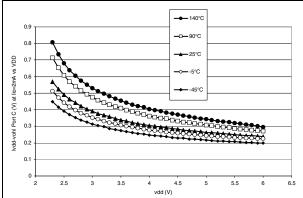

# COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)

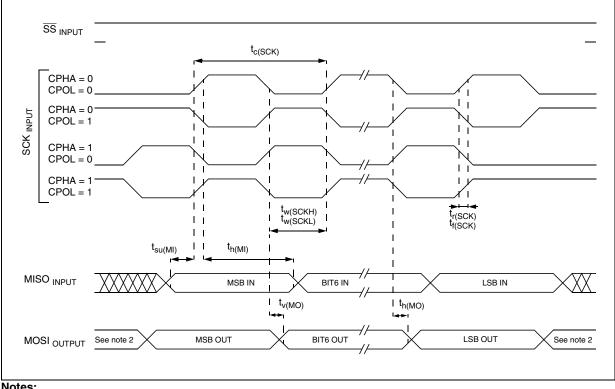

## Figure 108. SPI Slave Timing Diagram with CPHA=1<sup>1)</sup>

# Figure 109. SPI Master Timing Diagram <sup>1)</sup>

#### Notes:

1. Measurement points are done at CMOS levels:  $0.3xV_{DD}$  and  $0.7xV_{DD}$ .

2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends of the I/O port configuration.

# PACKAGE CHARACTERISTICS (Cont'd)

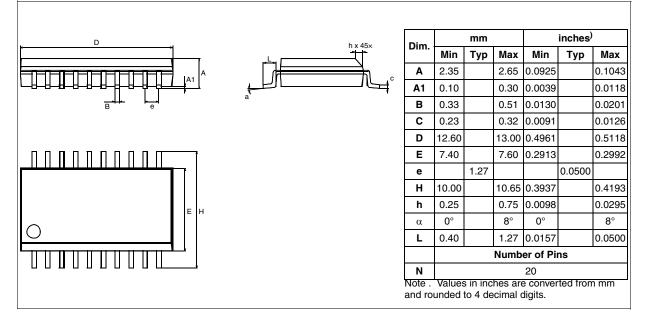

#### Figure 116. 20-Pin Plastic Small Outline Package, 300-mil Width

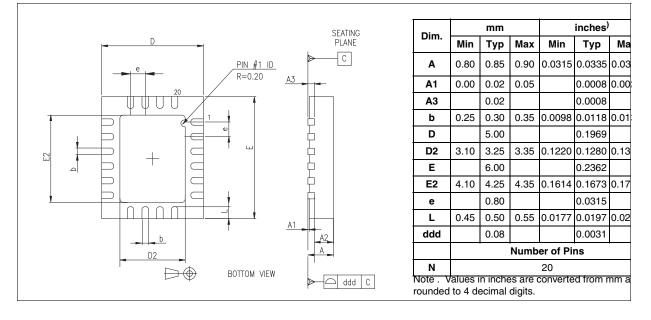

# Figure 117. 20-Lead Very thin Fine pitch Quad Flat No-Lead Package

| ST7LITE1xB FASTROM microcontroller option list                                                                                        |                                                                                                                      |                                              |                                                                                      |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------|--|--|

| Customer<br>Address<br>Contact<br>Phone No<br>Reference/FASTROM Code*:<br>*FASTROM code name is assig<br>FASTROM code must be sent in | ned by STMicroelect                                                                                                  | ronics.                                      | be processed.                                                                        |  |  |

| Device Type/Memory Size/Pack                                                                                                          |                                                                                                                      |                                              |                                                                                      |  |  |

| FASTROM DEVICE:                                                                                                                       | IROM DEVICE:                                                                                                         |                                              | 4KI                                                                                  |  |  |

| VFQFPN20:   [<br>SO20:   [<br>PDIP20:   [<br>SO16:   [<br>PDIP16:   [                                                                 | ] ST7PLIT19BF0Ux<br>] ST7PLIT19BF0Mx<br>] ST7PLIT19BF0Bx<br>] ST7PLIT19BF0Bx<br>] ST7PLIT19BY0Mx<br>] ST7PLIT19BY0Bx | []ST<br>  []ST<br>  []ST<br>  []ST<br>  []ST | 7PLIT19BF1Ux  <br>7PLIT19BF1Mx  <br>7PLIT19BF1Bx  <br>7PLIT19BY1Mx  <br>7PLIT19BY1Bx |  |  |

| Warning: Addresses DEE0h, I<br>and RCCR1 (see section 7.1 or                                                                          | DEE1h, DEE2h and page 23).                                                                                           | DEE3h are rese                               | rved areas for ST to program RCCR0                                                   |  |  |

| Conditioning (check only one or<br>VFQFPN []<br>SO []                                                                                 | tion, do not specify f                                                                                               | or DIP package)                              |                                                                                      |  |  |

| Special marking: [] No<br>Authorized characters are lette<br>Maximum character count: 8 cl                                            | rs, digits, '.', '-', '/' ar<br>nar. max                                                                             | [] Yes "<br>nd spaces only.                  | "                                                                                    |  |  |

| Temperature range:                                                                                                                    | []-40°C to                                                                                                           | +85°C                                        | [ ] -40°C to +125°C                                                                  |  |  |

| Watchdog selection (WDG_SW                                                                                                            | /): [] Software                                                                                                      | e activation                                 | [] Hardware activation                                                               |  |  |

| Watchdog reset on Halt (WDG                                                                                                           | _HALT): [] Reset                                                                                                     |                                              | [] No Reset                                                                          |  |  |

| LVD reset (LVD):                                                                                                                      | [] Disablec                                                                                                          | ł                                            | [] Enabled<br>[] Highest threshold<br>[] Medium threshold<br>[] Lowest threshold     |  |  |

| Sector 0 size (SEC):                                                                                                                  | []0.5K                                                                                                               | [] 1K                                        | []2K []4K                                                                            |  |  |

| Readout protection (FMP_R):                                                                                                           | [] Disabled                                                                                                          | [] Enabled                                   |                                                                                      |  |  |

| Flash write protection (FMP_W                                                                                                         | ): [] Disabled                                                                                                       | [] Enabled                                   |                                                                                      |  |  |

| RC oscillator (OSC) :                                                                                                                 | [] Disabled                                                                                                          | [] Enabled                                   |                                                                                      |  |  |

| Clock source selection (CKSEL<br>(if OSC disabled)                                                                                    |                                                                                                                      | tal / ceramic reso<br>k on PB4<br>k on PC0   | onator:                                                                              |  |  |

| PLL (PLLOFF):                                                                                                                         | [] Disabled                                                                                                          | [] Enabled                                   |                                                                                      |  |  |

| PLL factor (PLLx4x8):                                                                                                                 | [] PLLx4                                                                                                             | [] PLLx8                                     |                                                                                      |  |  |

| PLL32 (PLL32OFF):                                                                                                                     | [] Disabled                                                                                                          | [] Enabled                                   |                                                                                      |  |  |

| Supply operating range in the ap<br>Notes<br>Date :<br>Signature :                                                                    | plication :                                                                                                          |                                              | on page 150 for authorized option byte                                               |  |  |

| combinations.                                                                                                                         |                                                                                                                      |                                              |                                                                                      |  |  |