Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                    |

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | SPI                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 17                                                                     |

| Program Memory Size        | 2KB (2K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 7x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                         |

| Supplier Device Package    | 20-50                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7flit10bm6tr |

| Address                                            | Block                    | Register Label                              | Register Name                                                                                                                                                                      | Reset Status                                  | Remarks                                |  |  |  |

|----------------------------------------------------|--------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------|--|--|--|

| 0002Fh                                             | FLASH                    | FCSR                                        | Flash Control/Status Register                                                                                                                                                      | 00h                                           | R/W                                    |  |  |  |

| 00030h                                             | EEPROM                   | EECSR                                       | Data EEPROM Control/Status Register                                                                                                                                                | 00h                                           | R/W                                    |  |  |  |

| 0031h<br>0032h<br>0033h                            | SPI                      | SPIDR<br>SPICR<br>SPICSR                    | SPI Data I/O Register<br>SPI Control Register<br>SPI Control Status Register                                                                                                       | xxh<br>0xh<br>00h                             | R/W<br>R/W<br>R/W                      |  |  |  |

| 0034h<br>0035h<br>0036h                            | ADC                      | ADCCSR<br>ADCDRH<br>ADCDRL                  | A/D Control Status Register<br>A/D Data Register High<br>A/D Amplifier Control/Data Low Register                                                                                   | 00h<br>xxh<br>0xh                             | R/W<br>Read Only<br>R/W                |  |  |  |

| 0037h                                              | ITC                      | EICR                                        | External Interrupt Control Register                                                                                                                                                | 00h                                           | R/W                                    |  |  |  |

| 0038h                                              | MCC                      | MCCSR                                       | Main Clock Control/Status Register                                                                                                                                                 | 00h                                           | R/W                                    |  |  |  |

| 0039h<br>003Ah                                     | Clock and<br>Reset       | RCCR<br>SICSR                               | RC oscillator Control Register<br>System Integrity Control/Status Register                                                                                                         | FFh<br>0110 0xx0b                             | R/W<br>R/W                             |  |  |  |

| 003Bh                                              | PLL clock<br>select      | PLLTST                                      | PLL test register                                                                                                                                                                  | 00h                                           | R/W                                    |  |  |  |

| 003Ch                                              | ITC                      | EISR                                        | External Interrupt Selection Register                                                                                                                                              | 0Ch                                           | R/W                                    |  |  |  |

| 003Dh to<br>0048h                                  |                          |                                             | Reserved area (12 bytes)                                                                                                                                                           |                                               |                                        |  |  |  |

| 0049h<br>004Ah                                     | AWU                      | AWUPR<br>AWUCSR                             | AWU Prescaler Register<br>AWU Control/Status Register                                                                                                                              | FFh<br>00h                                    | R/W<br>R/W                             |  |  |  |

| 004Bh<br>004Ch<br>004Dh<br>004Eh<br>004Fh<br>0050h | DM <sup>3)</sup>         | DMCR DMSR DMBK1H DMBK1L DMBK2H DMBK2L DMCR2 | DM Control Register DM Status Register DM Breakpoint Register 1 High DM Breakpoint Register 1 Low DM Breakpoint Register 2 High DM Breakpoint Register 2 Low DM Control Register 2 | 00h<br>00h<br>00h<br>00h<br>00h<br>00h<br>00h | R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W |  |  |  |

| 0052h to<br>007Fh                                  | Reserved area (46 bytes) |                                             |                                                                                                                                                                                    |                                               |                                        |  |  |  |

**Legend**: x=undefined, R/W=read/write

# Notes:

1. The contents of the I/O port DR registers are readable only in output configuration. In input configuration, the values of the I/O pins are returned instead of the DR register contents.

2. The bits associated with unavailable pins must always keep their reset value.

3. For a description of the Debug Module registers, see ICC protocol reference manual.

## FLASH PROGRAM MEMORY (Cont'd)

## 4.5 Memory Protection

There are two different types of memory protection: Read Out Protection and Write/Erase Protection which can be applied individually.

#### 4.5.1 Read out Protection

Readout protection, when selected provides a protection against program memory content extraction and against write access to Flash memory. Even if no protection can be considered as totally unbreakable, the feature provides a very high level of protection for a general purpose microcontroller. Both program and data E<sup>2</sup> memory are protected.

In flash devices, this protection is removed by reprogramming the option. In this case, both program and data E<sup>2</sup> memory are automatically erased and the device can be reprogrammed.

Read-out protection selection depends on the device type:

- In Flash devices it is enabled and removed through the FMP\_R bit in the option byte.

- In ROM devices it is enabled by mask option specified in the Option List.

#### 4.5.2 Flash Write/Erase Protection

Write/erase protection, when set, makes it impossible to both overwrite and erase program memory. It does not apply to E<sup>2</sup> data. Its purpose is to provide advanced security to applications and prevent any change being made to the memory content.

**Warning**: Once set, Write/erase protection can never be removed. A write-protected flash device is no longer reprogrammable.

Write/erase protection is enabled through the FMP\_W bit in the option byte.

#### 4.6 Related Documentation

For details on Flash programming and ICC protocol, refer to the ST7 Flash Programming Reference Manual and to the ST7 ICC Protocol Reference Manual.

## 4.7 Register Description

# FLASH CONTROL/STATUS REGISTER (FCSR)

Read/Write

Reset Value: 000 0000 (00h) 1st RASS Key: 0101 0110 (56h) 2nd RASS Key: 1010 1110 (AEh)

| 7 |   |   |   |   |     |     | 0   |

|---|---|---|---|---|-----|-----|-----|

| 0 | 0 | 0 | 0 | 0 | OPT | LAT | PGM |

**Note:** This register is reserved for programming using ICP, IAP or other programming methods. It controls the XFlash programming and erasing operations.

When an EPB or another programming tool is used (in socket or ICP mode), the RASS keys are sent automatically.

47/

## POWER SAVING MODES (Cont'd)

## 9.3 WAIT MODE

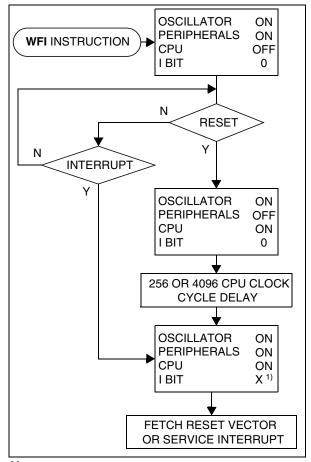

WAIT mode places the MCU in a low power consumption mode by stopping the CPU.

This power saving mode is selected by calling the 'WFI' instruction.

All peripherals remain active. During WAIT mode, the I bit of the CC register is cleared, to enable all interrupts. All other registers and memory remain unchanged. The MCU remains in WAIT mode until an interrupt or RESET occurs, whereupon the Program Counter branches to the starting address of the interrupt or Reset service routine.

The MCU will remain in WAIT mode until a Reset or an Interrupt occurs, causing it to wake up.

Refer to Figure 24.

Figure 24. WAIT Mode Flow-chart

## Note:

1. Before servicing an interrupt, the CC register is pushed on the stack. The I bit of the CC register is set during the interrupt routine and cleared when the CC register is popped.

### POWER SAVING MODES (Cont'd)

### Similarities with Halt mode

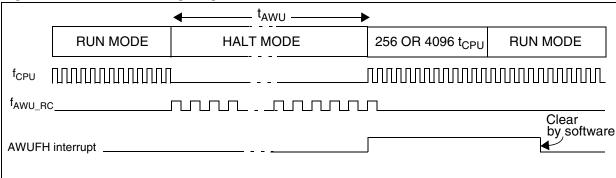

The following AWUFH mode behaviour is the same as normal Halt mode:

- The MCU can exit AWUFH mode by means of any interrupt with exit from Halt capability or a reset (see Section 9.4 HALT MODE).

- When entering AWUFH mode, the I bit in the CC register is forced to 0 to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes up immediately.

- In AWUFH mode, the main oscillator is turned off causing all internal processing to be stopped, including the operation of the on-chip peripherals. None of the peripherals are clocked except those which get their clock supply from another clock generator (such as an external or auxiliary oscillator like the AWU oscillator).

- The compatibility of Watchdog operation with AWUFH mode is configured by the WDGHALT option bit in the option byte. Depending on this setting, the HALT instruction when executed while the Watchdog system is enabled, can generate a Watchdog RESET.

Figure 30. AWUF Halt Timing Diagram

# I/O PORTS (Cont'd)

## 10.7 DEVICE-SPECIFIC I/O PORT CONFIGURATION

The I/O port register configurations are summarised as follows.

#### **Standard Ports**

## PA7:0, PB6:0

| MODE              | DDR | OR |

|-------------------|-----|----|

| floating input    | 0   | 0  |

| pull-up input     | 0   | 1  |

| open drain output | 1   | 0  |

| push-pull output  | 1   | 1  |

# **Interrupt Ports**

# Ports where the external interrupt capability is selected using the EISR register

| MODE                    | DDR | OR |

|-------------------------|-----|----|

| floating input          | 0   | 0  |

| pull-up interrupt input | 0   | 1  |

| open drain output       | 1   | 0  |

| push-pull output        | 1   | 1  |

# PC1:0 (multiplexed with OSC1,OSC2)

| MODE             | DDR |

|------------------|-----|

| floating input   | 0   |

| push-pull output | 1   |

The selection between OSC1 or PC0 and OSC2 or PC1 is done by option byte. Refer to section 15.1 on page 149. Interrupt capability is not available on PC1:0.

**Note:** PCOR not implemented but p-transistor always active in output mode (refer to Figure 32 on page 50)

## Table 10. Port Configuration (Standard ports)

| Port   | Pin name     | Inp      | out     | Output     |           |  |

|--------|--------------|----------|---------|------------|-----------|--|

|        | Fill liallie | OR = 0   | OR = 1  | OR = 0     | OR = 1    |  |

| Port A | PA7:0        | floating | pull-up | open drain | push-pull |  |

| Port B | PB6:0        | floating | pull-up | open drain | push-pull |  |

**Note:** On ports where the external interrupt capability is selected using the EISR register, the configuration will be as follows:

| Port   | Pin name   | Inj      | out               | Out        | Output    |  |  |

|--------|------------|----------|-------------------|------------|-----------|--|--|

|        | Filitianie | OR = 0   | OR = 1            | OR = 0     | OR = 1    |  |  |

| Port A | PA7:0      | floating | pull-up interrupt | open drain | push-pull |  |  |

| Port B | PB6:0      | floating | pull-up interrupt | open drain | push-pull |  |  |

Table 11. I/O Port Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|-------------------|-------------------|-----|---|---|---|---|---|---|-----|

| 00001-            | PADR              | MSB |   |   |   |   |   |   | LSB |

| 0000h             | Reset Value       | 1   | 1 | 1 | 1 | 1 | 1 | 1 | 1   |

| 0001h             | PADDR             | MSB |   |   |   |   |   |   | LSB |

|                   | Reset Value       | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

# **DUAL 12-BIT AUTORELOAD TIMER 4 (Cont'd)**

# 11.2.4 Low Power Modes

| Mode | Description           |

|------|-----------------------|

| WAIT | No effect on AT timer |

| HALT | AT timer halted.      |

# 11.2.5 Interrupts

| Interrupt<br>Event | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt | Exit<br>from<br>Active-<br>Halt |

|--------------------|---------------|--------------------------|----------------------|----------------------|---------------------------------|

| Overflow<br>Event  | OVF1          | OVIE1                    | Yes                  | No                   | Yes                             |

| AT4 IC Event       | ICF           | ICIE                     | Yes                  | No                   | No                              |

| CMP Event          | CMPFx         | CMPIE                    | Yes                  | No                   | No                              |

| Overflow<br>Event2 | OVF2          | OVIE2                    | Yes                  | No                   | No                              |

**Note:** The CMP and AT4 IC events are connected to the same interrupt vector.

The OVF event is mapped on a separate vector (see Interrupts chapter).

They generate an interrupt if the enable bit is set in the ATCSR register and the interrupt mask in the CC register is reset (RIM instruction).

# DUAL 12-BIT AUTORELOAD TIMER 4 (Cont'd)

Table 14. Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label      | 7            | 6            | 5            | 4            | 3             | 2             | 1            | 0            |

|-------------------|------------------------|--------------|--------------|--------------|--------------|---------------|---------------|--------------|--------------|

| 0D                | ATCSR<br>Reset Value   | 0            | ICF<br>0     | ICIE<br>0    | CK1<br>0     | CK0<br>0      | OVF1<br>0     | OVFIE1<br>0  | CMPIE<br>0   |

| 0E                | CNTR1H<br>Reset Value  | 0            | 0            | 0            | 0            | CNTR1_11<br>0 | CNTR1_10<br>0 | CNTR1_9<br>0 | CNTR1_8<br>0 |

| 0F                | CNTR1L<br>Reset Value  | CNTR1_7<br>0 | CNTR1_8<br>0 | CNTR1_7<br>0 | CNTR1_6<br>0 | CNTR1_3<br>0  | CNTR1_2<br>0  | CNTR1_1<br>0 | CNTR1_0<br>0 |

| 10                | ATR1H<br>Reset Value   | 0            | 0            | 0            | 0            | ATR11<br>0    | ATR10<br>0    | ATR9<br>0    | ATR8<br>0    |

| 11                | ATR1L<br>Reset Value   | ATR7<br>0    | ATR6<br>0    | ATR5<br>0    | ATR4<br>0    | ATR3<br>0     | ATR2<br>0     | ATR1<br>0    | ATR0<br>0    |

| 12                | PWMCR<br>Reset Value   | 0            | OE3<br>0     | 0            | OE2<br>0     | 0             | OE1<br>0      | 0            | OE0<br>0     |

| 13                | PWM0CSR<br>Reset Value | 0            | 0            | 0            | 0            | 0             | 0             | OP0<br>0     | CMPF0<br>0   |

| 14                | PWM1CSR<br>Reset Value | 0            | 0            | 0            | 0            | 0             | 0             | OP1<br>0     | CMPF1<br>0   |

| 15                | PWM2CSR<br>Reset Value | 0            | 0            | 0            | 0            | 0             | 0             | OP2<br>0     | CMPF2<br>0   |

| 16                | PWM3CSR<br>Reset Value | 0            | 0            | 0            | 0            | OP_EN<br>0    | OPEDGE<br>0   | OP3<br>0     | CMPF3<br>0   |

| 17                | DCR0H<br>Reset Value   | 0            | 0            | 0            | 0            | DCR11<br>0    | DCR10<br>0    | DCR9<br>0    | DCR8<br>0    |

| 18                | DCR0L<br>Reset Value   | DCR7<br>0    | DCR6<br>0    | DCR5<br>0    | DCR4<br>0    | DCR3<br>0     | DCR2<br>0     | DCR1<br>0    | DCR0<br>0    |

| 19                | DCR1H<br>Reset Value   | 0            | 0            | 0            | 0            | DCR11<br>0    | DCR10<br>0    | DCR9<br>0    | DCR8<br>0    |

| 1A                | DCR1L<br>Reset Value   | DCR7<br>0    | DCR6<br>0    | DCR5<br>0    | DCR4<br>0    | DCR3<br>0     | DCR2<br>0     | DCR1<br>0    | DCR0<br>0    |

| 1B                | DCR2H<br>Reset Value   | 0            | 0            | 0            | 0            | DCR11<br>0    | DCR10<br>0    | DCR9<br>0    | DCR8<br>0    |

| 1C                | DCR2L<br>Reset Value   | DCR7<br>0    | DCR6<br>0    | DCR5<br>0    | DCR4<br>0    | DCR3<br>0     | DCR2<br>0     | DCR1<br>0    | DCR0<br>0    |

| 1D                | DCR3H<br>Reset Value   | 0            | 0            | 0            | 0            | DCR11<br>0    | DCR10<br>0    | DCR9<br>0    | DCR8<br>0    |

| 1E                | DCR3L<br>Reset Value   | DCR7<br>0    | DCR6<br>0    | DCR5<br>0    | DCR4<br>0    | DCR3<br>0     | DCR2<br>0     | DCR1<br>0    | DCR0<br>0    |

| 1F                | ATICRH<br>Reset Value  | 0            | 0            | 0            | 0            | ICR11<br>0    | ICR10<br>0    | ICR9<br>0    | ICR8<br>0    |

| 20                | ATICRL<br>Reset Value  | ICR7<br>0    | ICR6<br>0    | ICR5<br>0    | ICR4<br>0    | ICR3<br>0     | ICR2<br>0     | ICR1<br>0    | ICR0<br>0    |

# 11.4.3.3 Master Mode Operation

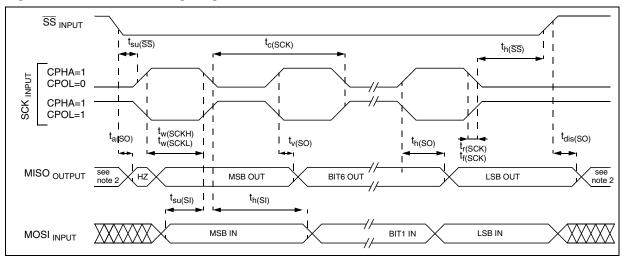

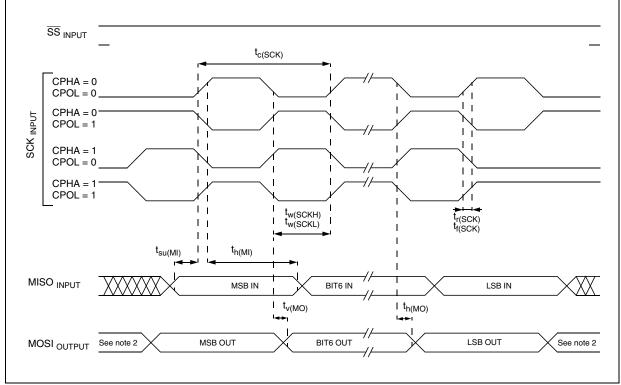

In master mode, the serial clock is output on the SCK pin. The clock frequency, polarity and phase are configured by software (refer to the description of the SPICSR register).

**Note:** The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL = 1 or pulling down SCK if CPOL = 0).

## How to operate the SPI in master mode

To operate the SPI in master mode, perform the following steps in order:

- 1. Write to the SPICR register:

- Select the clock frequency by configuring the SPR[2:0] bits.

- Select the clock polarity and clock phase by configuring the CPOL and CPHA bits. Figure 5 shows the four possible configurations.

Note: The slave must have the same CPOL and CPHA settings as the master.

- 2. Write to the SPICSR register:

- Either set the SSM bit and set the SSI bit or clear the SSM bit and tie the SS pin high for the complete byte transmit sequence.

- 3. Write to the SPICR register:

- Set the MSTR and SPE bits

Note: MSTR and SPE bits remain set only if SS is high).

**Important note:** if the SPICSR register is not written first, the SPICR register setting (MSTR bit) may be not taken into account.

The transmit sequence begins when software writes a byte in the SPIDR register.

## 11.4.3.4 Master Mode Transmit Sequence

When software writes to the SPIDR register, the data byte is loaded into the 8-bit shift register and then shifted out serially to the MOSI pin most significant bit first.

When data transfer is complete:

- The SPIF bit is set by hardware.

- An interrupt request is generated if the SPIE bit is set and the interrupt mask in the CCR register is cleared.

Clearing the SPIF bit is performed by the following software sequence:

- An access to the SPICSR register while the SPIF bit is set

- 2. A read to the SPIDR register

**Note:** While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

## 11.4.3.5 Slave Mode Operation

In slave mode, the serial clock is received on the SCK pin from the master device.

To operate the SPI in slave mode:

- Write to the SPICSR register to perform the following actions:

- Select the clock polarity and clock phase by configuring the CPOL and CPHA bits (see Figure 5).

Note: The slave must have the same CPOL

and CPHA settings as the master.

- Manage the SS pin as described in Section 0.1.3.2 and Figure 3. If CPHA = 1 SS must be held low continuously. If CPHA = 0 SS must be held low during byte transmission and pulled up between each byte to let the slave write in the shift register.

- Write to the SPICR register to clear the MSTR bit and set the SPE bit to enable the SPI I/O functions.

## 11.4.3.6 Slave Mode Transmit Sequence

When software writes to the SPIDR register, the data byte is loaded into the 8-bit shift register and then shifted out serially to the MISO pin most significant bit first.

The transmit sequence begins when the slave device receives the clock signal and the most significant bit of the data on its MOSI pin.

When data transfer is complete:

- The SPIF bit is set by hardware.

- An interrupt request is generated if SPIE bit is set and interrupt mask in the CCR register is cleared.

Clearing the SPIF bit is performed by the following software sequence:

- An access to the SPICSR register while the SPIF bit is set

- 2. A write or a read to the SPIDR register

**Notes:** While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

The SPIF bit can be cleared during a second transmission; however, it must be cleared before the second SPIF bit in order to prevent an Overrun condition (see Section 0.1.5.2).

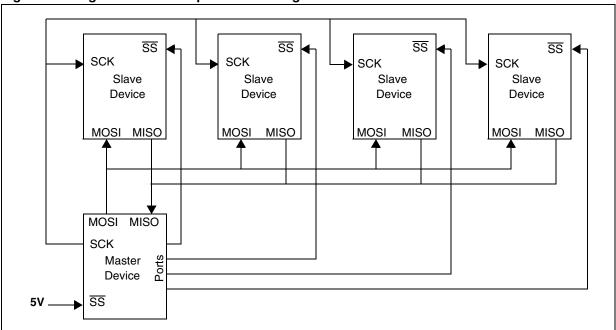

# 11.4.5.4 Single Master and Multimaster Configurations

There are two types of SPI systems:

- Single Master System

- Multimaster System

### Single Master System

A typical single master system may be configured using a device as the master and four devices as slaves (see Figure 7).

The master device selects the individual slave devices by <u>using</u> four pins of a parallel port to control the four <u>SS</u> pins of the slave devices.

The  $\overline{SS}$  pins are pulled high during reset since the master device ports will be forced to be inputs at that time, thus disabling the slave devices.

**Note:** To prevent a bus conflict on the MISO line, the master allows only one active slave device during a transmission.

For more security, the slave device may respond to the master with the received data byte. Then the master will receive the previous byte back from the slave device if all MISO and MOSI pins are connected and the slave has not written to its SPIDR register.

Other transmission security methods can use ports for handshake lines or data bytes with command fields.

## **Multimaster System**

A multimaster system may also be configured by the user. Transfer of master control could be implemented using a handshake method through the I/O ports or by an exchange of code messages through the serial peripheral interface system.

The multimaster system is principally handled by the MSTR bit in the SPICR register and the MODF bit in the SPICSR register.

Figure 59. Single Master / Multiple Slave Configuration

#### 11.4.6 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on SPI. SPI interrupt events cause the device to exit from WAIT mode.                                                                                                                                                                                                                                                                                                                                                                                                        |

| HALT | SPI registers are frozen. In HALT mode, the SPI is inactive. SPI operation resumes when the device is woken up by an interrupt with "exit from HALT mode" capability. The data received is subsequently read from the SPIDR register when the software is running (interrupt vector fetching). If several data are received before the wake-up event, then an overrun error is generated. This error can be detected after the fetch of the interrupt routine that woke up the Device. |

# 11.4.6.1 Using the SPI to wake up the device from Halt mode

In slave configuration, the SPI is able to wake up the device from HALT mode through a SPIF interrupt. The data received is subsequently read from the SPIDR register when the software is running (interrupt vector fetch). If multiple data transfers have been performed before software clears the SPIF bit, then the OVR bit is set by hardware.

**Note:** When waking up from HALT mode, if the SPI remains in Slave mode, it is recommended to perform an extra communications cycle to bring

the SPI from HALT mode state to normal state. If the SPI exits from Slave mode, it returns to normal state immediately.

**Caution:** The SPI can wake up the device from HALT mode only if the Slave Select signal (external SS pin or the SSI bit in the SPICSR register) is low when the device enters HALT mode. So, if Slave selection is configured as external (see Section 0.1.3.2), make sure the master drives a low level on the SS pin when the slave enters HALT mode.

# 11.4.7 Interrupts

| Interrupt Event              | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|------------------------------|---------------|--------------------------|----------------------|----------------------|

| SPI End of<br>Transfer Event | SPIF          |                          |                      | Yes                  |

| Master Mode<br>Fault Event   | MODF          | SPIE                     | Yes                  | No                   |

| Overrun Error                | OVR           |                          |                      |                      |

**Note**: The SPI interrupt events are connected to the same interrupt vector (see Interrupts chapter). They generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

# SPI CONTROL/STATUS REGISTER (SPICSR)

Read/Write (some bits Read Only) Reset Value: 0000 0000 (00h)

| 7    |      |     |      |   |     |     | 0   |

|------|------|-----|------|---|-----|-----|-----|

| SPIF | WCOL | OVR | MODF | - | SOD | SSM | SSI |

# Bit 7 = **SPIF** Serial Peripheral Data Transfer Flag (Read only)

This bit is set by hardware when a transfer has been completed. An interrupt is generated if SPIE = 1 in the SPICR register. It is cleared by a software sequence (an access to the SPICSR register followed by a write or a read to the SPIDR register).

- 0: Data transfer is in progress or the flag has been cleared.

- 1: Data transfer between the device and an external device has been completed.

**Note:** While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

Bit 6 = **WCOL** Write Collision status (Read only)

This bit is set by hardware when a write to the SPIDR register is done during a transmit sequence. It is cleared by a software sequence (see Figure 6).

- 0: No write collision occurred

- 1: A write collision has been detected

#### Bit 5 = **OVR** SPI Overrun error (Read only)

This bit is set by hardware when the byte currently being received in the shift register is ready to be transferred into the SPIDR register while SPIF = 1 (See Section 0.1.5.2). An interrupt is generated if SPIE = 1 in the SPICR register. The OVR bit is cleared by software reading the SPICSR register.

- 0: No overrun error

- 1: Overrun error detected

#### Bit 4 = **MODF** *Mode Fault flag (Read only)*

This bit is set by hardware when the  $\overline{SS}$  pin is pulled low in master mode (see Section 0.1.5.1 Master Mode Fault (MODF)). An SPI interrupt can be generated if SPIE = 1 in the SPICR register. This bit is cleared by a software sequence (An access to the SPICSR register while MODF = 1 followed by a write to the SPICR register).

- 0: No master mode fault detected

- 1: A fault in master mode has been detected

Bit 3 = Reserved, must be kept cleared.

## Bit 2 = **SOD** SPI Output Disable

This bit is set and cleared by software. When set, it disables the alternate function of the SPI output (MOSI in master mode / MISO in slave mode)

- 0: SPI output enabled (if SPE = 1)

- 1: SPI output disabled

# Bit $1 = SSM \overline{SS}$ Management

This bit is set and cleared by software. When set, it disables the alternate function of the SPI SS pin and uses the SSI bit value instead. See Section 0.1.3.2 Slave Select Management.

- 0: Hardware management (SS managed by external pin)

- 1: Software management (internal  $\overline{SS}$  signal controlled by SSI bit. External  $\overline{SS}$  pin free for general-purpose I/O)

#### Bit $0 = SSI \overline{SS}$ Internal Mode

This bit is set and cleared by software. It acts as a 'chip select' by controlling the level of the SS slave select signal when the SSM bit is set.

- 0: Slave selected

- 1: Slave deselected

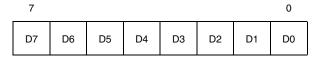

# SPI DATA I/O REGISTER (SPIDR)

Read/Write

Reset Value: Undefined

The SPIDR register is used to transmit and receive data on the serial bus. In a master device, a write to this register will initiate transmission/reception of another byte.

**Notes:** During the last clock cycle the SPIF bit is set, a copy of the received data byte in the shift register is moved to a buffer. When the user reads the serial peripheral data I/O register, the buffer is actually being read.

While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

**Warning:** A write to the SPIDR register places data directly into the shift register for transmission.

A read to the SPIDR register returns the value located in the buffer and not the content of the shift register (see Figure 1).

## ST7 ADDRESSING MODES (cont'd)

#### 12.1.1 Inherent

All Inherent instructions consist of a single byte. The opcode fully specifies all the required information for the CPU to process the operation.

| Inherent Instruction       | Function                            |

|----------------------------|-------------------------------------|

| NOP                        | No operation                        |

| TRAP                       | S/W Interrupt                       |

| WFI                        | Wait For Interrupt (Low Power Mode) |

| HALT                       | Halt Oscillator (Lowest Power Mode) |

| RET                        | Subroutine Return                   |

| IRET                       | Interrupt Subroutine Return         |

| SIM                        | Set Interrupt Mask                  |

| RIM                        | Reset Interrupt Mask                |

| SCF                        | Set Carry Flag                      |

| RCF                        | Reset Carry Flag                    |

| RSP                        | Reset Stack Pointer                 |

| LD                         | Load                                |

| CLR                        | Clear                               |

| PUSH/POP                   | Push/Pop to/from the stack          |

| INC/DEC                    | Increment/Decrement                 |

| TNZ                        | Test Negative or Zero               |

| CPL, NEG                   | 1 or 2 Complement                   |

| MUL                        | Byte Multiplication                 |

| SLL, SRL, SRA, RLC,<br>RRC | Shift and Rotate Operations         |

| SWAP                       | Swap Nibbles                        |

#### 12.1.2 Immediate

Immediate instructions have 2 bytes, the first byte contains the opcode, the second byte contains the operand value.

| Immediate Instruction | Function              |

|-----------------------|-----------------------|

| LD                    | Load                  |

| CP                    | Compare               |

| BCP                   | Bit Compare           |

| AND, OR, XOR          | Logical Operations    |

| ADC, ADD, SUB, SBC    | Arithmetic Operations |

#### 12.1.3 Direct

In Direct instructions, the operands are referenced by their memory address.

The direct addressing mode consists of two submodes:

# Direct (Short)

The address is a byte, thus requires only 1 byte after the opcode, but only allows 00 - FF addressing space.

# Direct (Long)

The address is a word, thus allowing 64 Kbyte addressing space, but requires 2 bytes after the opcode.

# 12.1.4 Indexed (No Offset, Short, Long)

In this mode, the operand is referenced by its memory address, which is defined by the unsigned addition of an index register (X or Y) with an offset.

The indirect addressing mode consists of three submodes:

# Indexed (No Offset)

There is no offset (no extra byte after the opcode), and allows 00 - FF addressing space.

# Indexed (Short)

The offset is a byte, thus requires only 1 byte after the opcode and allows 00 - 1FE addressing space.

#### Indexed (Long)

The offset is a word, thus allowing 64 Kbyte addressing space and requires 2 bytes after the opcode.

#### 12.1.5 Indirect (Short, Long)

The required data byte to do the operation is found by its memory address, located in memory (pointer)

The pointer address follows the opcode. The indirect addressing mode consists of two submodes:

#### Indirect (Short)

The pointer address is a byte, the pointer size is a byte, thus allowing 00 - FF addressing space, and requires 1 byte after the opcode.

#### Indirect (Long)

The pointer address is a byte, the pointer size is a word, thus allowing 64 Kbyte addressing space, and requires 1 byte after the opcode.

# 13.4.2 On-chip peripherals

| Symbol   | Parameter                                  | Cor                    | nditions              | Тур  | Unit |

|----------|--------------------------------------------|------------------------|-----------------------|------|------|

| 1        | 12-bit Auto-Reload Timer supply current 1) | f <sub>CPU</sub> =4MHz | V <sub>DD</sub> =3.0V | 150  |      |

| IDD(AT)  | 12-bit Auto-neload Timer supply current    | f <sub>CPU</sub> =8MHz | V <sub>DD</sub> =5.0V | 1000 |      |

| I        | SPI supply current <sup>2)</sup>           | f <sub>CPU</sub> =4MHz | V <sub>DD</sub> =3.0V | 50   | μA   |

| IDD(SPI) | Si i supply current                        | f <sub>CPU</sub> =8MHz | V <sub>DD</sub> =5.0V | 200  | μΑ   |

| 1        | ADC supply current when converting 3)      | f <sub>ADC</sub> =4MHz | V <sub>DD</sub> =3.0V | 250  |      |

| IDD(ADC) | ADO Supply current when converting         | IADC-4MI               | V <sub>DD</sub> =5.0V | 1100 |      |

#### Notes:

- 1. Data based on a differential  $I_{DD}$  measurement between reset configuration (timer stopped) and a timer running in PWM mode at  $f_{cpu}$ =8MHz.

- **2.** Data based on a differential  $I_{DD}$  measurement between reset configuration and a permanent SPI master communication (data sent equal to 55h).

- ${f 3.}$  Data based on a differential  ${f I}_{DD}$  measurement between reset configuration and continuous A/D conversions with amplifier disabled.

#### 13.7 EMC CHARACTERISTICS

Susceptibility tests are performed on a sample basis during product characterization.

# 13.7.1 Functional EMS (Electro Magnetic Susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electro magnetic events until a failure occurs (indicated by the LEDs).

- ESD: Electro-Static Discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

# 13.7.1.1 Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical applica-

tion environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

## **Software recommendations:**

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

### Prequalification trials:

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the RE-SET pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behaviour is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol            | Parameter                                                                                                                                | Conditions                                                                                     | Level/<br>Class |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                           | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C, f <sub>OSC</sub> =8MHz<br>conforms to IEC 1000-4-2 | 2B              |

| V <sub>FFTB</sub> | Fast transient voltage burst limits to be applied through 100pF on $\rm V_{DD}$ and $\rm V_{SS}$ pins to induce a functional disturbance | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C, f <sub>OSC</sub> =8MHz<br>conforms to IEC 1000-4-4 | ЗВ              |

#### 13.7.2 Electro Magnetic Interference (EMI)

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm SAE J 1752/3 which specifies the board and the loading of each pin.

| Symbol Parameter |             | Conditions                                                   | Monitored       | Max vs. [f <sub>OSC</sub> /f <sub>CPU</sub> ] |         | Unit      |

|------------------|-------------|--------------------------------------------------------------|-----------------|-----------------------------------------------|---------|-----------|

| Symbol           | raiailletei | Conditions                                                   | Frequency Band  | 8/4MHz                                        | 16/8MHz |           |

|                  |             | V =V = 0=00                                                  | 0.1MHz to 30MHz | 15                                            | 21      |           |

| S                | Peak level  | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C,<br>SO20 package, | 30MHz to 130MHz | 22                                            | 29      | $dB\mu V$ |

| S <sub>EMI</sub> | I can level | conforming to SAE J 1752/3                                   | 130MHz to 1GHz  | 17                                            | 22      |           |

|                  |             |                                                              | SAE EMI Level   | 3.5                                           | 3.5     | -         |

#### Note:

1. Data based on characterization results, not tested in production.

## **EMC CHARACTERISTICS** (Cont'd)

# 13.7.3 Absolute Maximum Ratings (Electrical Sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

# 13.7.3.1 Electro-Static Discharge (ESD)

Electro-Static Discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). Two models can be simulated: Human Body Model and Machine Model. This test conforms to the JESD22-A114A/A115A standard.

# **Absolute Maximum Ratings**

| Symbol                | Ratings                                             | Conditions            | Maximum value 1) | Unit |

|-----------------------|-----------------------------------------------------|-----------------------|------------------|------|

| V <sub>ESD(HBM)</sub> | Electro-static discharge voltage (Human Body Model) | T <sub>A</sub> =+25°C | 8000             | V    |

| V <sub>ESD(MM)</sub>  | Electro-static discharge voltage (Machine Model)    | T <sub>A</sub> =+25°C | 400              | V    |

#### Note:

1. Data based on characterization results, not tested in production.

### 13.7.3.2 Static Latch-Up

LU: 3 complementary static tests are required on 6 parts to assess the latch-up performance.

A supply overvoltage (applied to each power supply pin) and a current injection (applied to each input, output and configurable I/O pin) are performed on each sample. This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

## **Electrical Sensitivities**

| Symbol | Parameter             | Conditions                                     | Class  |

|--------|-----------------------|------------------------------------------------|--------|

| LU     | Static latch-up class | T <sub>A</sub> =+25°C<br>T <sub>A</sub> =+85°C | A<br>A |

47/

# I/O PORT PIN CHARACTERISTICS (Cont'd)

# 13.8.2 Output Driving Current

Subject to general operating conditions for V<sub>DD</sub>, f<sub>CPU</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol                          | Parameter                                                                                         |                       | Conditions                                   | Min                  | Max  | Unit |

|---------------------------------|---------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------|----------------------|------|------|

|                                 | Output low level voltage for a standard I/O pin                                                   |                       | I <sub>IO</sub> =+5mA T <sub>A</sub> ≤125°C  |                      | 1.0  |      |

| V <sub>OL</sub> 1)              | when 8 pins are sunk at same time (see Figure 83)                                                 |                       | I <sub>IO</sub> =+2mA T <sub>A</sub> ≤125°C  |                      | 0.4  |      |

| VOL                             | Output low level voltage for a high sink I/O pin                                                  | -5V                   | I <sub>IO</sub> =+20mA,T <sub>A</sub> ≤125°C |                      | 1.3  |      |

|                                 | when 4 pins are sunk at same time (see Figure 89)                                                 | V <sub>DD</sub> =5V   | I <sub>IO</sub> =+8mA T <sub>A</sub> ≤125°C  |                      | 0.75 |      |

| v 2)                            | Output high level voltage for an I/O pin                                                          |                       | I <sub>IO</sub> =-5mA, T <sub>A</sub> ≤125°C | V <sub>DD</sub> -1.5 |      |      |

| V <sub>OH</sub> <sup>2)</sup>   | when 4 pins are sourced at same time (see Figure 95)                                              |                       | I <sub>IO</sub> =-2mA T <sub>A</sub> ≤125°C  | V <sub>DD</sub> -0.8 |      |      |

| V <sub>OL</sub> 1)3)            | Output low level voltage for a standard I/O pin when 8 pins are sunk at same time (see Figure 82) |                       | I <sub>IO</sub> =+2mA T <sub>A</sub> ≤125°C  |                      | 0.5  |      |

|                                 | Output low level voltage for a high sink I/O pin when 4 pins are sunk at same time                | 3.3V                  | I <sub>IO</sub> =+8mA T <sub>A</sub> ≤125°C  |                      | 0.5  | V    |

| V <sub>OH</sub> <sup>2)3)</sup> | Output high level voltage for an I/O pin when 4 pins are sourced at same time (Figure 94)         | V <sub>DD</sub> =3.   | I <sub>IO</sub> =-2mA T <sub>A</sub> ≤125°C  | V <sub>DD</sub> -0.8 |      |      |

| V <sub>OL</sub> 1)3)            | Output low level voltage for a standard I/O pin when 8 pins are sunk at same time (see Figure 87) |                       | I <sub>IO</sub> =+2mA T <sub>A</sub> ≤125°C  |                      | 0.6  |      |

|                                 | Output low level voltage for a high sink I/O pin when 4 pins are sunk at same time                | >                     | I <sub>IO</sub> =+8mA T <sub>A</sub> ≤125°C  |                      | 0.6  |      |

| V <sub>OH</sub> <sup>2)3)</sup> | Output high level voltage for an I/O pin when 4 pins are sourced at same time (see Figure 101)    | V <sub>DD</sub> =2.7V | I <sub>IO</sub> =-2mA T <sub>A</sub> ≤125°C  | V <sub>DD</sub> -0.9 |      |      |

### Notes:

- 1. The  $I_{IO}$  current sunk must always respect the absolute maximum rating specified in Section 13.2.2 and the sum of  $I_{IO}$  (I/O ports and control pins) must not exceed  $I_{VSS}$ .

- 2. The  $I_{IO}$  current sourced must always respect the absolute maximum rating specified in Section 13.2.2 and the sum of  $I_{IO}$  (I/O ports and control pins) must not exceed  $I_{VDD}$ .

- 3. Not tested in production, based on characterization results.

# I/O PORT PIN CHARACTERISTICS (Cont'd)

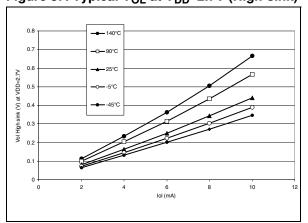

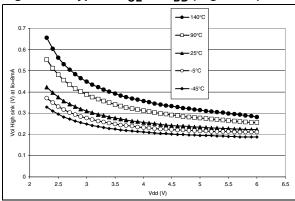

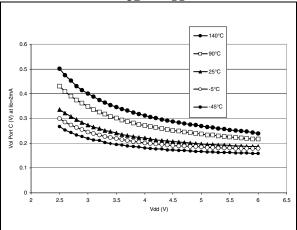

Figure 87. Typical  $V_{OL}$  at  $V_{DD}$ =2.7V (High-sink)

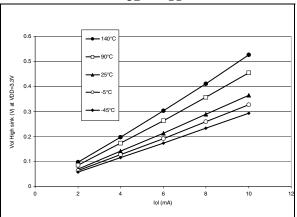

Figure 88. Typical V<sub>OL</sub> at V<sub>DD</sub>=3.3V (High-sink)

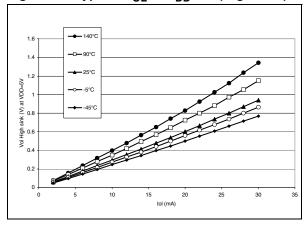

Figure 89. Typical  $V_{OL}$  at  $V_{DD}$ =5V (High-sink)

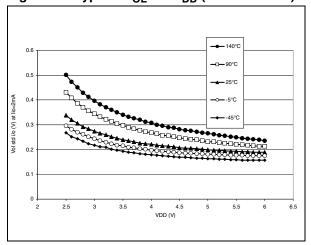

Figure 90. Typical V<sub>OL</sub> vs. V<sub>DD</sub> (standard I/Os)

Figure 91. Typical  $V_{OL}$  vs  $V_{DD}$  (High-sink)

Figure 92. Typical V<sub>OL</sub> vs V<sub>DD</sub> (Port C)

477

# **COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)**

# Figure 108. SPI Slave Timing Diagram with CPHA=1 1)

Figure 109. SPI Master Timing Diagram 1)

#### Notes:

- 1. Measurement points are done at CMOS levels:  $0.3xV_{DD}$  and  $0.7xV_{DD}$ .

- 2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends of the I/O port configuration.

*5*7

|                                                                           | 317L11                       | E1xB FASTRON                                          | i illicrocontrolle                    | er option list                                                                         |                                                |  |

|---------------------------------------------------------------------------|------------------------------|-------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------|--|

| Customer Address                                                          | <br>                         |                                                       |                                       |                                                                                        |                                                |  |

| D                                                                         | <br>e*:<br>assigned          | d by STMicroelec                                      | tronics.                              |                                                                                        |                                                |  |

| Device Type/Memory Size                                                   |                              |                                                       |                                       |                                                                                        |                                                |  |

| FASTROM DEVICE:                                                           |                              | 2K                                                    | · <br>·                               | 4K                                                                                     | <br>                                           |  |

| VFQFPN20:  <br>SO20:  <br>PDIP20:  <br>SO16:  <br>PDIP16:                 | [] S                         | ST7PLIT19BY0M                                         | x   []S                               | ST7PLIT19BF1Ux<br>ST7PLIT19BF1Mx<br>ST7PLIT19BF1Bx<br>ST7PLIT19BY1Mx<br>ST7PLIT19BY1Bx | <b>(</b>                                       |  |

| Warning: Addresses DEE and RCCR1 (see section                             | 0h, DE<br>7.1 on p           | E1h, DEE2h and                                        | d DEE3h are res                       | served areas for                                                                       | ST to program RCCF                             |  |

| Conditioning (check only o<br>VFQFPN<br>SO                                | ne optio<br>[ ] Ta<br>[ ] Ta | n, do not specify<br>pe & Reel<br>pe & Reel           | for DIP package<br>[] Tray<br>[] Tube | ):                                                                                     |                                                |  |

| Special marking: [<br>Authorized characters are<br>Maximum character coun | letters,                     | digits, '.', '-', '/' a                               | and spaces only.                      | "                                                                                      |                                                |  |

| Temperature range:                                                        |                              | []-40°C t                                             | o +85°C                               | []-40°C to                                                                             | +125°C                                         |  |

| Watchdog selection (WDG_SW):                                              |                              | [] Softwa                                             | re activation                         | [] Hardware                                                                            | e activation                                   |  |

| Watchdog reset on Halt (\                                                 | VDG_H                        | ALT): [] Reset                                        |                                       | [] No Reset                                                                            | [] No Reset                                    |  |

| LVD reset (LVD):                                                          |                              | [] Disable                                            | ed                                    | [ ] Mědi                                                                               | est threshold<br>um threshold<br>est threshold |  |

| Sector 0 size (SEC):                                                      |                              | [] 0.5K                                               | [] 1K                                 | []2K                                                                                   | []4K                                           |  |

| Readout protection (FMP                                                   | _R):                         | [] Disabled                                           | [] Enabled                            |                                                                                        |                                                |  |

| Flash write protection (FM                                                | P_W):                        | [] Disabled                                           | [] Enabled                            |                                                                                        |                                                |  |

| RC oscillator (OSC) :                                                     |                              | [] Disabled                                           | [] Enabled                            |                                                                                        |                                                |  |

| Clock source selection (C<br>(if OSC disabled)                            | KSEL):                       | [] External cry<br>[] External Clo<br>[] External Clo |                                       | sonator:                                                                               |                                                |  |

| PLL (PLLOFF):                                                             |                              | [] Disabled                                           | [] Enabled                            |                                                                                        |                                                |  |

| PLL factor (PLLx4x8):                                                     |                              | [] PLLx4                                              | [] PLLx8                              |                                                                                        |                                                |  |

| PLL32 (PLL32OFF):                                                         |                              | [] Disabled                                           | [] Enabled                            |                                                                                        |                                                |  |

| Comments :<br>Supply operating range in t                                 | he appli                     | cation:                                               |                                       |                                                                                        |                                                |  |

152/159

#### 15.3 DEVELOPMENT TOOLS

Development tools for the ST7 microcontrollers include a complete range of hardware systems and software tools from STMicroelectronics and third-party tool suppliers. The range of tools includes solutions to help you evaluate microcontroller peripherals, develop and debug your application, and program your microcontrollers.

#### 15.3.1 Starter kits

ST offers complete, affordable **starter kits**. Starter kits are complete hardware/software tool packages that include features and samples to help you quickly start developing your application.

# 15.3.2 Development and debugging tools

Application development for ST7 is supported by fully optimizing **C Compilers** and the **ST7 Assembler-Linker** toolchain, which are all seamlessly integrated in the ST7 integrated development environments in order to facilitate the debugging and fine-tuning of your application. The Cosmic C Compiler is available in a free version that outputs up to 16KBytes of code.

The range of hardware tools includes full-featured ST7-EMU3 series emulators, cost effective ST7-DVP3 series emulators and the low-cost RLink in-circuit debugger/programmer. These tools are supported by the ST7 Toolset from STMicroelectronics, which includes the STVD7 integrated development environment (IDE) with high-level lan-

guage debugger, editor, project manager and integrated programming interface.

### 15.3.3 Programming tools

During the development cycle, the **ST7-DVP3** and and **ST7-EMU3 series emulators** and the **RLink** provide in-circuit programming capability for programming the Flash microcontroller on your application board.

ST also provides a low-cost dedicated in-circuit programmer, the **ST7-STICK**, as well as **ST7 Socket Boards** which provide all the sockets required for programming any of the devices in a specific ST7 sub-family on a platform that can be used with any tool with in-circuit programming capability for ST7.

For production programming of ST7 devices, ST's third-party tool partners also provide a complete range of gang and automated programming solutions, which are ready to integrate into your production environment.

# 15.3.4 Order Codes for Development and Programming Tools

Table 28 below lists the ordering codes for the ST7LITE1xB development and programming tools. For additional ordering codes for spare parts and accessories, refer to the online product selector at www.st.com/mcu.

#### 15.3.5 Order codes for ST7LITE1xB development tools

Table 28. Development tool order codes for the ST7LITE1xB family

| MCU                                                          | In-circuit Debugger, RLink Series <sup>1)</sup> |                                    | Emulator                        |                   | Programming Tool                       |                                 |

|--------------------------------------------------------------|-------------------------------------------------|------------------------------------|---------------------------------|-------------------|----------------------------------------|---------------------------------|

| ST7FLIT1xBF0<br>ST7FLIT1xBF1<br>ST7FLIT1xBY0<br>ST7FLIT1xBY1 | Starter Kit without<br>Demo Board               | Starter Kit with<br>Demo Board     | DVP Series                      | EMU Series        | In-circuit<br>Programmer               | ST Socket<br>Boards and<br>EPBs |

|                                                              | STX-RLINK <sup>2)</sup>                         | ST7FLITE-<br>SK/RAIS <sup>2)</sup> | ST7MDT10-<br>DVP3 <sup>4)</sup> | ST7MDT10-<br>EMU3 | STX-RLINK<br>ST7-STICK <sup>3)5)</sup> | ST7SB10-<br>123 <sup>3)</sup>   |

#### Notes:

- 1. Available from ST or from Raisonance, www.raisonance.com

- 2. USB connection to PC

- 3. Add suffix /EU, /UK or /US for the power supply for your region

- 4. Includes connection kit for DIP16/SO16 only. See "How to order an EMU or DVP" in ST product and tool selection guide for connection kit ordering information

- Parallel port connection to PC