Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                    |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | SPI                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 17                                                                     |

| Program Memory Size        | 2KB (2K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 7x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                         |

| Supplier Device Package    | 20-50                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7flit15bf0m6 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## DATA EEPROM (Cont'd)

#### **5.4 POWER SAVING MODES**

#### Wait mode

The DATA EEPROM can enter WAIT mode on execution of the WFI instruction of the microcontroller or when the microcontroller enters Active-HALT mode. The DATA EEPROM will immediately enter this mode if there is no programming in progress, otherwise the DATA EEPROM will finish the cycle and then enter WAIT mode.

#### Active-Halt mode

Refer to Wait mode.

#### Halt mode

The DATA EEPROM immediately enters HALT mode if the microcontroller executes the HALT instruction. Therefore the EEPROM will stop the function in progress, and data may be corrupted.

#### 5.5 ACCESS ERROR HANDLING

If a read access occurs while E2LAT=1, then the data bus will not be driven.

If a write access occurs while E2LAT=0, then the data on the bus will not be latched.

If a programming cycle is interrupted (by a RESET action), the integrity of the data in memory will not be guaranteed.

#### 5.6 Data EEPROM Read-out Protection

The read-out protection is enabled through an option bit (see option byte section).

When this option is selected, the programs and data stored in the EEPROM memory are protected against read-out (including a re-write protection). In Flash devices, when this protection is removed by reprogramming the Option Byte, the entire Program memory and EEPROM is first automatically erased.

**Note:** Both Program Memory and data EEPROM are protected using the same option bit.

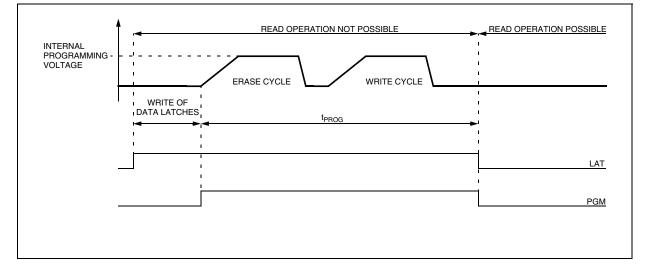

#### Figure 10. Data EEPROM Programming Cycle

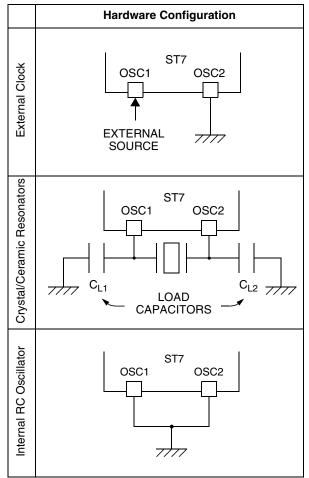

# 7.4 MULTI-OSCILLATOR (MO)

The main clock of the ST7 can be generated by four different source types coming from the multioscillator block (1 to 16MHz):

- an external source

- 5 different configurations for crystal or ceramic resonator oscillators

- an internal high frequency RC oscillator

Each oscillator is optimized for a given frequency range in terms of consumption and is selectable through the option byte. The associated hardware configurations are shown in Table 4. Refer to the electrical characteristics section for more details.

#### External Clock Source

In this external clock mode, a clock signal (square, sinus or triangle) with ~50% duty cycle has to drive the OSC1 pin while the OSC2 pin is tied to ground.

**Note:** when the Multi-Oscillator is not used, PB4 is selected by default as external clock.

#### **Crystal/Ceramic Oscillators**

In this mode, with a self-controlled gain feature, oscillator of any frequency from 1 to 16MHz can be placed on OSC1 and OSC2 pins. This family of oscillators has the advantage of producing a very accurate rate on the main clock of the ST7. In this mode of the multi-oscillator, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. The loading capacitance values must be adjusted according to the selected oscillator.

These oscillators are not stopped during the RESET phase to avoid losing time in the oscillator start-up phase.

#### Internal RC Oscillator

57/

In this mode, the tunable 1%RC oscillator is used as main clock source. The two oscillator pins have to be tied to ground if dedicately using for oscillator else can be found as general purpose IO. The calibration is done through the RCCR[7:0] and SICSR[6:5] registers.

Table 4. ST7 Clock Sources

## SYSTEM INTEGRITY MANAGEMENT (Cont'd)

### 7.6.3 Low Power Modes

| Mode | Description                                                              |

|------|--------------------------------------------------------------------------|

| WAIT | No effect on SI. AVD interrupts cause the device to exit from Wait mode. |

| HALT | The SICSR register is frozen.<br>The AVD remains active.                 |

#### 7.6.3.1 Interrupts

The AVD interrupt event generates an interrupt if the corresponding Enable Control Bit (AVDIE) is set and the interrupt mask in the CC register is reset (RIM instruction).

| Interrupt Event | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|-----------------|---------------|--------------------------|----------------------|----------------------|

| AVD event       | AVDF          | AVDIE                    | Yes                  | No                   |

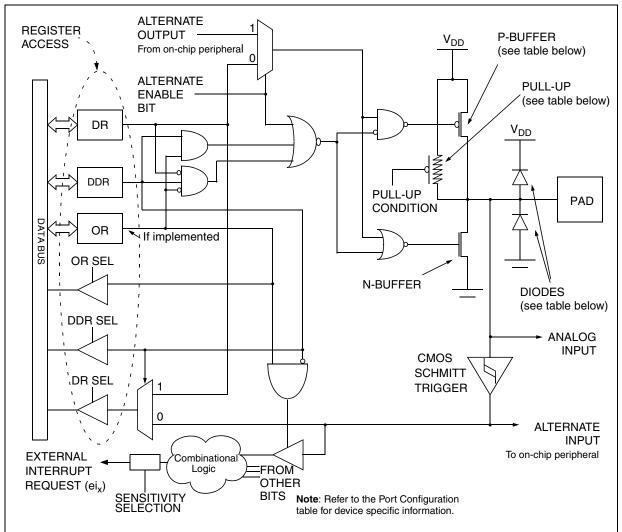

# I/O PORTS (Cont'd)

### Table 8. I/O Port Mode Options

| Configuration Mode                                                      |                          | Configuration Mode Pull-Up |          | Diodes             |                    |

|-------------------------------------------------------------------------|--------------------------|----------------------------|----------|--------------------|--------------------|

|                                                                         |                          | Puil-Op                    | P-Buffer | to V <sub>DD</sub> | to V <sub>SS</sub> |

| Input Floating with/without Interrupt<br>Pull-up with/without Interrupt |                          | Off                        | Off      |                    |                    |

|                                                                         |                          | On                         | OII      | On                 | On                 |

| Output Push-pull                                                        |                          | Off                        | On       | On                 | On                 |

| Output                                                                  | Open Drain (logic level) |                            | Off      |                    |                    |

Legend: Off - implemented not activated On - implemented and activated

## I/O PORTS (Cont'd)

#### **10.7 DEVICE-SPECIFIC I/O PORT CONFIGURATION**

The I/O port register configurations are summarised as follows.

#### **Standard Ports**

#### PA7:0, PB6:0

<u>ل</u>حک

| MODE              | DDR | OR |

|-------------------|-----|----|

| floating input    | 0   | 0  |

| pull-up input     | 0   | 1  |

| open drain output | 1   | 0  |

| push-pull output  | 1   | 1  |

#### PC1:0 (multiplexed with OSC1,OSC2)

| MODE             | DDR |

|------------------|-----|

| floating input   | 0   |

| push-pull output | 1   |

The selection between OSC1 or PC0 and OSC2 or PC1 is done by option byte. Refer to section 15.1 on page 149. Interrupt capability is not available on PC1:0.

**Note:** PCOR not implemented but p-transistor always active in output mode (refer to Figure 32 on page 50)

#### Table 10. Port Configuration (Standard ports)

| Port   | Pin name  | Ing      | out     | Output     |           |  |

|--------|-----------|----------|---------|------------|-----------|--|

| FUIL   | Fininanie | OR = 0   | OR = 1  | OR = 0     | OR = 1    |  |

| Port A | PA7:0     | floating | pull-up | open drain | push-pull |  |

| Port B | PB6:0     | floating | pull-up | open drain | push-pull |  |

**Note:** On ports where the external interrupt capability is selected using the EISR register, the configuration will be as follows:

| Port   | Pin name  | Inj      | out               | Output     |           |  |

|--------|-----------|----------|-------------------|------------|-----------|--|

| FUIT   | Fininanie | OR = 0   | OR = 1            | OR = 0     | OR = 1    |  |

| Port A | PA7:0     | floating | pull-up interrupt | open drain | push-pull |  |

| Port B | PB6:0     | floating | pull-up interrupt | open drain | push-pull |  |

#### Table 11. I/O Port Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|-------------------|-------------------|-----|---|---|---|---|---|---|-----|

| 0000h             | PADR              | MSB |   |   |   |   |   |   | LSB |

|                   | Reset Value       | 1   | 1 | 1 | 1 | 1 | 1 | 1 | 1   |

| 0001h             | PADDR             | MSB |   |   |   |   |   |   | LSB |

| 000111            | Reset Value       | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

#### **Interrupt Ports**

Ports where the external interrupt capability is selected using the EISR register

| MODE                    | DDR | OR |

|-------------------------|-----|----|

| floating input          | 0   | 0  |

| pull-up interrupt input | 0   | 1  |

| open drain output       | 1   | 0  |

| push-pull output        | 1   | 1  |

# WATCHDOG TIMER (Cont'd)

The application program must write in the CR register at regular intervals during normal operation to prevent an MCU reset. This downcounter is freerunning: it counts down even if the watchdog is disabled. The value to be stored in the CR register must be between FFh and C0h (see Table 12 .Watchdog Timing):

- The WDGA bit is set (watchdog enabled)

- The T6 bit is set to prevent generating an immediate reset

- The T[5:0] bits contain the number of increments which represents the time delay before the watchdog produces a reset.

Following a reset, the watchdog is disabled. Once activated it cannot be disabled, except by a reset.

The T6 bit can be used to generate a software reset (the WDGA bit is set and the T6 bit is cleared).

If the watchdog is activated, the HALT instruction will generate a Reset.

#### Table 12.Watchdog Timing

| f <sub>CPU</sub> = 8MHz       |     |     |  |  |  |

|-------------------------------|-----|-----|--|--|--|

| WDGminmaxCounter Code[ms][ms] |     |     |  |  |  |

| C0h                           | 1   | 2   |  |  |  |

| FFh                           | 127 | 128 |  |  |  |

Notes:

1. The timing variation shown in Table 12 is due to the unknown status of the prescaler when writing to the CR register.

2. The number of CPU clock cycles applied during the RESET phase (256 or 4096) must be taken into account in addition to these timings.

#### 11.1.4 Hardware Watchdog Option

If Hardware Watchdog is selected by option byte, the watchdog is always active and the WDGA bit in the CR is not used. Refer to the Option Byte description in section 15 on page 149.

# 11.1.4.1 Using Halt Mode with the WDG (WDGHALT option)

If Halt mode with Watchdog is enabled by option byte (No watchdog reset on HALT instruction), it is recommended before executing the HALT instruction to refresh the WDG counter, to avoid an unexpected WDG reset immediately after waking up the microcontroller. Same behaviour in active-halt mode.

#### 11.1.5 Interrupts

None.

# 11.1.6 Register Description CONTROL REGISTER (WDGCR)

Read/Write

Reset Value: 0111 1111 (7Fh)

| 7    |    |    |    |    |    |    | 0  |

|------|----|----|----|----|----|----|----|

| WDGA | Т6 | T5 | T4 | Т3 | T2 | T1 | то |

#### Bit 7 = **WDGA** *Activation bit.*

This bit is set by software and only cleared by hardware after a reset. When WDGA = 1, the watchdog can generate a reset.

0: Watchdog disabled

1: Watchdog enabled

**Note:** This bit is not used if the hardware watchdog option is enabled by option byte.

#### Bit 6:0 = **T[6:0]** 7-bit timer (MSB to LSB).

These bits contain the decremented value. A reset is produced when it rolls over from 40h to 3Fh (T6 becomes cleared).

#### Table 13. Watchdog Timer Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label | 7    | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------------------|-------------------|------|----|----|----|----|----|----|----|

| 002Eh             | WDGCR             | WDGA | T6 | T5 | T4 | T3 | T2 | T1 | T0 |

|                   | Reset Value       | 0    | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

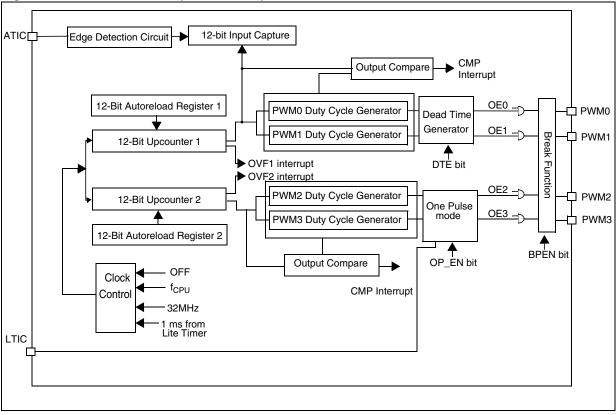

# DUAL 12-BIT AUTORELOAD TIMER 4 (Cont'd)

#### DUAL 12-BIT AUTORELOAD TIMER 4 (Cont'd)

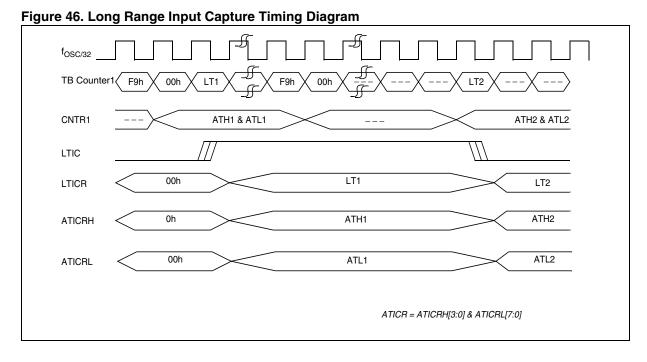

At the second input capture on the falling edge of the pulse, we assume that the values in the registers are as follows:

LTICR = LT2 ATICRH = ATH2 ATICRL = ATL2

Hence ATICR2 [11:0] = ATH2 & ATL2

Now pulse width P between first capture and second capture will be:

$\label{eq:P} \begin{array}{l} \mathsf{P} = \text{decimal} \left(\mathsf{FFF} * \mathsf{N}\right) + \mathsf{N} + \mathsf{ATICR2} + 1\right) * 0.004 \text{ms} + \text{dec-}\\ \text{imal} \left((\mathsf{FFF} * \mathsf{N}) + \mathsf{N} + \mathsf{ATICR2} - \mathsf{ATICR1} - 1\right) * 1 \text{ms}\\ \text{where } \mathsf{N} = \mathsf{No} \text{ of overflows of 12-bit CNTR1.} \end{array}$

#### DUAL 12-BIT AUTORELOAD TIMER 4 (Cont'd)

#### 11.2.3.6 One Pulse Mode

One Pulse Mode can be used to control PWM2/3 signal with an external LTIC pin. This mode is available only in dual timer mode i.e. only for CNTR2, when the OP\_EN bit in PWM3CSR register is set.

One Pulse Mode is activated by the external LTIC input. The active edge of the LTIC pin is selected by the OPEDGE bit in the PWM3CSR register.

After getting the active edge of the LTIC pin, CNTR2 is reset (000h) and PWM3 is set to high. CNTR2 starts counting from 000h, when it reaches the active DCR3 value then the PWM3 output goes low. Till this time, any further transitions on the LTIC signal will have no effect. If there are LTIC transitions after CNTR2 reaches the DCR3 value, CNTR2 is reset again and the PWM3 output goes high.

If there is no LTIC active edge then CNTR2 will count till it reaches the ATR2 value, and then it will be reset again and the PWM3 output is set to high. The counter again starts counting from 000h, when it reaches the active DCR3 value the PWM3 output goes low, the counter counts till it reaches the ATR2 value, it resets and the PWM3 output is set to high and it goes on the same way.

The same operation applies for the PWM2 output, but in this case the comparison is done on the DCR2 value.

The OP\_EN and OPEDGE bits take effect on the fly and are not synchronized with the CNTR2 over-flow.

The OP2/3 bits can be used to inverse the polarity of the PWM2/3 outputs in one-pulse mode. The update of these bits (OP2/3) is synchronized with the CNTR2 overflow, they will be updated if the TRAN2 bit is set.

#### Notes:

1. If CNTR2 is running at 32 MHz, the time taken from activation of LTIC input and CNTR2 reset is between 2 and 3  $t_{CNTR2}$  cycles, i.e. 66 ns to 99 ns (with 8 MHz  $f_{cpu}$ ).

2. The Lite Timer input capture interrupt must be disabled while 12-bit ARTimer is in One Pulse Mode. This is to avoid spurious interrupts.

3. The priority of various events affecting PWM3 is as follows:

- Break (Highest priority)

- One-pulse mode with active LTIC edge

- Forced overflow (by FORCE2 bit)

- One-pulse mode without active LTIC edge

- Normal PWM operation. (Lowest priority)

4. It is possible to synchronize the update of DCR2/3 registers and OP2/3 bits with the CNTR2 reset. This is managed by the overflow interrupt which is generated if CNTR2 is reset either due to an ATR match or an active pulse on the LTIC pin.

5. Updating the DCR2/3 registers and OP2/3 bits in one-pulse mode is done dynamically by software using force update (FORCE2 bit in the ATCSR2 register).

6. DCR3 update in this mode is not synchronized with any event. Consequently the next PWM3 cycle just after the change may be longer than expected (refer to Figure 15).

7. In One Pulse Mode the ATR2 value must be greater than the DCR2/3 value for the PWM2/3 outputs. (contrary to normal PWM mode)

8. If there is an active edge on the LTIC pin after the CNTR2 has reset due to an ATR2 match, then the timer gets reset again. The duty cycle may be modified depending on whether the new DCR value is less than or more than the previous value.

9. The TRAN2 bit must be set simultaneously with the FORCE2 bit in the same instruction after a write to the DCR register.

10. The ATR2 value should be changed after an overflow in one pulse mode to avoid an irregular PWM cycle.

11. When exiting from one pulse mode, the OP\_EN bit in the PWM3CSR register must be reset first and then the ENCNTR2 bit (if CNTR2 is to be stopped).

#### How to Enter One Pulse Mode:

1. Load the ATR2H/ATR2L registers with required value.

2. Load the DCR3H/DCR3L registers for PWM3 output. The ATR2 value must be greater than DCR3.

3. Set the OP3 bit in the PWM3CSR register if polarity change is required.

4. Start the CNTR2 counter by setting the ENCNTR2 bit in the ATCSR2 register.

5. Set TRAN2 bit in ATCSR2 to enable transfer.

6. Wait for an overflow event by polling the OVF2 flag in the ATCSR2 register.

7. Select the counter clock using the CK[1:0] bits in the ATCSR register.

LITE TIMER (Cont'd)

Bit 6 = **ICF** *Input Capture Flag* This bit is set by hardware and cleared by software by reading the LTICR register. Writing to this bit does not change the bit value. 0: No input capture 1: An input capture has occurred

**Note:** After an MCU reset, software must initialize the ICF bit by reading the LTICR register

Bit 5 = **TB** *Timebase period selection* This bit is set and cleared by software. 0: Timebase period =  $t_{OSC} * 8000 (1ms @ 8 MHz)$ 1: Timebase period =  $t_{OSC} * 16000 (2ms @ 8 MHz)$

Bit 4 = **TB1IE** *Timebase Interrupt enable* This bit is set and cleared by software. 0: Timebase (TB1) interrupt disabled 1: Timebase (TB1) interrupt enabled

Bit 3 =**TB1F** *Timebase Interrupt Flag* This bit is set by hardware and cleared by software reading the LTCSR register. Writing to this bit has no effect.

0: No counter overflow

1: A counter overflow has occurred

Bits 2:0 = Reserved

#### LITE TIMER INPUT CAPTURE REGISTER (LTICR) Read only

Reset Value: 0000 0000 (00h)

7

| ICR7 | ICR6 | ICR5 | ICR4 | ICR3 | ICR2 | ICR1 | ICR0 |

|------|------|------|------|------|------|------|------|

0

#### Bits 7:0 = ICR[7:0] Input Capture Value

These bits are read by software and cleared by hardware after a reset. If the ICF bit in the LTCSR is cleared, the value of the 8-bit up-counter will be captured when a rising or falling edge occurs on the LTIC pin.

# SERIAL PERIPHERAL INTERFACE (cont'd)

SPI CONTROL/STATUS REGISTER (SPICSR)

Read/Write (some bits Read Only) Reset Value: 0000 0000 (00h)

| 7    |      |     |      |   |     |     | 0   |

|------|------|-----|------|---|-----|-----|-----|

| SPIF | WCOL | OVR | MODF | - | SOD | SSM | SSI |

Bit 7 = **SPIF** Serial Peripheral Data Transfer Flag (Read only)

This bit is set by hardware when a transfer has been completed. An interrupt is generated if SPIE = 1 in the SPICR register. It is cleared by a software sequence (an access to the SPICSR register followed by a write or a read to the SPIDR register).

- 0: Data transfer is in progress or the flag has been cleared.

- 1: Data transfer between the device and an external device has been completed.

**Note:** While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

#### Bit 6 = **WCOL** Write Collision status (Read only)

This bit is set by hardware when a write to the SPIDR register is done during a transmit sequence. It is cleared by a software sequence (see Figure 6).

0: No write collision occurred

1: A write collision has been detected

#### Bit 5 = **OVR** SPI Overrun error (Read only)

This bit is set by hardware when the byte currently being received in the shift register is ready to be transferred into the SPIDR register while SPIF = 1 (See Section 0.1.5.2). An interrupt is generated if SPIE = 1 in the SPICR register. The OVR bit is cleared by software reading the SPICSR register. 0: No overrun error

1: Overrun error detected

#### Bit 4 = MODF Mode Fault flag (Read only)

This bit is set by hardware when the  $\overline{SS}$  pin is pulled low in master mode (see Section 0.1.5.1 Master Mode Fault (MODF)). An SPI interrupt can be generated if SPIE = 1 in the SPICR register. This bit is cleared by a software sequence (An access to the SPICSR register while MODF = 1 followed by a write to the SPICR register).

0: No master mode fault detected

1: A fault in master mode has been detected

Bit 3 = Reserved, must be kept cleared.

#### Bit 2 = SOD SPI Output Disable

This bit is set and cleared by software. When set, it disables the alternate function of the SPI output (MOSI in master mode / MISO in slave mode) 0: SPI output enabled (if SPE = 1) 1: SPI output disabled

#### Bit 1 = **SSM** *SS Management*

This bit is set and cleared by software. When set, it disables the alternate function of the SPI SS pin and uses the SSI bit value instead. See Section 0.1.3.2 Slave Select Management.

- 0: Hardware management (SS managed by external pin)

- 1: Software management (internal SS signal controlled by SSI bit. External SS pin free for general-purpose I/O)

#### Bit 0 = SSI SS Internal Mode

This bit is set and cleared by software. It <u>acts</u> as a 'chip select' by controlling the level of the SS slave select signal when the SSM bit is set.

0: Slave selected

1: Slave deselected

# SPI DATA I/O REGISTER (SPIDR)

Read/Write Reset Value: Undefined

| 7  |    |    |    |    |    |    | 0  |

|----|----|----|----|----|----|----|----|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

The SPIDR register is used to transmit and receive data on the serial bus. In a master device, a write to this register will initiate transmission/reception of another byte.

**Notes:** During the last clock cycle the SPIF bit is set, a copy of the received data byte in the shift register is moved to a buffer. When the user reads the serial peripheral data I/O register, the buffer is actually being read.

While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

**Warning:** A write to the SPIDR register places data directly into the shift register for transmission.

A read to the SPIDR register returns the value located in the buffer and not the content of the shift register (see Figure 1).

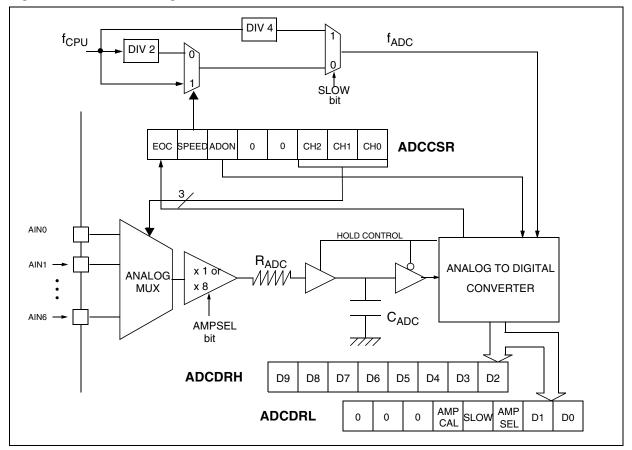

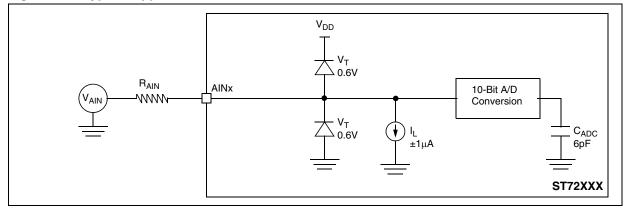

### 11.5 10-BIT A/D CONVERTER (ADC)

#### 11.5.1 Introduction

The on-chip Analog to Digital Converter (ADC) peripheral is a 10-bit, successive approximation converter with internal sample and hold circuitry. This peripheral has up to 7 multiplexed analog input channels (refer to device pin out description) that allow the peripheral to convert the analog voltage levels from up to 7 different sources.

The result of the conversion is stored in a 10-bit Data Register. The A/D converter is controlled through a Control/Status Register.

## 11.5.2 Main Features

- 10-bit conversion

- Up to 7 channels with multiplexed input

- Linear successive approximation

#### Figure 60. ADC Block Diagram

- Data register (DR) which contains the results

- Conversion complete status flag

- On/off bit (to reduce consumption)

The block diagram is shown in Figure 60.

#### **11.5.3 Functional Description**

#### 11.5.3.1 Analog Power Supply

$V_{DDA}$  and  $V_{SSA}$  are the high and low level reference voltage pins. In some devices (refer to device pin out description) they are internally connected to the  $V_{DD}$  and  $V_{SS}$  pins.

Conversion accuracy may therefore be impacted by voltage drops and noise in the event of heavily loaded or badly decoupled power supply lines.

47/

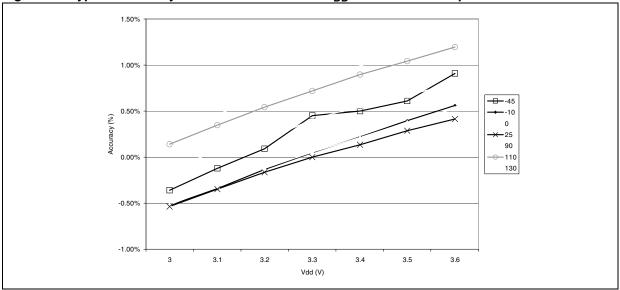

# **OPERATING CONDITIONS** (Cont'd)

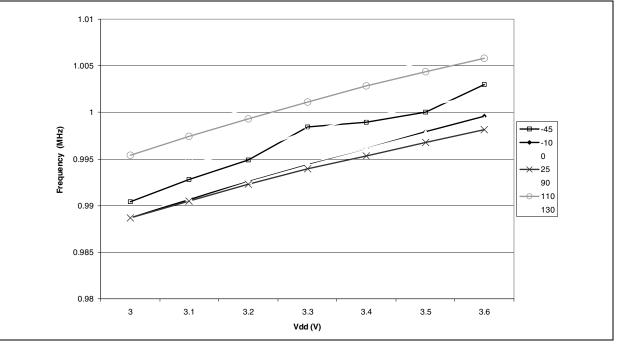

# Figure 68. Typical accuracy with RCCR=RCCR1 vs V<sub>DD</sub>= 3-3.6V and Temperature

# Figure 69. Typical RCCR1 vs $V_{\text{DD}}$ and Temperature

57

# **OPERATING CONDITIONS** (Cont'd)

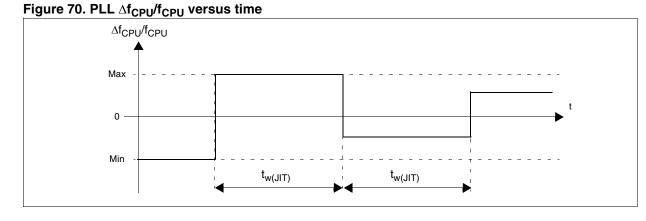

#### 13.3.5.3 32MHz PLL

$T_A$  = -40 to 125°C, unless otherwise specified

| Symbol             | Parameter               | Min | Тур | Max | Unit |

|--------------------|-------------------------|-----|-----|-----|------|

| V <sub>DD</sub>    | Voltage <sup>1)</sup>   | 4.5 | 5   | 5.5 | V    |

| f <sub>PLL32</sub> | Frequency <sup>1)</sup> |     | 32  |     | MHz  |

| f <sub>INPUT</sub> | Input Frequency         | 7   | 8   | 9   | MHz  |

#### Note:

**\$7**

**1.** 32 MHz is guaranteed within this voltage range.

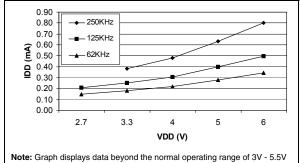

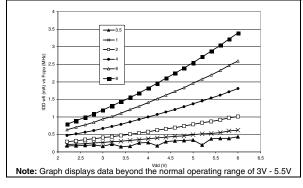

## Figure 73. Typical I<sub>DD</sub> in SLOW vs. f<sub>CPU</sub>

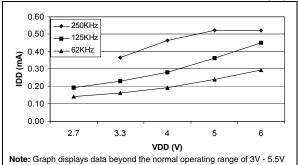

#### Figure 74. Typical I<sub>DD</sub> in WAIT vs. f<sub>CPU</sub>

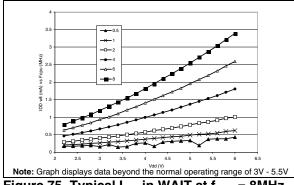

Figure 75. Typical I<sub>DD</sub> in WAIT at f<sub>CPU</sub>= 8MHz

Figure 76. Typical I<sub>DD</sub> in SLOW-WAIT vs. f<sub>CPU</sub>

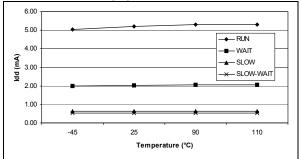

# Figure 77. Typical $I_{DD}$ vs. Temperature at $V_{DD}$ = 5V and $f_{CPU}$ = 8MHz

# **13.8 I/O PORT PIN CHARACTERISTICS**

#### **13.8.1 General Characteristics**

Subject to general operating conditions for  $V_{DD}$ ,  $f_{OSC}$ , and  $T_A$  unless otherwise specified.

| Symbol                | Parameter                                                                        |                                    | Conditions                                 | Min                   | Тур                 | Max                   | Unit             |

|-----------------------|----------------------------------------------------------------------------------|------------------------------------|--------------------------------------------|-----------------------|---------------------|-----------------------|------------------|

| V <sub>IL</sub>       | Input low level voltage                                                          |                                    |                                            | V <sub>SS</sub> - 0.3 | 0.3xV <sub>DD</sub> | V                     |                  |

| V <sub>IH</sub>       | Input high level voltage                                                         |                                    |                                            | 0.7xV <sub>DD</sub>   |                     | V <sub>DD</sub> + 0.3 | v                |

| V <sub>hys</sub>      | Schmitt trigger voltage                                                          |                                    |                                            |                       | 400                 |                       | mV               |

| ΙL                    | Input leakage current                                                            | V <sub>SS</sub> ≤V <sub>IN</sub> ≤ | ≤V <sub>DD</sub>                           |                       |                     | ±1                    |                  |

| ۱ <sub>S</sub>        | Static current consumption in-<br>duced by each floating input pin <sup>2)</sup> |                                    | nput mode                                  |                       | 400                 |                       | μA               |

| D                     | Weak pull-up equivalent                                                          | V _V                               | V <sub>DD</sub> =5V<br>V <sub>DD</sub> =3V | 50                    | 120                 | 250                   | kΩ               |

| R <sub>PU</sub>       | resistor <sup>3)</sup>                                                           | VIN-VSS                            | V <sub>DD</sub> =3V                        |                       | 160                 |                       | K52              |

| C <sub>IO</sub>       | I/O pin capacitance                                                              |                                    |                                            |                       | 5                   |                       | pF               |

| t <sub>f(IO)out</sub> | Output high to low level fall time <sup>1)</sup>                                 | C <sub>L</sub> =50pF               |                                            |                       | 25                  |                       | 20               |

| t <sub>r(IO)out</sub> | Output low to high level rise time <sup>1)</sup>                                 | Between                            | 10% and 90%                                |                       | 25                  |                       | ns               |

| t <sub>w(IT)in</sub>  | External interrupt pulse time 4)                                                 |                                    |                                            | 1                     |                     |                       | t <sub>CPU</sub> |

#### Notes:

1. Data based on validation/design results.

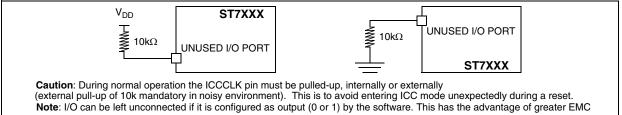

**2.** Configuration not recommended, all unused pins must be kept at a fixed voltage: using the output mode of the I/O for example or an external pull-up or pull-down resistor (see Figure 80). Static peak current value taken at a fixed  $V_{IN}$  value, based on design simulation and technology characteristics, not tested in production. This value depends on  $V_{DD}$  and temperature values.

3. The R<sub>PU</sub> pull-up equivalent resistor is based on a resistive transistor.

4. To generate an external interrupt, a minimum pulse width has to be applied on an I/O port pin configured as an external interrupt source.

#### Figure 80. Two typical Applications with unused I/O Pin

robustness and lower cost.

# 13.11 10-BIT ADC CHARACTERISTICS

Subject to general operating condition for V<sub>DD</sub>, f<sub>OSC</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol            | Parameter                                                                       | Conditions                                     | Min              | <b>Typ</b> <sup>1)</sup> | Max                | Unit |

|-------------------|---------------------------------------------------------------------------------|------------------------------------------------|------------------|--------------------------|--------------------|------|

| f <sub>ADC</sub>  | ADC clock frequency                                                             |                                                |                  |                          | 4                  | MHz  |

| V <sub>AIN</sub>  | Conversion voltage range <sup>2)</sup>                                          |                                                | V <sub>SSA</sub> |                          | V <sub>DDA</sub>   | V    |

| R <sub>AIN</sub>  | External input resistor                                                         |                                                |                  |                          | 10 <sup>3)</sup>   | kΩ   |

| C <sub>ADC</sub>  | Internal sample and hold capacitor                                              |                                                |                  | 6                        |                    | pF   |

| t <sub>STAB</sub> | Stabilization time after ADC enable                                             |                                                |                  | 0 4)                     |                    |      |

|                   | Conversion time (Sample+Hold)                                                   | f <sub>CPU</sub> =8MHz, f <sub>ADC</sub> =4MHz | 3.5              |                          |                    | μs   |

| t <sub>ADC</sub>  | <ul> <li>Sample capacitor loading time</li> <li>Hold conversion time</li> </ul> |                                                | 4<br>10          |                          | 1/f <sub>ADC</sub> |      |

| 1                 | Analog Part                                                                     |                                                |                  | 1                        |                    | mA   |

| IADC              | Digital Part                                                                    |                                                |                  | 0.2                      |                    | INA  |

#### Figure 110. Typical Application with ADC

#### Notes:

47/

1. Unless otherwise specified, typical data are based on  $T_A=25^{\circ}C$  and  $V_{DD}-V_{SS}=5V$ . They are given only as design guide-lines and are not tested.

2. When  $V_{DDA}$  and  $V_{SSA}$  pins are not available on the pinout, the ADC refers to  $V_{DD}$  and  $V_{SS}$ .

3. Any added external serial resistor will downgrade the ADC accuracy (especially for resistance greater than  $10k\Omega$ ). Data based on characterization results, not tested in production.

4. The stabilization time of the AD converter is masked by the first  $t_{LOAD}$ . The first conversion after the enable is then always valid.

#### **Related application notes:**

Understanding and minimizing ADC conversion errors (AN1636) Software techniques for compensating ST7 ADC errors (AN1711)

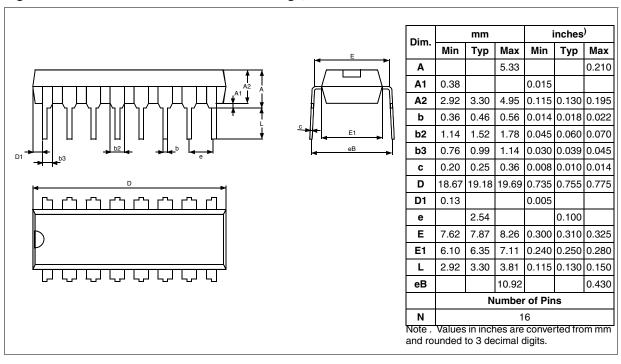

# **14 PACKAGE CHARACTERISTICS**

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a Lead-free second level interconnect. The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard

JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label.

ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com.

### 14.1 PACKAGE MECHANICAL DATA

#### Figure 113. 16-Pin Plastic Dual In-Line Package, 300-mil Width

#### **14.2 SOLDERING INFORMATION**

In accordance with the RoHS European directive, all STMicroelectronics packages have been converted to lead-free technology, named ECO-PACK<sup>TM</sup>.

- ECOPACK<sup>TM</sup> packages are qualified according to the JEDEC STD-020C compliant soldering profile.

- Detailed information on the STMicroelectronics ECOPACK<sup>TM</sup> transition program is available on www.st.com/stonline/leadfree/, with specific technical Application notes covering the main technical aspects related to lead-free conversion (AN2033, AN2034, AN2035, AN2036).

#### Backward and forward compatibility:

The main difference between Pb and Pb-free soldering process is the temperature range.

- ECOPACK<sup>TM</sup> TQFP, SDIP, SO and QFN20 packages are fully compatible with Lead (Pb) containing soldering process (see application note AN2034)

- TQFP, SDIP and SO Pb-packages are compatible with Lead-free soldering process, nevertheless it's the customer's duty to verify that the Pb-packages maximum temperature (mentioned on the Inner box label) is compatible with their Lead-free soldering temperature.

#### Table 25. Soldering Compatibility (wave and reflow soldering process)

| Package     | Plating material devices       | Pb solder paste | Pb-free solder paste |

|-------------|--------------------------------|-----------------|----------------------|

| SDIP & PDIP | Sn (pure Tin)                  | Yes             | Yes *                |

| QFN         | Sn (pure Tin)                  | Yes             | Yes *                |

| TQFP and SO | NiPdAu (Nickel-palladium-Gold) | Yes             | Yes *                |

\* Assemblers must verify that the Pb-package maximum temperature (mentioned on the Inner box label) is compatible with their Lead-free soldering process.

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com