Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | SPI                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 17                                                                     |

| Program Memory Size        | 4KB (4K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 7x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7flit15bf1b6 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

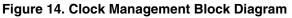

## 7.3 REGISTER DESCRIPTION

#### MAIN CLOCK CONTROL/STATUS REGISTER (MCCSR)

Read / Write

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |     | 0   |

|---|---|---|---|---|---|-----|-----|

| 0 | 0 | 0 | 0 | 0 | 0 | мсо | SMS |

Bits 7:2 = Reserved, must be kept cleared.

#### Bit 1 = MCO Main Clock Out enable

This bit is read/write by software and cleared by hardware after a reset. This bit allows to enable the MCO output clock.

- 0: MCO clock disabled, I/O port free for general purpose I/O.

- 1: MCO clock enabled.

#### Bit 0 = SMS Slow Mode select

This bit is read/write by software and cleared by hardware after a reset. This bit selects the input clock  $f_{OSC}$  or  $f_{OSC}/32$ .

0: Normal mode ( $f_{CPU} = f_{OSC}$

1: Slow mode ( $f_{CPU} = f_{OSC}/32$ )

5/

#### **RC CONTROL REGISTER (RCCR)**

Read / Write

Reset Value: 1111 1111 (FFh)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| CR9 | CR8 | CR7 | CR6 | CR5 | CR4 | CR3 | CR2 |

Bits 7:0 = **CR[9:2]** *RC* Oscillator Frequency Adjustment Bits

These bits must be written immediately after reset to adjust the RC oscillator frequency and to obtain an accuracy of 1%. The application can store the correct value for each voltage range in EEPROM and write it to this register at start-up.

00h = maximum available frequency

FFh = lowest available frequency

These bits are used with the CR[1:0] bits in the SICSR register. Refer to section 7.6.4 on page 35.

**Note:** To tune the oscillator, write a series of different values in the register until the correct frequency is reached. The fastest method is to use a dichotomy starting with 80h.

**لرکا**

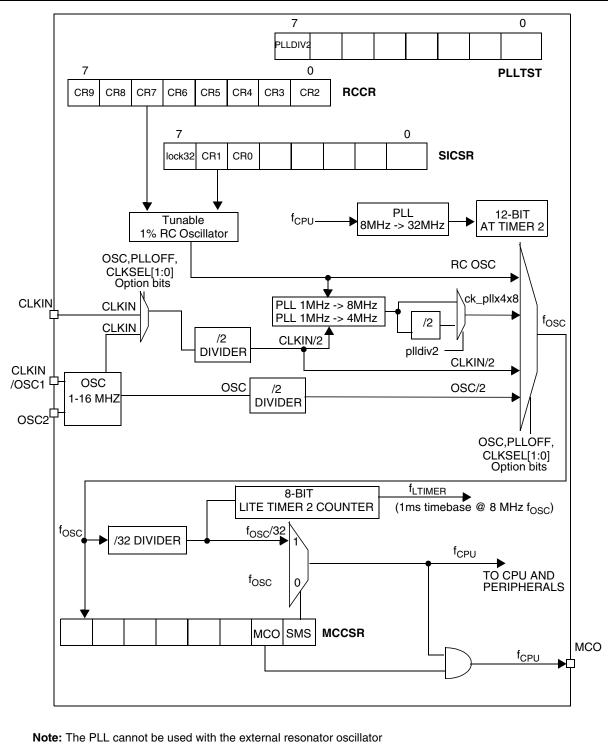

#### Figure 16. Reset Block Diagram

57

## SYSTEM INTEGRITY MANAGEMENT (Cont'd)

## 7.6.4 Register Description

## SYSTEM INTEGRITY (SI) CONTROL/STATUS REGISTER (SICSR)

#### Read/Write

Reset Value: 0110 0xx0 (6xh)

| 7          |     |     |           |        |       |      | 0     |

|------------|-----|-----|-----------|--------|-------|------|-------|

| LOCK<br>32 | CR1 | CR0 | WDG<br>RF | LOCKED | LVDRF | AVDF | AVDIE |

## Bit 7 = LOCK32 PLL 32Mhz Locked Flag

This bit is set and cleared by hardware. It is set automatically when the PLL 32Mhz reaches its operating frequency

- 0: PLL32 not locked

- 1: PLL32 locked

Bits 6:5 = **CR[1:0]** *RC* Oscillator Frequency Adjustment bits

These bits, as well as CR[9:2] bits in the RCCR register must be written immediately after reset to adjust the RC oscillator frequency and to obtain an accuracy of 1%. Refer to section 7.3 on page 25.

#### Bit 4 = WDGRF Watchdog Reset flag

This bit indicates that the last Reset was generated by the Watchdog peripheral. It is set by hardware (watchdog reset) and cleared by software (reading the SICSR register or writing 0 to this bit) or by an LVD Reset (to ensure a stable cleared state of the WDGRF flag when the CPU starts). Combined with the LVDRF flag information, the flag description is given by the following table.

| RESET Sources      | LVDRF | WDGRF |

|--------------------|-------|-------|

| External RESET pin | 0     | 0     |

| Watchdog           | 0     | 1     |

| LVD                | 1     | Х     |

#### Bit 3 = LOCKED PLL Locked Flag

This bit is set and cleared by hardware. It is set automatically when the PLL reaches its operating frequency.

0: PLL not locked

1: PLL locked

#### Bit 2 = LVDRF LVD reset flag

This bit indicates that the last Reset was generated by the LVD block. It is set by hardware (LVD reset) and cleared by software (by reading). When the LVD is disabled by OPTION BYTE, the LVDRF bit value is undefined.

#### Bit 1 = **AVDF** Voltage Detector Flag

This read-only bit is set and cleared by hardware. If the AVDIE bit is set, an interrupt request is generated when the AVDF bit is set. Refer to Figure 20 and to Section 7.6.2.1 for additional details.

0: V<sub>DD</sub> over AVD threshold

1: V<sub>DD</sub> under AVD threshold

#### Bit 0 = **AVDIE** Voltage Detector Interrupt Enable

This bit is set and cleared by software. It enables an interrupt to be generated when the AVDF flag is set. The pending interrupt information is automatically cleared when software enters the AVD interrupt routine.

0: AVD interrupt disabled

1: AVD interrupt enabled

#### **Application notes**

The LVDRF flag is not cleared when another RE-SET type occurs (external or watchdog), the LVDRF flag remains set to keep trace of the original failure.

In this case, a watchdog reset can be detected by software while an external reset can not.

#### PLL TEST REGISTER (PLLTST)

Read/Write

Reset Value: 0000 0000 (00h)

| 7       |   |   |   |   |   |   | 0 |

|---------|---|---|---|---|---|---|---|

| PLLdiv2 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### Bit 7 : PLLdiv2 PLL clock divide by 2

This bit is read or write by software and cleared by hardware after reset. This bit will divide the PLL output clock by 2.

0 : PLL output clock

1 : Divide by 2 of PLL output clock

Refer "Clock Management Block Diagram" on page 26

**Note :** Write of this bit will be effective after 2 Tcpu cycles (if system clock is 8mhz) else 1 cycle (if system clock is 4mhz) i.e. effective time is 250ns.

Bit 6:0 : Reserved , Must always be cleared

#### POWER SAVING MODES (Cont'd)

#### Similarities with Halt mode

The following AWUFH mode behaviour is the same as normal Halt mode:

- The MCU can exit AWUFH mode by means of any interrupt with exit from Halt capability or a reset (see Section 9.4 HALT MODE).

- When entering AWUFH mode, the I bit in the CC register is forced to 0 to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes up immediately.

- In AWUFH mode, the main oscillator is turned off causing all internal processing to be stopped, including the operation of the on-chip peripherals. None of the peripherals are clocked except those which get their clock supply from another clock generator (such as an external or auxiliary oscillator like the AWU oscillator).

- The compatibility of Watchdog operation with AWUFH mode is configured by the WDGHALT option bit in the option byte. Depending on this setting, the HALT instruction when executed while the Watchdog system is enabled, can generate a Watchdog RESET.

#### Figure 30. AWUF Halt Timing Diagram

57/

|                     |           | •    | t <sub>AWU</sub> | ▶                            |                      |

|---------------------|-----------|------|------------------|------------------------------|----------------------|

|                     | RUN MODE  | HALT | MODE             | 256 OR 4096 t <sub>CPU</sub> | RUN MODE             |

| f <sub>CPU</sub>    |           |      |                  |                              |                      |

| f <sub>AWU_RC</sub> | :         |      |                  |                              |                      |

| AWUFH               | interrupt |      |                  |                              | Clear<br>by software |

## 11.2 DUAL 12-BIT AUTORELOAD TIMER 4 (AT4)

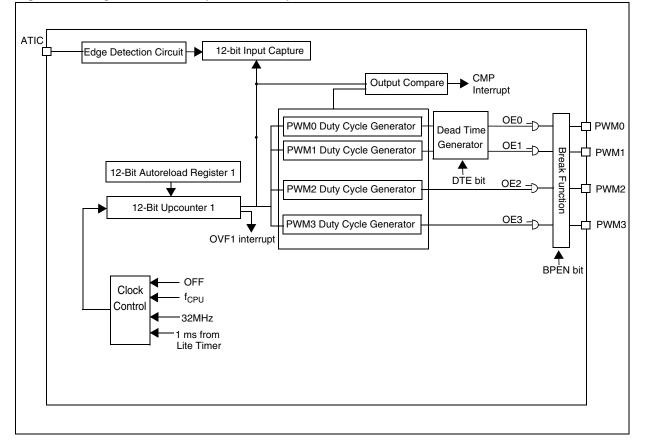

## 11.2.1 Introduction

The 12-bit Autoreload Timer can be used for general-purpose timing functions. It is based on one or two free-running 12-bit upcounters with an input capture register and four PWM output channels. There are 7 external pins:

- Four PWM outputs

- ATIC/LTIC pins for the Input Capture function

- BREAK pin for forcing a break condition on the PWM outputs

#### 11.2.2 Main Features

- Single Timer or Dual Timer mode with two 12-bit upcounters (CNTR1/CNTR2) and two 12-bit autoreload registers (ATR1/ATR2)

- Maskable overflow interrupts

- PWM mode

47/

## Figure 35. Single Timer Mode (ENCNTR2=0)

- Generation of four independent PWMx signals

- Dead time generation for Half bridge driving mode with programmable dead time

- Frequency 2 kHz 4 MHz (@ 8 MHz f<sub>CPU</sub>)

- Programmable duty-cycles

- Polarity control

- Programmable output modes

- Output Compare Mode

- Input Capture Mode

- 12-bit input capture register (ATICR)

- Triggered by rising and falling edges

- Maskable IC interrupt

- Long range input capture

- Internal/External Break control

- Flexible Clock control

- One Pulse mode on PWM2/3

- Force Update

## DUAL 12-BIT AUTORELOAD TIMER 4 (Cont'd)

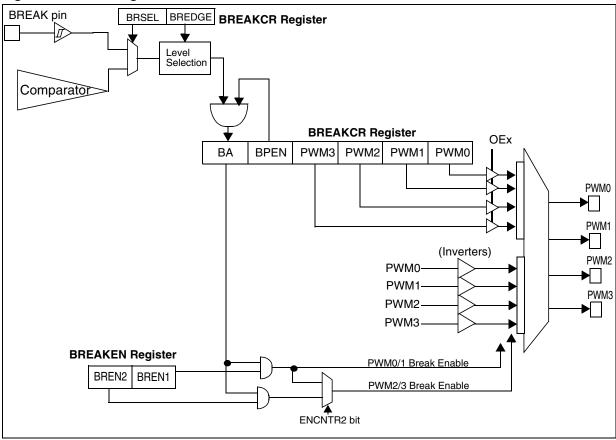

#### 11.2.3.3 Break Function

The break function can be used to perform an emergency shutdown of the application being driven by the PWM signals.

The break function is activated by the external BREAK pin or internal comparator output. This can be selected by using the BRSEL bit in BREAKCR Register. In order to use the break function it must be previously enabled by software setting the BPEN bit in the BREAKCR register.

The Break active level can be programmed by the BREDGE bit in the BREAKCR register. When an active level is detected on the BREAK pin, the BA bit is set and the break function is activated. In this case, the PWM signals are forced to BREAK value if respective OEx bit is set in PWMCR register.

Software can set the BA bit to activate the break function without using the BREAK pin. The BREN1 and BREN2 bits in the BREAKEN Register are used to enable the break activation on the 2 counters respectively. In Dual Timer Mode, the break for PWM2 and PWM3 is enabled by the BREN2 bit. In Single Timer Mode, the BREN1 bit enables the break for all PWM channels.

When a break function is activated (BA bit =1 and BREN1/BREN2 =1):

- The break pattern (PWM[3:0] bits in the BREAK-CR) is forced directly on the PWMx output pins if respective OEx is set. (after the inverter).

- The 12-bit PWM counter CNTR1 is put to its reset value, i.e. 00h (if BREN1 = 1).

- The 12-bit PWM counter CNTR2 is put to its reset value, i.e. 00h (if BREN2 = 1).

- ATR1, ATR2, Preload and Active DCRx are put to their reset values.

- Counters stop counting.

When the break function is deactivated after applying the break (BA bit goes from 1 to 0 by software), Timer takes the control of PWM ports.

## Figure 41. Block Diagram of Break Function

## DUAL 12-BIT AUTORELOAD TIMER 4 (Cont'd)

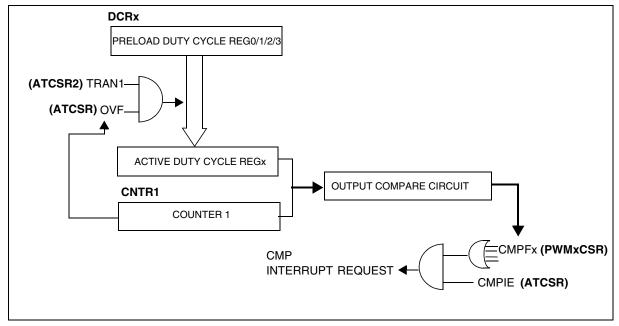

## 11.2.3.4 Output Compare Mode

5/

To use this function, load a 12-bit value in the Preload DCRxH and DCRxL registers.

When the 12-bit upcounter CNTR1 reaches the value stored in the Active DCRxH and DCRxL registers, the CMPFx bit in the PWMxCSR register is set and an interrupt request is generated if the CMPIE bit is set.

In single Timer mode the output compare function is performed only on CNTR1. The difference between both the modes is that, in Single Timer mode, CNTR1 can be compared with any of the four DCR registers, and in Dual Timer mode, CNTR1 is compared with DCR0 or DCR1 and CNTR2 is compared with DCR2 or DCR3.

#### Notes:

**1.** The output compare function is only available for DCRx values other than 0 (reset value).

**2.** Duty cycle registers are buffered internally. The CPU writes in Preload Duty Cycle Registers and these values are transferred in Active Duty Cycle Registers after an overflow event if the corresponding transfer bit (TRANx bit) is set. Output compare is done by comparing these active DCRx values with the counters.

## DUAL 12-BIT AUTORELOAD TIMER 4 (Cont'd)

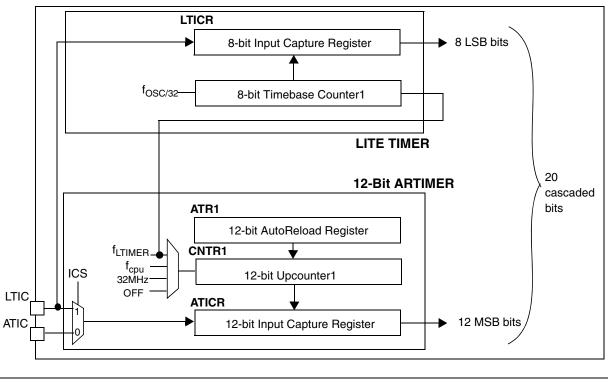

## Long Input Capture

Pulses that last more than  $8\mu s$  can be measured with an accuracy of  $4\mu s$  if  $f_{OSC} = 8$  MHz in the following conditions:

- The 12-bit AT4 Timer is clocked by the Lite Timer (RTC pulse: CK[1:0] = 01 in the ATCSR register)

- The ICS bit in the ATCSR2 register is set so that the LTIC pin is used to trigger the AT4 Timer capture.

Figure 45. Long Range Input Capture Block Diagram

- The signal to be captured is connected to LTIC pin

- Input Capture registers LTICR, ATICRH and ATICRL are read

This configuration allows to cascade the Lite Timer and the 12-bit AT4 Timer to get a 20-bit input capture value. Refer to Figure 11.

#### Notes:

**1.** Since the input capture flags (ICF) for both timers (AT4 Timer and LT Timer) are set when signal transition occurs, software must mask one interrupt by clearing the corresponding ICIE bit before setting the ICS bit.

**2.** If the ICS bit changes (from 0 to 1 or from 1 to 0), a spurious transition might occur on the input capture signal because of different values on LTIC and ATIC. To avoid this situation, it is recommended to do as follows:

- First, reset both ICIE bits.

- Then set the ICS bit.

- Reset both ICF bits.

- And then set the ICIE bit of desired interrupt.

**3**. How to compute a pulse length with long input capture feature.

As both timers are used, computing a pulse length is not straight-forward. The procedure is as follows:

At the first input capture on the rising edge of the pulse, we assume that values in the registers are as follows:

LTICR = LT1 ATICRH = ATH1 ATICRL = ATL1 Hence ATICR1 [11:0] = ATH1 & ATL1

Refer to Figure 12.

## SERIAL PERIPHERAL INTERFACE (cont'd)

#### 11.4.5 Error Flags

#### 11.4.5.1 Master Mode Fault (MODF)

Master mode fault occurs when the master device's SS pin is pulled low.

When a Master mode fault occurs:

- The MODF bit is set and an SPI interrupt request is generated if the SPIE bit is set.

- The SPE bit is reset. This blocks all output from the device and disables the SPI peripheral.

- The MSTR bit is reset, thus forcing the device into slave mode.

Clearing the MODF bit is done through a software sequence:

1. A read access to the SPICSR register while the MODF bit is set.

2. A write to the SPICR register.

**Notes:** To avoid any conflicts in an application with multiple slaves, the SS pin must be pulled high during the MODF bit clearing sequence. The SPE and MSTR bits may be restored to their original state during or after this clearing sequence.

Hardware does not allow the user to set the SPE and MSTR bits while the MODF bit is set except in the MODF bit clearing sequence.

In a slave device, the MODF bit can not be set, but in a multimaster configuration the device can be in slave mode with the MODF bit set.

The MODF bit indicates that there might have been a multimaster conflict and allows software to handle this using an interrupt routine and either perform a reset or return to an application default state.

## 11.4.5.2 Overrun Condition (OVR)

An overrun condition occurs when the master device has sent a data byte and the slave device has not cleared the SPIF bit issued from the previously transmitted byte.

When an Overrun occurs:

- The OVR bit is set and an interrupt request is generated if the SPIE bit is set.

In this case, the receiver buffer contains the byte sent after the SPIF bit was last cleared. A read to the SPIDR register returns this byte. All other bytes are lost.

The OVR bit is cleared by reading the SPICSR register.

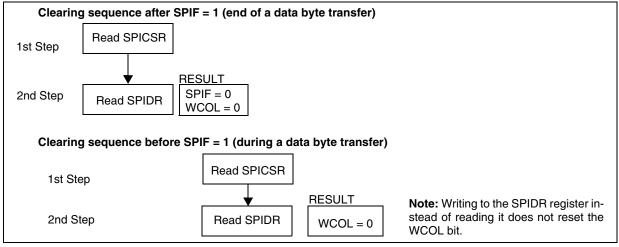

#### 11.4.5.3 Write Collision Error (WCOL)

A write collision occurs when the software tries to write to the SPIDR register while a data transfer is taking place with an external device. When this happens, the transfer continues uninterrupted and the software write will be unsuccessful.

Write collisions can occur both in master and slave mode. See also Section 0.1.3.2 Slave Select Management.

**Note:** A "read collision" will never occur since the received data byte is placed in a buffer in which access is always synchronous with the CPU operation.

The WCOL bit in the SPICSR register is set if a write collision occurs.

No SPI interrupt is generated when the WCOL bit is set (the WCOL bit is a status flag only).

Clearing the WCOL bit is done through a software sequence (see Figure 6).

#### Figure 58. Clearing the WCOL Bit (Write Collision Flag) Software Sequence

## SERIAL PERIPHERAL INTERFACE (cont'd)

SPI CONTROL/STATUS REGISTER (SPICSR)

Read/Write (some bits Read Only) Reset Value: 0000 0000 (00h)

| 7    |      |     |      |   |     |     | 0   |

|------|------|-----|------|---|-----|-----|-----|

| SPIF | WCOL | OVR | MODF | - | SOD | SSM | SSI |

Bit 7 = **SPIF** Serial Peripheral Data Transfer Flag (Read only)

This bit is set by hardware when a transfer has been completed. An interrupt is generated if SPIE = 1 in the SPICR register. It is cleared by a software sequence (an access to the SPICSR register followed by a write or a read to the SPIDR register).

- 0: Data transfer is in progress or the flag has been cleared.

- 1: Data transfer between the device and an external device has been completed.

**Note:** While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

#### Bit 6 = **WCOL** Write Collision status (Read only)

This bit is set by hardware when a write to the SPIDR register is done during a transmit sequence. It is cleared by a software sequence (see Figure 6).

0: No write collision occurred

1: A write collision has been detected

#### Bit 5 = **OVR** SPI Overrun error (Read only)

This bit is set by hardware when the byte currently being received in the shift register is ready to be transferred into the SPIDR register while SPIF = 1 (See Section 0.1.5.2). An interrupt is generated if SPIE = 1 in the SPICR register. The OVR bit is cleared by software reading the SPICSR register. 0: No overrun error

1: Overrun error detected

## Bit 4 = **MODF** Mode Fault flag (Read only)

This bit is set by hardware when the  $\overline{SS}$  pin is pulled low in master mode (see Section 0.1.5.1 Master Mode Fault (MODF)). An SPI interrupt can be generated if SPIE = 1 in the SPICR register. This bit is cleared by a software sequence (An access to the SPICSR register while MODF = 1 followed by a write to the SPICR register).

0: No master mode fault detected

1: A fault in master mode has been detected

Bit 3 = Reserved, must be kept cleared.

#### Bit 2 = SOD SPI Output Disable

This bit is set and cleared by software. When set, it disables the alternate function of the SPI output (MOSI in master mode / MISO in slave mode) 0: SPI output enabled (if SPE = 1) 1: SPI output disabled

#### Bit 1 = **SSM** *SS Management*

This bit is set and cleared by software. When set, it disables the alternate function of the SPI SS pin and uses the SSI bit value instead. See Section 0.1.3.2 Slave Select Management.

- 0: Hardware management (SS managed by external pin)

- 1: Software management (internal SS signal controlled by SSI bit. External SS pin free for general-purpose I/O)

#### Bit 0 = SSI SS Internal Mode

This bit is set and cleared by software. It <u>acts</u> as a 'chip select' by controlling the level of the SS slave select signal when the SSM bit is set.

0: Slave selected

1: Slave deselected

## SPI DATA I/O REGISTER (SPIDR)

Read/Write Reset Value: Undefined

| 7  |    |    |    |    |    |    | 0  |

|----|----|----|----|----|----|----|----|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

The SPIDR register is used to transmit and receive data on the serial bus. In a master device, a write to this register will initiate transmission/reception of another byte.

**Notes:** During the last clock cycle the SPIF bit is set, a copy of the received data byte in the shift register is moved to a buffer. When the user reads the serial peripheral data I/O register, the buffer is actually being read.

While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

**Warning:** A write to the SPIDR register places data directly into the shift register for transmission.

A read to the SPIDR register returns the value located in the buffer and not the content of the shift register (see Figure 1).

## INSTRUCTION GROUPS (cont'd)

| Mnemo | Description                | Function/Example    | Dst    | Src | Н | I | Ν | Z | С |

|-------|----------------------------|---------------------|--------|-----|---|---|---|---|---|

| ADC   | Add with Carry             | A = A + M + C       | А      | М   | Н |   | Ν | Z | С |

| ADD   | Addition                   | A=A+M               | А      | М   | Н |   | Ν | Z | С |

| AND   | Logical And                | A = A . M           | А      | М   |   |   | Ν | Z |   |

| BCP   | Bit compare A, Memory      | tst (A . M)         | А      | М   |   |   | Ν | Z |   |

| BRES  | Bit Reset                  | bres Byte, #3       | М      |     |   |   |   |   |   |

| BSET  | Bit Set                    | bset Byte, #3       | М      |     |   |   |   |   |   |

| BTJF  | Jump if bit is false (0)   | btjf Byte, #3, Jmp1 | М      |     |   |   |   |   | С |

| BTJT  | Jump if bit is true (1)    | btjt Byte, #3, Jmp1 | М      |     |   |   |   |   | С |

| CALL  | Call subroutine            |                     |        |     |   |   |   |   |   |

| CALLR | Call subroutine relative   |                     |        |     |   |   |   |   |   |

| CLR   | Clear                      |                     | reg, M |     |   |   | 0 | 1 |   |

| CP    | Arithmetic Compare         | tst(Reg - M)        | reg    | М   |   |   | Ν | Z | С |

| CPL   | One Complement             | A = FFH-A           | reg, M |     |   |   | Ν | Z | 1 |

| DEC   | Decrement                  | dec Y               | reg, M |     |   |   | Ν | Z |   |

| HALT  | Halt                       |                     |        |     |   | 0 |   |   |   |

| IRET  | Interrupt routine return   | Pop CC, A, X, PC    |        |     | Н | I | Ν | Z | С |

| INC   | Increment                  | inc X               | reg, M |     |   |   | Ν | Z |   |

| JP    | Absolute Jump              | jp [TBL.w]          |        |     |   |   |   |   |   |

| JRA   | Jump relative always       |                     |        |     |   |   |   |   |   |

| JRT   | Jump relative              |                     |        |     |   |   |   |   |   |

| JRF   | Never jump                 | jrf *               |        |     |   |   |   |   |   |

| JRIH  | Jump if ext. interrupt = 1 |                     |        |     |   |   |   |   |   |

| JRIL  | Jump if ext. interrupt = 0 |                     |        |     |   |   |   |   |   |

| JRH   | Jump if H = 1              | H = 1 ?             |        |     |   |   |   |   |   |

| JRNH  | Jump if H = 0              | H = 0 ?             |        |     |   |   |   |   |   |

| JRM   | Jump if I = 1              | I = 1 ?             |        |     |   |   |   |   |   |

| JRNM  | Jump if I = 0              | I = 0 ?             |        |     |   |   |   |   |   |

| JRMI  | Jump if N = 1 (minus)      | N = 1 ?             |        |     |   |   |   |   |   |

| JRPL  | Jump if N = 0 (plus)       | N = 0 ?             |        |     |   |   |   |   |   |

| JREQ  | Jump if Z = 1 (equal)      | Z = 1 ?             |        |     |   |   |   |   |   |

| JRNE  | Jump if Z = 0 (not equal)  | Z = 0 ?             |        |     |   |   |   |   |   |

| JRC   | Jump if C = 1              | C = 1 ?             |        |     |   |   |   |   |   |

| JRNC  | Jump if C = 0              | C = 0 ?             |        |     |   |   |   |   |   |

| JRULT | Jump if C = 1              | Unsigned <          |        |     |   |   |   |   |   |

| JRUGE | Jump if C = 0              | Jmp if unsigned >=  |        |     |   |   |   |   |   |

| JRUGT | Jump if $(C + Z = 0)$      | Unsigned >          |        |     |   |   |   |   |   |

## INSTRUCTION GROUPS (cont'd)

57

| Mnemo | Description            | Function/Example    | Dst     | Src     | н | I | Ν | z | С |

|-------|------------------------|---------------------|---------|---------|---|---|---|---|---|

| JRULE | Jump if $(C + Z = 1)$  | Unsigned <=         |         |         |   |   |   |   |   |

| LD    | Load                   | dst <= src          | reg, M  | M, reg  |   |   | Ν | Z |   |

| MUL   | Multiply               | X,A = X * A         | A, X, Y | X, Y, A | 0 |   |   |   | 0 |

| NEG   | Negate (2's compl)     | neg \$10            | reg, M  |         |   |   | Ν | Z | С |

| NOP   | No Operation           |                     |         |         |   |   |   |   |   |

| OR    | OR operation           | A = A + M           | А       | М       |   |   | Ν | Z |   |

| POP   | Pop from the Stack     | pop reg             | reg     | М       |   |   |   |   |   |

|       |                        | pop CC              | сс      | М       | Н | I | Ν | Z | С |

| PUSH  | Push onto the Stack    | push Y              | М       | reg, CC |   |   |   |   |   |

| RCF   | Reset carry flag       | C = 0               |         |         |   |   |   |   | 0 |

| RET   | Subroutine Return      |                     |         |         |   |   |   |   |   |

| RIM   | Enable Interrupts      | I = 0               |         |         |   | 0 |   |   |   |

| RLC   | Rotate left true C     | C <= Dst <= C       | reg, M  |         |   |   | Ν | Z | С |

| RRC   | Rotate right true C    | C => Dst => C       | reg, M  |         |   |   | Ν | Z | С |

| RSP   | Reset Stack Pointer    | S = Max allowed     |         |         |   |   |   |   |   |

| SBC   | Subtract with Carry    | A = A - M - C       | А       | М       |   |   | Ν | Z | С |

| SCF   | Set carry flag         | C = 1               |         |         |   |   |   |   | 1 |

| SIM   | Disable Interrupts     | l = 1               |         |         |   | 1 |   |   |   |

| SLA   | Shift left Arithmetic  | C <= Dst <= 0       | reg, M  |         |   |   | Ν | Z | С |

| SLL   | Shift left Logic       | C <= Dst <= 0       | reg, M  |         |   |   | Ν | Z | С |

| SRL   | Shift right Logic      | 0 => Dst => C       | reg, M  |         |   |   | 0 | Z | С |

| SRA   | Shift right Arithmetic | Dst7 => Dst => C    | reg, M  |         |   |   | Ν | Z | С |

| SUB   | Subtraction            | A = A - M           | А       | М       |   |   | Ν | Z | С |

| SWAP  | SWAP nibbles           | Dst[74] <=> Dst[30] | reg, M  |         |   |   | Ν | Z |   |

| TNZ   | Test for Neg & Zero    | tnz lbl1            |         |         |   |   | Ν | Z |   |

| TRAP  | S/W trap               | S/W interrupt       |         |         |   | 1 |   | 1 |   |

| WFI   | Wait for Interrupt     |                     |         |         |   | 0 |   |   |   |

| XOR   | Exclusive OR           | A = A XOR M         | A       | М       |   |   | Ν | Z |   |

|       |                        |                     |         |         |   |   |   |   |   |

#### 13.4.2 On-chip peripherals

| Symbol               | Parameter                                             | Сог                    | nditions              | Тур  | Unit |

|----------------------|-------------------------------------------------------|------------------------|-----------------------|------|------|

| I                    | 12-bit Auto-Reload Timer supply current <sup>1)</sup> | f <sub>CPU</sub> =4MHz | V <sub>DD</sub> =3.0V | 150  |      |

| 'DD(AT)              | IDD(AT) 12-bit Auto-Reload Timer supply current '/    | f <sub>CPU</sub> =8MHz | V <sub>DD</sub> =5.0V | 1000 |      |

| 1                    | SPI supply current <sup>2)</sup>                      | f <sub>CPU</sub> =4MHz | V <sub>DD</sub> =3.0V | 50   | μA   |

| DD(SPI)              | SPT supply current -                                  | f <sub>CPU</sub> =8MHz | V <sub>DD</sub> =5.0V | 200  | μΑ   |

| I <sub>DD(ADC)</sub> | ADC supply current when converting <sup>3)</sup>      | f <sub>ADC</sub> =4MHz | V <sub>DD</sub> =3.0V | 250  |      |

|                      | Abo supply current when converting                    | ADC-4WI12              | V <sub>DD</sub> =5.0V | 1100 |      |

#### Notes:

<u>ل</u>جک

1. Data based on a differential  $I_{DD}$  measurement between reset configuration (timer stopped) and a timer running in PWM mode at  $f_{cpu}$ =8MHz.

**2.** Data based on a differential  $I_{DD}$  measurement between reset configuration and a permanent SPI master communication (data sent equal to 55h).

3. Data based on a differential  $I_{DD}$  measurement between reset configuration and continuous A/D conversions with amplifier disabled.

## CLOCK AND TIMING CHARACTERISTICS (Cont'd)

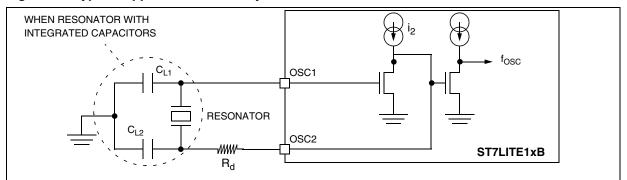

## 13.5.4 Crystal and Ceramic Resonator Oscillators

The ST7 internal clock can be supplied with ten different Crystal/Ceramic resonator oscillators. All the information given in this paragraph are based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal/ceramic resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol                             | Parameter                                                                                                                      | Conditions | Min             | Тур | Max | Unit |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------|-----------------|-----|-----|------|

| f <sub>CrOSC</sub>                 | Crystal Oscillator Frequency                                                                                                   |            | 2 16            |     |     | MHz  |

| C <sub>L1</sub><br>C <sub>L2</sub> | Recommended load capacitance ver-<br>sus equivalent serial resistance of the<br>crystal or ceramic resonator (R <sub>S</sub> ) |            | See table below |     |     | pF   |

| Supplier | f <sub>CrOSC</sub> | Typical Ceramic Resonators <sup>1)</sup> |                  | CL1 <sup>3)</sup> | CL2 <sup>3)</sup>  | Rd   | Supply Voltage | Temperature |  |

|----------|--------------------|------------------------------------------|------------------|-------------------|--------------------|------|----------------|-------------|--|

| Supplier | (MHz)              | Type <sup>2)</sup>                       | Reference        | [pF]              | [pF] [Ω] Range [V] |      | Range [V]      | Range [°C]  |  |

|          | 1                  |                                          | CSBFB1M00J58-R0  | 220               | 220                | 2.2k | 3.3V to 5.5V   |             |  |

|          | I                  | LEAD                                     | CSBLA1M00J58-B0  | 220               | 220                | 2.2k | 3.30 10 5.50   |             |  |

|          | 2                  | SMD                                      | CSTCC2M00G56Z-R0 | (47)              | (47)               | 0    |                |             |  |

| Murata   | 4                  | SMD                                      | CSTCR4M00G53Z-R0 | (15)              | (15)               | 0    | 3.0V to 5.5V   | -40 to 85   |  |

|          |                    | LEAD                                     | CSTLS4M00G53Z-B0 | (15)              | (15)               | 0    | 3.00 10 3.30   |             |  |

| Mur      | 8                  | SMD                                      | CSTCE8M00G52Z-R0 | (10)              | (10)               | 0    |                |             |  |

| _        | 0                  | LEAD                                     | CSTLS8M00G53Z-B0 | (15)              | (15)               | 0    |                |             |  |

|          | 12                 | SMD                                      | CSTCE12M0G52Z-R0 | (10)              | (10)               | 0    |                |             |  |

|          | 16                 | SMD                                      | CSTCE16M0V51Z-R0 | (5)               | (5)                | 0    | 3.3V to 5.5V   |             |  |

|          | 10                 | LEAD                                     | CSTLS16M0X51Z-B0 | (5)               | (5)                | 0    |                |             |  |

#### Notes:

57

1. Resonator characteristics given by the ceramic resonator manufacturer. For more information on these resonators, please consult www.murata.com

2. SMD = [-R0: Plastic tape package (Ø =180mm)]

LEAD = [-B0: Bulk]

3. () means load capacitor built in resonator

#### Figure 79. Typical Application with a Crystal or Ceramic Resonator

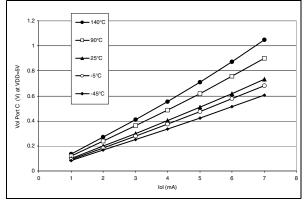

## I/O PORT PIN CHARACTERISTICS (Cont'd)

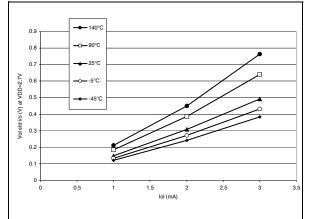

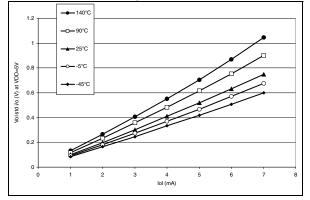

## Figure 81. Typical $V_{OL}$ at $V_{DD}$ =2.7V (standard)

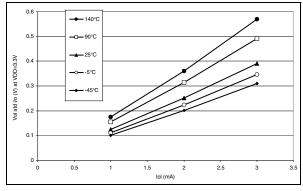

## Figure 82. Typical V<sub>OL</sub> at V<sub>DD</sub>=3.3V (standard)

## Figure 83. Typical $V_{OL}$ at $V_{DD}$ =5V (standard)

57

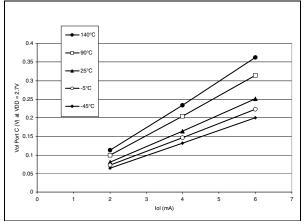

Figure 84. Typical V<sub>OL</sub> at V<sub>DD</sub>=2.7V (Port C)

Figure 85. Typical V<sub>OL</sub> at V<sub>DD</sub>=3.3V (Port C)

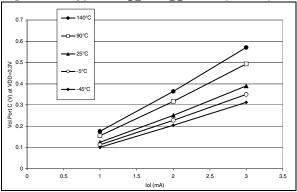

## Figure 86. Typical V<sub>OL</sub> at V<sub>DD</sub>=5V (Port C)

## PACKAGE CHARACTERISTICS (Cont'd)

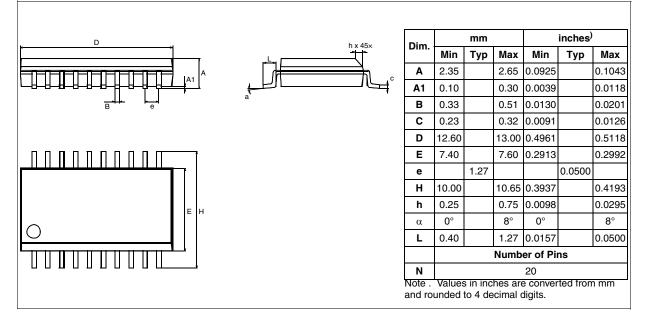

#### Figure 116. 20-Pin Plastic Small Outline Package, 300-mil Width

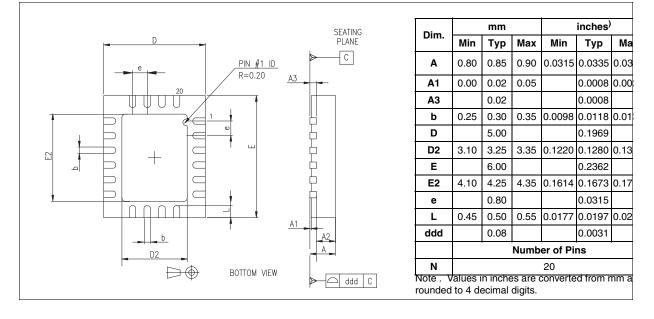

## Figure 117. 20-Lead Very thin Fine pitch Quad Flat No-Lead Package

## **15.3 DEVELOPMENT TOOLS**

Development tools for the ST7 microcontrollers include a complete range of hardware systems and software tools from STMicroelectronics and thirdparty tool suppliers. The range of tools includes solutions to help you evaluate microcontroller peripherals, develop and debug your application, and program your microcontrollers.

#### 15.3.1 Starter kits

ST offers complete, affordable **starter kits**. Starter kits are complete hardware/software tool packages that include features and samples to help you quickly start developing your application.

#### 15.3.2 Development and debugging tools

Application development for ST7 is supported by fully optimizing **C Compilers** and the **ST7 Assembler-Linker** toolchain, which are all seamlessly integrated in the ST7 integrated development environments in order to facilitate the debugging and fine-tuning of your application. The Cosmic C Compiler is available in a free version that outputs up to 16KBytes of code.

The range of hardware tools includes full-featured **ST7-EMU3 series emulators**, cost effective **ST7-DVP3 series emulators** and the low-cost **RLink** in-circuit debugger/programmer. These tools are supported by the **ST7 Toolset** from STMicroelectronics, which includes the STVD7 integrated development environment (IDE) with high-level lan-

guage debugger, editor, project manager and integrated programming interface.

#### 15.3.3 Programming tools

During the development cycle, the **ST7-DVP3** and and **ST7-EMU3 series emulators** and the **RLink** provide in-circuit programming capability for programming the Flash microcontroller on your application board.

ST also provides a low-cost dedicated in-circuit programmer, the **ST7-STICK**, as well as **ST7 Socket Boards** which provide all the sockets required for programming any of the devices in a specific ST7 sub-family on a platform that can be used with any tool with in-circuit programming capability for ST7.

For production programming of ST7 devices, ST's third-party tool partners also provide a complete range of gang and automated programming solutions, which are ready to integrate into your production environment.

# 15.3.4 Order Codes for Development and Programming Tools

Table 28 below lists the ordering codes for the ST7LITE1xB development and programming tools. For additional ordering codes for spare parts and accessories, refer to the online product selector at www.st.com/mcu.

#### 15.3.5 Order codes for ST7LITE1xB development tools

#### Table 28. Development tool order codes for the ST7LITE1xB family

| MCU                                          | In-circuit Debugger, RLink Series <sup>1)</sup> |                                    | Emula                           | ator              | Programming Tool                       |                                 |  |

|----------------------------------------------|-------------------------------------------------|------------------------------------|---------------------------------|-------------------|----------------------------------------|---------------------------------|--|

| ST7FLIT1xBF0<br>ST7FLIT1xBF1<br>ST7FLIT1xBY0 | Starter Kit without<br>Demo Board               | Starter Kit with<br>Demo Board     | DVP Series                      | EMU Series        | In-circuit<br>Programmer               | ST Socket<br>Boards and<br>EPBs |  |

| ST7FLIT1xBY1                                 | STX-RLINK <sup>2)</sup>                         | ST7FLITE-<br>SK/RAIS <sup>2)</sup> | ST7MDT10-<br>DVP3 <sup>4)</sup> | ST7MDT10-<br>EMU3 | STX-RLINK<br>ST7-STICK <sup>3)5)</sup> | ST7SB10-<br>123 <sup>3)</sup>   |  |

#### Notes:

57/

1. Available from ST or from Raisonance, www.raisonance.com

2. USB connection to PC

3. Add suffix /EU, /UK or /US for the power supply for your region

4. Includes connection kit for DIP16/SO16 only. See "How to order an EMU or DVP" in ST product and tool selection guide for connection kit ordering information

5. Parallel port connection to PC

## **15.4 ST7 APPLICATION NOTES**

## Table 29. ST7 Application Notes

| IDENTIFICATION   | DESCRIPTION                                                                                 |

|------------------|---------------------------------------------------------------------------------------------|

| APPLICATION E    | XAMPLES                                                                                     |

| AN1658           | SERIAL NUMBERING IMPLEMENTATION                                                             |

| AN1720           | MANAGING THE READ-OUT PROTECTION IN FLASH MICROCONTROLLERS                                  |

| AN1755           | A HIGH RESOLUTION/PRECISION THERMOMETER USING ST7 AND NE555                                 |

| AN1756           | CHOOSING A DALI IMPLEMENTATION STRATEGY WITH ST7DALI                                        |

| AN1812           | A HIGH PRECISION, LOW COST, SINGLE SUPPLY ADC FOR POSITIVE AND NEGATIVE IN-<br>PUT VOLTAGES |

| EXAMPLE DRIVE    | RS                                                                                          |

| AN 969           | SCI COMMUNICATION BETWEEN ST7 AND PC                                                        |

| AN 970           | SPI COMMUNICATION BETWEEN ST7 AND EEPROM                                                    |

| AN 971           | I <sup>2</sup> C COMMUNICATION BETWEEN ST7 AND M24CXX EEPROM                                |

| AN 972           | ST7 SOFTWARE SPI MASTER COMMUNICATION                                                       |

| AN 973           | SCI SOFTWARE COMMUNICATION WITH A PC USING ST72251 16-BIT TIMER                             |

| AN 974           | REAL TIME CLOCK WITH ST7 TIMER OUTPUT COMPARE                                               |

| AN 976           | DRIVING A BUZZER THROUGH ST7 TIMER PWM FUNCTION                                             |

| AN 979           | DRIVING AN ANALOG KEYBOARD WITH THE ST7 ADC                                                 |

| AN 980           | ST7 KEYPAD DECODING TECHNIQUES, IMPLEMENTING WAKE-UP ON KEYSTROKE                           |

| AN1017           | USING THE ST7 UNIVERSAL SERIAL BUS MICROCONTROLLER                                          |

| AN1041           | USING ST7 PWM SIGNAL TO GENERATE ANALOG OUTPUT (SINUSOÏD)                                   |

| AN1042           | ST7 ROUTINE FOR I <sup>2</sup> C SLAVE MODE MANAGEMENT                                      |

| AN1044           | MULTIPLE INTERRUPT SOURCES MANAGEMENT FOR ST7 MCUS                                          |

| AN1045           | ST7 S/W IMPLEMENTATION OF I <sup>2</sup> C BUS MASTER                                       |

| AN1046           | UART EMULATION SOFTWARE                                                                     |

| AN1047           | MANAGING RECEPTION ERRORS WITH THE ST7 SCI PERIPHERALS                                      |

| AN1048           | ST7 SOFTWARE LCD DRIVER                                                                     |

| AN1078           | PWM DUTY CYCLE SWITCH IMPLEMENTING TRUE 0% & 100% DUTY CYCLE                                |

| AN1082           | DESCRIPTION OF THE ST72141 MOTOR CONTROL PERIPHERALS REGISTERS                              |

| AN1083           | ST72141 BLDC MOTOR CONTROL SOFTWARE AND FLOWCHART EXAMPLE                                   |

| AN1105           | ST7 PCAN PERIPHERAL DRIVER                                                                  |

| AN1129           | PWM MANAGEMENT FOR BLDC MOTOR DRIVES USING THE ST72141                                      |

| ANTIZO           | AN INTRODUCTION TO SENSORLESS BRUSHLESS DC MOTOR DRIVE APPLICATIONS                         |

| AN1130           | WITH THE ST72141                                                                            |

| AN1148           | USING THE ST7263 FOR DESIGNING A USB MOUSE                                                  |

| AN1149           | HANDLING SUSPEND MODE ON A USB MOUSE                                                        |

| AN1180           | USING THE ST7263 KIT TO IMPLEMENT A USB GAME PAD                                            |

| AN1276           | BLDC MOTOR START ROUTINE FOR THE ST72141 MICROCONTROLLER                                    |

| AN1321           | USING THE ST72141 MOTOR CONTROL MCU IN SENSOR MODE                                          |

| AN1325           | USING THE ST7 USB LOW-SPEED FIRMWARE V4.X                                                   |

| AN1445           | EMULATED 16 BIT SLAVE SPI                                                                   |

| AN1475           | DEVELOPING AN ST7265X MASS STORAGE APPLICATION                                              |

| AN1475<br>AN1504 | STARTING A PWM SIGNAL DIRECTLY AT HIGH LEVEL USING THE ST7 16-BIT TIMER                     |

| AN1602           | 16-BIT TIMING OPERATIONS USING ST7262 OR ST7263B ST7 USB MCUS                               |

| AN1633           | DEVICE FIRMWARE UPGRADE (DFU) IMPLEMENTATION IN ST7 NON-USB APPLICATIONS                    |

| AN1712           | GENERATING A HIGH RESOLUTION SINEWAVE USING ST7 PWMART                                      |

|                  | SMBUS SLAVE DRIVER FOR ST7 I2C PERIPHERALS                                                  |

| AN1713           | SMBUS SLAVE DRIVER FOR ST712C PERIPHERALS<br>SOFTWARE UART USING 12-BIT ART                 |

| AN1753           |                                                                                             |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com