Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Obsolete                                                               |

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | SPI                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 11                                                                     |

| Program Memory Size        | 2KB (2K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 5x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                                         |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7flit15by0m3 |

# **Table of Contents**

|      |      | DUCTION                           |    |

|------|------|-----------------------------------|----|

|      |      | SCRIPTION                         |    |

| -    |      | TER & MEMORY MAP                  | _  |

| 4 FI | LASH | PROGRAM MEMORY                    | 12 |

| 4    |      | INTRODUCTION                      |    |

| 4    |      | MAIN FEATURES                     |    |

| 4    |      | PROGRAMMING MODES                 |    |

| 4    |      | ICC INTERFACE                     |    |

| 4    |      | MEMORY PROTECTION                 |    |

| 4    |      | RELATED DOCUMENTATION             |    |

|      |      | REGISTER DESCRIPTION              |    |

|      |      | EEPROM                            |    |

|      |      | INTRODUCTION                      |    |

|      |      | MAIN FEATURES                     |    |

|      |      | MEMORY ACCESS                     |    |

|      |      | POWER SAVING MODES                |    |

|      |      | ACCESS ERROR HANDLING             |    |

|      |      | DATA EEPROM READ-OUT PROTECTION   |    |

|      |      | REGISTER DESCRIPTION              |    |

|      |      | RAL PROCESSING UNIT               |    |

|      |      | INTRODUCTION                      |    |

|      |      | MAIN FEATURES                     |    |

|      |      | CPU REGISTERS                     |    |

| 7 SI |      | Y, RESET AND CLOCK MANAGEMENT     |    |

| 7    |      | INTERNAL RC OSCILLATOR ADJUSTMENT |    |

|      |      | PHASE LOCKED LOOP                 |    |

|      |      | REGISTER DESCRIPTION              |    |

|      |      | MULTI-OSCILLATOR (MO)             |    |

|      |      | RESET SEQUENCE MANAGER (RSM)      |    |

|      |      | SYSTEM INTEGRITY MANAGEMENT (SI)  |    |

| 8 IN |      | RUPTS                             |    |

| 8    |      | NON MASKABLE SOFTWARE INTERRUPT   |    |

| 8    |      | EXTERNAL INTERRUPTS               |    |

|      |      | PERIPHERAL INTERRUPTS             |    |

|      |      | R SAVING MODES                    |    |

|      |      | INTRODUCTION                      |    |

| 9    | _    | SLOW MODE                         | _  |

| 9    |      | WAIT MODE                         |    |

| 9    |      | HALT MODE                         |    |

|      |      | ACTIVE-HALT MODE                  |    |

| -    |      | AUTO WAKE UP FROM HALT MODE       |    |

|      |      | DRTS                              |    |

|      |      | INTRODUCTION                      |    |

|      |      | FUNCTIONAL DESCRIPTION            |    |

| 1    | 10.3 | I/O PORT IMPLEMENTATION           | 52 |

# **Table of Contents**

|    | 10.4  | UNUSED I/O PINS                                                                   | . 52 |

|----|-------|-----------------------------------------------------------------------------------|------|

|    | 10.5  | LOW POWER MODES                                                                   | . 52 |

|    |       | INTERRUPTS                                                                        |      |

|    | 10.7  | DEVICE-SPECIFIC I/O PORT CONFIGURATION                                            | . 53 |

|    | 10.8  | MULTIPLEXED INPUT/OUTPUT PORTS                                                    | . 54 |

| 11 |       | HIP PERIPHERALS                                                                   |      |

|    | 11.1  | WATCHDOG TIMER (WDG)                                                              | . 55 |

|    | 11.2  | DUAL 12-BIT AUTORELOAD TIMER 4 (AT4)                                              | . 57 |

|    |       | LITE TIMER 2 (LT2)                                                                |      |

|    | 11.4  | SERIAL PERIPHERAL INTERFACE (SPI)                                                 | . 84 |

|    |       | 10-BIT A/D CONVERTER (ADC)                                                        |      |

|    | 11.6  | ANALOG COMPARATOR (CMP)                                                           | 100  |

| 12 | INSTF | RUCTION SET                                                                       | 104  |

|    |       | ST7 ADDRESSING MODES                                                              |      |

|    |       | INSTRUCTION GROUPS                                                                |      |

| 13 |       | TRICAL CHARACTERISTICS                                                            |      |

|    |       | PARAMETER CONDITIONS                                                              |      |

|    | 13.2  | ABSOLUTE MAXIMUM RATINGS                                                          | 111  |

|    |       | OPERATING CONDITIONS                                                              |      |

|    | 13.4  | SUPPLY CURRENT CHARACTERISTICS                                                    |      |

|    | 13.5  | CLOCK AND TIMING CHARACTERISTICS                                                  |      |

|    | 13.6  | MEMORY CHARACTERISTICS                                                            |      |

|    |       | EMC CHARACTERISTICS                                                               |      |

|    |       | I/O PORT PIN CHARACTERISTICS                                                      |      |

|    | 13.9  | CONTROL PIN CHARACTERISTICS                                                       | 135  |

|    |       | COMMUNICATION INTERFACE CHARACTERISTICS                                           |      |

|    | 13.11 | 10-BIT ADC CHARACTERISTICS                                                        | 139  |

|    |       | ANALOG COMPARATOR CHARACTERISTICS                                                 |      |

|    |       | PROGRAMMABLE INTERNAL VOLTAGE REFERENCE CHARACTERISTICS                           |      |

|    | 13.14 | CURRENT BIAS CHARACTERISTICS (FOR COMPARATOR AND INTERNAL VOLTA<br>REFERENCE) 143 | ΙGΕ  |

| 14 |       | (AGE CHARACTERISTICS                                                              | 144  |

|    |       | PACKAGE MECHANICAL DATA                                                           |      |

|    |       | SOLDERING INFORMATION                                                             |      |

| 15 |       | CE CONFIGURATION AND ORDERING INFORMATION                                         |      |

| 13 |       | OPTION BYTES                                                                      |      |

|    |       | DEVICE ORDERING INFORMATION                                                       |      |

|    |       | DEVELOPMENT TOOLS                                                                 |      |

|    |       | ST7 APPLICATION NOTES                                                             |      |

| 16 | _     |                                                                                   | 154  |

|    |       |                                                                                   |      |

## PIN DESCRIPTION (Cont'd)

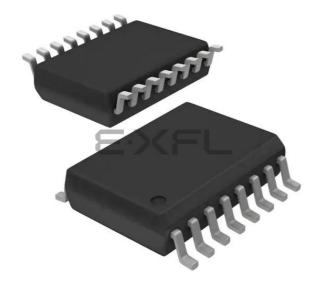

Figure 4. 16-Pin SO and DIP Package Pinout

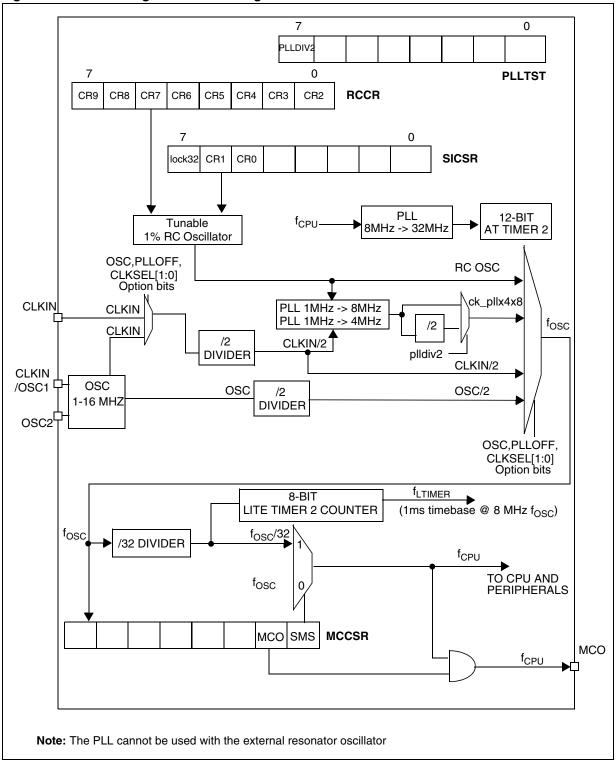

#### 7.3 REGISTER DESCRIPTION

# MAIN CLOCK CONTROL/STATUS REGISTER (MCCSR)

Read / Write

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |     | 0   |

|---|---|---|---|---|---|-----|-----|

| 0 | 0 | 0 | 0 | 0 | 0 | мсо | SMS |

Bits 7:2 = Reserved, must be kept cleared.

## Bit 1 = MCO Main Clock Out enable

This bit is read/write by software and cleared by hardware after a reset. This bit allows to enable the MCO output clock.

0: MCO clock disabled, I/O port free for general purpose I/O.

1: MCO clock enabled.

#### Bit 0 = **SMS** Slow Mode select

This bit is read/write by software and cleared by hardware after a reset. This bit selects the input clock  $f_{OSC}$  or  $f_{OSC}/32$ .

0: Normal mode (f<sub>CPU</sub> = f<sub>OSC</sub>

1: Slow mode ( $f_{CPU} = f_{OSC}/32$ )

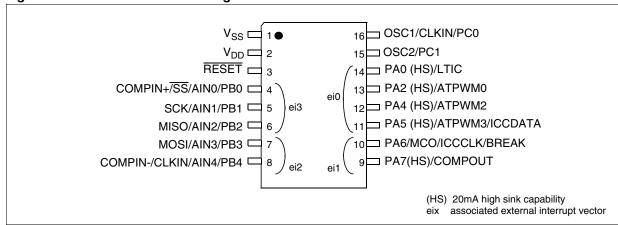

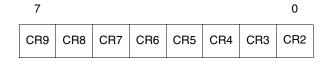

## RC CONTROL REGISTER (RCCR)

Read / Write

Reset Value: 1111 1111 (FFh)

# Bits 7:0 = **CR[9:2]** RC Oscillator Frequency Adjustment Bits

These bits must be written immediately after reset to adjust the RC oscillator frequency and to obtain an accuracy of 1%. The application can store the correct value for each voltage range in EEPROM and write it to this register at start-up.

00h = maximum available frequency

FFh = lowest available frequency

These bits are used with the CR[1:0] bits in the SICSR register. Refer to section 7.6.4 on page 35.

**Note:** To tune the oscillator, write a series of different values in the register until the correct frequency is reached. The fastest method is to use a dichotomy starting with 80h.

Figure 14. Clock Management Block Diagram

# 7.5 RESET SEQUENCE MANAGER (RSM)

#### 7.5.1 Introduction

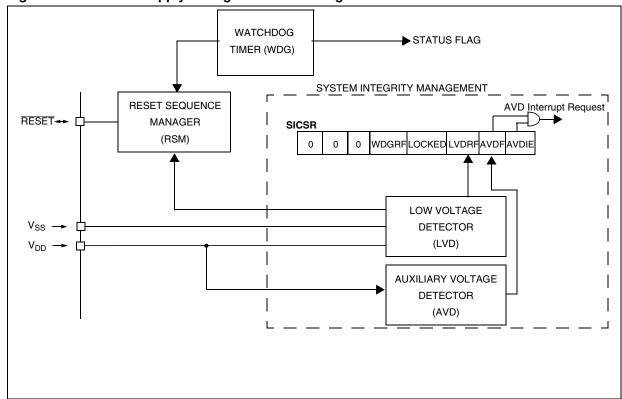

The reset sequence manager includes three RE-SET sources as shown in Figure 16:

- External RESET source pulse

- Internal LVD RESET (Low Voltage Detection)

- Internal WATCHDOG RESET

**Note:** A reset can also be triggered following the detection of an illegal opcode or prebyte code. Refer to section 12.2.1 on page 107 for further details.

These sources act on the RESET pin and it is always kept low during the delay phase.

The RESET service routine vector is fixed at addresses FFFEh-FFFFh in the ST7 memory map.

The basic RESET sequence consists of 3 phases as shown in Figure 15:

- Active Phase depending on the RESET source

- 256 or 4096 CPU clock cycle delay (see table below)

- RESET vector fetch

**Caution**: When the ST7 is unprogrammed or fully erased, the Flash is blank and the RESET vector is not programmed. For this reason, it is recommended to keep the RESET pin in low state until programming mode is entered, in order to avoid unwanted behavior.

The 256 or 4096 CPU clock cycle delay allows the oscillator to stabilise and ensures that recovery has taken place from the Reset state. The shorter or longer clock cycle delay is automatically selected depending on the clock source chosen by option byte:

The RESET vector fetch phase duration is 2 clock cycles.

| Clock Source                                                      | CPU clock cycle delay |

|-------------------------------------------------------------------|-----------------------|

| Internal RC Oscillator                                            | 256                   |

| External clock (connected to CLKIN pin)                           | 256                   |

| External Crystal/Ceramic Oscillator (connected to OSC1/OSC2 pins) | 4096                  |

If the PLL is enabled by option byte, it outputs the clock after an additional delay of  $t_{\text{STARTUP}}$  (see Figure 13).

Figure 15. RESET Sequence Phases

|              | RESET                                      |                 |

|--------------|--------------------------------------------|-----------------|

| Active Phase | INTERNAL RESET<br>256 or 4096 CLOCK CYCLES | FETCH<br>VECTOR |

# 7.5.2 Asynchronous External RESET pin

The RESET pin is both an input and an open-drain output with integrated R<sub>ON</sub> weak pull-up resistor. This pull-up has no fixed value but varies in accordance with the input voltage. It can be pulled low by external circuitry to reset the device. See Electrical Characteristic section for more details.

A RESET signal originating from an external source must have a duration of at least  $t_{h(RSTL)in}$  in order to be recognized (see Figure 17). This detection is asynchronous and therefore the MCU can enter reset state even in HALT mode.

# **SYSTEM INTEGRITY MANAGEMENT** (Cont'd)

Figure 19. Reset and Supply Management Block Diagram

## INTERRUPTS (Cont'd)

# EXTERNAL INTERRUPT CONTROL REGISTER (EICR)

Read/Write

Reset Value: 0000 0000 (00h)

7 0

| IS31 | IS30 | IS21 | IS20 | IS11 | IS10 | IS01 | IS00 |

|------|------|------|------|------|------|------|------|

|------|------|------|------|------|------|------|------|

## Bits 7:6 = **IS3[1:0]** *ei3 sensitivity*

These bits define the interrupt sensitivity for ei3 (Port B0) according to Table 6.

# Bits 5:4 = **IS2[1:0]** *ei2 sensitivity*

These bits define the interrupt sensitivity for ei2 (Port B3) according to Table 6.

## Bits 3:2 = **IS1[1:0]** *ei1 sensitivity*

These bits define the interrupt sensitivity for ei1 (Port A7) according to Table 6.

## Bits 1:0 = IS0[1:0] ei0 sensitivity

These bits define the interrupt sensitivity for ei0 (Port A0) according to Table 6.

#### Notes:

- 1. These 8 bits can be written only when the I bit in the CC register is set.

- 2. Changing the sensitivity of a particular external interrupt clears this pending interrupt. This can be used to clear unwanted pending interrupts. Refer to section "External Interrupt Function" on page 48.

**Table 6. Interrupt Sensitivity Bits**

| ISx1 | ISx0 | External Interrupt Sensitivity |

|------|------|--------------------------------|

| 0    | 0    | Falling edge & low level       |

| 0    | 1    | Rising edge only               |

| 1    | 0    | Falling edge only              |

| 1    | 1    | Rising and falling edge        |

# EXTERNAL INTERRUPT SELECTION REGISTER (EISR)

Read/Write

7

Reset Value: 0000 1100 (0Ch)

| ei31 ei30 ei21 ei20 ei11 ei10 ei01 ei00               |      |      |      |      |      |      |      |      |

|-------------------------------------------------------|------|------|------|------|------|------|------|------|

| ei31   ei30   ei21   ei20   ei11   ei10   ei01   ei00 | ei31 | ei30 | ei21 | ei20 | ei11 | ei10 | ei01 | ei00 |

0

## Bits 7:6 = **ei3[1:0]** *ei3 pin selection*

These bits are written by software. They select the Port B I/O pin used for the ei3 external interrupt according to the table below.

## External Interrupt I/O pin selection

| ei31 | ei30 | I/O Pin           |

|------|------|-------------------|

| 0    | 0    | PB0 <sup>1)</sup> |

| 0    | 1    | PB1               |

| 1    | 0    | PB2               |

#### Note:

1. Reset State

# Bits 5:4 = ei2[1:0] ei2 pin selection

These bits are written by software. They select the Port B I/O pin used for the ei2 external interrupt according to the table below.

## External Interrupt I/O pin selection

| ei21 | ei20 | I/O Pin           |

|------|------|-------------------|

| 0    | 0    | PB3 <sup>1)</sup> |

| 0    | 1    | PB4 <sup>2)</sup> |

| 1    | 0    | PB5               |

| 1    | 1    | PB6               |

#### Notes:

- 1. Reset State

- 2. PB4 cannot be used as an external interrupt in HALT mode.

### POWER SAVING MODES (Cont'd)

### Similarities with Halt mode

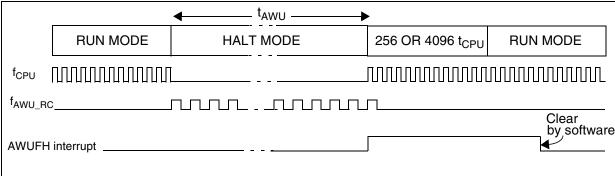

The following AWUFH mode behaviour is the same as normal Halt mode:

- The MCU can exit AWUFH mode by means of any interrupt with exit from Halt capability or a reset (see Section 9.4 HALT MODE).

- When entering AWUFH mode, the I bit in the CC register is forced to 0 to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes up immediately.

- In AWUFH mode, the main oscillator is turned off causing all internal processing to be stopped, including the operation of the on-chip peripherals. None of the peripherals are clocked except those which get their clock supply from another clock generator (such as an external or auxiliary oscillator like the AWU oscillator).

- The compatibility of Watchdog operation with AWUFH mode is configured by the WDGHALT option bit in the option byte. Depending on this setting, the HALT instruction when executed while the Watchdog system is enabled, can generate a Watchdog RESET.

Figure 30. AWUF Halt Timing Diagram

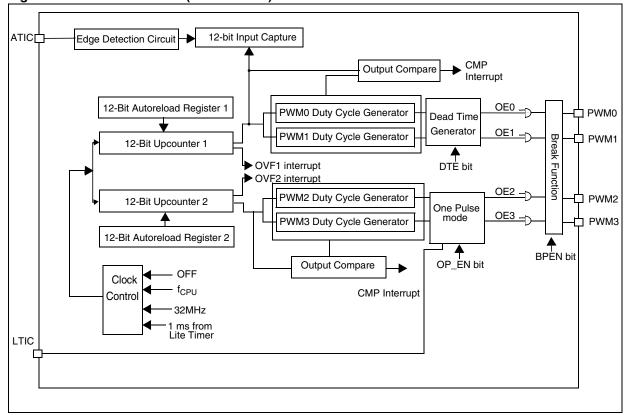

# **DUAL 12-BIT AUTORELOAD TIMER 4** (Cont'd)

Figure 36. Dual Timer Mode (ENCNTR2=1)

# **DUAL 12-BIT AUTORELOAD TIMER 4** (Cont'd)

# **AUTORELOAD REGISTER (ATR1H)**

Read / Write

Reset Value: 0000 0000 (00h)

# **AUTORELOAD REGISTER (ATR1L)**

Read / Write

Reset Value: 0000 0000 (00h)

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| ATR7 | ATR6 | ATR5 | ATR4 | ATR3 | ATR2 | ATR1 | ATR0 |

Bits 11:0 = ATR1[11:0] Autoreload Register 1. This is a 12-bit register which is written by software. The ATR1 register value is automatically loaded into the upcounter CNTR1 when an overflow occurs. The register value is used to set the PWM frequency.

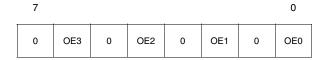

# PWM OUTPUT CONTROL REGISTER (PWMCR)

Read/Write

Reset Value: 0000 0000 (00h)

Bits 7:0 = **OE[3:0]** *PWMx output enable*.

These bits are set and cleared by software and cleared by hardware after a reset.

- PWM mode disabled. PWMx Output Alternate Function disabled (I/O pin free for general purpose I/O)

- 1: PWM mode enabled

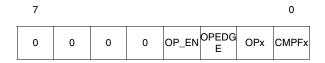

# PWMx CONTROL STATUS REGISTER (PWMxCSR)

Read / Write

Reset Value: 0000 0000 (00h)

Bits 7:4= Reserved, must be kept cleared.

Bit 3 = OP EN One Pulse Mode Enable

This bit is read/write by software and cleared by hardware after a reset. This bit enables the One Pulse feature for PWM2 and PWM3. (Only available for PWM3CSR)

0: One Pulse mode disabled for PWM2/3.

1: One Pulse mode enabled for PWM2/3.

Bit 2 = OPEDGE One Pulse Edge Selection.

This bit is read/write by software and cleared by hardware after a reset. This bit selects the polarity of the LTIC signal for One Pulse feature. This bit will be effective only if OP\_EN bit is set. (Only available for PWM3CSR)

0: Falling edge of LTIC is selected.

1: Rising edge of LTIC is selected.

Bit 1 = **OPx** *PWMx Output Polarity*.

This bit is read/write by software and cleared by hardware after a reset. This bit selects the polarity of the PWM signal.

0: The PWM signal is not inverted.

1: The PWM signal is inverted.

#### Bit 0 = **CMPFx** PWMx Compare Flag.

This bit is set by hardware and cleared by software by reading the PWMxCSR register. It indicates that the upcounter value matches the Active DCRx register value.

0: Upcounter value does not match DCRx value.

1: Upcounter value matches DCRx value.

## **DUAL 12-BIT AUTORELOAD TIMER 4** (Cont'd)

Bit 1= TRAN2 Transfer enable2

This bit is read/write by software, cleared by hardware after each completed transfer and set by hardware after reset. It controls the transfers on CNTR2.

It allows the value of the Preload DCRx registers to be transferred to the Active DCRx registers after the next overflow event.

The OPx bits are transferred to the shadow OPx bits in the same way.

#### Notes:

- DCR2/3 transfer will be controlled using this bit if ENCNTR2 bit is set.

- 2. This bit must not be reset by software

#### Bit 0 = TRAN1 Transfer enable 1

This bit is read/write by software, cleared by hardware after each completed transfer and set by hardware after reset. It controls the transfers on CNTR1. It allows the value of the Preload DCRx registers to be transferred to the Active DCRx registers after the next overflow event.

The OPx bits are transferred to the shadow OPx bits in the same way.

#### Notes:

- 1. DCR0,1 transfers are always controlled using this bit.

- DCR2/3 transfer will be controlled using this bit if ENCNTR2 is reset.

- 3. This bit must not be reset by software

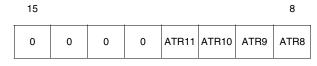

### **AUTORELOAD REGISTER2 (ATR2H)**

Read / Write

Reset Value: 0000 0000 (00h)

15 8

| Λ | 0 | 0 | 0 | ATD11  | ATD10  | ATR9 | ΛTDQ  |

|---|---|---|---|--------|--------|------|-------|

| U | 0 | 0 | 0 | A11111 | A11110 | AIII | AIIIO |

|   |   |   |   |        |        |      |       |

## **AUTORELOAD REGISTER (ATR2L)**

Read / Write

7

Reset Value: 0000 0000 (00h)

ATR7 ATR6 ATR5 ATR4 ATR3 ATR2 ATR1 ATR0

0

Bits 11:0 = **ATR2[11:0]** *Autoreload Register 2.*This is a 12-bit register which is written by software. The ATR2 register value is automatically loaded into the upcounter CNTR2 when an overflow of CNTR2 occurs. The register value is used

to set the PWM2/PWM3 frequency when

ENCNTR2 is set.

# **DEAD TIME GENERATOR REGISTER (DTGR)**

Read/Write

Reset Value: 0000 0000 (00h)

7 0

| DTE | DT6 | DT5 | DT4 | DT3 | DT2 | DT1 | DT0 |

#### Bit 7 = **DTE** Dead Time Enable

This bit is read/write by software. It enables a dead time generation on PWM0/PWM1.

0: No Dead time insertion.

1: Dead time insertion enabled.

#### Bits 6:0 = **DT[6:0]** Dead Time Value

These bits are read/write by software. They define the dead time inserted between PWM0/PWM1. Dead time is calculated as follows:

Dead Time = DT[6:0] x Tcounter1

#### Note:

1. If DTE is set and DT[6:0]=0, PWM output signals will be at their reset state.

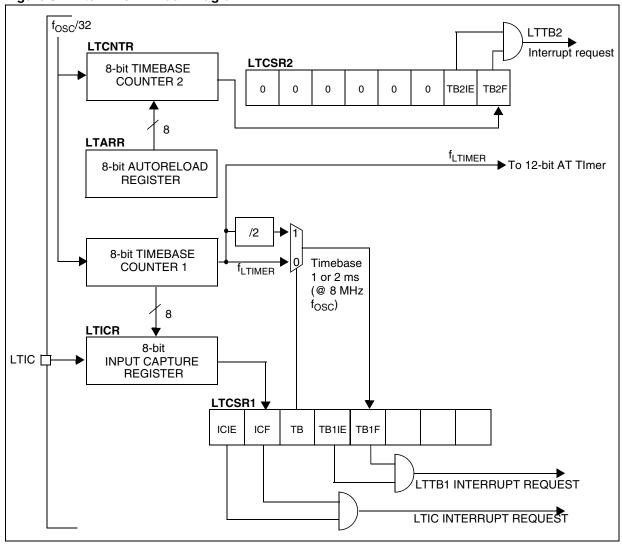

## **11.3 LITE TIMER 2 (LT2)**

#### 11.3.1 Introduction

The Lite Timer can be used for general-purpose timing functions. It is based on two free-running 8-bit upcounters and an 8-bit input capture register.

#### 11.3.2 Main Features

- Realtime Clock

- One 8-bit upcounter 1 ms or 2 ms timebase period (@ 8 MHz  $f_{OSC}$ )

- One 8-bit upcounter with autoreload and programmable timebase period from 4µs to 1.024ms in 4µs increments (@ 8 MHz f<sub>OSC</sub>)

- 2 Maskable timebase interrupts

- Input Capture

- 8-bit input capture register (LTICR)

- Maskable interrupt with wake-up from Halt mode capability

Figure 51. Lite Timer 2 Block Diagram

## **LITE TIMER** (Cont'd)

### 11.3.4 Low Power Modes

| Mode        | Description                         |  |  |  |  |

|-------------|-------------------------------------|--|--|--|--|

|             | No effect on Lite timer             |  |  |  |  |

| SLOW        | (this peripheral is driven directly |  |  |  |  |

|             | by f <sub>OSC</sub> /32)            |  |  |  |  |

| WAIT        | No effect on Lite timer             |  |  |  |  |

| ACTIVE HALT | No effect on Lite timer             |  |  |  |  |

| HALT        | Lite timer stops counting           |  |  |  |  |

## 11.3.5 Interrupts

| Interrupt<br>Event  | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Active<br>Halt | Exit<br>from<br>Halt |  |

|---------------------|---------------|--------------------------|----------------------|--------------------------------|----------------------|--|

| Timebase 1<br>Event | TB1F          | TB1IE                    |                      | Yes                            | No                   |  |

| Timebase 2<br>Event | TB2F          | TB2IE                    | Yes                  | No                             |                      |  |

| IC Event            | ICF           | ICIE                     |                      | No                             |                      |  |

Note: The TBxF and ICF interrupt events are connected to separate interrupt vectors (see Interrupts chapter).

They generate an interrupt if the enable bit is set in the LTCSR1 or LTCSR2 register and the interrupt mask in the CC register is reset (RIM instruction).

## 11.3.6 Register Description

# LITE TIMER CONTROL/STATUS REGISTER 2 (LTCSR2)

Read / Write

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |       | 0    |

|---|---|---|---|---|---|-------|------|

| 0 | 0 | 0 | 0 | 0 | 0 | TB2IE | TB2F |

Bits 7:2 = Reserved, must be kept cleared.

Bit 1 = **TB2IE** *Timebase 2 Interrupt enable* This bit is set and cleared by software. 0: Timebase (TB2) interrupt disabled

1: Timebase (TB2) interrupt enabled

Bit 0 = **TB2F** Timebase 2 Interrupt Flag This bit is set by hardware and cleared by software reading the LTCSR register. Writing to this bit has no effect.

0: No Counter 2 overflow

1: A Counter 2 overflow has occurred

#### LITE TIMER **AUTORELOAD** REGISTER (LTARR)

Read / Write

7

Reset Value: 0000 0000 (00h)

0 AR7 AR6 AR5 AR4 AR3 AR2 AR1 AR0

Bits 7:0 = AR[7:0] Counter 2 Reload Value These bits register is read/write by software. The LTARR value is automatically loaded into Counter 2 (LTCNTR) when an overflow occurs.

## **LITE TIMER COUNTER 2 (LTCNTR)**

Read only

Reset Value: 0000 0000 (00h)

7 0 CNT6 CNT5 CNT7 CNT4 CNT3 CNT2 CNT1 CNT<sub>0</sub>

Bits 7:0 = CNT[7:0] Counter 2 Reload Value This register is read by software. The LTARR value is automatically loaded into Counter 2 (LTCN-TR) when an overflow occurs.

# LITE TIMER CONTROL/STATUS REGISTER (LTCSR1)

Read / Write

Reset Value: 0x00 0000 (x0h)

7 0 ICIE ICF ТВ TB1IE TB1F

Bit 7 = **ICIE** Interrupt Enable

This bit is set and cleared by software.

0: Input Capture (IC) interrupt disabled

1: Input Capture (IC) interrupt enabled

# SERIAL PERIPHERAL INTERFACE (cont'd)

# SPI CONTROL/STATUS REGISTER (SPICSR)

Read/Write (some bits Read Only) Reset Value: 0000 0000 (00h)

| 7    |      |     |      |   |     |     | 0   |

|------|------|-----|------|---|-----|-----|-----|

| SPIF | WCOL | OVR | MODF | - | SOD | SSM | SSI |

# Bit 7 = **SPIF** Serial Peripheral Data Transfer Flag (Read only)

This bit is set by hardware when a transfer has been completed. An interrupt is generated if SPIE = 1 in the SPICR register. It is cleared by a software sequence (an access to the SPICSR register followed by a write or a read to the SPIDR register).

- 0: Data transfer is in progress or the flag has been cleared.

- 1: Data transfer between the device and an external device has been completed.

**Note:** While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

Bit 6 = **WCOL** Write Collision status (Read only)

This bit is set by hardware when a write to the SPIDR register is done during a transmit sequence. It is cleared by a software sequence (see Figure 6).

- 0: No write collision occurred

- 1: A write collision has been detected

#### Bit 5 = **OVR** SPI Overrun error (Read only)

This bit is set by hardware when the byte currently being received in the shift register is ready to be transferred into the SPIDR register while SPIF = 1 (See Section 0.1.5.2). An interrupt is generated if SPIE = 1 in the SPICR register. The OVR bit is cleared by software reading the SPICSR register.

- 0: No overrun error

- 1: Overrun error detected

#### Bit 4 = **MODF** *Mode Fault flag (Read only)*

This bit is set by hardware when the  $\overline{SS}$  pin is pulled low in master mode (see Section 0.1.5.1 Master Mode Fault (MODF)). An SPI interrupt can be generated if SPIE = 1 in the SPICR register. This bit is cleared by a software sequence (An access to the SPICSR register while MODF = 1 followed by a write to the SPICR register).

- 0: No master mode fault detected

- 1: A fault in master mode has been detected

Bit 3 = Reserved, must be kept cleared.

## Bit 2 = **SOD** SPI Output Disable

This bit is set and cleared by software. When set, it disables the alternate function of the SPI output (MOSI in master mode / MISO in slave mode)

- 0: SPI output enabled (if SPE = 1)

- 1: SPI output disabled

## Bit $1 = SSM \overline{SS} Management$

This bit is set and cleared by software. When set, it disables the alternate function of the SPI SS pin and uses the SSI bit value instead. See Section 0.1.3.2 Slave Select Management.

- 0: Hardware management (SS managed by external pin)

- 1: Software management (internal  $\overline{SS}$  signal controlled by SSI bit. External  $\overline{SS}$  pin free for general-purpose I/O)

#### Bit $0 = SSI \overline{SS}$ Internal Mode

This bit is set and cleared by software. It acts as a 'chip select' by controlling the level of the SS slave select signal when the SSM bit is set.

- 0: Slave selected

- 1: Slave deselected

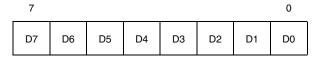

# SPI DATA I/O REGISTER (SPIDR)

Read/Write

Reset Value: Undefined

The SPIDR register is used to transmit and receive data on the serial bus. In a master device, a write to this register will initiate transmission/reception of another byte.

**Notes:** During the last clock cycle the SPIF bit is set, a copy of the received data byte in the shift register is moved to a buffer. When the user reads the serial peripheral data I/O register, the buffer is actually being read.

While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

**Warning:** A write to the SPIDR register places data directly into the shift register for transmission.

A read to the SPIDR register returns the value located in the buffer and not the content of the shift register (see Figure 1).

# 10-BIT A/D CONVERTER (ADC) (Cont'd)

Bit 2 = **AMPSEL** Amplifier Selection Bit This bit is set and cleared by software.

0: Amplifier is not selected

1: Amplifier is selected

Note: When AMPSEL=1 it is mandatory that  $f_{\mbox{\scriptsize ADC}}$

be less than or equal to 2 MHz.

Bits 1:0 = **D[1:0]** LSB of Analog Converted Value

**Table 18. ADC Register Map and Reset Values**

| Address<br>(Hex.) | Register<br>Label     | 7        | 6          | 5         | 4           | 3         | 2           | 1        | 0        |

|-------------------|-----------------------|----------|------------|-----------|-------------|-----------|-------------|----------|----------|

| 0034h             | ADCCSR<br>Reset Value | EOC<br>0 | SPEED<br>0 | ADON<br>0 | 0           | 0<br>0    | CH2<br>0    | CH1<br>0 | CH0<br>0 |

| 0035h             | ADCDRH<br>Reset Value | D9<br>x  | D8<br>x    | D7<br>x   | D6<br>x     | D5<br>x   | D4<br>x     | D3<br>x  | D2<br>x  |

| 0036h             | ADCDRL<br>Reset Value | 0        | 0 0        | 0 0       | AMPCAL<br>0 | SLOW<br>0 | AMPSEL<br>0 | D1<br>x  | D0<br>x  |

## 13 ELECTRICAL CHARACTERISTICS

#### 13.1 PARAMETER CONDITIONS

Unless otherwise specified, all voltages are referred to  $V_{\rm SS}$ .

#### 13.1.1 Minimum and Maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A$ =25°C and  $T_A$ = $T_A$ max (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

## 13.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A=25^{\circ}C$ ,  $V_{DD}=5V$  (for the  $4.5V \le V_{DD} \le 5.5V$  voltage range) and  $V_{DD}=3.3V$  (for the  $3V \le V_{DD} \le 3.6V$  voltage range). They are given only as design guidelines and are not tested.

#### 13.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

#### 13.1.4 Loading capacitor

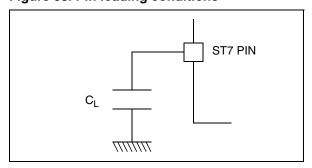

The loading conditions used for pin parameter measurement are shown in Figure 63.

Figure 63. Pin loading conditions

## 13.1.5 Pin input voltage

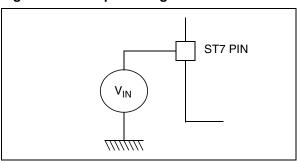

The input voltage measurement on a pin of the device is described in Figure 64.

Figure 64. Pin input voltage

477

## **OPERATING CONDITIONS** (Cont'd)

# 13.3.5.2 Devices with "6" or "3" order code suffix (tested for $T_A = -40$ to +125°C) @ $V_{DD} = 3.0$ to 3.6V

| Symbol               | Parameter                                          | Conditions                                                                         | Min  | Тур               | Max              | Unit |  |

|----------------------|----------------------------------------------------|------------------------------------------------------------------------------------|------|-------------------|------------------|------|--|

| 4                    | Internal RC oscillator fre-                        | RCCR = FF (reset value), T <sub>A</sub> =25°C, V <sub>DD</sub> = 3.3V              |      | 700               |                  | kHz  |  |

| f <sub>RC</sub>      | quency 1)                                          | RCCR=RCCR1 <sup>2)</sup> , T <sub>A</sub> =25°C, V <sub>DD</sub> = 3.3V            | 992  | 1000              | 1008             | K⊓Z  |  |

|                      |                                                    | T <sub>A</sub> =25°C,V <sub>DD</sub> =3.3V                                         | -0.8 |                   | +0.8             | %    |  |

|                      |                                                    | T <sub>A</sub> =25°C,V <sub>DD</sub> =3.0 to 3.6V <sup>3)</sup>                    | -1   |                   | +1               | %    |  |

| ACC                  | Accuracy of Internal RC oscillator when calibrated | T <sub>A</sub> =25 to +85°C,V <sub>DD</sub> =3.3V                                  | -3   |                   | +3               | %    |  |

| ACC <sub>RC</sub>    | with RCCR=RCCR1 <sup>2)</sup>                      | T <sub>A</sub> =25 to +85°C,V <sub>DD</sub> =3.0 to 3.6V <sup>3)</sup>             | -3.5 |                   | +3.5             | %    |  |

|                      |                                                    | $T_A=25 \text{ to } +125^{\circ}\text{C}, V_{DD}=3.0 \text{ to } 3.6\text{V}^{-3}$ | -5   |                   | +6.5             | %    |  |

|                      |                                                    | T <sub>A</sub> =-40 to +25°C,V <sub>DD</sub> =3.0 to 3.6V <sup>3)</sup>            | -3.5 |                   | +4               | %    |  |

| I <sub>DD(RC)</sub>  | RC oscillator current consumption                  | T <sub>A</sub> =25°C,V <sub>DD</sub> =3.3V                                         |      | 400 <sup>3)</sup> |                  | μА   |  |

| t <sub>su(RC)</sub>  | RC oscillator setup time                           | T <sub>A</sub> =25°C,V <sub>DD</sub> =3.3V                                         |      |                   | 10 <sup>2)</sup> | μS   |  |

| f <sub>PLL</sub>     | x4 PLL input clock                                 |                                                                                    |      | 0.7 <sup>3)</sup> |                  | MHz  |  |

| t <sub>LOCK</sub>    | PLL Lock time <sup>5)</sup>                        |                                                                                    |      | 2                 |                  | ms   |  |

| t <sub>STAB</sub>    | PLL Stabilization time <sup>5)</sup>               |                                                                                    |      | 4                 |                  | ms   |  |

| ACC                  | v4 DLL Acquirect                                   | $f_{RC} = 1MHz@T_A=25^{\circ}C, V_{DD}=2.7 \text{ to } 3.3V$                       |      | 0.1 <sup>4)</sup> |                  | %    |  |

| ACC <sub>PLL</sub>   | x4 PLL Accuracy                                    | $f_{RC} = 1MHz@T_A=40 \text{ to } +85^{\circ}C, V_{DD}=3.3V$                       |      | 0.1 <sup>4)</sup> |                  | %    |  |

| t <sub>w(JIT)</sub>  | PLL jitter period <sup>6)</sup>                    | $f_{RC} = 1MHz$                                                                    |      | 120               |                  | μs   |  |

| JIT <sub>PLL</sub>   | PLL jitter (∆f <sub>CPU</sub> /f <sub>CPU</sub> )  |                                                                                    |      | 1 <sup>7)</sup>   |                  | %    |  |

| I <sub>DD(PLL)</sub> | PLL current consumption                            | T <sub>A</sub> =25°C                                                               |      | 190 <sup>3)</sup> |                  | μΑ   |  |

#### Notes:

- 1. If the RC oscillator clock is selected, to improve clock stability and frequency accuracy, it is recommended to place a decoupling capacitor, typically 100nF, between the  $V_{DD}$  and  $V_{SS}$  pins as close as possible to the ST7 device.

- 2. See "INTERNAL RC OSCILLATOR ADJUSTMENT" on page 23.

- 3. Data based on characterization results, not tested in production

- 4. Averaged over a 4ms period. After the LOCKED bit is set, a period of t<sub>STAB</sub> is required to reach ACC<sub>PLL</sub> accuracy

- After the LOCKED bit is set ACC<sub>PLL</sub> is max. 10% until t<sub>STAB</sub> has elapsed. See Figure 13 on page 24.

- 6. This period is the PLL servoing period. During this period, the frequency remains unchanged.

- 7. Guaranteed by design.

# I/O PORT PIN CHARACTERISTICS (Cont'd)

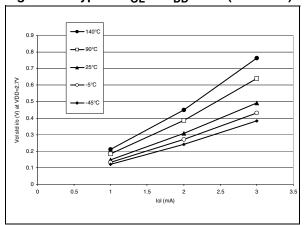

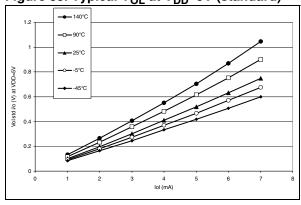

Figure 81. Typical V<sub>OL</sub> at V<sub>DD</sub>=2.7V (standard)

Figure 82. Typical V<sub>OL</sub> at V<sub>DD</sub>=3.3V (standard)

Figure 83. Typical  $V_{OL}$  at  $V_{DD}$ =5V (standard)

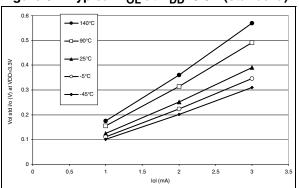

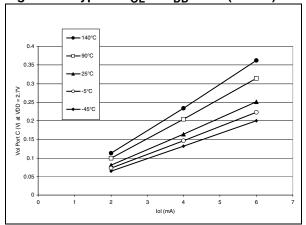

Figure 84. Typical V<sub>OL</sub> at V<sub>DD</sub>=2.7V (Port C)

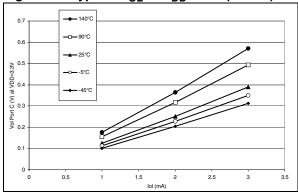

Figure 85. Typical V<sub>OL</sub> at V<sub>DD</sub>=3.3V (Port C)

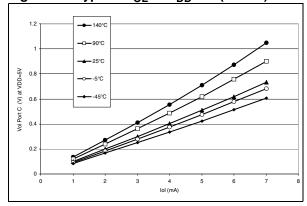

Figure 86. Typical V<sub>OL</sub> at V<sub>DD</sub>=5V (Port C)

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com