#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | SPI                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 11                                                                     |

| Program Memory Size        | 4KB (4K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 5x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 16-DIP (0.300", 7.62mm)                                                |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7flit15by1b6 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **3 REGISTER & MEMORY MAP**

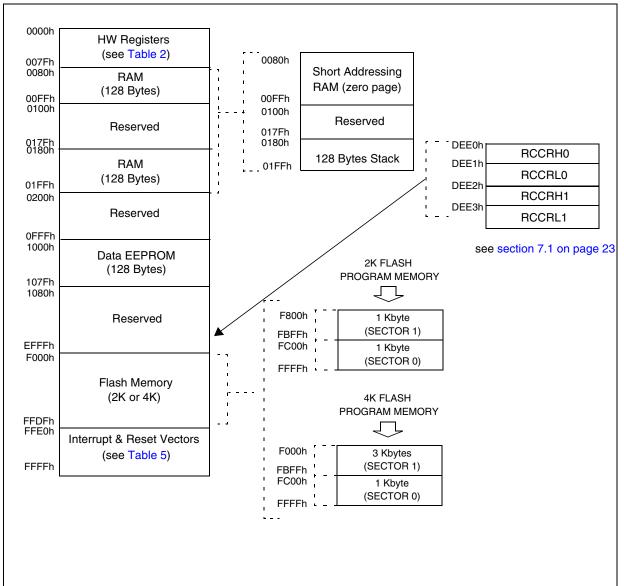

As shown in Figure 5, the MCU is capable of addressing 64K bytes of memories and I/O registers.

The available memory locations consist of 128 bytes of register locations, 256 bytes of RAM, 128 bytes of data EEPROM and up to 4 Kbytes of flash program memory. The RAM space includes up to 128 bytes for the stack from 180h to 1FFh.

The highest address bytes contain the user reset and interrupt vectors.

The Flash memory contains two sectors (see Figure 5) mapped in the upper part of the ST7 ad-

dressing space so the reset and interrupt vectors are located in Sector 0 (F000h-FFFFh).

The size of Flash Sector 0 and other device options are configurable by Option byte (refer to section 15.1 on page 149).

**IMPORTANT:** Memory locations marked as "Reserved" must never be accessed. Accessing a reserved area can have unpredictable effects on the device.

#### Figure 5. Memory Map

**لرکا**

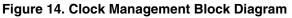

#### 7.4 MULTI-OSCILLATOR (MO)

The main clock of the ST7 can be generated by four different source types coming from the multioscillator block (1 to 16MHz):

- an external source

- 5 different configurations for crystal or ceramic resonator oscillators

- an internal high frequency RC oscillator

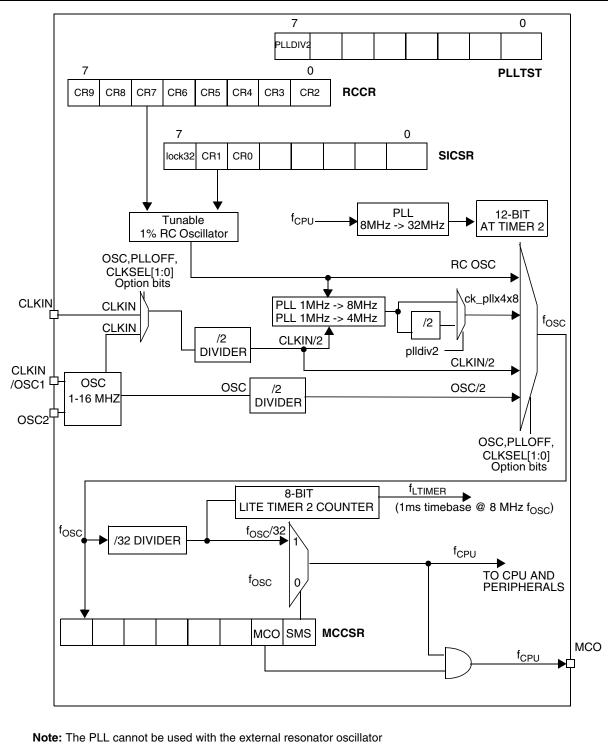

Each oscillator is optimized for a given frequency range in terms of consumption and is selectable through the option byte. The associated hardware configurations are shown in Table 4. Refer to the electrical characteristics section for more details.

#### External Clock Source

In this external clock mode, a clock signal (square, sinus or triangle) with ~50% duty cycle has to drive the OSC1 pin while the OSC2 pin is tied to ground.

**Note:** when the Multi-Oscillator is not used, PB4 is selected by default as external clock.

#### **Crystal/Ceramic Oscillators**

In this mode, with a self-controlled gain feature, oscillator of any frequency from 1 to 16MHz can be placed on OSC1 and OSC2 pins. This family of oscillators has the advantage of producing a very accurate rate on the main clock of the ST7. In this mode of the multi-oscillator, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. The loading capacitance values must be adjusted according to the selected oscillator.

These oscillators are not stopped during the RESET phase to avoid losing time in the oscillator start-up phase.

#### Internal RC Oscillator

57/

In this mode, the tunable 1%RC oscillator is used as main clock source. The two oscillator pins have to be tied to ground if dedicately using for oscillator else can be found as general purpose IO. The calibration is done through the RCCR[7:0] and SICSR[6:5] registers.

Table 4. ST7 Clock Sources

#### 7.6 SYSTEM INTEGRITY MANAGEMENT (SI)

The System Integrity Management block contains the Low voltage Detector (LVD) and Auxiliary Voltage Detector (AVD) functions. It is managed by the SICSR register.

**Note:** A reset can also be triggered following the detection of an illegal opcode or prebyte code. Refer to section 12.2.1 on page 107 for further details.

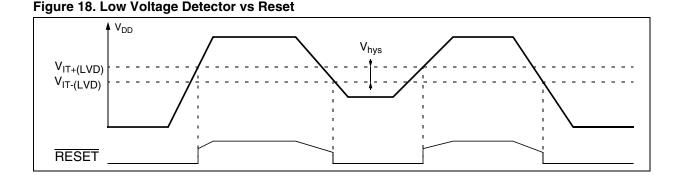

#### 7.6.1 Low Voltage Detector (LVD)

The Low Voltage Detector function (LVD) generates a static reset when the V<sub>DD</sub> supply voltage is below a V<sub>IT-(LVD)</sub> reference value. This means that it secures the power-up as well as the power-down keeping the ST7 in reset.

The V<sub>IT-(LVD)</sub> reference value for a voltage drop is lower than the V<sub>IT+(LVD)</sub> reference value for poweron in order to avoid a parasitic reset when the MCU starts running and sinks current on the supply (hysteresis).

The LVD Reset circuitry generates a reset when  $V_{DD}$  is below:

$-V_{IT+(LVD)}$  when  $V_{DD}$  is rising

$- V_{IT-(LVD)}$  when  $V_{DD}$  is falling

57/

The LVD function is illustrated in Figure 18.

The voltage threshold can be configured by option byte to be low, medium or high.

Provided the minimum  $V_{DD}$  value (guaranteed for the oscillator frequency) is above  $V_{IT\mathchar`(LVD)},$  the MCU can only be in two modes:

- under full software control

- in static safe reset

In these conditions, secure operation is always ensured for the application without the need for external reset hardware.

During a Low Voltage Detector Reset, the RESET pin is held low, thus permitting the MCU to reset other devices.

#### Notes:

The LVD allows the device to be used without any external RESET circuitry.

The LVD is an optional function which can be selected by option byte.

Use of LVD with capacitive power supply: with this type of power supply, if power cuts occur in the application, it is recommended to pull  $V_{DD}$  down to 0V to ensure optimum restart conditions. Refer to circuit example in Figure 106 on page 136 and note 4.

It is recommended to make sure that the  $V_{DD}$  supply voltage rises monotonously when the device is exiting from Reset, to ensure the application functions properly.

0

#### POWER SAVING MODES (Cont'd)

#### 9.6.0.1 Register Description

#### AWUFH CONTROL/STATUS REGISTER (AWUCSR)

Read/Write Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |          |          | 0         |

|---|---|---|---|---|----------|----------|-----------|

| 0 | 0 | 0 | 0 | 0 | AWU<br>F | AWU<br>M | AWU<br>EN |

Bits 7:3 = Reserved.

#### Bit 1= AWUF Auto Wake Up Flag

This bit is set by hardware when the AWU module generates an interrupt and cleared by software on reading AWUCSR. Writing to this bit does not change its value.

0: No AWU interrupt occurred

1: AWU interrupt occurred

#### Bit 1= **AWUM** Auto Wake Up Measurement

This bit enables the AWU RC oscillator and connects its output to the input capture of the 12-bit Auto-Reload timer. This allows the timer to be used to measure the AWU RC oscillator dispersion and then compensate this dispersion by providing the right value in the AWUPRE register.

0: Measurement disabled

1: Measurement enabled

5/

Bit 0 = **AWUEN** Auto Wake Up From Halt Enabled This bit enables the Auto Wake Up From Halt feature: once HALT mode is entered, the AWUFH wakes up the microcontroller after a time delay dependent on the AWU prescaler value. It is set and cleared by software.

- 0: AWUFH (Auto Wake Up From Halt) mode disabled

- 1: AWUFH (Auto Wake Up From Halt) mode enabled

#### AWUFH PRESCALER REGISTER (AWUPR) Read/Write

| 7 |  |

|---|--|

| 1 |  |

| AWU        | AWU | AWU | AWU | AWU | AWU | AWU | AWU |

|------------|-----|-----|-----|-----|-----|-----|-----|

| AWU<br>PR7 | PR6 | PR5 | PR4 | PR3 | PR2 | PR1 | PR0 |

Bits 7:0= **AWUPR[7:0]** Auto Wake Up Prescaler These 8 bits define the AWUPR Dividing factor (as explained below:

| AWUPR[7:0] | Dividing factor |

|------------|-----------------|

| 00h        | Forbidden       |

| 01h        | 1               |

|            |                 |

| FEh        | 254             |

| FFh        | 255             |

In AWU mode, the period that the MCU stays in Halt Mode (t\_{AWU} in Figure 30 on page 45) is defined by

$$^{t}AWU = 64 \times AWUPR \times \frac{1}{f_{AWURC}} + ^{t}RCSTRT$$

This prescaler register can be programmed to modify the time that the MCU stays in Halt mode before waking up automatically.

**Note:** If 00h is written to AWUPR, depending on the product, an interrupt is generated immediately after a HALT instruction, or the AWUPR remains unchanged.

| Address<br>(Hex.) | Register<br>Label     | 7           | 6           | 5           | 4           | 3           | 2           | 1           | 0           |

|-------------------|-----------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| 0049h             | AWUPR<br>Reset Value  | AWUPR7<br>1 | AWUPR6<br>1 | AWUPR5<br>1 | AWUPR4<br>1 | AWUPR3<br>1 | AWUPR2<br>1 | AWUPR1<br>1 | AWUPR0<br>1 |

| 004Ah             | AWUCSR<br>Reset Value | 0           | 0           | 0           | 0           | 0           | AWUF        | AWUM        | AWUEN       |

# 10 I/O PORTS

#### **10.1 INTRODUCTION**

The I/O ports allow data transfer. An I/O port can contain up to 8 pins. Each pin can be programmed independently either as a digital input or digital output. In addition, specific pins may have several other functions. These functions can include external interrupt, alternate signal input/output for onchip peripherals or analog input.

#### **10.2 FUNCTIONAL DESCRIPTION**

A Data Register (DR) and a Data Direction Register (DDR) are always associated with each port. The Option Register (OR), which allows input/output options, may or may not be implemented. The following description takes into account the OR register. Refer to the Port Configuration table for device specific information.

An I/O pin is programmed using the corresponding bits in the DDR, DR and OR registers: bit x corresponding to pin x of the port.

Figure 32 shows the generic I/O block diagram.

#### 10.2.1 Input Modes

Clearing the DDRx bit selects input mode. In this mode, reading its DR bit returns the digital value from that I/O pin.

If an OR bit is available, different input modes can be configured by software: floating or pull-up. Refer to I/O Port Implementation section for configuration.

#### Notes:

1. Writing to the DR modifies the latch value but does not change the state of the input pin.

2. Do not use read/modify/write instructions (BSET/BRES) to modify the DR register.

#### 10.2.1.1 External Interrupt Function

Depending on the device, setting the ORx bit while in input mode can configure an I/O as an input with interrupt. In this configuration, a signal edge or level input on the I/O generates an interrupt request via the corresponding interrupt vector (eix).

Falling or rising edge sensitivity is programmed independently for each interrupt vector. The External Interrupt Control Register (EICR) or the Miscellaneous Register controls this sensitivity, depending on the device.

Each external interrupt vector is linked to a dedicated group of I/O port pins (see pinout description and interrupt section). If several I/O interrupt pins on the same interrupt vector are selected simultaneously, they are logically combined. For this reason if one of the interrupt pins is tied low, it may mask the others.

External interrupts are hardware interrupts. Fetching the corresponding interrupt vector automatically clears the request latch. Changing the sensitivity of a particular external interrupt clears this pending interrupt. This can be used to clear unwanted pending interrupts.

#### Spurious interrupts

When enabling/disabling an external interrupt by setting/resetting the related OR register bit, a spurious interrupt is generated if the pin level is low and its edge sensitivity includes falling/rising edge. This is due to the edge detector input which is switched to '1' when the external interrupt is disabled by the OR register.

To avoid this unwanted interrupt, a "safe" edge sensitivity (rising edge for enabling and falling edge for disabling) has to be selected before changing the OR register bit and configuring the appropriate sensitivity again.

**Caution:** In case a pin level change occurs during these operations (asynchronous signal input), as interrupts are generated according to the current sensitivity, it is advised to disable all interrupts before and to reenable them after the complete previous sequence in order to avoid an external interrupt occurring on the unwanted edge.

This corresponds to the following steps:

- 1. To enable an external interrupt:

- set the interrupt mask with the SIM instruction (in cases where a pin level change could occur)

- select rising edge

- enable the external interrupt through the OR register

- select the desired sensitivity if different from rising edge

- reset the interrupt mask with the RIM instruction (in cases where a pin level change could occur)

- 2. To disable an external interrupt:

- set the interrupt mask with the SIM instruction SIM (in cases where a pin level change could occur)

- select falling edge

- disable the external interrupt through the OR register

#### I/O PORTS (Cont'd)

#### **10.7 DEVICE-SPECIFIC I/O PORT CONFIGURATION**

The I/O port register configurations are summarised as follows.

#### **Standard Ports**

#### PA7:0, PB6:0

<u>ل</u>حک

| MODE              | DDR | OR |

|-------------------|-----|----|

| floating input    | 0   | 0  |

| pull-up input     | 0   | 1  |

| open drain output | 1   | 0  |

| push-pull output  | 1   | 1  |

#### PC1:0 (multiplexed with OSC1,OSC2)

| MODE             | DDR |

|------------------|-----|

| floating input   | 0   |

| push-pull output | 1   |

The selection between OSC1 or PC0 and OSC2 or PC1 is done by option byte. Refer to section 15.1 on page 149. Interrupt capability is not available on PC1:0.

**Note:** PCOR not implemented but p-transistor always active in output mode (refer to Figure 32 on page 50)

#### Table 10. Port Configuration (Standard ports)

| Port   | Pin name       | Ing      | out     | Output     |           |  |

|--------|----------------|----------|---------|------------|-----------|--|

| FUIL   | FOIL FIII name | OR = 0   | OR = 1  | OR = 0     | OR = 1    |  |

| Port A | PA7:0          | floating | pull-up | open drain | push-pull |  |

| Port B | PB6:0          | floating | pull-up | open drain | push-pull |  |

**Note:** On ports where the external interrupt capability is selected using the EISR register, the configuration will be as follows:

| Port   | Pin name  | Ing      | out               | Output     |           |  |

|--------|-----------|----------|-------------------|------------|-----------|--|

| FOIL   | Fininanie | OR = 0   | OR = 1            | OR = 0     | OR = 1    |  |

| Port A | PA7:0     | floating | pull-up interrupt | open drain | push-pull |  |

| Port B | PB6:0     | floating | pull-up interrupt | open drain | push-pull |  |

#### Table 11. I/O Port Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|-------------------|-------------------|-----|---|---|---|---|---|---|-----|

| 0000h             | PADR              | MSB |   |   |   |   |   |   | LSB |

| 0000h             | Reset Value       | 1   | 1 | 1 | 1 | 1 | 1 | 1 | 1   |

| 00016             | PADDR             | MSB |   |   |   |   |   |   | LSB |

| 0001h             | Reset Value       | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

#### **Interrupt Ports**

Ports where the external interrupt capability is selected using the EISR register

| MODE                    | DDR | OR |

|-------------------------|-----|----|

| floating input          | 0   | 0  |

| pull-up interrupt input | 0   | 1  |

| open drain output       | 1   | 0  |

| push-pull output        | 1   | 1  |

| Address<br>(Hex.) | Register<br>Label | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|-------------------|-------------------|-----|---|---|---|---|---|---|-----|

| 0000h             | PAOR              | MSB |   |   |   |   |   |   | LSB |

| 0002h             | Reset Value       | 0   | 1 | 0 | 0 | 0 | 0 | 0 | 0   |

| 0000              | PBDR              | MSB |   |   |   |   |   |   | LSB |

| 0003h             | Reset Value       | 1   | 1 | 1 | 1 | 1 | 1 | 1 | 1   |

|                   | PBDDR             | MSB |   |   |   |   |   |   | LSB |

| 0004h             | Reset Value       | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

| 00051             | PBOR              | MSB |   |   |   |   |   |   | LSB |

| 0005h             | Reset Value       | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

| 00001             | PCDR              | MSB |   |   |   |   |   |   | LSB |

| 0006h             | Reset Value       | 0   | 0 | 0 | 0 | 0 | 0 | 1 | 1   |

| 0007              | PCDDR             | MSB |   |   |   |   |   |   | LSB |

| 0007h             | Reset Value       | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

#### **10.8 MULTIPLEXED INPUT/OUTPUT PORTS**

OSC1/PC0 are multiplexed on one pin (pin20) and OSC2/PC1 are multiplexed on another pin (pin 19).

#### DUAL 12-BIT AUTORELOAD TIMER 4 (Cont'd)

#### DUAL 12-BIT AUTORELOAD TIMER 4 (Cont'd)

#### **BREAK CONTROL REGISTER (BREAKCR)**

Read/Write

Reset Value: 0000 0000 (00h)

| 7     |        |    |      |      |      |      | 0    |

|-------|--------|----|------|------|------|------|------|

| BRSEL | BREDGE | ВА | BPEN | PWM3 | PWM2 | PWM1 | PWM0 |

#### Bit 7 = **BRSEL** Break Input Selection

This bit is read/write by software and cleared by hardware after reset. It selects the active Break signal from external BREAK pin and the output of the comparator.

0: External BREAK pin is selected for break mode.

1: Comparator output is selected for break mode.

#### Bit 6 = BREDGE Break Input Edge Selection

This bit is read/write by software and cleared by hardware after reset. It selects the active level of Break signal.

0: Low level of Break selected as active level.

1: High level of Break selected as active level.

#### Bit 5 = **BA** Break Active.

This bit is read/write by software, cleared by hardware after reset and set by hardware when the active level defined by the BREDGE bit is applied on the BREAK pin. It activates/deactivates the Break function.

0: Break not active

1: Break active

#### Bit 4 = **BPEN** Break Pin Enable.

This bit is read/write by software and cleared by hardware after Reset.

0: Break pin disabled

1: Break pin enabled

#### Bits 3:0 = **PWM[3:0]** Break Pattern.

These bits are read/write by software and cleared by hardware after a reset. They are used to force the four PWMx output signals into a stable state when the Break function is active and corresponding OEx bit is set.

#### **PWMx DUTY CYCLE REGISTER HIGH (DCRxH)**

Read / Write

Reset Value: 0000 0000 (00h)

| 15 |   |   |   |       |       |      | 8    |

|----|---|---|---|-------|-------|------|------|

| 0  | 0 | 0 | 0 | DCR11 | DCR10 | DCR9 | DCR8 |

#### Bits 15:12 = Reserved.

#### PWMx DUTY CYCLE REGISTER LOW (DCRxL) Read / Write

Reset Value: 0000 0000 (00h)

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| DCR7 | DCR6 | DCR5 | DCR4 | DCR3 | DCR2 | DCR1 | DCR0 |

Bits 11:0 = **DCRx[11:0]** *PWMx Duty Cycle Value* This 12-bit value is written by software. It defines the duty cycle of the corresponding PWM output signal (see Figure 4).

In PWM mode (OEx=1 in the PWMCR register) the DCR[11:0] bits define the duty cycle of the PWMx output signal (see Figure 4). In Output Compare mode, they define the value to be compared with the 12-bit upcounter value.

#### INPUT CAPTURE REGISTER HIGH (ATICRH)

Read only Reset Value: 0000 0000 (00h)

| 15 |   |   |   |       |       |      | 8    |

|----|---|---|---|-------|-------|------|------|

| 0  | 0 | 0 | 0 | ICR11 | ICR10 | ICR9 | ICR8 |

Bits 15:12 = Reserved.

#### INPUT CAPTURE REGISTER LOW (ATICRL)

Read only

7

Reset Value: 0000 0000 (00h)

|      |      |      |      |      |      |      | Ū    |

|------|------|------|------|------|------|------|------|

| ICR7 | ICR6 | ICR5 | ICR4 | ICR3 | ICR2 | ICR1 | ICR0 |

Λ

#### SERIAL PERIPHERAL INTERFACE (cont'd)

#### 11.4.3.1 Functional Description

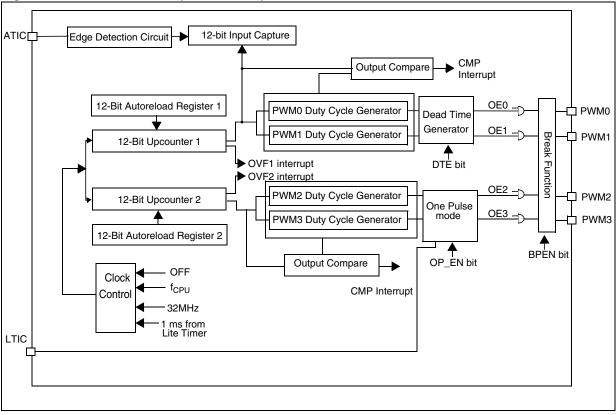

A basic example of interconnections between a single master and a single slave is illustrated in Figure 2.

The MOSI pins are connected together and the MISO pins are connected together. In this way data is transferred serially between master and slave (most significant bit first).

The communication is always initiated by the master. When the master device transmits data to a slave device via MOSI pin, the slave device responds by sending data to the master device via the MISO pin. This implies full duplex communication with both data out and data in synchronized with the same clock signal (which is provided by the master device via the SCK pin).

To use a single data line, the MISO and MOSI pins must be connected at each node (in this case only simplex communication is possible).

Four possible data/clock timing relationships may be chosen (see Figure 5 on page 7) but master and slave must be programmed with the same timing mode.

#### Figure 54. Single Master/ Single Slave Application

#### SERIAL PERIPHERAL INTERFACE (cont'd)

#### 11.4.5 Error Flags

#### 11.4.5.1 Master Mode Fault (MODF)

Master mode fault occurs when the master device's SS pin is pulled low.

When a Master mode fault occurs:

- The MODF bit is set and an SPI interrupt request is generated if the SPIE bit is set.

- The SPE bit is reset. This blocks all output from the device and disables the SPI peripheral.

- The MSTR bit is reset, thus forcing the device into slave mode.

Clearing the MODF bit is done through a software sequence:

1. A read access to the SPICSR register while the MODF bit is set.

2. A write to the SPICR register.

**Notes:** To avoid any conflicts in an application with multiple slaves, the SS pin must be pulled high during the MODF bit clearing sequence. The SPE and MSTR bits may be restored to their original state during or after this clearing sequence.

Hardware does not allow the user to set the SPE and MSTR bits while the MODF bit is set except in the MODF bit clearing sequence.

In a slave device, the MODF bit can not be set, but in a multimaster configuration the device can be in slave mode with the MODF bit set.

The MODF bit indicates that there might have been a multimaster conflict and allows software to handle this using an interrupt routine and either perform a reset or return to an application default state.

#### 11.4.5.2 Overrun Condition (OVR)

An overrun condition occurs when the master device has sent a data byte and the slave device has not cleared the SPIF bit issued from the previously transmitted byte.

When an Overrun occurs:

- The OVR bit is set and an interrupt request is generated if the SPIE bit is set.

In this case, the receiver buffer contains the byte sent after the SPIF bit was last cleared. A read to the SPIDR register returns this byte. All other bytes are lost.

The OVR bit is cleared by reading the SPICSR register.

#### 11.4.5.3 Write Collision Error (WCOL)

A write collision occurs when the software tries to write to the SPIDR register while a data transfer is taking place with an external device. When this happens, the transfer continues uninterrupted and the software write will be unsuccessful.

Write collisions can occur both in master and slave mode. See also Section 0.1.3.2 Slave Select Management.

**Note:** A "read collision" will never occur since the received data byte is placed in a buffer in which access is always synchronous with the CPU operation.

The WCOL bit in the SPICSR register is set if a write collision occurs.

No SPI interrupt is generated when the WCOL bit is set (the WCOL bit is a status flag only).

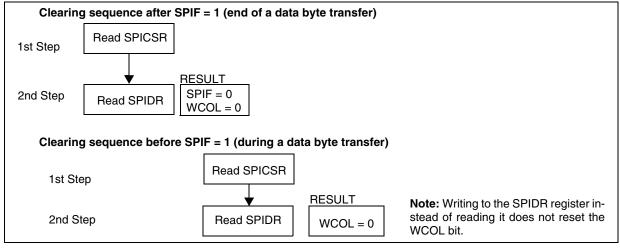

Clearing the WCOL bit is done through a software sequence (see Figure 6).

#### Figure 58. Clearing the WCOL Bit (Write Collision Flag) Software Sequence

#### ANALOG COMPARATOR (Cont'd)

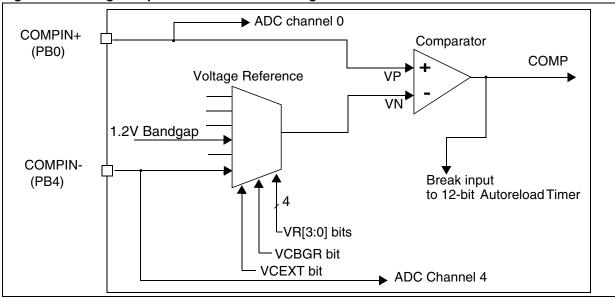

#### Figure 61. Analog Comparator and Internal Voltage Reference

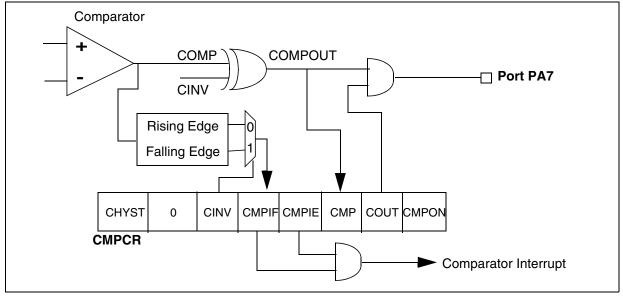

#### Figure 62. Analog Comparator

**\$7**

#### ST7 ADDRESSING MODES (cont'd)

#### 12.1.6 Indirect Indexed (Short, Long)

This is a combination of indirect and short indexed addressing modes. The operand is referenced by its memory address, which is defined by the unsigned addition of an index register value (X or Y) with a pointer value located in memory. The pointer address follows the opcode.

The indirect indexed addressing mode consists of two submodes:

#### Indirect Indexed (Short)

The pointer address is a byte, the pointer size is a byte, thus allowing 00 - 1FE addressing space, and requires 1 byte after the opcode.

#### Indirect Indexed (Long)

The pointer address is a byte, the pointer size is a word, thus allowing 64 Kbyte addressing space, and requires 1 byte after the opcode.

# Table 23. InstructionsSupportingDirect,Indexed,IndirectandIndirectIndexedAddressingModesAddressingAddressingAddressing

| Long and Short<br>Instructions | Function                                        |

|--------------------------------|-------------------------------------------------|

| LD                             | Load                                            |

| CP                             | Compare                                         |

| AND, OR, XOR                   | Logical Operations                              |

| ADC, ADD, SUB, SBC             | Arithmetic Addition/subtrac-<br>tion operations |

| BCP                            | Bit Compare                                     |

| Short Instructions Only    | Function                          |

|----------------------------|-----------------------------------|

| CLR                        | Clear                             |

| INC, DEC                   | Increment/Decrement               |

| TNZ                        | Test Negative or Zero             |

| CPL, NEG                   | 1 or 2 Complement                 |

| BSET, BRES                 | Bit Operations                    |

| BTJT, BTJF                 | Bit Test and Jump Opera-<br>tions |

| SLL, SRL, SRA, RLC,<br>RRC | Shift and Rotate Operations       |

| SWAP                       | Swap Nibbles                      |

| CALL, JP                   | Call or Jump subroutine           |

#### 12.1.7 Relative Mode (Direct, Indirect)

This addressing mode is used to modify the PC register value by adding an 8-bit signed offset to it.

| Available Relative Direct/<br>Indirect Instructions | Function         |

|-----------------------------------------------------|------------------|

| JRxx                                                | Conditional Jump |

| CALLR                                               | Call Relative    |

The relative addressing mode consists of two submodes:

#### **Relative (Direct)**

The offset follows the opcode.

#### **Relative (Indirect)**

The offset is defined in memory, of which the address follows the opcode.

# **13 ELECTRICAL CHARACTERISTICS**

#### **13.1 PARAMETER CONDITIONS**

Unless otherwise specified, all voltages are referred to  $\ensuremath{\mathsf{V}_{SS}}\xspace.$

#### 13.1.1 Minimum and Maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A=25^{\circ}C$  and  $T_A=T_Amax$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\Sigma$ ).

#### 13.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A{=}25^\circ\text{C},~V_{DD}{=}5V$  (for the  $4.5V{\leq}V_{DD}{\leq}5.5V$  voltage range) and  $V_{DD}{=}3.3V$  (for the  $3V{\leq}V_{DD}{\leq}3.6V$  voltage range). They are given only as design guidelines and are not tested.

#### 13.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

#### 13.1.4 Loading capacitor

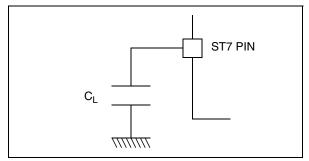

The loading conditions used for pin parameter measurement are shown in Figure 63.

#### Figure 63. Pin loading conditions

#### 13.1.5 Pin input voltage

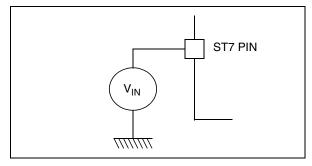

The input voltage measurement on a pin of the device is described in Figure 64.

#### Figure 64. Pin input voltage

#### 13.4.2 On-chip peripherals

| Symbol                    | Parameter                                             | Сог                    | nditions              | Тур  | Unit |

|---------------------------|-------------------------------------------------------|------------------------|-----------------------|------|------|

| I <sub>DD(AT)</sub> 12-bi | 12-bit Auto-Reload Timer supply current <sup>1)</sup> | f <sub>CPU</sub> =4MHz | V <sub>DD</sub> =3.0V | 150  |      |

|                           |                                                       | f <sub>CPU</sub> =8MHz | V <sub>DD</sub> =5.0V | 1000 |      |

| 1                         | SPI supply current <sup>2)</sup>                      | f <sub>CPU</sub> =4MHz | V <sub>DD</sub> =3.0V | 50   | μA   |

| DD(SPI)                   |                                                       | f <sub>CPU</sub> =8MHz | V <sub>DD</sub> =5.0V | 200  | μΑ   |

| 1                         | ADC supply current when converting <sup>3)</sup>      | f <sub>ADC</sub> =4MHz | V <sub>DD</sub> =3.0V | 250  |      |

| DD(ADC)                   |                                                       | ADC-4WI12              | V <sub>DD</sub> =5.0V | 1100 |      |

#### Notes:

<u>ل</u>حک

1. Data based on a differential  $I_{DD}$  measurement between reset configuration (timer stopped) and a timer running in PWM mode at  $f_{cpu}$ =8MHz.

**2.** Data based on a differential  $I_{DD}$  measurement between reset configuration and a permanent SPI master communication (data sent equal to 55h).

3. Data based on a differential  $I_{DD}$  measurement between reset configuration and continuous A/D conversions with amplifier disabled.

#### EMC CHARACTERISTICS (Cont'd)

# 13.7.3 Absolute Maximum Ratings (Electrical Sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

#### 13.7.3.1 Electro-Static Discharge (ESD)

Electro-Static Discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). Two models can be simulated: Human Body Model and Machine Model. This test conforms to the JESD22-A114A/A115A standard.

#### Absolute Maximum Ratings

| Symbol                | Ratings                                                | Conditions            | Maximum value <sup>1)</sup> | Unit |

|-----------------------|--------------------------------------------------------|-----------------------|-----------------------------|------|

| V <sub>ESD(HBM)</sub> | Electro-static discharge voltage<br>(Human Body Model) | T <sub>A</sub> =+25°C | 8000                        | V    |

| V <sub>ESD(MM)</sub>  | Electro-static discharge voltage (Machine Model)       | T <sub>A</sub> =+25°C | 400                         | v    |

#### Note:

1. Data based on characterization results, not tested in production.

#### 13.7.3.2 Static Latch-Up

LU: 3 complementary static tests are required on 6 parts to assess the latch-up performance. A supply overvoltage (applied to each power supply pin) and a current injection (applied to each input, output and configurable I/O pin) are performed on each sample. This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

#### **Electrical Sensitivities**

| Symbol | Parameter            | Conditions                                     | Class |  |  |

|--------|----------------------|------------------------------------------------|-------|--|--|

| LU St  | tatic latch-up class | T <sub>A</sub> =+25°C<br>T <sub>A</sub> =+85°C | A     |  |  |

### I/O PORT PIN CHARACTERISTICS (Cont'd)

#### 13.8.2 Output Driving Current

Subject to general operating conditions for V<sub>DD</sub>, f<sub>CPU</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol                          | Parameter                                                                                               |                       | Conditions                                   | Min                  | Max  | Unit |

|---------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------|----------------------------------------------|----------------------|------|------|

| V <sub>OL</sub> <sup>1)</sup>   | Output low level voltage for a standard I/O pin                                                         |                       | I <sub>IO</sub> =+5mA T <sub>A</sub> ≤125°C  |                      | 1.0  | -    |

|                                 | when 8 pins are sunk at same time (see Figure 83)                                                       |                       | I <sub>IO</sub> =+2mA T <sub>A</sub> ≤125°C  |                      | 0.4  |      |

| VOL                             | Output low level voltage for a high sink I/O pin                                                        | =5V                   | $I_{IO}$ =+20mA, $T_A$ ≤125°C                |                      | 1.3  |      |

|                                 | when 4 pins are sunk at same time (see Figure 89)                                                       | V <sub>DD</sub> =5V   | I <sub>IO</sub> =+8mA T <sub>A</sub> ≤125°C  |                      | 0.75 |      |

| V 2)                            | Output high level voltage for an I/O pin                                                                | I                     | I <sub>IO</sub> =-5mA, T <sub>A</sub> ≤125°C | V <sub>DD</sub> -1.5 |      |      |

| V <sub>OH</sub> <sup>2)</sup>   | when 4 pins are sourced at same time (see Figure 95)                                                    |                       | I <sub>IO</sub> =-2mA T <sub>A</sub> ≤125°C  | V <sub>DD</sub> -0.8 |      |      |

| V <sub>OL</sub> <sup>1)3)</sup> | Output low level voltage for a standard I/O pin<br>when 8 pins are sunk at same time<br>(see Figure 82) |                       | I <sub>IO</sub> =+2mA T <sub>A</sub> ≤125°C  |                      | 0.5  |      |

|                                 | Output low level voltage for a high sink I/O pin when 4 pins are sunk at same time                      | V <sub>DD</sub> =3.3V | I <sub>IO</sub> =+8mA T <sub>A</sub> ≤125°C  |                      | 0.5  | V    |

| V <sub>OH</sub> <sup>2)3)</sup> | Output high level voltage for an I/O pin when 4 pins are sourced at same time (Figure 94)               | V <sub>DD</sub> =     | I <sub>IO</sub> =-2mA T <sub>A</sub> ≤125°C  | V <sub>DD</sub> -0.8 |      |      |

| V <sub>OL</sub> <sup>1)3)</sup> | Output low level voltage for a standard I/O pin<br>when 8 pins are sunk at same time<br>(see Figure 87) |                       | I <sub>IO</sub> =+2mA T <sub>A</sub> ≤125°C  |                      | 0.6  |      |

|                                 | Output low level voltage for a high sink I/O pin when 4 pins are sunk at same time                      | 7                     | I <sub>IO</sub> =+8mA T <sub>A</sub> ≤125°C  |                      | 0.6  |      |

| V <sub>OH</sub> <sup>2)3)</sup> | Output high level voltage for an I/O pin<br>when 4 pins are sourced at same time<br>(see Figure 101)    | V <sub>DD</sub> =2.7  | I <sub>IO</sub> =-2mA T <sub>A</sub> ≤125°C  | V <sub>DD</sub> -0.9 |      |      |

#### Notes:

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in Section 13.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. The I<sub>IO</sub> current sourced must always respect the absolute maximum rating specified in Section 13.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

**47/**

3. Not tested in production, based on characterization results.

#### PACKAGE CHARACTERISTICS (Cont'd)

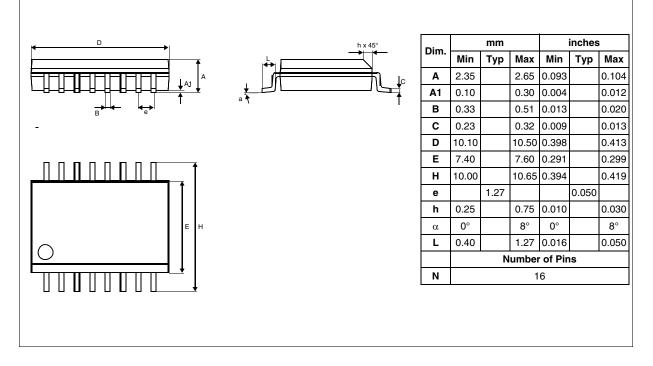

#### Figure 114. 16-Pin Plastic Small Outline Package, 300-mil Width

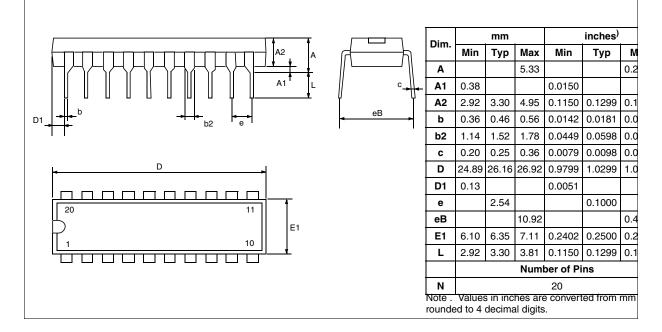

#### Figure 115. 20-Pin Plastic Dual In-Line Package, 300-mil Width

57/

# **15 DEVICE CONFIGURATION AND ORDERING INFORMATION**

Each device is available for production in user programmable versions (FLASH).

#### **15.1 OPTION BYTES**

The two option bytes allow the hardware configuration of the microcontroller to be selected.

The option bytes can be accessed only in programming mode (for example using a standard ST7 programming tool).

#### **OPTION BYTE 0**

5/

OPT7 = Reserved, must always be 1.

OPT6 = **PKG** *Package selection* 0: 16-pin package 1: 20-pin package

#### OPT5:4 = **CLKSEL** *Clock Source Selection*

When the internal RC oscillator is not selected (Option OSC=1), these option bits select the clock source: resonator oscillator or external clock

| Clock Sou              | urce   | Port C                               | CLKSEL |   |  |

|------------------------|--------|--------------------------------------|--------|---|--|

| Resonator              |        | Ext. Osc Disabled/<br>Port C Enabled | 0      | 0 |  |

| Ext.                   | on PB4 | Ext. Osc Enabled/                    | 0      | 1 |  |

| Clock source:<br>CLKIN | on PC0 | Port C Disabled                      | 1      | 1 |  |

| Reserve                | ed     |                                      | 1      | 0 |  |

**Note:** When the internal RC oscillator is selected, the CLKSEL option bits must be kept at their default value in order to select the 256 clock cycle delay (see Section 7.5).

ST7FLITE1xB devices are shipped to customers with a default program memory content (FFh). This implies that FLASH devices have to be configured by the customer using the Option Bytes.

#### OPT3:2 = SEC[1:0] Sector 0 size definition

These option bits indicate the size of sector 0 according to the following table.

| Sector 0 Size | SEC1 | SEC0 |

|---------------|------|------|

| 0.5k          | 0    | 0    |

| 1k            | 0    | 1    |

| 2k            | 1    | 0    |

| 4k            | 1    | 1    |

#### OPT1 = **FMP\_R** Read-out protection

Readout protection, when selected provides a protection against program memory content extraction and against write access to Flash memory. Erasing the option bytes when the FMP\_R option is selected will cause the whole memory to be erased first and the device can be reprogrammed. Refer to the ST7 Flash Programming Reference Manual and section 4.5 on page 14 for more details

0: Read-out protection off

1: Read-out protection on

#### OPT0 = FMP\_W FLASH write protection

This option indicates if the FLASH program memory is write protected.

**Warning:** When this option is selected, the program memory (and the option bit itself) can never be erased or programmed again.

0: Write protection off

1: Write protection on

|                  | OPTION BYTE 0 |     |     |     |      |      |          |          | OPTION BYTE 1 |            |              |     |      |      |           |             |

|------------------|---------------|-----|-----|-----|------|------|----------|----------|---------------|------------|--------------|-----|------|------|-----------|-------------|

|                  | 7             |     |     |     |      |      |          | 0        | 7             |            |              |     | 0    |      |           |             |

|                  | Res.          | PKG | CLK | SEL | SEC1 | SEC0 | FMP<br>R | FMP<br>W | PLL<br>x4x8   | PLL<br>OFF | PLL32<br>OFF | osc | LVD1 | LVD0 | WDG<br>SW | WDG<br>HALT |

| Default<br>Value | 1             | 1   | 1   | 1   | 0    | 1    | 0        | 0        | 1             | 1          | 1            | 0   | 1    | 1    | 1         | 1           |