Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | SPI                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 17                                                                     |

| Program Memory Size        | 2KB (2K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 128 x 8                                                                |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 7x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Through Hole                                                           |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7flit19bf0b6 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **3 REGISTER & MEMORY MAP**

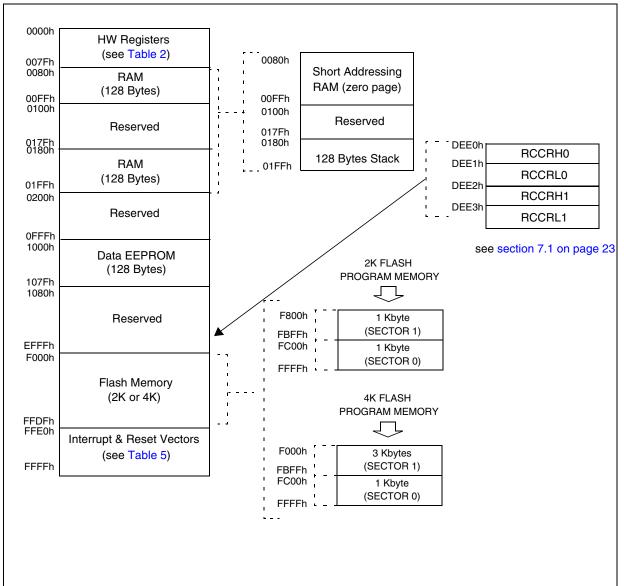

As shown in Figure 5, the MCU is capable of addressing 64K bytes of memories and I/O registers.

The available memory locations consist of 128 bytes of register locations, 256 bytes of RAM, 128 bytes of data EEPROM and up to 4 Kbytes of flash program memory. The RAM space includes up to 128 bytes for the stack from 180h to 1FFh.

The highest address bytes contain the user reset and interrupt vectors.

The Flash memory contains two sectors (see Figure 5) mapped in the upper part of the ST7 ad-

dressing space so the reset and interrupt vectors are located in Sector 0 (F000h-FFFFh).

The size of Flash Sector 0 and other device options are configurable by Option byte (refer to section 15.1 on page 149).

**IMPORTANT:** Memory locations marked as "Reserved" must never be accessed. Accessing a reserved area can have unpredictable effects on the device.

# Figure 5. Memory Map

| Address                                                     | Block               | Register Label                                                | Register Name                                                                                                                                                                                        | Reset Status                                  | Remarks                                |

|-------------------------------------------------------------|---------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------|

| 0002Fh                                                      | FLASH               | FCSR                                                          | Flash Control/Status Register                                                                                                                                                                        | 00h                                           | R/W                                    |

| 00030h                                                      | EEPROM              | EECSR                                                         | Data EEPROM Control/Status Register                                                                                                                                                                  | 00h                                           | R/W                                    |

| 0031h<br>0032h<br>0033h                                     | SPI                 | SPIDR<br>SPICR<br>SPICSR                                      | SPI Data I/O Register<br>SPI Control Register<br>SPI Control Status Register                                                                                                                         | xxh<br>0xh<br>00h                             | R/W<br>R/W<br>R/W                      |

| 0034h<br>0035h<br>0036h                                     | ADC                 | ADCCSR<br>ADCDRH<br>ADCDRL                                    | A/D Control Status Register<br>A/D Data Register High<br>A/D Amplifier Control/Data Low Register                                                                                                     | 00h<br>xxh<br>0xh                             | R/W<br>Read Only<br>R/W                |

| 0037h                                                       | ITC                 | EICR                                                          | External Interrupt Control Register                                                                                                                                                                  | 00h                                           | R/W                                    |

| 0038h                                                       | MCC                 | MCCSR                                                         | Main Clock Control/Status Register                                                                                                                                                                   | 00h                                           | R/W                                    |

| 0039h<br>003Ah                                              | Clock and<br>Reset  | RCCR<br>SICSR                                                 | RC oscillator Control Register<br>System Integrity Control/Status Register                                                                                                                           | FFh<br>0110 0xx0b                             | R/W<br>R/W                             |

| 003Bh                                                       | PLL clock<br>select | PLLTST                                                        | PLL test register                                                                                                                                                                                    | 00h                                           | R/W                                    |

| 003Ch                                                       | ITC                 | EISR                                                          | External Interrupt Selection Register                                                                                                                                                                | 0Ch                                           | R/W                                    |

| 003Dh to<br>0048h                                           |                     |                                                               | Reserved area (12 bytes)                                                                                                                                                                             |                                               | I                                      |

| 0049h<br>004Ah                                              | AWU                 | AWUPR<br>AWUCSR                                               | AWU Prescaler Register<br>AWU Control/Status Register                                                                                                                                                | FFh<br>00h                                    | R/W<br>R/W                             |

| 004Bh<br>004Ch<br>004Dh<br>004Eh<br>004Fh<br>0050h<br>0051h | DM <sup>3)</sup>    | DMCR<br>DMSR<br>DMBK1H<br>DMBK1L<br>DMBK2H<br>DMBK2L<br>DMCR2 | DM Control Register<br>DM Status Register<br>DM Breakpoint Register 1 High<br>DM Breakpoint Register 1 Low<br>DM Breakpoint Register 2 High<br>DM Breakpoint Register 2 Low<br>DM Control Register 2 | 00h<br>00h<br>00h<br>00h<br>00h<br>00h<br>00h | R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W |

| 0052h to<br>007Fh                                           |                     | 1                                                             | Reserved area (46 bytes)                                                                                                                                                                             |                                               | 1                                      |

Legend: x=undefined, R/W=read/write

# Notes:

57

**1.** The contents of the I/O port DR registers are readable only in output configuration. In input configuration, the values of the I/O pins are returned instead of the DR register contents.

2. The bits associated with unavailable pins must always keep their reset value.

3. For a description of the Debug Module registers, see ICC protocol reference manual.

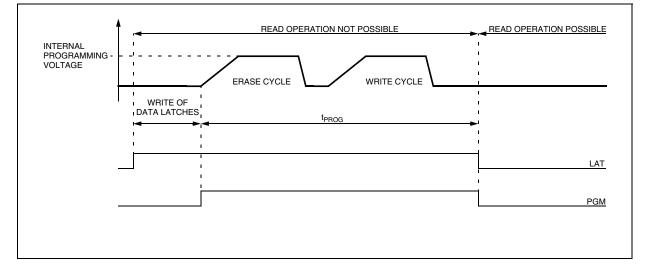

# DATA EEPROM (Cont'd)

# **5.4 POWER SAVING MODES**

#### Wait mode

The DATA EEPROM can enter WAIT mode on execution of the WFI instruction of the microcontroller or when the microcontroller enters Active-HALT mode. The DATA EEPROM will immediately enter this mode if there is no programming in progress, otherwise the DATA EEPROM will finish the cycle and then enter WAIT mode.

#### Active-Halt mode

Refer to Wait mode.

# Halt mode

The DATA EEPROM immediately enters HALT mode if the microcontroller executes the HALT instruction. Therefore the EEPROM will stop the function in progress, and data may be corrupted.

# 5.5 ACCESS ERROR HANDLING

If a read access occurs while E2LAT=1, then the data bus will not be driven.

If a write access occurs while E2LAT=0, then the data on the bus will not be latched.

If a programming cycle is interrupted (by a RESET action), the integrity of the data in memory will not be guaranteed.

#### 5.6 Data EEPROM Read-out Protection

The read-out protection is enabled through an option bit (see option byte section).

When this option is selected, the programs and data stored in the EEPROM memory are protected against read-out (including a re-write protection). In Flash devices, when this protection is removed by reprogramming the Option Byte, the entire Program memory and EEPROM is first automatically erased.

**Note:** Both Program Memory and data EEPROM are protected using the same option bit.

# Figure 10. Data EEPROM Programming Cycle

# SYSTEM INTEGRITY MANAGEMENT (Cont'd)

# 7.6.4 Register Description

# SYSTEM INTEGRITY (SI) CONTROL/STATUS REGISTER (SICSR)

#### Read/Write

Reset Value: 0110 0xx0 (6xh)

| 7          |     |     |           |        |       |      | 0     |

|------------|-----|-----|-----------|--------|-------|------|-------|

| LOCK<br>32 | CR1 | CR0 | WDG<br>RF | LOCKED | LVDRF | AVDF | AVDIE |

# Bit 7 = LOCK32 PLL 32Mhz Locked Flag

This bit is set and cleared by hardware. It is set automatically when the PLL 32Mhz reaches its operating frequency

- 0: PLL32 not locked

- 1: PLL32 locked

Bits 6:5 = **CR[1:0]** *RC* Oscillator Frequency Adjustment bits

These bits, as well as CR[9:2] bits in the RCCR register must be written immediately after reset to adjust the RC oscillator frequency and to obtain an accuracy of 1%. Refer to section 7.3 on page 25.

#### Bit 4 = WDGRF Watchdog Reset flag

This bit indicates that the last Reset was generated by the Watchdog peripheral. It is set by hardware (watchdog reset) and cleared by software (reading the SICSR register or writing 0 to this bit) or by an LVD Reset (to ensure a stable cleared state of the WDGRF flag when the CPU starts). Combined with the LVDRF flag information, the flag description is given by the following table.

| RESET Sources      | LVDRF | WDGRF |

|--------------------|-------|-------|

| External RESET pin | 0     | 0     |

| Watchdog           | 0     | 1     |

| LVD                | 1     | Х     |

#### Bit 3 = LOCKED PLL Locked Flag

This bit is set and cleared by hardware. It is set automatically when the PLL reaches its operating frequency.

0: PLL not locked

1: PLL locked

#### Bit 2 = LVDRF LVD reset flag

This bit indicates that the last Reset was generated by the LVD block. It is set by hardware (LVD reset) and cleared by software (by reading). When the LVD is disabled by OPTION BYTE, the LVDRF bit value is undefined.

#### Bit 1 = **AVDF** Voltage Detector Flag

This read-only bit is set and cleared by hardware. If the AVDIE bit is set, an interrupt request is generated when the AVDF bit is set. Refer to Figure 20 and to Section 7.6.2.1 for additional details.

0: V<sub>DD</sub> over AVD threshold

1: V<sub>DD</sub> under AVD threshold

# Bit 0 = **AVDIE** Voltage Detector Interrupt Enable

This bit is set and cleared by software. It enables an interrupt to be generated when the AVDF flag is set. The pending interrupt information is automatically cleared when software enters the AVD interrupt routine.

0: AVD interrupt disabled

1: AVD interrupt enabled

# **Application notes**

The LVDRF flag is not cleared when another RE-SET type occurs (external or watchdog), the LVDRF flag remains set to keep trace of the original failure.

In this case, a watchdog reset can be detected by software while an external reset can not.

#### PLL TEST REGISTER (PLLTST)

Read/Write

Reset Value: 0000 0000 (00h)

| 7       |   |   |   |   |   |   | 0 |

|---------|---|---|---|---|---|---|---|

| PLLdiv2 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### Bit 7 : PLLdiv2 PLL clock divide by 2

This bit is read or write by software and cleared by hardware after reset. This bit will divide the PLL output clock by 2.

0 : PLL output clock

1 : Divide by 2 of PLL output clock

Refer "Clock Management Block Diagram" on page 26

**Note :** Write of this bit will be effective after 2 Tcpu cycles (if system clock is 8mhz) else 1 cycle (if system clock is 4mhz) i.e. effective time is 250ns.

Bit 6:0 : Reserved , Must always be cleared

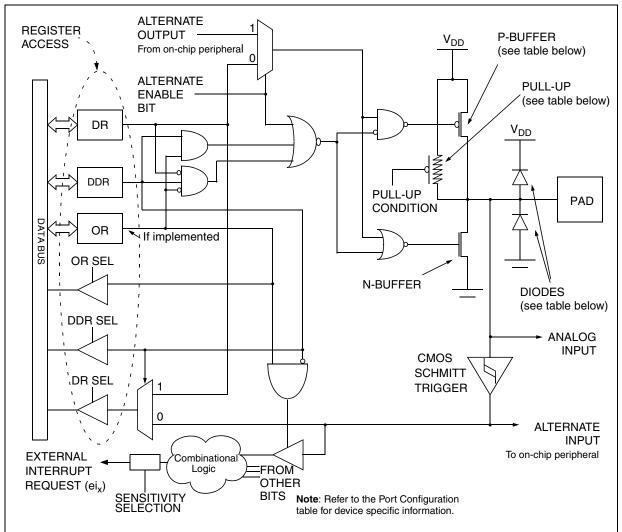

# I/O PORTS (Cont'd)

# Table 8. I/O Port Mode Options

| Configuration Mode |                                 | Dull Un | Pull-Up P-Buffer |                    | des                |

|--------------------|---------------------------------|---------|------------------|--------------------|--------------------|

|                    |                                 | Pull-Op | F-Builei         | to V <sub>DD</sub> | to V <sub>SS</sub> |

| Input              | Floating with/without Interrupt | Off     | Off              |                    |                    |

| Input              | Pull-up with/without Interrupt  | On      | OII              | On                 | On                 |

| Output             | Push-pull                       | Off     | On               | On                 | On                 |

| Output             | Open Drain (logic level)        |         | Off              |                    |                    |

Legend: Off - implemented not activated On - implemented and activated

# DUAL 12-BIT AUTORELOAD TIMER 4 (Cont'd)

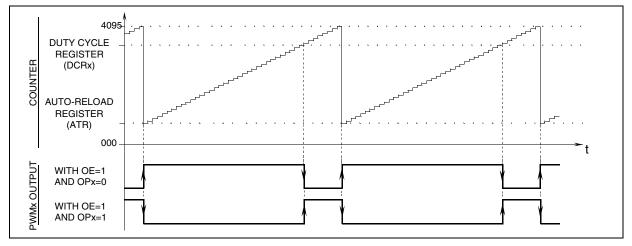

# Figure 38. PWM Function

# Figure 39. PWM Signal from 0% to 100% Duty Cycle

**لرك**ا

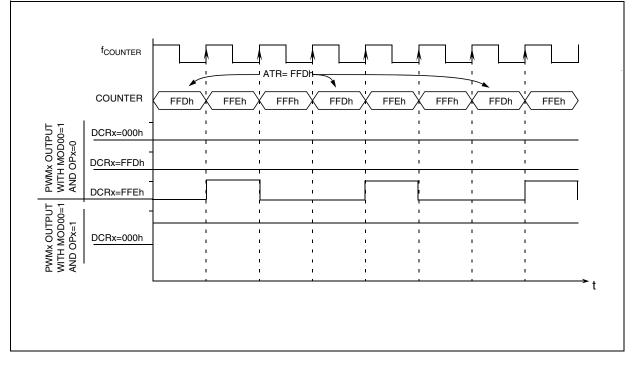

### Figure 49. Dynamic DCR2/3 update in One Pulse Mode

57

# ST7LITE1xB

| Address<br>(Hex.) | Register<br>Label      | 7      | 6      | 5    | 4      | 3          | 2          | 1          | 0          |

|-------------------|------------------------|--------|--------|------|--------|------------|------------|------------|------------|

| 21                | ATCSR2                 | FORCE2 | FORCE1 | ICS  | OVFIE2 | OVF2       | ENCNTR2    | TRAN2      | TRAN1      |

|                   | Reset Value            | 0      | 0      | 0    | 0      | 0          | 0          | 1          | 1          |

| 22                | BREAKCR                | BRSEL  | BREDGE | BA   | BPEN   | PWM3       | PWM2       | PWM1       | PWM0       |

|                   | Reset Value            | 0      | 0      | 0    | 0      | 0          | 0          | 0          | 0          |

| 23                | ATR2H<br>Reset Value   | 0      | 0      | 0    | 0      | ATR11<br>0 | ATR10<br>0 | ATR9<br>0  | ATR8<br>0  |

| 24                | ATR2L                  | ATR7   | ATR6   | ATR5 | ATR4   | ATR3       | ATR2       | ATR1       | ATR0       |

|                   | Reset Value            | 0      | 0      | 0    | 0      | 0          | 0          | 0          | 0          |

| 25                | <b>DTGR</b>            | DTE    | DT6    | DT5  | DT4    | DT3        | DT2        | DT1        | DT0        |

|                   | Reset Value            | 0      | 0      | 0    | 0      | 0          | 0          | 0          | 0          |

| 26                | BREAKEN<br>Reset Value | 0      | 0      | 0    | 0      | 0          | 0          | BREN2<br>1 | BREN1<br>1 |

# LITE TIMER (Cont'd)

# **11.3.3 Functional Description**

# 11.3.3.1 Timebase Counter 1

The 8-bit value of Counter 1 cannot be read or written by software. After an MCU reset, it starts incrementing from 0 at a frequency of  $f_{OSC}/32$ . An overflow event occurs when the counter rolls over from F9h to 00h. If  $f_{OSC} = 8$  MHz, then the time period between two counter overflow events is 1 ms. This period can be doubled by setting the TB bit in the LTCSR1 register.

When Counter 1 overflows, the TB1F bit is set by hardware and an interrupt request is generated if the TB1IE bit is set. The TB1F bit is cleared by software reading the LTCSR1 register.

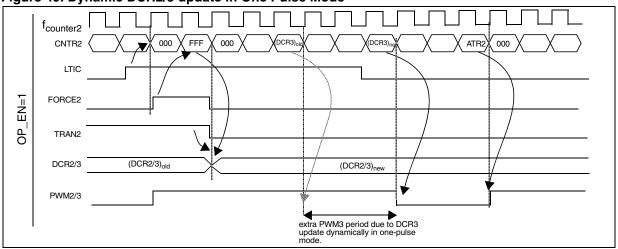

# 11.3.3.2 Input Capture

The 8-bit input capture register is used to latch the free-running upcounter (Counter 1) 1 after a rising or falling edge is detected on the LTIC pin. When an input capture occurs, the ICF bit is set and the LTICR register contains the counter 1 value. An in-

tains the data from the last input capture. Input capture is inhibited if the ICF bit is set.

# 11.3.3.3 Timebase Counter 2

Counter 2 is an 8-bit autoreload upcounter. It can be read by accessing the LTCNTR register. After an MCU reset, it increments at a frequency of  $f_{OSC}/32$  starting from the value stored in the LTARR register. A counter overflow event occurs when the counter rolls over from FFh to the LTARR reload value. Software can write a new value at any time in the LTARR register, this value will be automatically loaded in the counter when the next overflow occurs.

terrupt is generated if the ICIE bit is set. The ICF bit is cleared by reading the LTICR register.

The LTICR is a read-only register and always con-

When Counter 2 overflows, the TB2F bit in the LTCSR2 register is set by hardware and an interrupt request is generated if the TB2IE bit is set. The TB2F bit is cleared by software reading the LTCSR2 register.

LITE TIMER (Cont'd)

Bit 6 = **ICF** *Input Capture Flag* This bit is set by hardware and cleared by software by reading the LTICR register. Writing to this bit does not change the bit value. 0: No input capture 1: An input capture has occurred

**Note:** After an MCU reset, software must initialize the ICF bit by reading the LTICR register

Bit 5 = **TB** *Timebase period selection* This bit is set and cleared by software. 0: Timebase period =  $t_{OSC} * 8000 (1ms @ 8 MHz)$ 1: Timebase period =  $t_{OSC} * 16000 (2ms @ 8 MHz)$

Bit 4 = **TB1IE** *Timebase Interrupt enable* This bit is set and cleared by software. 0: Timebase (TB1) interrupt disabled 1: Timebase (TB1) interrupt enabled

Bit 3 =**TB1F** *Timebase Interrupt Flag* This bit is set by hardware and cleared by software reading the LTCSR register. Writing to this bit has no effect.

0: No counter overflow

1: A counter overflow has occurred

Bits 2:0 = Reserved

#### LITE TIMER INPUT CAPTURE REGISTER (LTICR) Read only

Reset Value: 0000 0000 (00h)

7

| ICR7 | ICR6 | ICR5 | ICR4 | ICR3 | ICR2 | ICR1 | ICR0 |

|------|------|------|------|------|------|------|------|

0

#### Bits 7:0 = ICR[7:0] Input Capture Value

These bits are read by software and cleared by hardware after a reset. If the ICF bit in the LTCSR is cleared, the value of the 8-bit up-counter will be captured when a rising or falling edge occurs on the LTIC pin.

# SERIAL PERIPHERAL INTERFACE (cont'd)

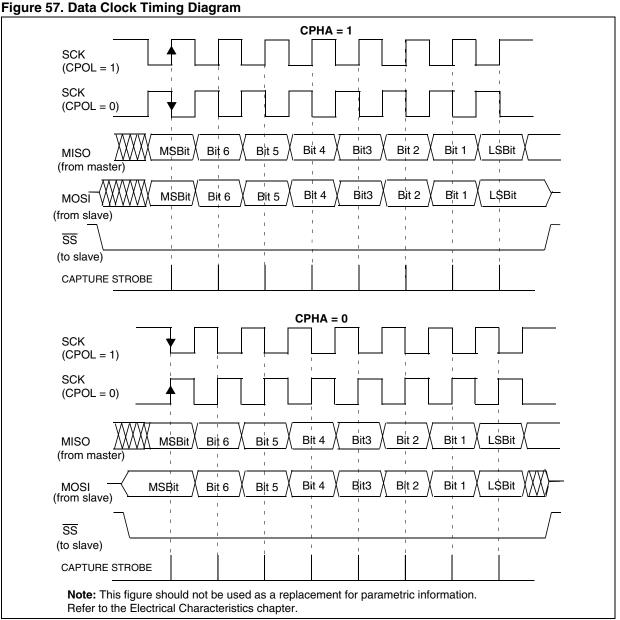

# 11.4.4 Clock Phase and Clock Polarity

Four possible timing relationships may be chosen by software, using the CPOL and CPHA bits (See Figure 5).

Note: The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL = 1 or pulling down SCK if CPOL = 0).

The combination of the CPOL clock polarity and CPHA (clock phase) bits selects the data capture clock edge.

Figure 5 shows an SPI transfer with the four combinations of the CPHA and CPOL bits. The diagram may be interpreted as a master or slave timing diagram where the SCK pin, the MISO pin and the MOSI pin are directly connected between the master and the slave device.

Note: If CPOL is changed at the communication byte boundaries, the SPI must be disabled by resetting the SPE bit.

47/

# 11.4.8 Register Description SPI CONTROL REGISTER (SPICR)

Read/Write

Reset Value: 0000 xxxx (0xh)

| 7    |     |      |      |      |      |      | 0    |

|------|-----|------|------|------|------|------|------|

| SPIE | SPE | SPR2 | MSTR | CPOL | CPHA | SPR1 | SPR0 |

Bit 7 = **SPIE** Serial Peripheral Interrupt Enable This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SPI interrupt is generated whenever an End of Transfer event, Master Mode Fault or Overrun error occurs (SPIF = 1, MODF = 1 or OVR = 1 in the SPICSR register)

# Bit 6 = **SPE** Serial Peripheral Output Enable

This bit is set and cleared by software. It is also cleared by hardware when, in master mode,  $\overline{SS} = 0$  (see Section 0.1.5.1 Master Mode Fault (MODF)). The SPE bit is cleared by reset, so the SPI peripheral is not initially connected to the external pins.

0: I/O pins free for general purpose I/O

1: SPI I/O pin alternate functions enabled

#### Bit 5 = **SPR2** Divider Enable

This bit is set and cleared by software and is cleared by reset. It is used with the SPR[1:0] bits to set the baud rate. Refer to Table 1 SPI Master Mode SCK Frequency.

0: Divider by 2 enabled

1: Divider by 2 disabled

Note: This bit has no effect in slave mode.

#### Bit 4 = MSTR Master Mode

This bit is set and cleared by software. It is also cleared by hardware when, in master mode,  $\overline{SS} = 0$  (see Section 0.1.5.1 Master Mode Fault (MODF)).

0: Slave mode

57

1: Master mode. The function of the SCK pin changes from an input to an output and the functions of the MISO and MOSI pins are reversed.

#### Bit 3 = CPOL Clock Polarity

This bit is set and cleared by software. This bit determines the idle state of the serial Clock. The CPOL bit affects both the master and slave modes.

0: SCK pin has a low level idle state

1: SCK pin has a high level idle state

**Note**: If CPOL is changed at the communication byte boundaries, the SPI must be disabled by resetting the SPE bit.

#### Bit 2 = CPHA Clock Phase

This bit is set and cleared by software.

- 0: The first clock transition is the first data capture edge.

- 1: The second clock transition is the first capture edge.

**Note:** The slave must have the same CPOL and CPHA settings as the master.

#### Bits 1:0 = SPR[1:0] Serial Clock Frequency

These bits are set and cleared by software. Used with the SPR2 bit, they select the baud rate of the SPI serial clock SCK output by the SPI in master mode.

Note: These 2 bits have no effect in slave mode.

#### Table 16. SPI Master Mode SCK Frequency

| Serial Clock          | SPR2 | SPR1 | SPR0 |

|-----------------------|------|------|------|

| f <sub>CPU</sub> /4   | 1    |      | 0    |

| f <sub>CPU</sub> /8   | 0    | 0    | 0    |

| f <sub>CPU</sub> /16  | 0    |      | 1    |

| f <sub>CPU</sub> /32  | 1    |      | 0    |

| f <sub>CPU</sub> /64  | 0    | 1    | 0    |

| f <sub>CPU</sub> /128 | 0    |      | 1    |

# 13.3.4 Auxiliary Voltage Detector (AVD) Thresholds $T_A$ = -40 to 125°C, unless otherwise specified

| Symbol                | Parameter                                                  | Conditions                                        | Тур                  | Unit |

|-----------------------|------------------------------------------------------------|---------------------------------------------------|----------------------|------|

| V <sub>IT+(AVD)</sub> | 1=>0 AVDF flag toggle threshold<br>(V <sub>DD</sub> rise)  | High Threshold<br>Med. Threshold<br>Low Threshold | 4.50<br>4.00<br>3.35 | V    |

| V <sub>IT-(AVD)</sub> | 0=>1 AVDF flag toggle threshold<br>(V <sub>DD</sub> fall)  | High Threshold<br>Med. Threshold<br>Low Threshold | 4.40<br>3.85<br>3.20 | v    |

| V <sub>hys</sub>      | AVD voltage threshold hysteresis                           | V <sub>IT+(AVD)</sub> -V <sub>IT-(AVD)</sub>      | 170                  | mV   |

| ΔV <sub>IT-</sub>     | Voltage drop between AVD flag set and LVD reset activation | V <sub>DD</sub> fall                              | 0.15                 | V    |

# 13.3.5 Internal RC Oscillator and PLL

The ST7 internal clock can be supplied by an internal RC oscillator and PLL (selectable by option byte).

| Symbol                 | Parameter                                | Conditions                                                            | Min | Тур | Max | Unit                                                   |

|------------------------|------------------------------------------|-----------------------------------------------------------------------|-----|-----|-----|--------------------------------------------------------|

| V <sub>DD(RC)</sub>    | Internal RC Oscillator operating voltage | Refer to operating range                                              | 2.7 |     | 5.5 |                                                        |

| V <sub>DD(x4PLL)</sub> | x4 PLL operating voltage                 | of V <sub>DD</sub> with T <sub>A,</sub> section<br>13.3.1 on page 112 | 2.7 |     | 3.7 | v                                                      |

| V <sub>DD(x8PLL)</sub> | x8 PLL operating voltage                 |                                                                       | 3.3 |     | 5.5 |                                                        |

| <sup>t</sup> STARTUP   | PLL Startup time                         |                                                                       |     | 60  |     | PLL<br>input<br>clock<br>(f <sub>PLL</sub> )<br>cycles |

# **OPERATING CONDITIONS** (Cont'd)

The RC oscillator and PLL characteristics are temperature-dependent and are grouped in four tables. 13.3.5.1 Devices with ""6" or "3" order code suffix (tested for  $T_A = -40$  to +125°C) @  $V_{DD} = 5V$

| Symbol               | Parameter                                         | Conditions                                                                         | Min  | Тур               | Max              | Unit |

|----------------------|---------------------------------------------------|------------------------------------------------------------------------------------|------|-------------------|------------------|------|

| 4                    | Internal RC oscillator fre-                       | RCCR = FF (reset value), T <sub>A</sub> =25°C,V <sub>DD</sub> =5V                  |      | 700               |                  |      |

| f <sub>RC</sub>      | quency <sup>1)</sup>                              | RCCR = RCCR0 <sup>2</sup> ),T <sub>A</sub> =25°C,V <sub>DD</sub> =5V               | 992  | 1000              | 1008             | kHz  |

|                      |                                                   | T <sub>A</sub> =25°C,V <sub>DD</sub> =5V                                           | -0.8 |                   | +0.8             | %    |

|                      |                                                   | T <sub>A</sub> =25°C, V <sub>DD</sub> =4.5 to 5.5V <sup>3)</sup>                   | -1   |                   | +1               | %    |

|                      | Accuracy of Internal RC                           | T <sub>A</sub> =25°C to +85°C,V <sub>DD</sub> =5V                                  | -3   |                   | +3               | %    |

| ACC <sub>RC</sub>    | oscillator with                                   | $T_A=25^{\circ}C$ to +85°C, $V_{DD}=4.5$ to 5.5 $V^{3}$                            | -3.5 |                   | +3.5             | %    |

|                      | RCCR=RCCR0 <sup>2)</sup>                          | T <sub>A</sub> =85°C to +125°C,V <sub>DD</sub> =5V                                 | -3.5 |                   | +5               | %    |

|                      |                                                   | $T_A = 85^{\circ}C \text{ to } + 125^{\circ}C, V_{DD} = 4.5 \text{ to } 5.5V^{3)}$ | -3.5 |                   | +6               | %    |

|                      |                                                   | $T_A = -40 \text{ to } +25^{\circ}\text{C}, V_{DD} = 5V^{3)}$                      | -3   |                   | +7               | %    |

| I <sub>DD(RC)</sub>  | RC oscillator current con-<br>sumption            | T <sub>A</sub> =25°C,V <sub>DD</sub> =5V                                           |      | 600 <sup>3)</sup> |                  | μA   |

| t <sub>su(RC)</sub>  | RC oscillator setup time                          | T <sub>A</sub> =25°C,V <sub>DD</sub> =5V                                           |      |                   | 10 <sup>2)</sup> | μS   |

| f <sub>PLL</sub>     | x8 PLL input clock                                |                                                                                    |      | 1 <sup>3)</sup>   |                  | MHz  |

| t <sub>LOCK</sub>    | PLL Lock time <sup>5)</sup>                       |                                                                                    |      | 2                 |                  | ms   |

| t <sub>STAB</sub>    | PLL Stabilization time <sup>5)</sup>              |                                                                                    |      | 4                 |                  | ms   |

| 100                  |                                                   | f <sub>RC</sub> = 1MHz@T <sub>A</sub> =25°C,V <sub>DD</sub> =4.5 to 5.5V           |      | 0.1 <sup>4)</sup> |                  | %    |

| ACC <sub>PLL</sub>   | x8 PLL Accuracy                                   | $f_{RC} = 1MHz@T_A=-40 \text{ to } +85^{\circ}C,V_{DD}=5V$                         |      | 0.1 <sup>4)</sup> |                  | %    |

| t <sub>w(JIT)</sub>  | PLL jitter period 6)                              | f <sub>RC</sub> = 1MHz                                                             |      | 120               |                  | μs   |

| JIT <sub>PLL</sub>   | PLL jitter (∆f <sub>CPU</sub> /f <sub>CPU</sub> ) |                                                                                    |      | 1 <sup>7)</sup>   |                  | %    |

| I <sub>DD(PLL)</sub> | PLL current consumption                           | T <sub>A</sub> =25°C                                                               |      | 600 <sup>3)</sup> |                  | μA   |

#### Notes:

5/

1. If the RC oscillator clock is selected, to improve clock stability and frequency accuracy, it is recommended to place a decoupling capacitor, typically 100nF, between the  $V_{DD}$  and  $V_{SS}$  pins as close as possible to the ST7 device.

2. See "INTERNAL RC OSCILLATOR ADJUSTMENT" on page 23

3. Data based on characterization results, not tested in production

4. Averaged over a 4ms period. After the LOCKED bit is set, a period of t<sub>STAB</sub> is required to reach ACC<sub>PLL</sub> accuracy.

- 5. After the LOCKED bit is set  $ACC_{PLL}$  is max. 10% until  $t_{STAB}$  has elapsed. See Figure 13 on page 24.

- 6. This period is the phase servo loop period. During this period, the frequency remains unchanged.

7. Guaranteed by design.

# CLOCK AND TIMING CHARACTERISTICS (Cont'd)

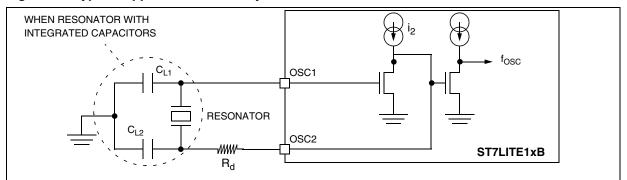

# 13.5.4 Crystal and Ceramic Resonator Oscillators

The ST7 internal clock can be supplied with ten different Crystal/Ceramic resonator oscillators. All the information given in this paragraph are based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal/ceramic resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol                             | Parameter                                                                                                                      | Conditions | Min | Тур         | Max | Unit |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------|-----|-------------|-----|------|

| f <sub>CrOSC</sub>                 | Crystal Oscillator Frequency                                                                                                   |            | 2   |             | 16  | MHz  |

| C <sub>L1</sub><br>C <sub>L2</sub> | Recommended load capacitance ver-<br>sus equivalent serial resistance of the<br>crystal or ceramic resonator (R <sub>S</sub> ) |            | Se  | e table bel | low | pF   |

| Supplier | f <sub>CrOSC</sub> | Туріса             | I Ceramic Resonators <sup>1)</sup> | CL1 <sup>3)</sup> | CL2 <sup>3)</sup> | Rd                  | Supply Voltage | Temperature |

|----------|--------------------|--------------------|------------------------------------|-------------------|-------------------|---------------------|----------------|-------------|

| Supplier | (MHz)              | Type <sup>2)</sup> | Reference                          | [pF]              | [pF]              | <b>[</b> Ω <b>]</b> | Range [V]      | Range [°C]  |

|          | 1                  | SMD                | CSBFB1M00J58-R0                    | 220               | 220               | 2.2k                | 3.3V to 5.5V   |             |

|          | I                  | LEAD               | CSBLA1M00J58-B0                    | 220               | 220               | 2.2k                | 5.50 10 5.50   |             |

|          | 2                  | SMD                | CSTCC2M00G56Z-R0                   | (47)              | (47)              | 0                   |                |             |

|          | 4                  | SMD                | CSTCR4M00G53Z-R0                   | (15)              | (15)              | 0                   | 3.0V to 5.5V   | -40 to 85   |

| Murata   |                    | LEAD               | CSTLS4M00G53Z-B0                   | (15)              | (15)              | 0                   | 3.00 10 3.30   |             |

| Mur      | 8                  | SMD                | CSTCE8M00G52Z-R0                   | (10)              | (10)              | 0                   |                |             |

|          | 0                  | LEAD               | CSTLS8M00G53Z-B0                   | (15)              | (15)              | 0                   |                |             |

|          | 12                 | SMD                | CSTCE12M0G52Z-R0                   | (10)              | (10)              | 0                   |                |             |

|          | 16                 | SMD                | CSTCE16M0V51Z-R0                   | (5)               | (5)               | 0                   | 3.3V to 5.5V   |             |

|          | 10                 | LEAD               | CSTLS16M0X51Z-B0                   | (5)               | (5)               | 0                   |                |             |

#### Notes:

57

1. Resonator characteristics given by the ceramic resonator manufacturer. For more information on these resonators, please consult www.murata.com

2. SMD = [-R0: Plastic tape package (Ø =180mm)]

LEAD = [-B0: Bulk]

3. () means load capacitor built in resonator

#### Figure 79. Typical Application with a Crystal or Ceramic Resonator

# **13.6 MEMORY CHARACTERISTICS**

$T_A = -40^{\circ}C$  to 125°C, unless otherwise specified

# 13.6.1 RAM and Hardware Registers

| Symbol          | Parameter                         | Conditions           | Min | Тур | Max | Unit |

|-----------------|-----------------------------------|----------------------|-----|-----|-----|------|

| V <sub>RM</sub> | Data retention mode <sup>1)</sup> | HALT mode (or RESET) | 1.6 |     |     | V    |

### 13.6.2 FLASH Program Memory

| Symbol            | Parameter                                     | Conditions                                                                    | Min | Тур  | Max  | Unit   |

|-------------------|-----------------------------------------------|-------------------------------------------------------------------------------|-----|------|------|--------|

| V <sub>DD</sub>   | Operating voltage for Flash write/erase       | Refer to operating range of $V_{DD}$ with $T_{A,}$ section 13.3.1 on page 112 | 2.7 |      | 5.5  | V      |

|                   | Programming time for 1~32 bytes <sup>2)</sup> | T <sub>A</sub> =-40 to +125°C                                                 |     | 5    | 10   | ms     |

| t <sub>prog</sub> | Programming time for 1.5 kBytes               | T <sub>A</sub> =+25°C                                                         |     | 0.24 | 0.48 | s      |

| t <sub>RET</sub>  | Data retention 4)                             | T <sub>A</sub> =+55°C <sup>3)</sup>                                           | 20  |      |      | years  |

| N <sub>RW</sub>   | Write erase cycles                            | T <sub>A</sub> =+25°C                                                         | 10K |      |      | cycles |

|                   | Quarky summer (f)                             | Read / Write / Erase modes $f_{CPU} = 8MHz$ , $V_{DD} = 5.5V$                 |     |      | 2.6  | mA     |

| IDD               | Supply current <sup>6)</sup>                  | No Read/No Write Mode                                                         |     |      | 100  | μΑ     |

|                   |                                               | Power down mode / HALT                                                        |     | 0    | 0.1  | μA     |

# 13.6.3 EEPROM Data Memory

| Symbol            | Parameter                                | Conditions                                                                    | Min  | Тур | Max | Unit   |

|-------------------|------------------------------------------|-------------------------------------------------------------------------------|------|-----|-----|--------|

| V <sub>DD</sub>   | Operating voltage for EEPROM write/erase | Refer to operating range of $V_{DD}$ with $T_{A,}$ section 13.3.1 on page 112 | 2.7  |     | 5.5 | V      |

| t <sub>prog</sub> | Programming time for 1~32 bytes          | T <sub>A</sub> =-40 to +125°C                                                 |      | 5   | 10  | ms     |

| t <sub>ret</sub>  | Data retention 4)                        | T <sub>A</sub> =+55°C <sup>3)</sup>                                           | 20   |     |     | years  |

| N <sub>RW</sub>   | Write erase cycles                       | T <sub>A</sub> =+25°C                                                         | 300K |     |     | cycles |

#### Notes:

**1.** Minimum  $V_{DD}$  supply voltage without losing data stored in RAM (in HALT mode or under RESET) or in hardware registers (only in HALT mode). Guaranteed by construction, not tested in production.

2. Up to 32 bytes can be programmed at a time.

**3.** The data retention time increases when the  $T_A$  decreases.

- 4. Data based on reliability test results and monitored in production.

- 5. Data based on characterization results, not tested in production.

6. Guaranteed by Design. Not tested in production.

# CONTROL PIN CHARACTERISTICS (Cont'd)

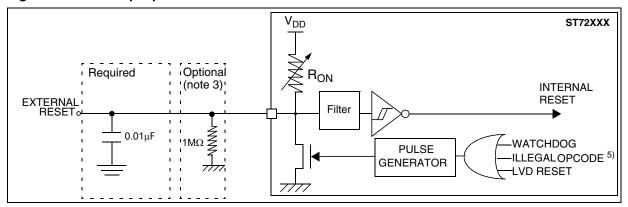

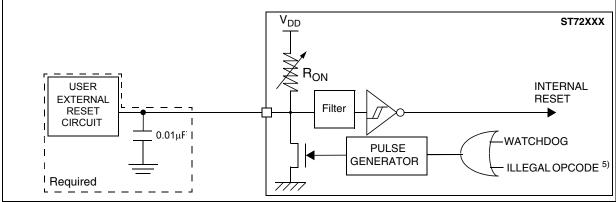

# Figure 105. RESET pin protection when LVD is enabled.<sup>1)2)3)4)</sup>

Figure 106. RESET pin protection when LVD is disabled.<sup>1)</sup>

#### Note 1:

- The reset network protects the device against parasitic resets.

- The output of the external reset circuit must have an open-drain output to drive the ST7 reset pad. Otherwise the device can be damaged when the ST7 generates an internal reset (LVD or watchdog).

- Whatever the reset source is (internal or external), the user must ensure that the level on the RESET pin can go below the V<sub>IL</sub> max. level specified in section 13.9.1 on page 135. Otherwise the reset will not be taken into account internally.

- Because the reset circuit is designed to allow the internal RESET to be output in the RESET pin, the user must ensure that the current sunk on the RESET pin is less than the absolute maximum value specified for I<sub>INJ(RESET)</sub> in section 13.2.2 on page 111.

**Note 2:** When the LVD is enabled, it is recommended not to connect a pull-up resistor or capacitor. A 10nF pull-down capacitor is required to filter noise on the reset line.

**Note 3:** In case a capacitive power supply is used, it is recommended to connect a 1M $\Omega$  pull-down resistor to the RESET pin to discharge any residual voltage induced by the capacitive effect of the power supply (this will add 5µA to the power consumption of the MCU).

Note 4: Tips when using the LVD:

- 1. Check that all recommendations related to ICCCLK and reset circuit have been applied (see caution in Table 1 on page 7 and notes above)

- 2. Check that the power supply is properly decoupled (100nF + 10µF close to the MCU). Refer to AN1709 and AN2017. If this cannot be done, it is recommended to put a 100nF + 1MΩ pull-down on the RESET pin.

- 3. The capacitors connected on the RESET pin and also the power supply are key to avoid any start-up marginality. <u>In most</u> cases, steps 1 and 2 above are sufficient for a robust solution. Otherwise: replace 10nF pull-down on the RESET pin with a 5µF to 20µF capacitor."

Note 5: Please refer to "Illegal Opcode Reset" on page 107 for more details on illegal opcode reset conditions.

# **14.2 SOLDERING INFORMATION**

In accordance with the RoHS European directive, all STMicroelectronics packages have been converted to lead-free technology, named ECO-PACK<sup>TM</sup>.

- ECOPACK<sup>TM</sup> packages are qualified according to the JEDEC STD-020C compliant soldering profile.

- Detailed information on the STMicroelectronics ECOPACK<sup>TM</sup> transition program is available on www.st.com/stonline/leadfree/, with specific technical Application notes covering the main technical aspects related to lead-free conversion (AN2033, AN2034, AN2035, AN2036).

#### Backward and forward compatibility:

The main difference between Pb and Pb-free soldering process is the temperature range.

- ECOPACK<sup>TM</sup> TQFP, SDIP, SO and QFN20 packages are fully compatible with Lead (Pb) containing soldering process (see application note AN2034)

- TQFP, SDIP and SO Pb-packages are compatible with Lead-free soldering process, nevertheless it's the customer's duty to verify that the Pb-packages maximum temperature (mentioned on the Inner box label) is compatible with their Lead-free soldering temperature.

#### Table 25. Soldering Compatibility (wave and reflow soldering process)

| Package     | Plating material devices       | Pb solder paste | Pb-free solder paste |

|-------------|--------------------------------|-----------------|----------------------|

| SDIP & PDIP | Sn (pure Tin)                  | Yes             | Yes *                |

| QFN         | Sn (pure Tin)                  | Yes             | Yes *                |

| TQFP and SO | NiPdAu (Nickel-palladium-Gold) | Yes             | Yes *                |

\* Assemblers must verify that the Pb-package maximum temperature (mentioned on the Inner box label) is compatible with their Lead-free soldering process.

# **15 DEVICE CONFIGURATION AND ORDERING INFORMATION**

Each device is available for production in user programmable versions (FLASH).

# **15.1 OPTION BYTES**

The two option bytes allow the hardware configuration of the microcontroller to be selected.

The option bytes can be accessed only in programming mode (for example using a standard ST7 programming tool).

# **OPTION BYTE 0**

5/

OPT7 = Reserved, must always be 1.

OPT6 = **PKG** *Package selection* 0: 16-pin package 1: 20-pin package

# OPT5:4 = **CLKSEL** *Clock Source Selection*

When the internal RC oscillator is not selected (Option OSC=1), these option bits select the clock source: resonator oscillator or external clock

| Clock Sou              | urce   | Port C                               | CLK | SEL |

|------------------------|--------|--------------------------------------|-----|-----|

| Resonator              |        | Ext. Osc Disabled/<br>Port C Enabled | 0   | 0   |

| Ext.                   | on PB4 | Ext. Osc Enabled/                    | 0 1 |     |

| Clock source:<br>CLKIN | on PC0 | Port C Disabled                      | 1   |     |

| Reserve                | ed     |                                      | 1   | 0   |

**Note:** When the internal RC oscillator is selected, the CLKSEL option bits must be kept at their default value in order to select the 256 clock cycle delay (see Section 7.5).

ST7FLITE1xB devices are shipped to customers with a default program memory content (FFh). This implies that FLASH devices have to be configured by the customer using the Option Bytes.

# OPT3:2 = SEC[1:0] Sector 0 size definition

These option bits indicate the size of sector 0 according to the following table.

| Sector 0 Size | SEC1 | SEC0 |

|---------------|------|------|

| 0.5k          | 0    | 0    |

| 1k            | 0    | 1    |

| 2k            | 1    | 0    |

| 4k            | 1    | 1    |

# OPT1 = **FMP\_R** Read-out protection

Readout protection, when selected provides a protection against program memory content extraction and against write access to Flash memory. Erasing the option bytes when the FMP\_R option is selected will cause the whole memory to be erased first and the device can be reprogrammed. Refer to the ST7 Flash Programming Reference Manual and section 4.5 on page 14 for more details

0: Read-out protection off

1: Read-out protection on

#### OPT0 = FMP\_W FLASH write protection

This option indicates if the FLASH program memory is write protected.

**Warning:** When this option is selected, the program memory (and the option bit itself) can never be erased or programmed again.

0: Write protection off

1: Write protection on

|                  |      | OPTION BYTE 0           |   |   |      |          |          |             |            |              | OF  | PTION | BYTE | 1         |             |   |

|------------------|------|-------------------------|---|---|------|----------|----------|-------------|------------|--------------|-----|-------|------|-----------|-------------|---|

|                  | 7    | 7 0                     |   |   |      |          |          | 7           |            |              |     |       |      |           | 0           |   |

|                  | Res. | es. PKG CLKSEL SEC1 SEC |   |   | SEC0 | FMP<br>R | FMP<br>W | PLL<br>x4x8 | PLL<br>OFF | PLL32<br>OFF | osc | LVD1  | LVD0 | WDG<br>SW | WDG<br>HALT |   |

| Default<br>Value | 1    | 1                       | 1 | 1 | 0    | 1        | 0        | 0           | 1          | 1            | 1   | 0     | 1    | 1         | 1           | 1 |

# **15.3 DEVELOPMENT TOOLS**

Development tools for the ST7 microcontrollers include a complete range of hardware systems and software tools from STMicroelectronics and thirdparty tool suppliers. The range of tools includes solutions to help you evaluate microcontroller peripherals, develop and debug your application, and program your microcontrollers.

#### 15.3.1 Starter kits

ST offers complete, affordable **starter kits**. Starter kits are complete hardware/software tool packages that include features and samples to help you quickly start developing your application.

#### 15.3.2 Development and debugging tools

Application development for ST7 is supported by fully optimizing **C Compilers** and the **ST7 Assembler-Linker** toolchain, which are all seamlessly integrated in the ST7 integrated development environments in order to facilitate the debugging and fine-tuning of your application. The Cosmic C Compiler is available in a free version that outputs up to 16KBytes of code.

The range of hardware tools includes full-featured **ST7-EMU3 series emulators**, cost effective **ST7-DVP3 series emulators** and the low-cost **RLink** in-circuit debugger/programmer. These tools are supported by the **ST7 Toolset** from STMicroelectronics, which includes the STVD7 integrated development environment (IDE) with high-level lan-

guage debugger, editor, project manager and integrated programming interface.

#### 15.3.3 Programming tools

During the development cycle, the **ST7-DVP3** and and **ST7-EMU3 series emulators** and the **RLink** provide in-circuit programming capability for programming the Flash microcontroller on your application board.

ST also provides a low-cost dedicated in-circuit programmer, the **ST7-STICK**, as well as **ST7 Socket Boards** which provide all the sockets required for programming any of the devices in a specific ST7 sub-family on a platform that can be used with any tool with in-circuit programming capability for ST7.

For production programming of ST7 devices, ST's third-party tool partners also provide a complete range of gang and automated programming solutions, which are ready to integrate into your production environment.

# 15.3.4 Order Codes for Development and Programming Tools

Table 28 below lists the ordering codes for the ST7LITE1xB development and programming tools. For additional ordering codes for spare parts and accessories, refer to the online product selector at www.st.com/mcu.

#### 15.3.5 Order codes for ST7LITE1xB development tools

#### Table 28. Development tool order codes for the ST7LITE1xB family

| MCU                                          | In-circuit Debugge                | r, RLink Series <sup>1)</sup>      | Emula                           | ator              | Programming Tool                       |                                 |  |

|----------------------------------------------|-----------------------------------|------------------------------------|---------------------------------|-------------------|----------------------------------------|---------------------------------|--|

| ST7FLIT1xBF0<br>ST7FLIT1xBF1<br>ST7FLIT1xBY0 | Starter Kit without<br>Demo Board | Starter Kit with<br>Demo Board     | DVP Series                      | EMU Series        | In-circuit<br>Programmer               | ST Socket<br>Boards and<br>EPBs |  |

| ST7FLIT1xBY1                                 | STX-RLINK <sup>2)</sup>           | ST7FLITE-<br>SK/RAIS <sup>2)</sup> | ST7MDT10-<br>DVP3 <sup>4)</sup> | ST7MDT10-<br>EMU3 | STX-RLINK<br>ST7-STICK <sup>3)5)</sup> | ST7SB10-<br>123 <sup>3)</sup>   |  |

#### Notes:

57/

1. Available from ST or from Raisonance, www.raisonance.com

2. USB connection to PC

3. Add suffix /EU, /UK or /US for the power supply for your region

4. Includes connection kit for DIP16/SO16 only. See "How to order an EMU or DVP" in ST product and tool selection guide for connection kit ordering information

5. Parallel port connection to PC