Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Not For New Designs                                                    |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | SPI                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 17                                                                     |

| Program Memory Size        | 2KB (2K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 128 x 8                                                                |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 7x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                         |

| Supplier Device Package    | 20-50                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7flit19bf0m6 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

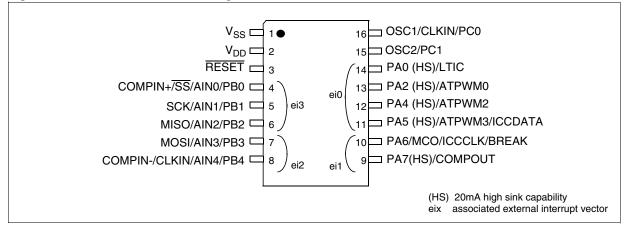

## PIN DESCRIPTION (Cont'd)

#### Figure 4. 16-Pin SO and DIP Package Pinout

## ST7LITE1xB

| Р          | in No | <b>o</b> . |                           |      | Le    | vel    |       | Po  | rt/C | Cont | rol |     |                       |                                                                                                                                                                                                                                                                                                                                                              |

|------------|-------|------------|---------------------------|------|-------|--------|-------|-----|------|------|-----|-----|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 120        | 0     | P16        | Pin Name                  | Type |       | ıt     |       | Inp | out  |      | Out | put | Main<br>Function      | Alternate Function                                                                                                                                                                                                                                                                                                                                           |

| SO20/DPI20 | QFN20 | SO16/DIP16 | FIII Name                 | Ту   | Input | Output | float | ndm | int  | ana  | ОD  | ЬΡ  | (after<br>reset)      |                                                                                                                                                                                                                                                                                                                                                              |

|            |       |            |                           |      |       | •      |       |     | •    |      |     |     |                       | Main Clock Output or In Circuit<br>Communication Clock or External<br>BREAK                                                                                                                                                                                                                                                                                  |

| 12         | 10    | 10         | PA6 /MCO/<br>ICCCLK/BREAK | I/O  | C     | Ст     | х     | ei  | i1   |      | х   | х   | Port A6               | <b>Caution:</b> During normal operation<br>this pin must be pulled- up, inter-<br>nally or externally (external pull-up<br>of 10k mandatory in noisy environ-<br>ment). This is to avoid entering ICC<br>mode unexpectedly during a reset.<br>In the application, even if the pin is<br>configured as output, any reset will<br>put it back in input pull-up |

| 13         | 11    | 11         | PA5 /ICCDATA/<br>ATPWM3   | I/O  | CT    | HS     | х     | e   | i1   |      | Х   | Х   | Port A5               | In Circuit Communication Data or<br>Auto-Reload Timer PWM3                                                                                                                                                                                                                                                                                                   |

| 14         | 12    | 12         | PA4/ATPWM2                | I/O  | CT    | HS     | Х     |     |      |      | Х   | Х   | Port A4               | Auto-Reload Timer PWM2                                                                                                                                                                                                                                                                                                                                       |

| 15         | 13    | -          | PA3/ATPWM1                | I/O  | Ст    | HS     | Х     |     |      |      | Х   | Х   | Port A3               | Auto-Reload Timer PWM1                                                                                                                                                                                                                                                                                                                                       |

| 16         | 14    | 13         | PA2/ATPWM0                | I/O  | CT    | HS     | X     | e   | i∩   |      | Х   | Х   | Port A2               | Auto-Reload Timer PWM0                                                                                                                                                                                                                                                                                                                                       |

| 17         | 15    | -          | PA1/ATIC                  | I/O  | CT    | HS     | Х     |     | 10   |      | Х   | Х   | Port A1               | Auto-Reload Timer Input Capture                                                                                                                                                                                                                                                                                                                              |

| 18         | 16    | 14         | PA0/LTIC                  | I/O  | CT    | HS     | Х     |     |      |      | Х   | Х   | Port A0               | Lite Timer Input Capture                                                                                                                                                                                                                                                                                                                                     |

| 19         | 17    | 15         | OSC2/PC1                  | I/O  |       |        | x     |     |      |      |     | х   | Port C1 <sup>3)</sup> | Resonator oscillator inverter out-<br>put                                                                                                                                                                                                                                                                                                                    |

| 20         | 18    | 16         | OSC1/CLKIN/PC0            | I/O  |       |        | X     |     |      |      |     | х   | Port C0 <sup>3)</sup> | Resonator oscillator inverter input<br>or External clock input                                                                                                                                                                                                                                                                                               |

## Notes:

1. It is mandatory to connect all available  $V_{DD}$  and  $V_{DDA}$  pins to the supply voltage and all  $V_{SS}$  and  $V_{SSA}$  pins to ground.

2. When the pin is configured as analog input, positive and negative current injections are not allowed.

3. PCOR not implemented but p-transistor always active in output mode (refer to Figure 32 on page 50).

## FLASH PROGRAM MEMORY (Cont'd)

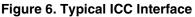

#### 4.4 ICC interface

ICP needs a minimum of 4 and up to 6 pins to be connected to the programming tool. These pins are:

- RESET: device reset

- V<sub>SS</sub>: device power supply ground

- ICCCLK: ICC output serial clock pin

- ICCDATA: ICC input serial data pin

- OSC1: main clock input for external source (not required on devices without OSC1/OSC2 pins)

- $V_{DD}$ : application board power supply (optional, see Note 3)

#### Notes:

57/

1. If the ICCCLK or ICCDATA pins are only used as outputs in the application, no signal isolation is necessary. As soon as the Programming Tool is plugged to the board, even if an ICC session is not in progress, the ICCCLK and ICCDATA pins are not available for the application. If they are used as inputs by the application, isolation such as a serial resistor has to be implemented in case another device forces the signal. Refer to the Programming Tool documentation for recommended resistor values.

2. During the ICP session, the programming tool must control the RESET pin. This can lead to conflicts between the programming tool and the application reset circuit if it drives more than 5mA at high level (push pull output or pull-up resistor<1K). A schottky diode can be used to isolate the application RESET circuit in this case. When using a

classical RC network with R>1K or a reset management IC with open drain output and pull-up resistor>1K, no additional components are needed. In all cases the user must ensure that no external reset is generated by the application during the ICC session.

3. The use of pin 7 of the ICC connector depends on the Programming Tool architecture. This pin must be connected when using most ST Programming Tools (it is used to monitor the application power supply). Please refer to the Programming Tool manual.

4. Pin 9 has to be connected to the OSC1 pin of the ST7 when the clock is not available in the application or if the selected clock option is not programmed in the option byte. ST7 devices with multi-oscillator capability need to have OSC2 grounded in this case.

5. In 38-pulse ICC mode, the internal RC oscillator is forced as a clock source, regardless of the selection in the option byte. For ST7LITE10B devices which do not support the internal RC oscillator, the "option byte disabled" mode must be used (35pulse ICC mode entry, clock provided by the tool).

**Caution:** During normal operation the ICCCLK pin must be pulled- up, internally or externally (external pull-up of 10k mandatory in noisy environment). This is to avoid entering ICC mode unexpectedly during a reset. In the application, even if the pin is configured as output, any reset will put it back in input pull-up.

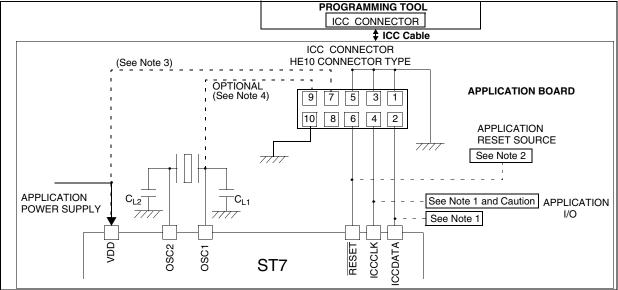

## DATA EEPROM (Cont'd)

#### **5.3 MEMORY ACCESS**

The Data EEPROM memory read/write access modes are controlled by the E2LAT bit of the EEP-ROM Control/Status register (EECSR). The flowchart in Figure 8 describes these different memory access modes.

#### Read Operation (E2LAT=0)

The EEPROM can be read as a normal ROM location when the E2LAT bit of the EECSR register is cleared.

On this device, Data EEPROM can also be used to execute machine code. Take care not to write to the Data EEPROM while executing from it. This would result in an unexpected code being executed.

#### Write Operation (E2LAT=1)

To access the write mode, the E2LAT bit has to be set by software (the E2PGM bit remains cleared). When a write access to the EEPROM area occurs,

#### Figure 8. Data EEPROM Programming Flowchart

the value is latched inside the 32 data latches according to its address.

When PGM bit is set by the software, all the previous bytes written in the data latches (up to 32) are programmed in the EEPROM cells. The effective high address (row) is determined by the last EEP-ROM write sequence. To avoid wrong programming, the user must take care that all the bytes written between two programming sequences have the same high address: only the five Least Significant Bits of the address can change.

At the end of the programming cycle, the PGM and LAT bits are cleared simultaneously.

**Note**: Care should be taken during the programming cycle. Writing to the same memory location will over-program the memory (logical AND between the two write access data result) because the data latches are only cleared at the end of the programming cycle and by the falling edge of the E2LAT bit.

It is not possible to read the latched data. This note is illustrated by the Figure 10.

## CPU REGISTERS (cont'd) CONDITION CODE REGISTER (CC)

Read/Write

Reset Value: 111x1xxx

| 7 |   |   |   |   |   |   | 0 |

|---|---|---|---|---|---|---|---|

| 1 | 1 | 1 | н | Ι | Ν | Z | С |

The 8-bit Condition Code register contains the interrupt mask and four flags representative of the result of the instruction just executed. This register can also be handled by the PUSH and POP instructions.

These bits can be individually tested and/or controlled by specific instructions.

#### Bit 4 = H Half carry

This bit is set by hardware when a carry occurs between bits 3 and 4 of the ALU during an ADD or ADC instruction. It is reset by hardware during the same instructions.

0: No half carry has occurred.

1: A half carry has occurred.

This bit is tested using the JRH or JRNH instruction. The H bit is useful in BCD arithmetic subroutines.

#### Bit 3 = I Interrupt mask

This bit is set by hardware when entering in interrupt or by software to disable all interrupts except the TRAP software interrupt. This bit is cleared by software.

0: Interrupts are enabled.

57

1: Interrupts are disabled.

This bit is controlled by the RIM, SIM and IRET instructions and is tested by the JRM and JRNM instructions.

**Note:** Interrupts requested while I is set are latched and can be processed when I is cleared. By default an interrupt routine is not interruptible

because the I bit is set by hardware at the start of the routine and reset by the IRET instruction at the end of the routine. If the I bit is cleared by software in the interrupt routine, pending interrupts are serviced regardless of the priority level of the current interrupt routine.

#### Bit 2 = N Negative

This bit is set and cleared by hardware. It is representative of the result sign of the last arithmetic, logical or data manipulation. It is a copy of the 7<sup>th</sup> bit of the result.

0: The result of the last operation is positive or null.

1: The result of the last operation is negative (that is, the most significant bit is a logic 1).

This bit is accessed by the JRMI and JRPL instructions.

#### Bit 1 = Z Zero

This bit is set and cleared by hardware. This bit indicates that the result of the last arithmetic, logical or data manipulation is zero.

- 0: The result of the last operation is different from zero.

- 1: The result of the last operation is zero.

This bit is accessed by the JREQ and JRNE test instructions.

#### Bit 0 = C Carry/borrow

This bit is set and cleared by hardware and software. It indicates an overflow or an underflow has occurred during the last arithmetic operation. 0: No overflow or underflow has occurred.

1: An overflow or underflow has occurred.

This bit is driven by the SCF and RCF instructions and tested by the JRC and JRNC instructions. It is also affected by the "bit test and branch", shift and rotate instructions.

## **8 INTERRUPTS**

The ST7 core may be interrupted by one of two different methods: Maskable hardware interrupts as listed in the "interrupt mapping" table and a nonmaskable software interrupt (TRAP). The Interrupt processing flowchart is shown in Figure 1.

The maskable interrupts must be enabled by clearing the I bit in order to be serviced. However, disabled interrupts may be latched and processed when they are enabled (see external interrupts subsection).

Note: After reset, all interrupts are disabled.

When an interrupt has to be serviced:

- Normal processing is suspended at the end of the current instruction execution.

- The PC, X, A and CC registers are saved onto the stack.

- The I bit of the CC register is set to prevent additional interrupts.

- The PC is then loaded with the interrupt vector of the interrupt to service and the first instruction of the interrupt service routine is fetched (refer to the Interrupt Mapping table for vector addresses).

The interrupt service routine should finish with the IRET instruction which causes the contents of the saved registers to be recovered from the stack.

**Note:** As a consequence of the IRET instruction, the I bit is cleared and the main program resumes.

#### **Priority Management**

By default, a servicing interrupt cannot be interrupted because the I bit is set by hardware entering in interrupt routine.

In the case when several interrupts are simultaneously pending, an hardware priority defines which one will be serviced first (see the Interrupt Mapping table).

#### Interrupts and Low Power Mode

All interrupts allow the processor to leave the WAIT low power mode. Only external and specifically mentioned interrupts allow the processor to leave the HALT low power mode (refer to the "Exit from HALT" column in the Interrupt Mapping table).

#### **8.1 NON MASKABLE SOFTWARE INTERRUPT**

This interrupt is entered when the TRAP instruction is executed regardless of the state of the I bit. It is serviced according to the flowchart in Figure 1.

#### **8.2 EXTERNAL INTERRUPTS**

External interrupt vectors can be loaded into the PC register if the corresponding external interrupt occurred and if the I bit is cleared. These interrupts allow the processor to leave the HALT low power mode.

The external interrupt polarity is selected through the miscellaneous register or interrupt register (if available).

An external interrupt triggered on edge will be latched and the interrupt request automatically cleared upon entering the interrupt service routine.

**Caution:** The type of sensitivity defined in the Miscellaneous or Interrupt register (if available) applies to the ei source. In case of a NANDed source (as described in the I/O ports section), a low level on an I/O pin, configured as input with interrupt, masks the interrupt request even in case of rising-edge sensitivity.

## **8.3 PERIPHERAL INTERRUPTS**

Different peripheral interrupt flags in the status register are able to cause an interrupt when they are active if both:

- The I bit of the CC register is cleared.

- The corresponding enable bit is set in the control register.

If any of these two conditions is false, the interrupt is latched and thus remains pending.

Clearing an interrupt request is done by:

- Writing "0" to the corresponding bit in the status register or

- Access to the status register while the flag is set followed by a read or write of an associated register.

**Note**: The clearing sequence resets the internal latch. A pending interrupt (that is, waiting for being enabled) will therefore be lost if the clear sequence is executed.

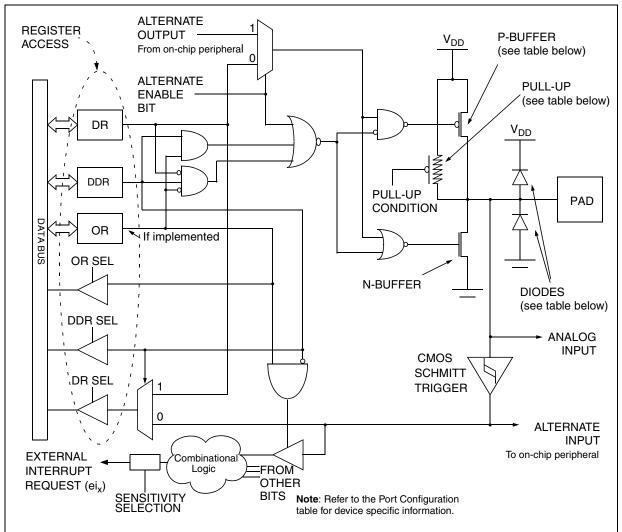

## I/O PORTS (Cont'd)

## Table 8. I/O Port Mode Options

| Configuration Mode |                                 | Pull-Up | P-Buffer | Diodes             |                    |  |

|--------------------|---------------------------------|---------|----------|--------------------|--------------------|--|

|                    |                                 | Puil-Op | F-Builei | to V <sub>DD</sub> | to V <sub>SS</sub> |  |

| Input              | Floating with/without Interrupt | Off     | Off      | 07                 | On                 |  |

| Input              | Pull-up with/without Interrupt  | On      | OII      |                    |                    |  |

| Output             | Push-pull                       | Off     | On       | On                 |                    |  |

| Output             | Open Drain (logic level)        |         | Off      |                    |                    |  |

Legend: Off - implemented not activated On - implemented and activated

## I/O PORTS (Cont'd)

## **10.7 DEVICE-SPECIFIC I/O PORT CONFIGURATION**

The I/O port register configurations are summarised as follows.

#### **Standard Ports**

#### PA7:0, PB6:0

<u>ل</u>رك

| MODE              | DDR | OR |

|-------------------|-----|----|

| floating input    | 0   | 0  |

| pull-up input     | 0   | 1  |

| open drain output | 1   | 0  |

| push-pull output  | 1   | 1  |

#### PC1:0 (multiplexed with OSC1,OSC2)

| MODE             | DDR |

|------------------|-----|

| floating input   | 0   |

| push-pull output | 1   |

The selection between OSC1 or PC0 and OSC2 or PC1 is done by option byte. Refer to section 15.1 on page 149. Interrupt capability is not available on PC1:0.

**Note:** PCOR not implemented but p-transistor always active in output mode (refer to Figure 32 on page 50)

#### Table 10. Port Configuration (Standard ports)

| Port   | Pin name | Ing      | out     | Output     |           |  |

|--------|----------|----------|---------|------------|-----------|--|

| FOIL   | Finname  | OR = 0   | OR = 1  | OR = 0     | OR = 1    |  |

| Port A | PA7:0    | floating | pull-up | open drain | push-pull |  |

| Port B | PB6:0    | floating | pull-up | open drain | push-pull |  |

**Note:** On ports where the external interrupt capability is selected using the EISR register, the configuration will be as follows:

| Port   | Pin name | Inj      | out               | Output     |           |  |

|--------|----------|----------|-------------------|------------|-----------|--|

|        |          | OR = 0   | OR = 1            | OR = 0     | OR = 1    |  |

| Port A | PA7:0    | floating | pull-up interrupt | open drain | push-pull |  |

| Port B | PB6:0    | floating | pull-up interrupt | open drain | push-pull |  |

#### Table 11. I/O Port Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|-------------------|-------------------|-----|---|---|---|---|---|---|-----|

| 0000h             | PADR              | MSB |   |   |   |   |   |   | LSB |

|                   | Reset Value       | 1   | 1 | 1 | 1 | 1 | 1 | 1 | 1   |

| 0001h             | PADDR             | MSB |   |   |   |   |   |   | LSB |

|                   | Reset Value       | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

#### **Interrupt Ports**

Ports where the external interrupt capability is selected using the EISR register

| MODE                    | DDR | OR |

|-------------------------|-----|----|

| floating input          | 0   | 0  |

| pull-up interrupt input | 0   | 1  |

| open drain output       | 1   | 0  |

| push-pull output        | 1   | 1  |

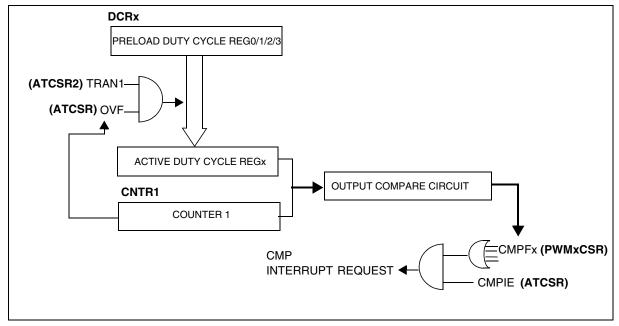

## DUAL 12-BIT AUTORELOAD TIMER 4 (Cont'd)

## 11.2.3.4 Output Compare Mode

5/

To use this function, load a 12-bit value in the Preload DCRxH and DCRxL registers.

When the 12-bit upcounter CNTR1 reaches the value stored in the Active DCRxH and DCRxL registers, the CMPFx bit in the PWMxCSR register is set and an interrupt request is generated if the CMPIE bit is set.

In single Timer mode the output compare function is performed only on CNTR1. The difference between both the modes is that, in Single Timer mode, CNTR1 can be compared with any of the four DCR registers, and in Dual Timer mode, CNTR1 is compared with DCR0 or DCR1 and CNTR2 is compared with DCR2 or DCR3.

#### Notes:

**1.** The output compare function is only available for DCRx values other than 0 (reset value).

**2.** Duty cycle registers are buffered internally. The CPU writes in Preload Duty Cycle Registers and these values are transferred in Active Duty Cycle Registers after an overflow event if the corresponding transfer bit (TRANx bit) is set. Output compare is done by comparing these active DCRx values with the counters.

## DUAL 12-BIT AUTORELOAD TIMER 4 (Cont'd)

#### 11.2.4 Low Power Modes

| Mode | Description           |

|------|-----------------------|

| WAIT | No effect on AT timer |

| HALT | AT timer halted.      |

#### 11.2.5 Interrupts

57

| Interrupt<br>Event | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt | Exit<br>from<br>Active-<br>Halt |

|--------------------|---------------|--------------------------|----------------------|----------------------|---------------------------------|

| Overflow<br>Event  | OVF1          | OVIE1                    | Yes                  | No                   | Yes                             |

| AT4 IC Event       | ICF           | ICIE                     | Yes                  | No                   | No                              |

| CMP Event          | CMPFx         | CMPIE                    | Yes                  | No                   | No                              |

| Overflow<br>Event2 | OVF2          | OVIE2                    | Yes                  | No                   | No                              |

**Note:** The CMP and AT4 IC events are connected to the same interrupt vector.

The OVF event is mapped on a separate vector (see Interrupts chapter).

They generate an interrupt if the enable bit is set in the ATCSR register and the interrupt mask in the CC register is reset (RIM instruction).

## **ON-CHIP PERIPHERALS** (cont'd)

## **11.4 SERIAL PERIPHERAL INTERFACE (SPI)**

#### 11.4.1 Introduction

The Serial Peripheral Interface (SPI) allows fullduplex, synchronous, serial communication with external devices. An SPI system may consist of a master and one or more slaves or a system in which devices may be either masters or slaves.

#### 11.4.2 Main Features

- Full duplex synchronous transfers (on three lines)

- Simplex synchronous transfers (on two lines)

- Master or slave operation

- 6 master mode frequencies (f<sub>CPU</sub>/4 max.)

- I f<sub>CPU</sub>/2 max. slave mode frequency (see note)

- SS Management by software or hardware

- Programmable clock polarity and phase

- End of transfer interrupt flag

- Write collision, Master Mode Fault and Overrun flags

**Note:** In slave mode, continuous transmission is not possible at maximum frequency due to the software overhead for clearing status flags and to initiate the next transmission sequence.

#### **11.4.3 General Description**

Figure 1 on page 3 shows the serial peripheral interface (SPI) block diagram. There are three registers:

- SPI Control Register (SPICR)

- SPI Control/Status Register (SPICSR)

- SPI Data Register (SPIDR)

The SPI is connected to external devices through four pins:

- MISO: Master In / Slave Out data

- MOSI: Master Out / Slave In data

- SCK: Serial Clock out by SPI masters and input by SPI slaves

- SS: Slave select:

This input signal acts as a 'chip select' to let the SPI master communicate with slaves individually and to avoid contention on the data lines. Slave SS inputs can be driven by standard I/O ports on the master Device.

## SERIAL PERIPHERAL INTERFACE (cont'd)

#### 11.4.5 Error Flags

#### 11.4.5.1 Master Mode Fault (MODF)

Master mode fault occurs when the master device's SS pin is pulled low.

When a Master mode fault occurs:

- The MODF bit is set and an SPI interrupt request is generated if the SPIE bit is set.

- The SPE bit is reset. This blocks all output from the device and disables the SPI peripheral.

- The MSTR bit is reset, thus forcing the device into slave mode.

Clearing the MODF bit is done through a software sequence:

1. A read access to the SPICSR register while the MODF bit is set.

2. A write to the SPICR register.

**Notes:** To avoid any conflicts in an application with multiple slaves, the SS pin must be pulled high during the MODF bit clearing sequence. The SPE and MSTR bits may be restored to their original state during or after this clearing sequence.

Hardware does not allow the user to set the SPE and MSTR bits while the MODF bit is set except in the MODF bit clearing sequence.

In a slave device, the MODF bit can not be set, but in a multimaster configuration the device can be in slave mode with the MODF bit set.

The MODF bit indicates that there might have been a multimaster conflict and allows software to handle this using an interrupt routine and either perform a reset or return to an application default state.

#### 11.4.5.2 Overrun Condition (OVR)

An overrun condition occurs when the master device has sent a data byte and the slave device has not cleared the SPIF bit issued from the previously transmitted byte.

When an Overrun occurs:

- The OVR bit is set and an interrupt request is generated if the SPIE bit is set.

In this case, the receiver buffer contains the byte sent after the SPIF bit was last cleared. A read to the SPIDR register returns this byte. All other bytes are lost.

The OVR bit is cleared by reading the SPICSR register.

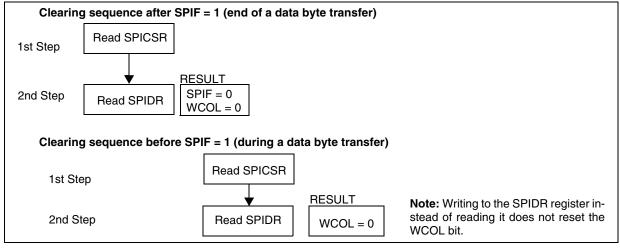

#### 11.4.5.3 Write Collision Error (WCOL)

A write collision occurs when the software tries to write to the SPIDR register while a data transfer is taking place with an external device. When this happens, the transfer continues uninterrupted and the software write will be unsuccessful.

Write collisions can occur both in master and slave mode. See also Section 0.1.3.2 Slave Select Management.

**Note:** A "read collision" will never occur since the received data byte is placed in a buffer in which access is always synchronous with the CPU operation.

The WCOL bit in the SPICSR register is set if a write collision occurs.

No SPI interrupt is generated when the WCOL bit is set (the WCOL bit is a status flag only).

Clearing the WCOL bit is done through a software sequence (see Figure 6).

#### Figure 58. Clearing the WCOL Bit (Write Collision Flag) Software Sequence

## SERIAL PERIPHERAL INTERFACE (cont'd)

## 11.4.6 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on SPI.<br>SPI interrupt events cause the device to exit<br>from WAIT mode.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| HALT | SPI registers are frozen.<br>In HALT mode, the SPI is inactive. SPI oper-<br>ation resumes when the device is woken up<br>by an interrupt with "exit from HALT mode"<br>capability. The data received is subsequently<br>read from the SPIDR register when the soft-<br>ware is running (interrupt vector fetching). If<br>several data are received before the wake-<br>up event, then an overrun error is generated.<br>This error can be detected after the fetch of<br>the interrupt routine that woke up the Device. |

# 11.4.6.1 Using the SPI to wake up the device from Halt mode

In slave configuration, the SPI is able to wake up the device from HALT mode through a SPIF interrupt. The data received is subsequently read from the SPIDR register when the software is running (interrupt vector fetch). If multiple data transfers have been performed before software clears the SPIF bit, then the OVR bit is set by hardware.

**Note:** When waking up from HALT mode, if the SPI remains in Slave mode, it is recommended to perform an extra communications cycle to bring

the SPI from HALT mode state to normal state. If the SPI exits from Slave mode, it returns to normal state immediately.

**Caution:** The SPI can wake up the device from HALT mode only if the Slave Select signal (external SS pin or the SSI bit in the SPICSR register) is low when the device enters HALT mode. So, if Slave selection is configured as external (see Section 0.1.3.2), make sure the master drives a low level on the SS pin when the slave enters HALT mode.

#### 11.4.7 Interrupts

| Interrupt Event              | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|------------------------------|---------------|--------------------------|----------------------|----------------------|

| SPI End of<br>Transfer Event | SPIF          |                          |                      | Yes                  |

| Master Mode<br>Fault Event   | MODF          | SPIE                     | Yes                  | No                   |

| Overrun Error                | OVR           |                          |                      |                      |

**Note**: The SPI interrupt events are connected to the same interrupt vector (see Interrupts chapter). They generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

## SERIAL PERIPHERAL INTERFACE (Cont'd)

57

## Table 17. SPI Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label           | 7         | 6         | 5         | 4         | 3         | 2         | 1         | 0         |

|-------------------|-----------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| 0031h             | <b>SPIDR</b><br>Reset Value | MSB<br>x  | x         | x         | x         | x         | x         | x         | LSB<br>x  |

| 0032h             | SPICR<br>Reset Value        | SPIE<br>0 | SPE<br>0  | SPR2<br>0 | MSTR<br>0 | CPOL<br>x | CPHA<br>x | SPR1<br>x | SPR0<br>x |

| 0033h             | SPICSR<br>Reset Value       | SPIF<br>0 | WCOL<br>0 | OVR<br>0  | MODF<br>0 | 0         | SOD<br>0  | SSM<br>0  | SSI<br>0  |

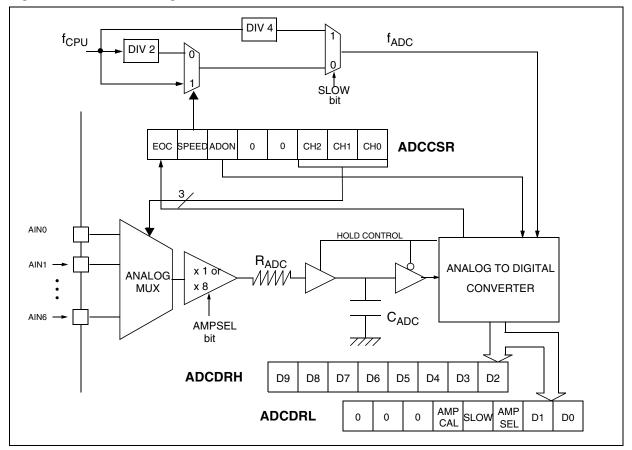

## 11.5 10-BIT A/D CONVERTER (ADC)

#### 11.5.1 Introduction

The on-chip Analog to Digital Converter (ADC) peripheral is a 10-bit, successive approximation converter with internal sample and hold circuitry. This peripheral has up to 7 multiplexed analog input channels (refer to device pin out description) that allow the peripheral to convert the analog voltage levels from up to 7 different sources.

The result of the conversion is stored in a 10-bit Data Register. The A/D converter is controlled through a Control/Status Register.

## 11.5.2 Main Features

- 10-bit conversion

- Up to 7 channels with multiplexed input

- Linear successive approximation

#### Figure 60. ADC Block Diagram

- Data register (DR) which contains the results

- Conversion complete status flag

- On/off bit (to reduce consumption)

The block diagram is shown in Figure 60.

#### **11.5.3 Functional Description**

#### 11.5.3.1 Analog Power Supply

$V_{DDA}$  and  $V_{SSA}$  are the high and low level reference voltage pins. In some devices (refer to device pin out description) they are internally connected to the  $V_{DD}$  and  $V_{SS}$  pins.

Conversion accuracy may therefore be impacted by voltage drops and noise in the event of heavily loaded or badly decoupled power supply lines.

47/

## 10-BIT A/D CONVERTER (ADC) (Cont'd)

Bit 2 = **AMPSEL** Amplifier Selection Bit This bit is set and cleared by software. 0: Amplifier is not selected 1: Amplifier is selected

Note: When AMPSEL=1 it is mandatory that  $\rm f_{ADC}$  be less than or equal to 2 MHz.

Bits 1:0 = D[1:0] LSB of Analog Converted Value

| Table 18 | ADC R | egister | Map a | nd Res | et Values |

|----------|-------|---------|-------|--------|-----------|

|----------|-------|---------|-------|--------|-----------|

57

| Address<br>(Hex.) | Register<br>Label | 7   | 6     | 5    | 4      | 3    | 2      | 1   | 0   |

|-------------------|-------------------|-----|-------|------|--------|------|--------|-----|-----|

| 0034h             | ADCCSR            | EOC | SPEED | ADON | 0      | 0    | CH2    | CH1 | CH0 |

|                   | Reset Value       | 0   | 0     | 0    | 0      | 0    | 0      | 0   | 0   |

| 0035h             | ADCDRH            | D9  | D8    | D7   | D6     | D5   | D4     | D3  | D2  |

|                   | Reset Value       | x   | x     | x    | x      | x    | x      | x   | x   |

| 0036h             | ADCDRL            | 0   | 0     | 0    | AMPCAL | SLOW | AMPSEL | D1  | D0  |

|                   | Reset Value       | 0   | 0     | 0    | 0      | 0    | 0      | x   | x   |

# **12 INSTRUCTION SET**

## 12.1 ST7 ADDRESSING MODES

The ST7 Core features 17 different addressing modes which can be classified in seven main groups:

| Addressing Mode | Example         |

|-----------------|-----------------|

| Inherent        | nop             |

| Immediate       | ld A,#\$55      |

| Direct          | ld A,\$55       |

| Indexed         | ld A,(\$55,X)   |

| Indirect        | ld A,([\$55],X) |

| Relative        | jrne loop       |

| Bit operation   | bset byte,#5    |

Table 22. ST7 Addressing Mode Overview

The ST7 Instruction set is designed to minimize the number of bytes required per instruction: To do so, most of the addressing modes may be subdivided in two submodes called long and short:

- Long addressing mode is more powerful because it can use the full 64 Kbyte address space, however it uses more bytes and more CPU cycles.

- Short addressing mode is less powerful because it can generally only access page zero (0000h -00FFh range), but the instruction size is more compact, and faster. All memory to memory instructions use short addressing modes only (CLR, CPL, NEG, BSET, BRES, BTJT, BTJF, INC, DEC, RLC, RRC, SLL, SRL, SRA, SWAP)

The ST7 Assembler optimizes the use of long and short addressing modes.

|           | Mode     |          | Syntax              | Destination/<br>Source      | Pointer<br>Address<br>(Hex.) | Pointer<br>Size<br>(Hex.) | Length<br>(Bytes)                              |

|-----------|----------|----------|---------------------|-----------------------------|------------------------------|---------------------------|------------------------------------------------|

| Inherent  |          |          | nop                 |                             |                              |                           | + 0                                            |

| Immediate |          |          | ld A,#\$55          |                             |                              |                           | + 1                                            |

| Short     | Direct   |          | ld A,\$10           | 00FF                        |                              |                           | + 1                                            |

| Long      | Direct   |          | ld A,\$1000         | 0000FFFF                    |                              |                           | + 2                                            |

| No Offset | Direct   | Indexed  | ld A,(X)            | 00FF                        |                              |                           | + 0 (with X register)<br>+ 1 (with Y register) |

| Short     | Direct   | Indexed  | ld A,(\$10,X)       | 001FE                       |                              |                           | + 1                                            |

| Long      | Direct   | Indexed  | ld A,(\$1000,X)     | 0000FFFF                    |                              |                           | + 2                                            |

| Short     | Indirect |          | ld A,[\$10]         | 00FF                        | 00FF                         | byte                      | + 2                                            |

| Long      | Indirect |          | ld A,[\$10.w]       | 0000FFFF                    | 00FF                         | word                      | + 2                                            |

| Short     | Indirect | Indexed  | ld A,([\$10],X)     | 001FE                       | 00FF                         | byte                      | + 2                                            |

| Long      | Indirect | Indexed  | ld A,([\$10.w],X)   | 0000FFFF                    | 00FF                         | word                      | + 2                                            |

| Relative  | Direct   |          | jrne loop           | PC-128/PC+127 <sup>1)</sup> |                              |                           | + 1                                            |

| Relative  | Indirect |          | jrne [\$10]         | PC-128/PC+127 <sup>1)</sup> | 00FF                         | byte                      | + 2                                            |

| Bit       | Direct   |          | bset \$10,#7        | 00FF                        |                              |                           | + 1                                            |

| Bit       | Indirect |          | bset [\$10],#7      | 00FF                        | 00FF                         | byte                      | + 2                                            |

| Bit       | Direct   | Relative | btjt \$10,#7,skip   | 00FF                        |                              |                           | + 2                                            |

| Bit       | Indirect | Relative | btjt [\$10],#7,skip | 00FF                        | 00FF                         | byte                      | + 3                                            |

|           |          |          |                     |                             | 00FF                         | byte                      |                                                |

Note:

1. At the time the instruction is executed, the Program Counter (PC) points to the instruction following JRxx.

## INSTRUCTION GROUPS (cont'd)

57

| Mnemo | Description            | Function/Example    | Dst     | Src     | н | I | Ν | z | С |

|-------|------------------------|---------------------|---------|---------|---|---|---|---|---|

| JRULE | Jump if $(C + Z = 1)$  | Unsigned <=         |         |         |   |   |   |   |   |

| LD    | Load                   | dst <= src          | reg, M  | M, reg  |   |   | Ν | Z |   |

| MUL   | Multiply               | X,A = X * A         | A, X, Y | X, Y, A | 0 |   |   |   | 0 |

| NEG   | Negate (2's compl)     | neg \$10            | reg, M  |         |   |   | Ν | Z | С |

| NOP   | No Operation           |                     |         |         |   |   |   |   |   |

| OR    | OR operation           | A = A + M           | А       | М       |   |   | Ν | Z |   |

| POP   | Pop from the Stack     | pop reg             | reg     | М       |   |   |   |   |   |

|       |                        | pop CC              | сс      | М       | Н | I | Ν | Z | С |

| PUSH  | Push onto the Stack    | push Y              | М       | reg, CC |   |   |   |   |   |

| RCF   | Reset carry flag       | C = 0               |         |         |   |   |   |   | 0 |

| RET   | Subroutine Return      |                     |         |         |   |   |   |   |   |

| RIM   | Enable Interrupts      | I = 0               |         |         |   | 0 |   |   |   |

| RLC   | Rotate left true C     | C <= Dst <= C       | reg, M  |         |   |   | Ν | Z | С |

| RRC   | Rotate right true C    | C => Dst => C       | reg, M  |         |   |   | Ν | Z | С |

| RSP   | Reset Stack Pointer    | S = Max allowed     |         |         |   |   |   |   |   |

| SBC   | Subtract with Carry    | A = A - M - C       | А       | М       |   |   | Ν | Z | С |

| SCF   | Set carry flag         | C = 1               |         |         |   |   |   |   | 1 |

| SIM   | Disable Interrupts     | l = 1               |         |         |   | 1 |   |   |   |

| SLA   | Shift left Arithmetic  | C <= Dst <= 0       | reg, M  |         |   |   | Ν | Z | С |

| SLL   | Shift left Logic       | C <= Dst <= 0       | reg, M  |         |   |   | Ν | Z | С |

| SRL   | Shift right Logic      | 0 => Dst => C       | reg, M  |         |   |   | 0 | Z | С |

| SRA   | Shift right Arithmetic | Dst7 => Dst => C    | reg, M  |         |   |   | Ν | Z | С |

| SUB   | Subtraction            | A = A - M           | А       | М       |   |   | Ν | Z | С |

| SWAP  | SWAP nibbles           | Dst[74] <=> Dst[30] | reg, M  |         |   |   | Ν | Z |   |

| TNZ   | Test for Neg & Zero    | tnz lbl1            |         |         |   |   | Ν | Z |   |

| TRAP  | S/W trap               | S/W interrupt       |         |         |   | 1 |   | 1 |   |

| WFI   | Wait for Interrupt     |                     |         |         |   | 0 |   |   |   |

| XOR   | Exclusive OR           | A = A XOR M         | A       | М       |   |   | Ν | Z |   |

|       |                        |                     |         |         |   |   |   |   |   |

## **13.2 ABSOLUTE MAXIMUM RATINGS**

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these condi-

#### 13.2.1 Voltage Characteristics

tions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                            | Ratings                                         | Maximum value                                      | Unit    |

|-----------------------------------|-------------------------------------------------|----------------------------------------------------|---------|

| V <sub>DD</sub> - V <sub>SS</sub> | Supply voltage                                  | 7.0                                                | V       |

| V <sub>IN</sub>                   | Input voltage on any pin <sup>1) &amp; 2)</sup> | $V_{\rm SS}\mbox{-}0.3$ to $V_{\rm DD}\mbox{+}0.3$ | v       |

| V <sub>ESD(HBM)</sub>             |                                                 |                                                    | 200 128 |

| V <sub>ESD(MM)</sub>              | Electrostatic discharge voltage (Machine Model) | see section 13.7.3 on pa                           | aye 120 |

#### **13.2.2 Current Characteristics**

| Symbol                        | Ratings                                                                | Maximum value | Unit |

|-------------------------------|------------------------------------------------------------------------|---------------|------|

| I <sub>VDD</sub>              | Total current into V <sub>DD</sub> power lines (source) 3)             | 75            |      |

| I <sub>VSS</sub>              | Total current out of V <sub>SS</sub> ground lines (sink) 3)            | 150           |      |

|                               | Output current sunk by any standard I/O and control pin                | 20            |      |

| I <sub>IO</sub>               | Output current sunk by any high sink I/O pin                           | 40            |      |

|                               | Output current source by any I/Os and control pin                      | - 25          |      |

|                               | Injected current on ISPSEL pin                                         | ± 5           | mA   |

|                               | Injected current on RESET pin                                          | ± 5           |      |

| I <sub>INJ(PIN)</sub> 2) & 4) | Injected current on OSC1 and OSC2 pins                                 | ± 5           |      |

|                               | Injected current on PB0 pin <sup>5)</sup>                              | +5            |      |

|                               | Injected current on any other pin 6)                                   | ± 5           |      |

| $\Sigma I_{INJ(PIN)}^{2)}$    | Total injected current (sum of all I/O and control pins) <sup>6)</sup> | ± 20          |      |

#### 13.2.3 Thermal Characteristics

| Symbol           | Ratings                                                       | Value               | Unit |

|------------------|---------------------------------------------------------------|---------------------|------|

| T <sub>STG</sub> | Storage temperature range                                     | -65 to +150         | °C   |

| TJ               | Maximum junction temperature (see Table 24, "THERM, page 147) | AL CHARACTERISTICS, | " on |

#### Notes:

1. Directly connecting the RESET and I/O pins to V<sub>DD</sub> or V<sub>SS</sub> could damage the device if an unintentional internal reset is generated or an unexpected change of the I/O configuration occurs (for example, due to a corrupted program counter). To guarantee safe operation, this connection has to be done through a pull-up or pull-down resistor (typical:  $4.7k\Omega$  for RESET,  $10k\Omega$  for I/Os). Unused I/O pins must be tied in the same way to V<sub>DD</sub> or V<sub>SS</sub> according to their reset configuration. 2. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub><V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub><V<sub>SS</sub>. For true open-drain pads, there is no positive injection current, and the corresponding V<sub>IN</sub> maximum must always be respected

3. All power  $(V_{DD})$  and ground  $(V_{SS})$  lines must always be connected to the external supply.

4. Negative injection disturbs the analog performance of the device. In particular, it induces leakage currents throughout the device including the analog inputs. To avoid undesirable effects on the analog functions, care must be taken:

- Analog input pins must have a negative injection less than 0.8 mA (assuming that the impedance of the analog voltage is lower than the specified limits)

- Pure digital pins must have a negative injection less than 1.6mA. In addition, it is recommended to inject the current as far as possible from the analog input pins.

5. No negative current injection allowed on PB0 pin.

6. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterisation with  $\Sigma I_{INJ(PIN)}$  maximum current injection on four I/O port pins of the device.

57

## **15.2 DEVICE ORDERING INFORMATION**

#### Figure 118. Ordering information scheme

| Example:                                    | ST7 | F | LIT1xB | F | 0 | Μ | 3 | TR |

|---------------------------------------------|-----|---|--------|---|---|---|---|----|

| <b>Family</b><br>ST7 Microcontroller Family |     |   |        |   |   |   |   |    |

| Memory type                                 |     |   |        |   |   |   |   |    |

| F: Flash                                    |     |   |        |   |   |   |   |    |

| P: FASTROM                                  |     |   |        |   |   |   |   |    |

| <b>Version</b><br>10B, 15B or 19B           |     |   |        |   |   |   |   |    |

| No. of pins                                 |     |   |        |   |   |   |   |    |

| F = 20                                      |     |   |        |   |   |   |   |    |

| Y = 16                                      |     |   |        |   |   |   |   |    |

| Memory size                                 |     |   |        |   |   |   |   |    |

| 0 = 2K<br>1 = 4K                            |     |   |        |   |   |   |   |    |

| Package                                     |     |   |        |   |   |   |   |    |

| B = DIP                                     |     |   |        |   |   |   |   |    |

| M = SO<br>U = VFQFPN                        |     |   |        |   |   |   |   |    |

|                                             |     |   |        |   |   |   |   |    |

| Temperature range                           |     |   |        |   |   |   |   |    |

| 6 = -40 °C to 85 °C                         |     |   |        |   |   |   |   |    |

| 3 = -40 °C to 125 °C                        |     |   |        |   |   |   |   |    |

| Shipping Option                             |     |   |        |   |   |   |   |    |

TR = Tape & Reel packing Blank = Tube (DIP or SO) or Tray (VFQFPN)

57

For a list of available options (e.g. data EEPROM, package) and orderable part numbers or for further information on any aspect of this device, please contact the ST Sales Office nearest to you.