Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | SPI                                                                    |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 11                                                                     |

| Program Memory Size        | 4KB (4K x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 128 x 8                                                                |

| RAM Size                   | 256 x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 5x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 16-SOIC (0.295", 7.50mm Width)                                         |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st7flit19by1m3 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## FLASH PROGRAM MEMORY (Cont'd)

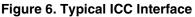

## 4.4 ICC interface

ICP needs a minimum of 4 and up to 6 pins to be connected to the programming tool. These pins are:

- RESET: device reset

- V<sub>SS</sub>: device power supply ground

- ICCCLK: ICC output serial clock pin

- ICCDATA: ICC input serial data pin

- OSC1: main clock input for external source (not required on devices without OSC1/OSC2 pins)

- $V_{DD}$ : application board power supply (optional, see Note 3)

#### Notes:

57/

1. If the ICCCLK or ICCDATA pins are only used as outputs in the application, no signal isolation is necessary. As soon as the Programming Tool is plugged to the board, even if an ICC session is not in progress, the ICCCLK and ICCDATA pins are not available for the application. If they are used as inputs by the application, isolation such as a serial resistor has to be implemented in case another device forces the signal. Refer to the Programming Tool documentation for recommended resistor values.

2. During the ICP session, the programming tool must control the RESET pin. This can lead to conflicts between the programming tool and the application reset circuit if it drives more than 5mA at high level (push pull output or pull-up resistor<1K). A schottky diode can be used to isolate the application RESET circuit in this case. When using a

classical RC network with R>1K or a reset management IC with open drain output and pull-up resistor>1K, no additional components are needed. In all cases the user must ensure that no external reset is generated by the application during the ICC session.

3. The use of pin 7 of the ICC connector depends on the Programming Tool architecture. This pin must be connected when using most ST Programming Tools (it is used to monitor the application power supply). Please refer to the Programming Tool manual.

4. Pin 9 has to be connected to the OSC1 pin of the ST7 when the clock is not available in the application or if the selected clock option is not programmed in the option byte. ST7 devices with multi-oscillator capability need to have OSC2 grounded in this case.

5. In 38-pulse ICC mode, the internal RC oscillator is forced as a clock source, regardless of the selection in the option byte. For ST7LITE10B devices which do not support the internal RC oscillator, the "option byte disabled" mode must be used (35pulse ICC mode entry, clock provided by the tool).

**Caution:** During normal operation the ICCCLK pin must be pulled- up, internally or externally (external pull-up of 10k mandatory in noisy environment). This is to avoid entering ICC mode unexpectedly during a reset. In the application, even if the pin is configured as output, any reset will put it back in input pull-up.

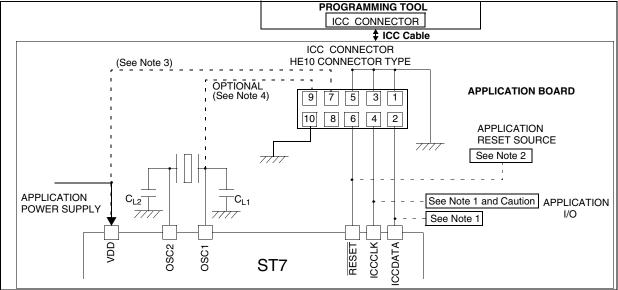

## 7.4 MULTI-OSCILLATOR (MO)

The main clock of the ST7 can be generated by four different source types coming from the multioscillator block (1 to 16MHz):

- an external source

- 5 different configurations for crystal or ceramic resonator oscillators

- an internal high frequency RC oscillator

Each oscillator is optimized for a given frequency range in terms of consumption and is selectable through the option byte. The associated hardware configurations are shown in Table 4. Refer to the electrical characteristics section for more details.

## External Clock Source

In this external clock mode, a clock signal (square, sinus or triangle) with ~50% duty cycle has to drive the OSC1 pin while the OSC2 pin is tied to ground.

**Note:** when the Multi-Oscillator is not used, PB4 is selected by default as external clock.

## Crystal/Ceramic Oscillators

In this mode, with a self-controlled gain feature, oscillator of any frequency from 1 to 16MHz can be placed on OSC1 and OSC2 pins. This family of oscillators has the advantage of producing a very accurate rate on the main clock of the ST7. In this mode of the multi-oscillator, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. The loading capacitance values must be adjusted according to the selected oscillator.

These oscillators are not stopped during the RESET phase to avoid losing time in the oscillator start-up phase.

## Internal RC Oscillator

57/

In this mode, the tunable 1%RC oscillator is used as main clock source. The two oscillator pins have to be tied to ground if dedicately using for oscillator else can be found as general purpose IO. The calibration is done through the RCCR[7:0] and SICSR[6:5] registers.

Table 4. ST7 Clock Sources

## SYSTEM INTEGRITY MANAGEMENT (Cont'd)

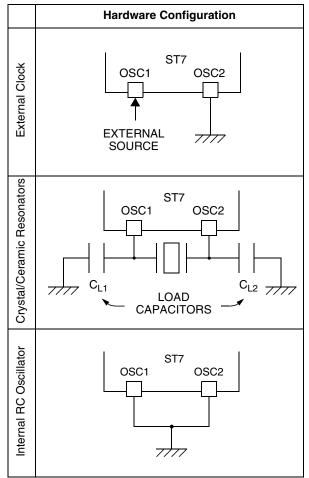

## 7.6.2 Auxiliary Voltage Detector (AVD)

The Voltage Detector function (AVD) is based on an analog comparison between a  $V_{IT\text{-}(AVD)}$  and  $V_{IT\text{+}(AVD)}$  reference value and the  $V_{DD}$  main supply voltage ( $V_{AVD}$ ). The  $V_{IT\text{-}(AVD)}$  reference value for falling voltage is lower than the  $V_{IT\text{+}(AVD)}$  reference value for rising voltage in order to avoid parasitic detection (hysteresis).

The output of the AVD comparator is directly readable by the application software through a real time status bit (AVDF) in the SICSR register. This bit is read only.

Caution: The AVD functions only if the LVD is en-

## Figure 20. Using the AVD to Monitor $V_{DD}$

57/

abled through the option byte.

## 7.6.2.1 Monitoring the $V_{\mbox{\scriptsize DD}}$ Main Supply

The AVD voltage threshold value is relative to the selected LVD threshold configured by option byte (see section 15.1 on page 149).

If the AVD interrupt is enabled, an interrupt is generated when the voltage crosses the  $V_{IT+(LVD)}$  or  $V_{IT-(AVD)}$  threshold (AVDF bit is set).

In the case of a drop in voltage, the AVD interrupt acts as an early warning, allowing software to shut down safely before the LVD resets the microcontroller. See Figure 20.

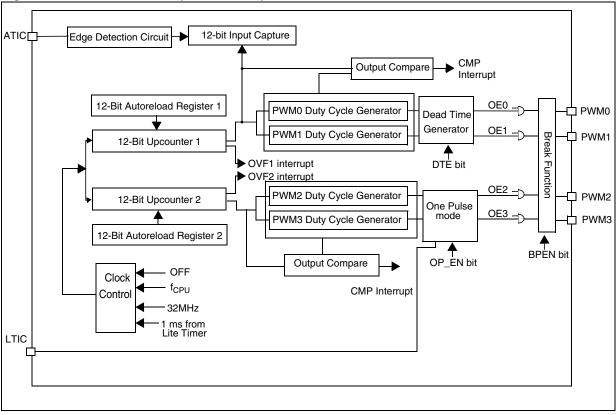

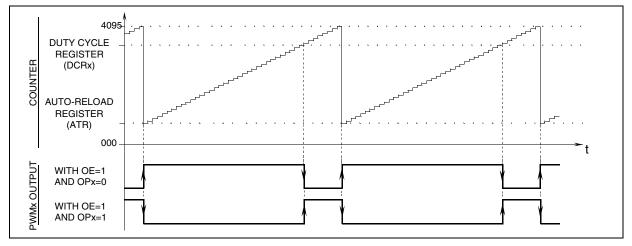

## Figure 38. PWM Function

## Figure 39. PWM Signal from 0% to 100% Duty Cycle

**لرك**ا

## 11.2.3.6 One Pulse Mode

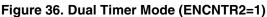

One Pulse Mode can be used to control PWM2/3 signal with an external LTIC pin. This mode is available only in dual timer mode i.e. only for CNTR2, when the OP\_EN bit in PWM3CSR register is set.

One Pulse Mode is activated by the external LTIC input. The active edge of the LTIC pin is selected by the OPEDGE bit in the PWM3CSR register.

After getting the active edge of the LTIC pin, CNTR2 is reset (000h) and PWM3 is set to high. CNTR2 starts counting from 000h, when it reaches the active DCR3 value then the PWM3 output goes low. Till this time, any further transitions on the LTIC signal will have no effect. If there are LTIC transitions after CNTR2 reaches the DCR3 value, CNTR2 is reset again and the PWM3 output goes high.

If there is no LTIC active edge then CNTR2 will count till it reaches the ATR2 value, and then it will be reset again and the PWM3 output is set to high. The counter again starts counting from 000h, when it reaches the active DCR3 value the PWM3 output goes low, the counter counts till it reaches the ATR2 value, it resets and the PWM3 output is set to high and it goes on the same way.

The same operation applies for the PWM2 output, but in this case the comparison is done on the DCR2 value.

The OP\_EN and OPEDGE bits take effect on the fly and are not synchronized with the CNTR2 over-flow.

The OP2/3 bits can be used to inverse the polarity of the PWM2/3 outputs in one-pulse mode. The update of these bits (OP2/3) is synchronized with the CNTR2 overflow, they will be updated if the TRAN2 bit is set.

#### Notes:

1. If CNTR2 is running at 32 MHz, the time taken from activation of LTIC input and CNTR2 reset is between 2 and 3  $t_{CNTR2}$  cycles, i.e. 66 ns to 99 ns (with 8 MHz  $f_{cpu}$ ).

2. The Lite Timer input capture interrupt must be disabled while 12-bit ARTimer is in One Pulse Mode. This is to avoid spurious interrupts.

3. The priority of various events affecting PWM3 is as follows:

- Break (Highest priority)

- One-pulse mode with active LTIC edge

- Forced overflow (by FORCE2 bit)

- One-pulse mode without active LTIC edge

- Normal PWM operation. (Lowest priority)

4. It is possible to synchronize the update of DCR2/3 registers and OP2/3 bits with the CNTR2 reset. This is managed by the overflow interrupt which is generated if CNTR2 is reset either due to an ATR match or an active pulse on the LTIC pin.

5. Updating the DCR2/3 registers and OP2/3 bits in one-pulse mode is done dynamically by software using force update (FORCE2 bit in the ATCSR2 register).

6. DCR3 update in this mode is not synchronized with any event. Consequently the next PWM3 cycle just after the change may be longer than expected (refer to Figure 15).

7. In One Pulse Mode the ATR2 value must be greater than the DCR2/3 value for the PWM2/3 outputs. (contrary to normal PWM mode)

8. If there is an active edge on the LTIC pin after the CNTR2 has reset due to an ATR2 match, then the timer gets reset again. The duty cycle may be modified depending on whether the new DCR value is less than or more than the previous value.

9. The TRAN2 bit must be set simultaneously with the FORCE2 bit in the same instruction after a write to the DCR register.

10. The ATR2 value should be changed after an overflow in one pulse mode to avoid an irregular PWM cycle.

11. When exiting from one pulse mode, the OP\_EN bit in the PWM3CSR register must be reset first and then the ENCNTR2 bit (if CNTR2 is to be stopped).

#### How to Enter One Pulse Mode:

1. Load the ATR2H/ATR2L registers with required value.

2. Load the DCR3H/DCR3L registers for PWM3 output. The ATR2 value must be greater than DCR3.

3. Set the OP3 bit in the PWM3CSR register if polarity change is required.

4. Start the CNTR2 counter by setting the ENCNTR2 bit in the ATCSR2 register.

5. Set TRAN2 bit in ATCSR2 to enable transfer.

6. Wait for an overflow event by polling the OVF2 flag in the ATCSR2 register.

7. Select the counter clock using the CK[1:0] bits in the ATCSR register.

## 11.2.4 Low Power Modes

| Mode | Description           |

|------|-----------------------|

| WAIT | No effect on AT timer |

| HALT | AT timer halted.      |

## 11.2.5 Interrupts

57

| Interrupt<br>Event | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt | Exit<br>from<br>Active-<br>Halt |

|--------------------|---------------|--------------------------|----------------------|----------------------|---------------------------------|

| Overflow<br>Event  | OVF1          | OVIE1                    | Yes                  | No                   | Yes                             |

| AT4 IC Event       | ICF           | ICIE                     | Yes                  | No                   | No                              |

| CMP Event          | CMPFx         | CMPIE                    | Yes                  | No                   | No                              |

| Overflow<br>Event2 | OVF2          | OVIE2                    | Yes                  | No                   | No                              |

**Note:** The CMP and AT4 IC events are connected to the same interrupt vector.

The OVF event is mapped on a separate vector (see Interrupts chapter).

They generate an interrupt if the enable bit is set in the ATCSR register and the interrupt mask in the CC register is reset (RIM instruction).

## 11.2.6 Register Description

#### TIMER CONTROL STATUS REGISTER (ATCSR) Read / Write

Reset Value: 0x00 0000 (x0h)

| 7 |     |      |     |     |      |        | 0     |

|---|-----|------|-----|-----|------|--------|-------|

| 0 | ICF | ICIE | CK1 | CK0 | OVF1 | OVFIE1 | CMPIE |

Bit 7 = Reserved.

## Bit 6 = **ICF** Input Capture Flag.

This bit is set by hardware and cleared by software by reading the ATICR register (a read access to ATICRH or ATICRL will clear this flag). Writing to this bit does not change the bit value.

0: No input capture

1: An input capture has occurred

Bit 5 = **ICIE** *IC* Interrupt Enable. This bit is set and cleared by software. 0: Input capture interrupt disabled 1: Input capture interrupt enabled

## Bits 4:3 = **CK[1:0]** Counter Clock Selection.

These bits are set and cleared by software and cleared by hardware after a reset. They select the clock frequency of the counter.

| Counter Clock Selection                     | CK1 | СКО |

|---------------------------------------------|-----|-----|

| OFF                                         | 0   | 0   |

| 32 MHz                                      | 1   | 1   |

| f <sub>LTIMER</sub> (1 ms timebase @ 8 MHz) | 0   | 1   |

| f <sub>CPU</sub>                            | 1   | 0   |

## Bit 2 = OVF1 Overflow Flag.

This bit is set by hardware and cleared by software by reading the ATCSR register. It indicates the transition of the counter1 CNTR1 from FFFh to ATR1 value.

0: No counter overflow occurred

1: Counter overflow occurred

## Bit 1 = **OVFIE1** Overflow Interrupt Enable.

This bit is read/write by software and cleared by hardware after a reset.

0: Overflow interrupt disabled.

1: Overflow interrupt enabled.

## Bit 0 = **CMPIE** Compare Interrupt Enable.

This bit is read/write by software and cleared by hardware after a reset. It can be used to mask the interrupt generated when any of the CMPFx bit is set.

0: Output compare interrupt disabled.

1: Output Compare interrupt enabled.

## **COUNTER REGISTER 1 HIGH (CNTR1H)**

Read only

Reset Value: 0000 0000 (00h)

| 15 |   |   |   |              |              |             | 8           |

|----|---|---|---|--------------|--------------|-------------|-------------|

| 0  | 0 | 0 | 0 | CNTR1_<br>11 | CNTR1_<br>10 | CNTR1_<br>9 | CNTR1_<br>8 |

## COUNTER REGISTER 1 LOW (CNTR1L)

Read only

7

Reset Value: 0000 0000 (00h)

| -      |        |        |        |        |        |        | -      |

|--------|--------|--------|--------|--------|--------|--------|--------|

| CNTR1_ |

| 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

Bits 15:12 = Reserved.

## Bits 11:0 = CNTR1[11:0] Counter Value.

This 12-bit register is read by software and cleared by hardware after a reset. The counter CNTR1 increments continuously as soon as a counter clock is selected. To obtain the 12-bit value, software should read the counter value in two consecutive read operations. As there is no latch, it is recommended to read LSB first. In this case, CNTR1H can be incremented between the two read operations and to have an accurate result when  $f_{timer}=f_{CPU}$ , special care must be taken when CNTR1L values close to FFh are read.

When a counter overflow occurs, the counter restarts from the value specified in the ATR1 register.

0

Bits 11:0 = ICR[11:0] Input Capture Data.

This is a 12-bit register which is readable by software and cleared by hardware after a reset. The ATICR register contains captured the value of the 12-bit CNTR1 register when a rising or falling edge occurs on the ATIC or LTIC pin (depending on

ICS). Capture will only be performed when the ICF flag is cleared.

## **BREAK ENABLE REGISTER (BREAKEN)**

#### Read/Write

Reset Value: 0000 0011 (03h)

7

0

0

0

0

0

BREN2

BREN1

Bits 7:2 = Reserved, must be kept cleared.

#### Bit 1 = BREN2 Break Enable for Counter 2

This bit is read/write by software. It enables the break functionality for Counter2 if BA bit is set in BREAKCR. It controls PWM2/3 if ENCNTR2 bit is set.

0: No Break applied for CNTR2 1: Break applied for CNTR2

## Bit 0 = BREN1 Break Enable for Counter 1

This bit is read/write by software. It enables the break functionality for Counter1. If BA bit is set, it controls PWM0/1 by default, and controls PWM2/3 also if ENCNTR2 bit is reset.

0: No Break applied for CNTR1

1: Break applied for CNTR1

#### TIMER CONTROL REGISTER2 (ATCSR2) Read/Write

Reset Value: 0000 0011 (03h)

5/

| 7          |            |     |        |      |             |       | 0     |

|------------|------------|-----|--------|------|-------------|-------|-------|

| FORCE<br>2 | FORCE<br>1 | ICS | OVFIE2 | OVF2 | ENCNT<br>R2 | TRAN2 | TRAN1 |

## Bit 7 = FORCE2 Force Counter 2 Overflow

This bit is read/set by software. When set, it loads FFFh in the CNTR2 register. It is reset by hard-

ware one CPU clock cycle after counter 2 overflow has occurred.

0 : No effect on CNTR2

1 : Loads FFFh in CNTR2

Note: This bit must not be reset by software

#### Bit 6 = FORCE1 Force Counter 1 Overflow

This bit is read/set by software. When set, it loads FFFh in CNTR1 register. It is reset by hardware one CPU clock cycle after counter 1 overflow has occurred.

0 : No effect on CNTR1

1 : Loads FFFh in CNTR1

Note: This bit must not be reset by software

#### Bit 5 = ICS Input Capture Shorted

This bit is read/write by software. It allows the ATtimer CNTR1 to use the LTIC pin for long input capture.

0 : ATIC for CNTR1 input capture

1 : LTIC for CNTR1 input capture

## Bit 4 = **OVFIE2** Overflow interrupt 2 enable

This bit is read/write by software and controls the overflow interrupt of counter2.

0: Overflow interrupt disabled.

1: Overflow interrupt enabled.

## Bit 3 = **OVF2** Overflow Flag.

This bit is set by hardware and cleared by software by reading the ATCSR2 register. It indicates the transition of the counter2 from FFFh to ATR2 value.

0: No counter overflow occurred 1: Counter overflow occurred

## Bit 2 = **ENCNTR2** Enable counter2 for PWM2/3

This bit is read/write by software and switches the PWM2/3 operation to the CNTR2 counter. If this bit is set, PWM2/3 will be generated using CNTR2. 0: PWM2/3 is generated using CNTR1. 1: PWM2/3 is generated using CNTR2.

**Note:** Counter 2 gets frozen when the ENCNTR2 bit is reset. When ENCNTR2 is set again, the counter will restart from the last value.

LITE TIMER (Cont'd)

Bit 6 = **ICF** *Input Capture Flag* This bit is set by hardware and cleared by software by reading the LTICR register. Writing to this bit does not change the bit value. 0: No input capture 1: An input capture has occurred

**Note:** After an MCU reset, software must initialize the ICF bit by reading the LTICR register

Bit 5 = **TB** *Timebase period selection* This bit is set and cleared by software. 0: Timebase period =  $t_{OSC} * 8000 (1ms @ 8 MHz)$ 1: Timebase period =  $t_{OSC} * 16000 (2ms @ 8 MHz)$

Bit 4 = **TB1IE** *Timebase Interrupt enable* This bit is set and cleared by software. 0: Timebase (TB1) interrupt disabled 1: Timebase (TB1) interrupt enabled

Bit 3 =**TB1F** *Timebase Interrupt Flag* This bit is set by hardware and cleared by software reading the LTCSR register. Writing to this bit has no effect.

0: No counter overflow

1: A counter overflow has occurred

Bits 2:0 = Reserved

#### LITE TIMER INPUT CAPTURE REGISTER (LTICR) Read only

Reset Value: 0000 0000 (00h)

7

| ICR7 | ICR6 | ICR5 | ICR4 | ICR3 | ICR2 | ICR1 | ICR0 |

|------|------|------|------|------|------|------|------|

0

## Bits 7:0 = ICR[7:0] Input Capture Value

These bits are read by software and cleared by hardware after a reset. If the ICF bit in the LTCSR is cleared, the value of the 8-bit up-counter will be captured when a rising or falling edge occurs on the LTIC pin.

## LITE TIMER (Cont'd)

57

## Table 15. Lite Timer Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label     | 7         | 6        | 5       | 4          | 3         | 2    | 1          | 0         |

|-------------------|-----------------------|-----------|----------|---------|------------|-----------|------|------------|-----------|

| 08                | LTCSR2<br>Reset Value | 0         | 0        | 0       | 0          | 0         | 0    | TB2IE<br>0 | TB2F<br>0 |

| 09                | LTARR                 | AR7       | AR6      | AR5     | AR4        | AR3       | AR2  | AR1        | AR0       |

|                   | Reset Value           | 0         | 0        | 0       | 0          | 0         | 0    | 0          | 0         |

| 0A                | LTCNTR                | CNT7      | CNT6     | CNT5    | CNT4       | CNT3      | CNT2 | CNT1       | CNT0      |

|                   | Reset Value           | 0         | 0        | 0       | 0          | 0         | 0    | 0          | 0         |

| 0B                | LTCSR1<br>Reset Value | ICIE<br>0 | ICF<br>x | ТВ<br>0 | TB1IE<br>0 | TB1F<br>0 | 0    | 0          | 0         |

| 0C                | LTICR                 | ICR7      | ICR6     | ICR5    | ICR4       | ICR3      | ICR2 | ICR1       | ICR0      |

|                   | Reset Value           | 0         | 0        | 0       | 0          | 0         | 0    | 0          | 0         |

## **ON-CHIP PERIPHERALS** (cont'd)

## **11.4 SERIAL PERIPHERAL INTERFACE (SPI)**

#### 11.4.1 Introduction

The Serial Peripheral Interface (SPI) allows fullduplex, synchronous, serial communication with external devices. An SPI system may consist of a master and one or more slaves or a system in which devices may be either masters or slaves.

#### 11.4.2 Main Features

- Full duplex synchronous transfers (on three lines)

- Simplex synchronous transfers (on two lines)

- Master or slave operation

- 6 master mode frequencies (f<sub>CPU</sub>/4 max.)

- I f<sub>CPU</sub>/2 max. slave mode frequency (see note)

- SS Management by software or hardware

- Programmable clock polarity and phase

- End of transfer interrupt flag

- Write collision, Master Mode Fault and Overrun flags

**Note:** In slave mode, continuous transmission is not possible at maximum frequency due to the software overhead for clearing status flags and to initiate the next transmission sequence.

## **11.4.3 General Description**

Figure 1 on page 3 shows the serial peripheral interface (SPI) block diagram. There are three registers:

- SPI Control Register (SPICR)

- SPI Control/Status Register (SPICSR)

- SPI Data Register (SPIDR)

The SPI is connected to external devices through four pins:

- MISO: Master In / Slave Out data

- MOSI: Master Out / Slave In data

- SCK: Serial Clock out by SPI masters and input by SPI slaves

- SS: Slave select:

This input signal acts as a 'chip select' to let the SPI master communicate with slaves individually and to avoid contention on the data lines. Slave SS inputs can be driven by standard I/O ports on the master Device.

## ANALOG COMPARATOR (Cont'd)

## Bit 4 = CMPIF Comparator Interrupt Flag

This bit is set by hardware when interrupt is generated at the rising edge (CINV = 0) or falling edge (CINV = 1) of comparator output. This bit is cleared by reading the CMPCR register. Writing to this bit does not change the value.

0 : Comparator interrupt flag cleared

1 : Comparator interrupt flag set and can generate interrupt if CMPIE is set.

## Bit 3 : CMPIE Comparator Interrupt Enable

This bit is set or reset by software and cleared by hardware reset. This bit enables or disables the interrupt generation depending on interrupt flag 0: Interrupt not generated

1: Interrupt generated if interrupt flag is set

## Note:

57/

This bit should be set to enable interrupt only after the comparator has been switched ON, i.e. when CMPON is set.

Once CMPON bit is set, it is recommended to wait the specified stabilization time before setting CMPIE bit in order to avoid a spurious interrupt (see section 13.12 on page 143).

## Bit 2 : CMP Comparator Output

This bit is set or reset by software and cleared by hardware reset. It stores the value of comparator output.

Bit 1 = COUT Comparator Output Enable on Port This bit is set or cleared by software. When this bit is set, the comparator output is available on PA7 port.

0 : Comparator output not connected to PA7

1 : Comparator output connected to PA7

## Bit 0 : CMPON Comparator ON/OFF

This bit is set or cleared by software and reset by hardware reset. This bit is used to switch ON/OFF the comparator, internal voltage reference and current bias which provides  $4\mu$ A current to both. 0: Comparator, Internal Voltage Reference, Bias

- OFF (in power-down state).

- 1: Comparator, Internal Voltage Reference, Bias ON

**Note:** For the comparator interrupt generation, it takes 250ns delay from comparator output change to rising or falling edge of interrupt generated.

## Table 21. Analog Comparator Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label | 7     | 6     | 5    | 4     | 3     | 2   | 1    | 0     |

|-------------------|-------------------|-------|-------|------|-------|-------|-----|------|-------|

| 002Ch             | VREFCR            | VCEXT | VCBGR | VR3  | VR2   | VR1   | VR0 | -    | -     |

|                   | Reset Value       | 0     | 0     | 0    | 0     | 0     | 0   | 0    | 0     |

| 002Dh             | CMPCR             | CHYST | -     | CINV | CMPIF | CMPIE | CMP | COUT | CMPON |

|                   | Reset value       | 1     | 0     | 0    | 0     | 0     | 0   | 0    | 0     |

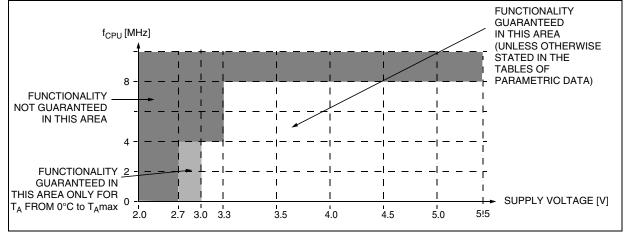

## **13.3 OPERATING CONDITIONS**

## 13.3.1 General Operating Conditions: Suffix 6 Devices

$T_A = -40$  to  $+85^{\circ}C$  unless otherwise specified.

| Symbol           | Parameter                      | Min                                                   | Max     | Unit |     |

|------------------|--------------------------------|-------------------------------------------------------|---------|------|-----|

|                  | V <sub>DD</sub> Supply voltage | $f_{CPU} = 4$ MHz. max., $T_A = 0$ to $85^{\circ}C$   | 2.7     | 5.5  |     |

| $V_{DD}$         |                                | $f_{CPU} = 4$ MHz. max., $T_A = -40$ to $85^{\circ}C$ | 3.0     | 5.5  | V   |

|                  |                                | f <sub>CPU</sub> = 8 MHz. max.                        | 3.3     | 5.5  | Ī   |

| f                | CPU clock frequency            | V <sub>DD</sub> ≥3.3V                                 | up      | to 8 | MHz |

| † <sub>CPU</sub> | CFO Clock frequency            | $2.7V \le V_{DD} < 3.3V$                              | up to 4 |      |     |

## 13.3.2 General Operating Conditions: Suffix 3 Devices

$T_A = -40$  to  $+125^{\circ}C$  unless otherwise specified.

| Symbol           | Parameter                                                                                                                    | Conditions                                             | Min     | Max  | Unit |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------|------|------|

|                  |                                                                                                                              | $f_{CPU} = 4$ MHz. max., $T_A = 0$ to $125^{\circ}C$   | 2.7     | 5.5  |      |

| V <sub>DD</sub>  | Supply voltage $f_{CPU} = 4 \text{ MHz. max.}, T_A = -40 \text{ to } 125^{\circ}\text{C}$<br>$f_{CPU} = 8 \text{ MHz. max.}$ | $f_{CPU} = 4$ MHz. max., $T_A = -40$ to $125^{\circ}C$ | 3.0     | 5.5  | V    |

|                  |                                                                                                                              | 3.3                                                    | 5.5     |      |      |

| f <sub>CPU</sub> | CPU clock frequency                                                                                                          | V <sub>DD</sub> ≥3.3V                                  | up to 8 |      | MHz  |

|                  | CFO clock frequency                                                                                                          | 2.7V≤V <sub>DD</sub> <3.3V                             | up      | to 4 |      |

## Figure 65. $f_{CPU}$ Maximum Operating Frequency Versus V<sub>DD</sub> Supply Voltage

## EMC CHARACTERISTICS (Cont'd)

# 13.7.3 Absolute Maximum Ratings (Electrical Sensitivity)

Based on two different tests (ESD and LU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

## 13.7.3.1 Electro-Static Discharge (ESD)

Electro-Static Discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). Two models can be simulated: Human Body Model and Machine Model. This test conforms to the JESD22-A114A/A115A standard.

## Absolute Maximum Ratings

| Symbol                                                                   | Ratings                                                | Conditions            | Maximum value <sup>1)</sup> | Unit |

|--------------------------------------------------------------------------|--------------------------------------------------------|-----------------------|-----------------------------|------|

| V <sub>ESD(HBM)</sub>                                                    | Electro-static discharge voltage<br>(Human Body Model) | T <sub>A</sub> =+25°C | 8000                        | V    |

| V <sub>ESD(MM)</sub> Electro-static discharge voltage<br>(Machine Model) |                                                        | T <sub>A</sub> =+25°C | 400                         | v    |

#### Note:

1. Data based on characterization results, not tested in production.

## 13.7.3.2 Static Latch-Up

LU: 3 complementary static tests are required on 6 parts to assess the latch-up performance. A supply overvoltage (applied to each power supply pin) and a current injection (applied to each input, output and configurable I/O pin) are performed on each sample. This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

#### **Electrical Sensitivities**

| Symbol | Parameter            | Conditions                                     | Class |  |

|--------|----------------------|------------------------------------------------|-------|--|

| LU St  | tatic latch-up class | T <sub>A</sub> =+25°C<br>T <sub>A</sub> =+85°C | A     |  |

## COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)

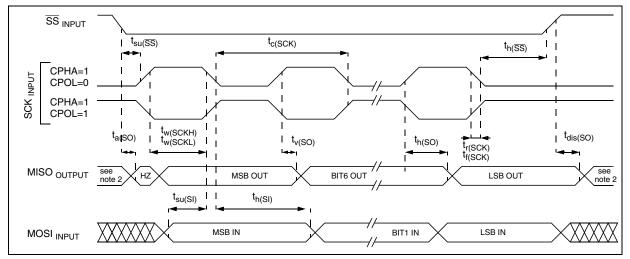

## Figure 108. SPI Slave Timing Diagram with CPHA=1<sup>1)</sup>

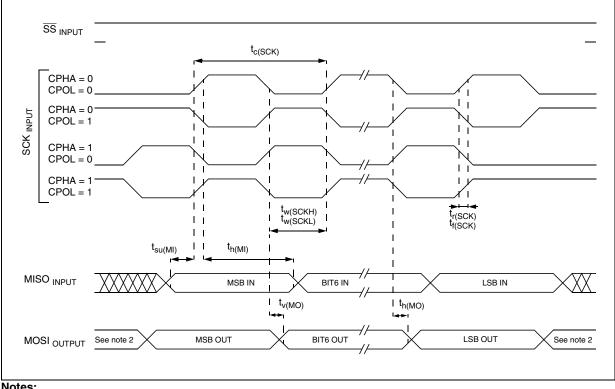

## Figure 109. SPI Master Timing Diagram <sup>1)</sup>

#### Notes:

1. Measurement points are done at CMOS levels:  $0.3xV_{DD}$  and  $0.7xV_{DD}$ .

2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends of the I/O port configuration.

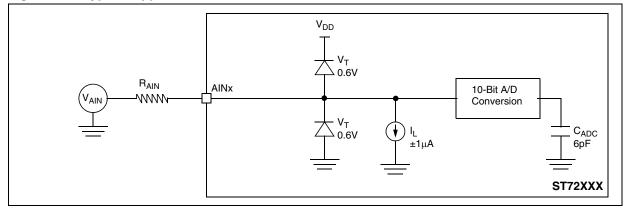

## 13.11 10-BIT ADC CHARACTERISTICS

Subject to general operating condition for V<sub>DD</sub>, f<sub>OSC</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol                                                                     | Parameter                                                                    | Conditions | Min Typ <sup>1)</sup> Max |     | Unit             |                    |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------|------------|---------------------------|-----|------------------|--------------------|

| f <sub>ADC</sub>                                                           | ADC clock frequency                                                          |            | 4                         |     | MHz              |                    |

| V <sub>AIN</sub>                                                           | Conversion voltage range <sup>2)</sup>                                       |            | V <sub>SSA</sub>          |     | V <sub>DDA</sub> | V                  |

| R <sub>AIN</sub>                                                           | External input resistor                                                      |            |                           |     | 10 <sup>3)</sup> | kΩ                 |

| C <sub>ADC</sub>                                                           | Internal sample and hold capacitor                                           |            |                           | 6   |                  | pF                 |

| t <sub>STAB</sub>                                                          | Stabilization time after ADC enable                                          |            | 0 <sup>4)</sup>           |     |                  |                    |

|                                                                            | Conversion time (Sample+Hold) f <sub>CPU</sub> =8MHz, f <sub>ADC</sub> =4MHz |            | 3.5                       |     |                  | μs                 |

| t <sub>ADC</sub> - Sample capacitor loading time<br>- Hold conversion time |                                                                              |            | 4<br>10                   |     |                  | 1/f <sub>ADC</sub> |

| I <sub>ADC</sub>                                                           | Analog Part                                                                  |            |                           | 1   |                  | mA                 |

|                                                                            | Digital Part                                                                 |            |                           | 0.2 |                  | INA                |

## Figure 110. Typical Application with ADC

#### Notes:

47/

1. Unless otherwise specified, typical data are based on  $T_A=25^{\circ}C$  and  $V_{DD}-V_{SS}=5V$ . They are given only as design guide-lines and are not tested.

2. When  $V_{DDA}$  and  $V_{SSA}$  pins are not available on the pinout, the ADC refers to  $V_{DD}$  and  $V_{SS}$ .

3. Any added external serial resistor will downgrade the ADC accuracy (especially for resistance greater than  $10k\Omega$ ). Data based on characterization results, not tested in production.

4. The stabilization time of the AD converter is masked by the first  $t_{LOAD}$ . The first conversion after the enable is then always valid.

## **Related application notes:**

Understanding and minimizing ADC conversion errors (AN1636) Software techniques for compensating ST7 ADC errors (AN1711)

## OPTION BYTES (Cont'd)

## **OPTION BYTE 1**

OPT7 = **PLLx4x8** *PLL Factor selection.* 0: PLLx4 1: PLLx8

OPT6 = **PLLOFF** *PLL disable.* 0: PLL enabled 1: PLL disabled (by-passed)

OPT5 = **PLL32OFF** *32MHz PLL disable.* 0: PLL32 enabled 1: PLL32 disabled (by-passed)

OPT4 = **OSC** *RC* Oscillator selection 0: RC oscillator on 1: RC oscillator off

## Notes:

- 1% RC oscillator available on ST7LITE15B and ST7LITE19B devices only

- If the RC oscillator is selected, then to improve clock stability and frequency accuracy, it is recommended to place a decoupling capacitor, typically 100nF, between the V<sub>DD</sub> and V<sub>SS</sub> pins as close as possible to the ST7 device.

# OPT3:2 = **LVD[1:0]** Low voltage detection selection

These option bits enable the LVD block with a selected threshold as shown in Table 26.

## Table 26. LVD Threshold Configuration

| Configuration                     | LVD1 | LVD0 |

|-----------------------------------|------|------|

| LVD Off                           | 1    | 1    |

| Highest Voltage Threshold (~4.1V) | 1    | 0    |

| Medium Voltage Threshold (~3.5V)  | 0    | 1    |

| Lowest Voltage Threshold (~2.8V)  | 0    | 0    |

## OPT1 = **WDG SW** Hardware or Software Watchdog

This option bit selects the watchdog type.

0: Hardware (watchdog always enabled)

1: Software (watchdog to be enabled by software)

OPT0 = **WDG HALT** *Watchdog Reset on Halt* This option bit determines if a RESET is generated when entering HALT mode while the Watchdog is active.

0: No Reset generation when entering Halt mode 1: Reset generation when entering Halt mode

|                       | Operating conditions         |     |                      |     | Option Bits | ;       |

|-----------------------|------------------------------|-----|----------------------|-----|-------------|---------|

| V <sub>DD</sub> range | Clock Source                 | PLL | Typ f <sub>CPU</sub> | OSC | PLLOFF      | PLLx4x8 |

|                       | Internal RC 1% <sup>1)</sup> | off | 1MHz @3.3V           | 0   | 1           | 1       |

|                       |                              | x4  | 4MHz @3.3V           | 0   | 0           | 0       |

| 2.7V - 3.3V           |                              | x8  | -                    | -   | -           | -       |

| 2.7 V - 3.3 V         | External clock               | off | 0-4MHz               | 1   | 1           | 1       |

|                       |                              | x4  | 4MHz                 | 1   | 0           | 0       |

|                       |                              | x8  | -                    | -   | -           | -       |

|                       |                              | off | 1MHz @5V             | 0   | 1           | 1       |

|                       | Internal RC 1% <sup>1)</sup> | x4  | -                    | -   | -           | -       |

| 3.3V - 5.5V           |                              | x8  | 8MHz @5V             | 0   | 0           | 1       |

|                       | External clock               | off | 0-8MHz               | 1   | 1           | 1       |

|                       |                              | x4  | -                    | -   | -           | -       |

|                       |                              | x8  | 8 MHz                | 1   | 0           | 1       |

## Table 27. List of valid option combinations

Note 1: Configuration available on ST7LITE15B and ST7LITE19B devices only

Note: see Clock Management Block diagram in Figure 14

| ST7                                                                                                                                  | LITE1xB FASTROM                                                                                       | microcontroller                              | option list                                                                          |                                       |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------|

| Customer<br>Address<br>Contact<br>Phone No<br>Reference/FASTROM Code*:<br>*FASTROM code name is assig<br>FASTROM code must be sent i | ned by STMicroelect                                                                                   | ronics.                                      | be processed.                                                                        | · · · · · · · · · · · · · · · · · · · |

| Device Type/Memory Size/Pack                                                                                                         |                                                                                                       |                                              |                                                                                      |                                       |

| FASTROM DEVICE:                                                                                                                      | 2K                                                                                                    |                                              | 4K                                                                                   |                                       |

| VFQFPN20:  <br>SO20:  <br>PDIP20:  <br>SO16:  <br>PDIP16:                                                                            | [] ST7PLIT19BF0Ux<br>[] ST7PLIT19BF0Mx<br>[] ST7PLIT19BF0Bx<br>[] ST7PLIT19BY0Mx<br>[] ST7PLIT19BY0Bx | []ST<br>  []ST<br>  []ST<br>  []ST<br>  []ST | 7PLIT19BF1Ux  <br>7PLIT19BF1Mx  <br>7PLIT19BF1Bx  <br>7PLIT19BY1Mx  <br>7PLIT19BY1Bx |                                       |

| Warning: Addresses DEE0h, and RCCR1 (see section 7.1 c                                                                               | DEE1h, DEE2h and<br>n page 23).                                                                       | DEE3h are rese                               | rved areas for ST to program R                                                       | CCR0                                  |

| Conditioning (check only one o<br>VFQFPN [<br>SO [                                                                                   | ption, do not specify f                                                                               | or DIP package)                              |                                                                                      |                                       |

| Special marking: [] No<br>Authorized characters are lette<br>Maximum character count: 8 c                                            | )<br>ers, digits, '.', '-', '/' ar<br>har. max                                                        | [] Yes "<br>nd spaces only.<br>              | "<br>                                                                                |                                       |

| Temperature range:                                                                                                                   | []-40°C to                                                                                            | ) +85°C                                      | [] -40°C to +125°C                                                                   |                                       |

| Watchdog selection (WDG_SV                                                                                                           | V): [] Software                                                                                       | e activation                                 | [] Hardware activation                                                               |                                       |

| Watchdog reset on Halt (WDG                                                                                                          | _HALT): [] Reset                                                                                      |                                              | [] No Reset                                                                          |                                       |

| LVD reset (LVD):                                                                                                                     | [] Disabled                                                                                           | Ŀ                                            | [] Enabled<br>[] Highest threshold<br>[] Medium threshold<br>[] Lowest threshold     |                                       |

| Sector 0 size (SEC):                                                                                                                 | []0.5K                                                                                                | [] 1K                                        | []2K []4K                                                                            |                                       |

| Readout protection (FMP_R):                                                                                                          | [] Disabled                                                                                           | [] Enabled                                   |                                                                                      |                                       |

| Flash write protection (FMP_V                                                                                                        | /): [] Disabled                                                                                       | [] Enabled                                   |                                                                                      |                                       |

| RC oscillator (OSC) :                                                                                                                | [] Disabled                                                                                           | [] Enabled                                   |                                                                                      |                                       |

| Clock source selection (CKSE<br>(if OSC disabled)                                                                                    |                                                                                                       | tal / ceramic reso<br>ck on PB4<br>ck on PC0 | onator:                                                                              |                                       |

| PLL (PLLOFF):                                                                                                                        | [] Disabled                                                                                           | [] Enabled                                   |                                                                                      |                                       |

| PLL factor (PLLx4x8):                                                                                                                | [] PLLx4                                                                                              | [] PLLx8                                     |                                                                                      |                                       |

| PLL32 (PLL32OFF):                                                                                                                    | [] Disabled                                                                                           | [] Enabled                                   |                                                                                      |                                       |

| Supply operating range in the a<br>Notes<br>Date :<br>Signature :                                                                    | pplication :                                                                                          |                                              | on page 150 for authorized option                                                    | · · · · ·                             |

| combinations.                                                                                                                        |                                                                                                       |                                              |                                                                                      |                                       |

## **16 REVISION HISTORY**

57

| Date       | Revision | Main changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20-Dec-05  | 1        | Initial release on internet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 20-July-06 | 2        | Added reset default state in bold for RESET, PC0 and PC1 in Table 1, "Device Pin Description," on page 7<br>Changed note below Figure 9 on page 17 and the last paragraph of "ACCESS ERROR HAN-<br>DLING" on page 18<br>Modified note 3 in Table 2, "Hardware Register Map," on page 10, changed LTICR reset value<br>and replaced h by b for LTCSR1, ATCSR and SICSR reset values<br>Added note to Figure 14 on page 26<br>Modified aution in section 7.2 on page 23<br>Added note to Figure 14 on page 26<br>Modified exution in section 7.2 on page 48<br>Removed references to true open drain in Table 8 on page 50, Table 9 on page 51 and notes<br>Replaced Auto reload timer 3 by Auto reload timer 4 in section 11.2. on page 57<br>Modified the BA bit description in the BREAKCR register in section 11.2.6 on page 70<br>Changed order of Section 11.3.3.2 and section 11.3.3.3 on page 80 and removed two para-<br>graphs before section 11.3.4 on page 81<br>Modified Section 11.3.4.2 and section 11.6.4 on page 100 and added note to CHYST bit descrip-<br>tion in section 11.6.4 on page 101<br>Modified CINC bit description in section 11.6.4 on page 102 and Figure 62 on page 101<br>Changed ortSR2 reset values in Table 2 on page 10 and in section 11.3.6 on page 81<br>Modified Section 13.3.2 on page 111 (I <sub>10</sub> values)<br>Modified Section 13.3.1 on page 112<br>Removed V <sub>POP</sub> min value in section 13.3.2 on page 112<br>Removed V <sub>POP</sub> min value in section 13.3.3.1 on page 113<br>Modified section 13.3.5.1 on page 114<br>Modified section 13.3.5.1 on page 121<br>Added note in section 13.5.3 on page 124<br>Removed figures "PLLx4 and PLLx8 Output vs CLKIN frequency"<br>Updated section 13.6.4 on page 127<br>Modified section 13.6.4 on page 127<br>Modified section 13.6.7 on page 137 (t <sub>sul</sub> (SE), t <sub>v</sub> (MO) and t <sub>v</sub> (MO))<br>Modified section 13.6.1 on page 137 (t <sub>sul</sub> (SE), t <sub>v</sub> (MO) and t <sub>v</sub> (MO))<br>Modified section 13.6.1 on page 137<br>Modified section 13.6.1 on page 138 (t <sub>v</sub> (MO)) t <sub>v</sub> (MO))<br>Removed empty figure "Typical I <sub>PU</sub> vs. O <sub>DD</sub> with V <sub>IN</sub> =V <sub>SS</sub> - in section 13.8.1 on page 129 and<br>modified section 13.0.1 on page 135<br>Added rister AD plication notes" |

| 15-Sept-06 | 3        | Removed QFN20 pinout and mechanical data.<br>Modified description of CNTR[11:0] bits in section 11.2.6 on page 72<br>Added "External Clock Source" on page 124 and Figure 78 on page 124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |