Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                |

|----------------------------|----------------------------------------------------------------|

| Product Status             | Last Time Buy                                                  |

| Core Processor             | 8051                                                           |

| Core Size                  | 8-Bit                                                          |

| Speed                      | 25MHz                                                          |

| Connectivity               | SMBus (2-Wire/l²C), SPI, UART/USART                            |

| Peripherals                | POR, PWM, Temp Sensor, WDT                                     |

| Number of I/O              | 17                                                             |

| Program Memory Size        | 8KB (8K x 8)                                                   |

| Program Memory Type        | OTP                                                            |

| EEPROM Size                | -                                                              |

| RAM Size                   | 768 x 8                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                    |

| Data Converters            | A/D 16x10b; D/A 1x10b                                          |

| Oscillator Type            | Internal                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                              |

| Mounting Type              | Surface Mount                                                  |

| Package / Case             | 20-VFQFN Exposed Pad                                           |

| Supplier Device Package    | 20-QFN (4x4)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051t630-gm |

| 22. | UART0       |                                          |     |

|-----|-------------|------------------------------------------|-----|

|     | Table 22.1. | Timer Settings for Standard Baud Rates   |     |

|     |             | Using The Internal 24.5 MHz Oscillator   | 155 |

|     | Table 22.2. | Timer Settings for Standard Baud Rates   |     |

|     |             | Using an External 22.1184 MHz Oscillator | 155 |

| 23. | Enhanced    | Serial Peripheral Interface (SPI0)       |     |

|     | Table 23.1. | SPI Slave Timing Parameters              | 168 |

| 25. | Programm    | able Counter Array                       |     |

|     | Table 25.1. | PCA Timebase Input Options               | 192 |

|     | Table 25.2. | PCA0CPM and PCA0PWM Bit Settings         |     |

|     |             | for PCA Capture/Compare Modules          | 194 |

|     | Table 25.3. | Watchdog Timer Timeout Intervals1        | 203 |

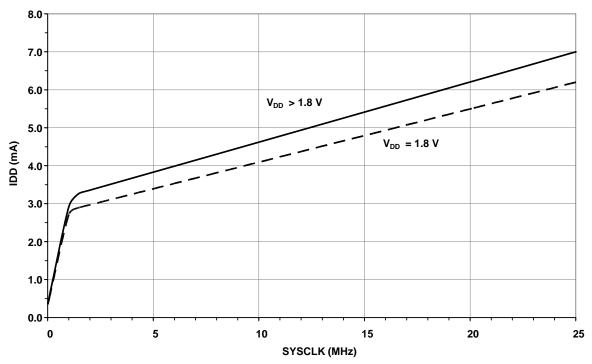

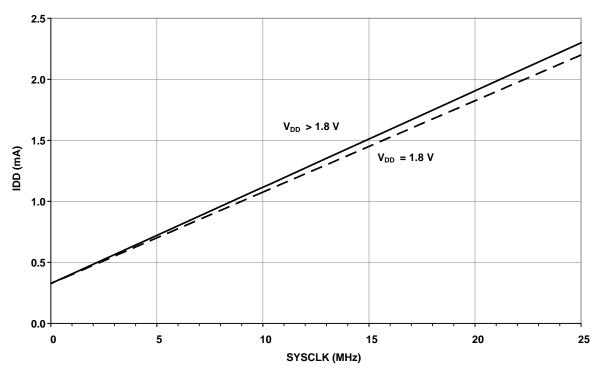

### **5.3. Typical Performance Curves**

Figure 5.1. Normal Mode Digital Supply Current vs. Frequency (MPCE = 1)

Figure 5.2. Idle Mode Digital Supply Current vs. Frequency (MPCE = 1)

SILICON LABS

## SFR Definition 8.1. IDA0CN: IDA0 Control

| Bit   | 7      | 6   | 5           | 4 | 3 | 2 | 1      | 0       |

|-------|--------|-----|-------------|---|---|---|--------|---------|

| Name  | IDA0EN |     | IDA0CM[2:0] |   |   |   | IDA00I | MD[1:0] |

| Туре  | R/W    | R/W |             |   | R | R | R/     | W       |

| Reset | 0      | 1   | 1           | 1 | 0 | 0 | 1      | 0       |

#### SFR Address = 0xB9

| Bit | Name         | Function                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IDA0EN       | IDA0 Enable. 0: IDA0 Disabled. 1: IDA0 Enabled.                                                                                                                                                                                                                                                                                                                                                                            |

| 6:4 | IDA0CM[2:0]  | IDA0 Update Source Select bits.  000: DAC output updates on Timer 0 overflow.  001: DAC output updates on Timer 1 overflow.  010: DAC output updates on Timer 2 overflow.  011: DAC output updates on Timer 3 overflow.  100: DAC output updates on rising edge of CNVSTR.  101: DAC output updates on falling edge of CNVSTR.  110: DAC output updates on any edge of CNVSTR.  111: DAC output updates on write to IDA0H. |

| 3:2 | Unused       | Unused. Read = 00b. Write = Don't care.                                                                                                                                                                                                                                                                                                                                                                                    |

| 1:0 | IDA0OMD[1:0] | IDA0 Output Mode Select bits.  00: 0.5 mA full-scale output current.  01: 1.0 mA full-scale output current.  1x: 2.0 mA full-scale output current.                                                                                                                                                                                                                                                                         |

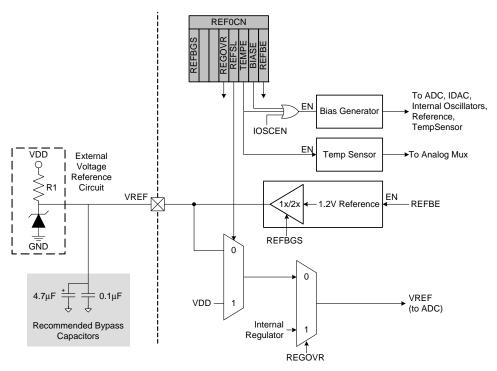

Figure 9.1. Voltage Reference Functional Block Diagram

### 11.1. Comparator Multiplexer

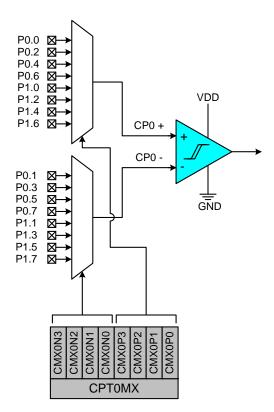

C8051T630/1/2/3/4/5 devices include an analog input multiplexer to connect Port I/O pins to the comparator inputs. The Comparator0 inputs are selected in the CPT0MX register (SFR Definition 11.3). The CMX-0P3–CMX0P0 bits select the Comparator0 positive input; the CMX0N3–CMX0N0 bits select the Comparator0 negative input. **Important Note About Comparator Inputs:** The Port pins selected as comparator inputs should be configured as analog inputs in their associated Port configuration register, and configured to be skipped by the Crossbar (for details on Port configuration, see Section "20.6. Special Function Registers for Accessing and Configuring Port I/O" on page 121).

Figure 11.3. Comparator Input Multiplexer Block Diagram

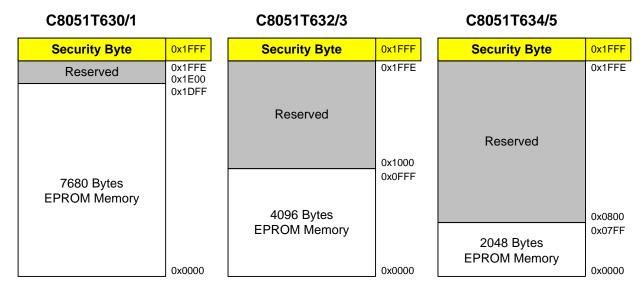

### 13.1. Program Memory

The CIP-51 core has a 64 kB program memory space. The C8051T630/1 implements 8192 bytes of this program memory space as in-system, Byte-Programmable EPROM, organized in a contiguous block from addresses 0x0000 to 0x1FFF. Note that 512 bytes (0x1E00 – 0x1FFF) of this memory are reserved for factory use and are not available for user program storage. The C8051T632/3 implements 4096 bytes of EPROM program memory space; the C8051T634/5 implements 2048 bytes of EPROM program memory space. C2 Register Definition 13.2 shows the program memory maps for C8051T630/1/2/3/4/5 devices.

Figure 13.2. Program Memory Map

Program memory is read-only from within firmware. Individual program memory bytes can be read using the MOVC instruction. This facilitates the use of EPROM space for constant storage.

#### 13.2. Data Memory

The C8051T630/1/2/3/4/5 device family includes 768 bytes of RAM data memory. 256 bytes of this memory is mapped into the internal RAM space of the 8051. 512 bytes of this memory is on-chip "external" memory. The data memory map is shown in Figure 13.1 for reference.

#### 13.2.1. Internal RAM

There are 256 bytes of internal RAM mapped into the data memory space from 0x00 through 0xFF. The lower 128 bytes of data memory are used for general purpose registers and scratch pad memory. Either direct or indirect addressing may be used to access the lower 128 bytes of data memory. Locations 0x00 through 0x1F are addressable as four banks of general purpose registers, each bank consisting of eight byte-wide registers. The next 16 bytes, locations 0x20 through 0x2F, may either be addressed as bytes or as 128 bit locations accessible with the direct addressing mode.

The upper 128 bytes of data memory are accessible only by indirect addressing. This region occupies the same address space as the Special Function Registers (SFR) but is physically separate from the SFR space. The addressing mode used by an instruction when accessing locations above 0x7F determines whether the CPU accesses the upper 128 bytes of data memory space or the SFRs. Instructions that use direct addressing will access the SFR space. Instructions using indirect addressing above 0x7F access the upper 128 bytes of data memory. Figure 13.1 illustrates the data memory organization of the C8051T630/1/2/3/4/5.

### 13.2.1.1. General Purpose Registers

The lower 32 bytes of data memory, locations 0x00 through 0x1F, may be addressed as four banks of general-purpose registers. Each bank consists of eight byte-wide registers designated R0 through R7. Only one of these banks may be enabled at a time. Two bits in the program status word, RS0 (PSW.3) and RS1 (PSW.4), select the active register bank (see description of the PSW in SFR Definition 12.6). This allows fast context switching when entering subroutines and interrupt service routines. Indirect addressing modes use registers R0 and R1 as index registers.

#### 13.2.1.2. Bit Addressable Locations

In addition to direct access to data memory organized as bytes, the sixteen data memory locations at 0x20 through 0x2F are also accessible as 128 individually addressable bits. Each bit has a bit address from 0x00 to 0x7F. Bit 0 of the byte at 0x20 has bit address 0x00 while bit7 of the byte at 0x20 has bit address 0x07. Bit 7 of the byte at 0x2F has bit address 0x7F. A bit access is distinguished from a full byte access by the type of instruction used (bit source or destination).

The MCS-51<sup>™</sup> assembly language allows an alternate notation for bit addressing of the form XX.B where XX is the byte address and B is the bit position within the byte. For example, the instruction:

MOV C, 22.3h

moves the Boolean value at 0x13 (bit 3 of the byte at location 0x22) into the Carry flag.

#### 13.2.1.3. Stack

A programmer's stack can be located anywhere in the 256-byte data memory. The stack area is designated using the Stack Pointer (SP) SFR. The SP will point to the last location used. The next value pushed on the stack is placed at SP+1 and then SP is incremented. A reset initializes the stack pointer to location 0x07. Therefore, the first value pushed on the stack is placed at location 0x08, which is also the first register (R0) of register bank 1. Thus, if more than one register bank is to be used, the SP should be initialized to a location in the data memory not being used for data storage. The stack depth can extend up to 256 bytes.

#### 13.2.2. External RAM

There are 512 bytes of on-chip RAM mapped into the external data memory space. All of these address locations may be accessed using the external move instruction (MOVX) and the data pointer (DPTR), or using MOVX indirect addressing mode. If the MOVX instruction is used with an 8-bit address operand (such as @R1), then the high byte of the 16-bit address is provided by the External Memory Interface Control Register (EMI0CN as shown in SFR Definition 13.1).

For a 16-bit MOVX operation (@DPTR), the upper 7 bits of the 16-bit external data memory address word are "don't cares". As a result, the 512-byte RAM is mapped modulo style over the entire 64 k external data memory address range. For example, the XRAM byte at address 0x0000 is shadowed at addresses 0x0200, 0x0400, 0x0600, 0x0800, etc. This is a useful feature when performing a linear memory fill, as the address pointer doesn't have to be reset when reaching the RAM block boundary.

# SFR Definition 15.3. EIE1: Extended Interrupt Enable 1

| Bit   | 7   | 6        | 5    | 4     | 3     | 2      | 1    | 0     |

|-------|-----|----------|------|-------|-------|--------|------|-------|

| Name  | ET3 | Reserved | ECP0 | EPCA0 | EADC0 | EWADC0 | EMAT | ESMB0 |

| Туре  | R/W | R/W      | R/W  | R/W   | R/W   | R/W    | R/W  | R/W   |

| Reset | 0   | 0        | 0    | 0     | 0     | 0      | 0    | 0     |

#### SFR Address = 0xE6

| Bit | Name     | Function                                                                                                                                                                                                                              |  |  |  |  |  |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7   | ET3      | Enable Timer 3 Interrupt.  This bit sets the masking of the Timer 3 interrupt.  0: Disable Timer 3 interrupts.  1: Enable interrupt requests generated by the TF3L or TF3H flags.                                                     |  |  |  |  |  |

| 6   | Reserved | Reserved. Must Write 0.                                                                                                                                                                                                               |  |  |  |  |  |

| 5   | ECP0     | Enable Comparator0 (CP0) Interrupt.  This bit sets the masking of the CP0 interrupt.  0: Disable CP0 interrupts.  1: Enable interrupt requests generated by the CP0RIF or CP0FIF flags.                                               |  |  |  |  |  |

| 4   | EPCA0    | Enable Programmable Counter Array (PCA0) Interrupt.  This bit sets the masking of the PCA0 interrupts.  0: Disable all PCA0 interrupts.  1: Enable interrupt requests generated by PCA0.                                              |  |  |  |  |  |

| 3   | EADC0    | Enable ADC0 Conversion Complete Interrupt.  This bit sets the masking of the ADC0 Conversion Complete interrupt.  0: Disable ADC0 Conversion Complete interrupt.  1: Enable interrupt requests generated by the AD0INT flag.          |  |  |  |  |  |

| 2   | EWADC0   | Enable Window Comparison ADC0 Interrupt.  This bit sets the masking of ADC0 Window Comparison interrupt.  0: Disable ADC0 Window Comparison interrupt.  1: Enable interrupt requests generated by ADC0 Window Compare flag (AD0WINT). |  |  |  |  |  |

| 1   | EMAT     | Enable Port Match Interrupts.  This bit sets the masking of the Port Match Event interrupt.  0: Disable all Port Match interrupts.  1: Enable interrupt requests generated by a Port Match.                                           |  |  |  |  |  |

| 0   | ESMB0    | Enable SMBus (SMB0) Interrupt.  This bit sets the masking of the SMB0 interrupt.  0: Disable all SMB0 interrupts.  1: Enable interrupt requests generated by SMB0.                                                                    |  |  |  |  |  |

#### 16.3. Program Memory CRC

A CRC engine is included on-chip which provides a means of verifying EPROM contents once the device has been programmed. The CRC engine is available for EPROM verification even if the device is fully read and write locked, allowing for verification of code contents at any time.

The CRC engine is operated through the C2 debug and programming interface, and performs 16-bit CRCs on individual 256-Byte blocks of program memory, or a 32-bit CRC on the entire memory space. To prevent hacking and extrapolation of security-locked source code, the CRC engine will only allow CRCs to be performed on contiguous 256-Byte blocks beginning on 256-Byte boundaries (lowest 8-bits of address are 0x00). For example, the CRC engine can perform a CRC for locations 0x0400 through 0x04FF, but it cannot perform a CRC for locations 0x0401 through 0x0500, or on block sizes smaller or larger than 256 bytes.

#### 16.3.1. Performing 32-bit CRCs on Full EPROM Content

A 32-bit CRC on the entire EPROM space is initiated by writing to the CRC1 byte over the C2 interface. The CRC calculation begins at address 0x0000 and ends at the end of user EPROM space. The EPBusy bit in register C2ADD will be set during the CRC operation, and cleared once the operation is complete. The 32-bit results will be available in the CRC3-0 registers. CRC3 is the MSB, and CRC0 is the LSB. The polynomial used for the 32-bit CRC calculation is 0x04C11DB7.

**Note:** If a 16-bit CRC has been performed since the last device reset, a device reset should be initiated before performing a 32-bit CRC operation.

#### 16.3.2. Performing 16-bit CRCs on 256-Byte EPROM Blocks

A 16-bit CRC of individual 256-byte blocks of EPROM can be initiated by writing to the CRC0 byte over the C2 interface. The value written to CRC0 is the high byte of the beginning address for the CRC. For example, if CRC0 is written to 0x02, the CRC will be performed on the 256-bytes beginning at address 0x0200, and ending at address 0x2FF. The EPBusy bit in register C2ADD will be set during the CRC operation, and cleared once the operation is complete. The 16-bit results will be available in the CRC1-0 registers. CRC1 is the MSB, and CRC0 is the LSB. The polynomial for the 16-bit CRC calculation is 0x1021

## SFR Definition 19.1. CLKSEL: Clock Select

| Bit   | 7 | 6 | 5 | 4 | 3 | 2 | 1          | 0 |

|-------|---|---|---|---|---|---|------------|---|

| Name  |   |   |   |   |   |   | CLKSL[1:0] |   |

| Туре  | R | R | R | R | R | R | R/W        |   |

| Reset | 0 | 0 | 0 | 0 | 0 | 0 | 0          | 0 |

### SFR Address = 0xA9

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                                                              |

|-----|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:2 | Unused     | Unused. Read = 000000b; Write = Don't Care                                                                                                                                                                                                                                                                                                            |

| 1:0 | CLKSL[1:0] | System Clock Source Select Bits.                                                                                                                                                                                                                                                                                                                      |

|     |            | <ul> <li>00: SYSCLK derived from the Internal High-Frequency Oscillator and scaled per the IFCN bits in register OSCICN.</li> <li>01: SYSCLK derived from the External Oscillator circuit.</li> <li>10: SYSCLK derived from the Internal Low-Frequency Oscillator and scaled per the OSCLD bits in register OSCLCN.</li> <li>11: reserved.</li> </ul> |

## **SFR Definition 19.3. OSCICN: Internal H-F Oscillator Control**

| Bit   | 7      | 6     | 5       | 4      | 3 | 2 | 1         | 0 |

|-------|--------|-------|---------|--------|---|---|-----------|---|

| Name  | IOSCEN | IFRDY | SUSPEND | STSYNC |   |   | IFCN[1:0] |   |

| Туре  | R/W    | R     | R/W     | R      | R | R | R/W       |   |

| Reset | 1      | 1     | 0       | 0      | 0 | 0 | 0         | 0 |

#### SFR Address = 0xB2

| Bit | Name      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | IOSCEN    | Internal H-F Oscillator Enable Bit.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |           | 0: Internal H-F Oscillator Disabled. 1: Internal H-F Oscillator Enabled.                                                                                                                                                                                                                                                                                                                                                                                               |

| 6   | IFRDY     | Internal H-F Oscillator Frequency Ready Flag.                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |           | O: Internal H-F Oscillator is not running at programmed frequency.     I: Internal H-F Oscillator is running at programmed frequency.                                                                                                                                                                                                                                                                                                                                  |

| 5   | SUSPEND   | Internal Oscillator Suspend Enable Bit.                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |           | Setting this bit to logic 1 places the internal oscillator in SUSPEND mode. The internal oscillator resumes operation when one of the SUSPEND mode awakening events occurs.                                                                                                                                                                                                                                                                                            |

| 4   | STSYNC    | Suspend Timer Synchronization Bit.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |           | This bit is used to indicate when it is safe to read and write the registers associated with the suspend wake-up timer. If a suspend wake-up source other than the timer has brought the oscillator out of suspend mode, it may take up to three timer clocks before the timer can be read or written. When STSYNC reads '1', reads and writes of the timer register should not be performed. When STSYNC reads '0', it is safe to read and write the timer registers. |

| 3:2 | Unused    | Unused. Read = 00b; Write = Don't Care                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1:0 | IFCN[1:0] | Internal H-F Oscillator Frequency Divider Control Bits.                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |           | 00: SYSCLK derived from Internal H-F Oscillator divided by 8.                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |           | 01: SYSCLK derived from Internal H-F Oscillator divided by 4.                                                                                                                                                                                                                                                                                                                                                                                                          |

|     |           | 10: SYSCLK derived from Internal H-F Oscillator divided by 2.  11: SYSCLK derived from Internal H-F Oscillator divided by 1.                                                                                                                                                                                                                                                                                                                                           |

#### 20.2.3. Assigning Port I/O Pins to External Digital Event Capture Functions

External digital event capture functions can be used to trigger an interrupt or wake the device from a low power mode when a transition occurs on a digital I/O pin. The digital event capture functions do not require dedicated pins and will function on both GPIO pins (PnSKIP = 1) and pins in use by the Crossbar (PnSKIP = 0). External digital event capture functions cannot be used on pins configured for analog I/O. Table 20.3 shows all available external digital event capture functions.

Table 20.3. Port I/O Assignment for External Digital Event Capture Functions

| Digital Function     | Potentially Assignable Port Pins | SFR(s) used for<br>Assignment  |

|----------------------|----------------------------------|--------------------------------|

| External Interrupt 0 | P0.0–P0.7                        | IT01CF                         |

| External Interrupt 1 | P0.0–P0.7                        | IT01CF                         |

| Port Match           | P0.0–P1.7                        | P0MASK, P0MAT<br>P1MASK, P1MAT |

## SFR Definition 21.2. SMB0CN: SMBus Control

| Bit   | 7      | 6      | 5   | 4   | 3     | 2       | 1   | 0   |

|-------|--------|--------|-----|-----|-------|---------|-----|-----|

| Name  | MASTER | TXMODE | STA | STO | ACKRQ | ARBLOST | ACK | SI  |

| Туре  | R      | R      | R/W | R/W | R     | R       | R/W | R/W |

| Reset | 0      | 0      | 0   | 0   | 0     | 0       | 0   | 0   |

SFR Address = 0xC0; Bit-Addressable

| Bit | Name    | Description                                                                                                                                                                             | Read                                                                                                          | Write                                                                                                                                                           |  |  |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7   | MASTER  | SMBus Master/Slave<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a master.                                                                            | SMBus operating in slave mode.     SMBus operating in master mode.                                            | N/A                                                                                                                                                             |  |  |

| 6   | TXMODE  | SMBus Transmit Mode<br>Indicator. This read-only bit<br>indicates when the SMBus is<br>operating as a transmitter.                                                                      | 0: SMBus in Receiver<br>Mode.<br>1: SMBus in Transmitter<br>Mode.                                             | N/A                                                                                                                                                             |  |  |

| 5   | STA     | SMBus Start Flag.                                                                                                                                                                       | O: No Start or repeated Start detected.  1: Start or repeated Start detected.                                 | O: No Start generated.  1: When Configured as a Master, initiates a START or repeated START.                                                                    |  |  |

| 4   | STO     | SMBus Stop Flag.                                                                                                                                                                        | O: No Stop condition detected.  1: Stop condition detected (if in Slave Mode) or pending (if in Master Mode). | O: No STOP condition is transmitted.  1: When configured as a Master, causes a STOP condition to be transmitted after the next ACK cycle.  Cleared by Hardware. |  |  |

| 3   | ACKRQ   | SMBus Acknowledge<br>Request.                                                                                                                                                           | 0: No Ack requested<br>1: ACK requested                                                                       | N/A                                                                                                                                                             |  |  |

| 2   | ARBLOST | SMBus Arbitration Lost Indicator.                                                                                                                                                       | 0: No arbitration error. 1: Arbitration Lost                                                                  | N/A                                                                                                                                                             |  |  |

| 1   | ACK     | SMBus Acknowledge.                                                                                                                                                                      | 0: NACK received.<br>1: ACK received.                                                                         | 0: Send NACK<br>1: Send ACK                                                                                                                                     |  |  |

| 0   | SI      | SMBus Interrupt Flag. This bit is set by hardware under the conditions listed in Table 15.3. SI must be cleared by software. While SI is set, SCL is held low and the SMBus is stalled. | No interrupt pending     Interrupt Pending                                                                    | O: Clear interrupt, and initiate next state machine event.  1: Force interrupt.                                                                                 |  |  |

Table 21.6. SMBus Status Decoding With Hardware ACK Generation Enabled (EHACK = 1) (Continued)

|                   | Val    | ıes   | Rea      | ad  |                                                                                       |                                                        |     | lues<br>Vrit |     | tus                            |

|-------------------|--------|-------|----------|-----|---------------------------------------------------------------------------------------|--------------------------------------------------------|-----|--------------|-----|--------------------------------|

| Mode              | Status | ACKRQ | ARBLOST  | ACK | Current SMbus State                                                                   | Typical Response Options                               | STA | STO          | ACK | Next Status<br>Vector Expected |

| <u></u>           |        | 0     | 0        | 0   | A slave byte was transmitted; NACK received.                                          | No action required (expecting STOP condition).         | 0   | 0            | X   | 0001                           |

| smitte            | 0100   | 0     | 0        | 1   | A slave byte was transmitted; ACK received.                                           | Load SMB0DAT with next data byte to transmit.          | 0   | 0            | Х   | 0100                           |

| Slave Transmitter |        | 0     | 1        | Х   | A Slave byte was transmitted; error detected.                                         | No action required (expecting Master to end transfer). | 0   | 0            | X   | 0001                           |

| Slav              | 0101   | 0     | Х        | Х   | An illegal STOP or bus error was detected while a Slave Transmission was in progress. | Clear STO.                                             | 0   | 0            | X   | _                              |

|                   |        | 0     | 0        | Х   | A slave address + R/W was                                                             | If Write, Set ACK for first data byte.                 | 0   | 0            | 1   | 0000                           |

|                   |        |       |          |     | received; ACK sent.                                                                   | If Read, Load SMB0DAT with data byte                   | 0   | 0            | X   | 0100                           |

|                   | 0010   |       |          |     | Lost arbitration as master;                                                           | If Write, Set ACK for first data byte.                 | 0   | 0            | 1   | 0000                           |

| iver              |        | 0     | 1        | X   | slave address + R/W received;<br>ACK sent.                                            | data byte                                              | 0   | 0            | X   | 0100                           |

| ece               |        |       |          |     |                                                                                       | Reschedule failed transfer                             | 1   | 0            | Χ   | 1110                           |

| Slave Receiver    | 0001   | 0     | 0        | Х   | A STOP was detected while addressed as a Slave Transmitter or Slave Receiver.         | Clear STO.                                             | 0   | 0            | X   |                                |

|                   |        | 0     | 1        | Х   | Lost arbitration while attempting a STOP.                                             | No action required (transfer complete/aborted).        | 0   | 0            | 0   |                                |

|                   | 0000   | 0     | 0        | Y   | A slave byte was received.                                                            | Set ACK for next data byte;<br>Read SMB0DAT.           | 0   | 0            | 1   | 0000                           |

|                   | 0000   | U     | U        | ^   | A slave byte was received.                                                            | Set NACK for next data byte;<br>Read SMB0DAT.          | 0   | 0            | 0   | 0000                           |

| ion               | 0010   | 0     | 1        | Х   | Lost arbitration while attempt-                                                       | Abort failed transfer.                                 | 0   | 0            | Χ   |                                |

| dit               |        |       | Ľ        |     | ing a repeated START.                                                                 | Reschedule failed transfer.                            | 1   | 0            | Χ   | 1110                           |

| So                | 0001   | 0     | 1        | Х   | Lost arbitration due to a                                                             | Abort failed transfer.                                 | 0   | 0            | Χ   | _                              |

| Error Condition   | 2301   |       | Ľ        |     | detected STOP.                                                                        | Reschedule failed transfer.                            | 1   | 0            | Χ   | 1110                           |

| ,<br>E            | 0000   | 0     | 1        | X   | Lost arbitration while transmit-                                                      | Abort failed transfer.                                 | 0   | 0            | Χ   | _                              |

| Bus               | 5500   |       | <u>'</u> |     | ting a data byte as master.                                                           | Reschedule failed transfer.                            | 1   | 0            | Х   | 1110                           |

## SFR Definition 22.2. SBUF0: Serial (UART0) Port Data Buffer

| Bit   | 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|------------|---|---|---|---|---|---|---|--|

| Name  | SBUF0[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W        |   |   |   |   |   |   |   |  |

| Reset | 0          | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

### SFR Address = 0x99

| Bit | Name       | Function                                                                                                                                                                                                                                                                                                           |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | SBUF0[7:0] | Serial Data Buffer Bits 7–0 (MSB–LSB).                                                                                                                                                                                                                                                                             |

|     |            | This SFR accesses two registers; a transmit shift register and a receive latch register. When data is written to SBUF0, it goes to the transmit shift register and is held for serial transmission. Writing a byte to SBUF0 initiates the transmission. A read of SBUF0 returns the contents of the receive latch. |

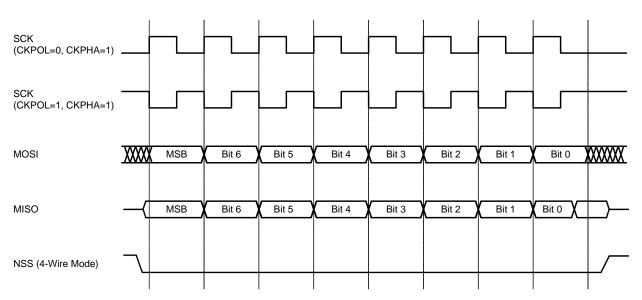

Figure 23.7. Slave Mode Data/Clock Timing (CKPHA = 1)

### 23.6. SPI Special Function Registers

SPI0 is accessed and controlled through four special function registers in the system controller: SPI0CN Control Register, SPI0DAT Data Register, SPI0CFG Configuration Register, and SPI0CKR Clock Rate Register. The four special function registers related to the operation of the SPI0 Bus are described in the following figures.

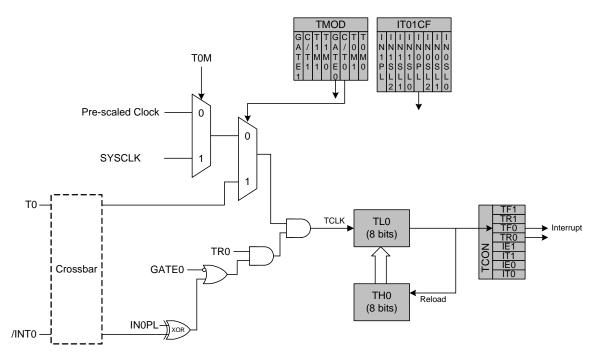

#### 24.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 in the TCON register is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit (TCON.4) enables the timer when either GATE0 in the TMOD register is logic 0 or when the input signal INT0 is active as defined by bit IN0PL in register IT01CF (see Section "15.3. INT0 and INT1 External Interrupts" on page 87 for details on the external input signals INT0 and INT1).

Figure 24.2. T0 Mode 2 Block Diagram

## SFR Definition 24.2. TCON: Timer Control

| Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| Name  | TF1 | TR1 | TF0 | TR0 | IE1 | IT1 | IE0 | IT0 |

| Туре  | R/W |

| Reset | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

SFR Address = 0x88; Bit-Addressable

| Bit | Name | Function                                                                                                                                                                                                                                                      |

|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TF1  | Timer 1 Overflow Flag.                                                                                                                                                                                                                                        |

|     |      | Set to 1 by hardware when Timer 1 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 1 interrupt service routine.                                                                                 |

| 6   | TR1  | Timer 1 Run Control.                                                                                                                                                                                                                                          |

|     |      | Timer 1 is enabled by setting this bit to 1.                                                                                                                                                                                                                  |

| 5   | TF0  | Timer 0 Overflow Flag.                                                                                                                                                                                                                                        |

|     |      | Set to 1 by hardware when Timer 0 overflows. This flag can be cleared by software but is automatically cleared when the CPU vectors to the Timer 0 interrupt service routine.                                                                                 |

| 4   | TR0  | Timer 0 Run Control.                                                                                                                                                                                                                                          |

|     |      | Timer 0 is enabled by setting this bit to 1.                                                                                                                                                                                                                  |

| 3   | IE1  | External Interrupt 1.                                                                                                                                                                                                                                         |

|     |      | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 1 service routine in edge-triggered mode.                       |

| 2   | IT1  | Interrupt 1 Type Select.                                                                                                                                                                                                                                      |

|     |      | This bit selects whether the configured /INT1 interrupt will be edge or level sensitive. /INT1 is configured active low or high by the IN1PL bit in the IT01CF register (see SFR Definition 15.5).  0: /INT1 is level triggered.  1: /INT1 is edge triggered. |

| 1   | IE0  | External Interrupt 0.                                                                                                                                                                                                                                         |

|     |      | This flag is set by hardware when an edge/level of type defined by IT1 is detected. It can be cleared by software but is automatically cleared when the CPU vectors to the External Interrupt 0 service routine in edge-triggered mode.                       |

| 0   | IT0  | Interrupt 0 Type Select.                                                                                                                                                                                                                                      |

|     |      | This bit selects whether the configured INTO interrupt will be edge or level sensitive. INTO is configured active low or high by the INOPL bit in register ITO1CF (see SFR Definition 15.5).  0: INTO is level triggered.  1: INTO is edge triggered.         |

### 25.3. Capture/Compare Modules

Each module can be configured to operate independently in one of six operation modes: edge-triggered capture, software timer, high-speed output, frequency output, 8 to 11-bit pulse width modulator, or 16-bit pulse width modulator. Each module has Special Function Registers (SFRs) associated with it in the CIP-51 system controller. These registers are used to exchange data with a module and configure the module's mode of operation. Table 25.2 summarizes the bit settings in the PCA0CPMn and PCA0PWM registers used to select the PCA capture/compare module's operating mode. Note that all modules set to use 8, 9, 10, or 11-bit PWM mode must use the same cycle length (8–11 bits). Setting the ECCFn bit in a PCA0CPMn register enables the module's CCFn interrupt.

Table 25.2. PCA0CPM and PCA0PWM Bit Settings for PCA Capture/Compare Modules

| Operational Mode                            |   |   | PCA0CPMn |   |   |   |   |   |   | PCA0PWM |   |     |     |

|---------------------------------------------|---|---|----------|---|---|---|---|---|---|---------|---|-----|-----|

| Bit Number                                  | 7 | 6 | 5        | 4 | 3 | 2 | 1 | 0 | 7 | 6       | 5 | 4–2 | 1–0 |

| Capture triggered by positive edge on CEXn  | Χ | Χ | 1        | 0 | 0 | 0 | 0 | Α | 0 | Χ       | В | XXX | XX  |

| Capture triggered by negative edge on CEXn  | Χ | Х | 0        | 1 | 0 | 0 | 0 | Α | 0 | Χ       | В | XXX | XX  |

| Capture triggered by any transition on CEXn | Χ | Χ | 1        | 1 | 0 | 0 | 0 | Α | 0 | Χ       | В | XXX | XX  |

| Software Timer                              | Χ | С | 0        | 0 | 1 | 0 | 0 | Α | 0 | Χ       | В | XXX | XX  |

| High Speed Output                           | Χ | С | 0        | 0 | 1 | 1 | 0 | Α | 0 | Χ       | В | XXX | XX  |

| Frequency Output                            | Χ | С | 0        | 0 | 0 | 1 | 1 | Α | 0 | Χ       | В | XXX | XX  |

| 8-Bit Pulse Width Modulator (Note 7)        | 0 | С | 0        | 0 | Е | 0 | 1 | Α | 0 | Χ       | В | XXX | 00  |

| 9-Bit Pulse Width Modulator (Note 7)        | 0 | С | 0        | 0 | Е | 0 | 1 | Α | D | Χ       | В | XXX | 01  |

| 10-Bit Pulse Width Modulator (Note 7)       | 0 | С | 0        | 0 | Е | 0 | 1 | Α | D | Χ       | В | XXX | 10  |

| 11-Bit Pulse Width Modulator (Note 7)       | 0 | С | 0        | 0 | Е | 0 | 1 | Α | D | Χ       | В | XXX | 11  |

| 16-Bit Pulse Width Modulator                | 1 | С | 0        | 0 | Е | 0 | 1 | Α | 0 | Χ       | В | XXX | XX  |

#### Notes:

- **1.** X = Don't Care (no functional difference for individual module if 1 or 0).

- **2.** A = Enable interrupts for this module (PCA interrupt triggered on CCFn set to 1).

- **3.** B = Enable 8th, 9th, 10th or 11th bit overflow interrupt (Depends on setting of CLSEL[1:0]).

- **4.** C = When set to 0, the digital comparator is off. For high speed and frequency output modes, the associated pin will not toggle. In any of the PWM modes, this generates a 0% duty cycle (output = 0).

- **5.** D = Selects whether the Capture/Compare register (0) or the Auto-Reload register (1) for the associated channel is accessed via addresses PCA0CPHn and PCA0CPLn.

- 6. E = When set, a match event will cause the CCFn flag for the associated channel to be set.

- 7. All modules set to 8, 9, 10 or 11-bit PWM mode use the same cycle length setting.

CHICAN LARG

# C2 Register Definition 26.8. EPADDRH: C2 EPROM Address High Byte

| Bit   | 7            | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|--------------|---|---|---|---|---|---|---|--|

| Name  | EPADDR[15:8] |   |   |   |   |   |   |   |  |

| Туре  | R/W          |   |   |   |   |   |   |   |  |

| Reset | 0            | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

C2 Address: 0xAF

| Bit | Name         | Function                                                                            |

|-----|--------------|-------------------------------------------------------------------------------------|

| 7:0 | EPADDR[15:8] | C2 EPROM Address High Byte.                                                         |

|     |              | This register is used to set the EPROM address location during C2 EPROM operations. |

# C2 Register Definition 26.9. EPADDRL: C2 EPROM Address Low Byte

| Bit   | 7           | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-------------|---|---|---|---|---|---|---|--|

| Name  | EPADDR[7:0] |   |   |   |   |   |   |   |  |

| Туре  | R/W         |   |   |   |   |   |   |   |  |

| Reset | 0           | 0 | 0 | 0 | 0 | 0 | 0 | 0 |  |

C2 Address: 0xAE

| Bit | Name         | Function                                                                            |

|-----|--------------|-------------------------------------------------------------------------------------|

| 7:0 | EPADDR[15:8] | C2 EPROM Address Low Byte.                                                          |

|     |              | This register is used to set the EPROM address location during C2 EPROM operations. |