Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | M8C                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 24MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                       |

| Peripherals                | LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 28                                                                          |

| Program Memory Size        | 8KB (8K x 8)                                                                |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                |

| Data Converters            | A/D 1x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 32-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 32-QFN (5x5)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c24193-24lqxi |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **More Information**

Cypress provides a wealth of data at www.cypress.com to help you to select the right PSoC device for your design, and quickly and effectively integrate the device into your design. For a comprehensive list of resources, see the knowledge base article "How to Design with  $PSoC^{\mbox{\sc B}}$  1,  $PowerPSoC^{\mbox{\sc B}}$ , and PLC - KBA88292".

- Overview: PSoC Portfolio, PSoC Roadmap

- Product Selectors: PSoC 1, PSoC 3, PSoC 4, or PSoC 5LP. In addition, PSoC Designer includes a device selection tool.

- Application Notes and Code Examples: Cover a broad range of topics, from basic to advanced level. Many of the application notes include code examples.

- Technical Reference Manuals (TRM): The TRM provides complete detailed descriptions of the internal architecture of the PSoC 1 devices.

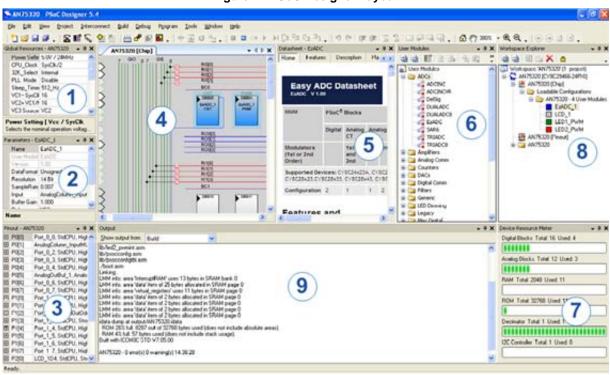

#### **PSoC Designer**

PSoC Designer is a free Windows-based Integrated Design Environment (IDE). Develop your applications using a library of pre-characterized analog and digital peripherals in a drag-and-drop design environment. Then, customize your design leveraging the dynamically generated API libraries of code. Figure 1 shows PSoC Designer windows. **Note:** This is not the default view.

- 1. Global Resources all device hardware settings.

- 2. **Parameters** the parameters of the currently selected User Modules.

- 3. Pinout information related to device pins.

- 4. Chip-Level Editor a diagram of the resources available on the selected chip.

#### Development Kits:

- CY3215A-DK In-Circuit Emulation Lite Development Kit includes an in-circuit emulator (ICE). While the ICE-Cube is primarily used to debug PSoC 1 devices, it can also program PSoC 1 devices using ISSP.

- CY3210-PSOCEVAL1 Kit enables you to evaluate and experiment Cypress's PSoC 1 programmable system-on-chip design methodology and architecture.

The MiniProg1 and MiniProg3 device provides an interface for flash programming.

- 5. Datasheet the datasheet for the currently selected UM

- 6. User Modules all available User Modules for the selected device.

- 7. **Device Resource Meter** device resource usage for the current project configuration.

- 8. **Workspace** a tree level diagram of files associated with the project.

- 9. Output output from project build and debug operations.

**Note:** For detailed information on PSoC Designer, go to **PSoC**<sup>®</sup> **Designer** > **Help** > **Documentation** > **Designer Specific Documents** > **IDE User Guide**.

#### Figure 1. PSoC Designer Layout

## 48-pin QFN (OCD) (36 GPIOs) [23]

The 48-pin QFN part is for the CY8C240093 On-Chip Debug (OCD). Note that this part is only used for in-circuit debugging.

| Pin<br>No.         | Digital | Analog | Name            | Description                                                                  |                    |           | Figu                           |                                  | /8C240093                                                                                                                                                                   |

|--------------------|---------|--------|-----------------|------------------------------------------------------------------------------|--------------------|-----------|--------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 <sup>[26]</sup>  |         |        | OCDOE           | OCD mode direction pin                                                       |                    |           | ·                              | Po[5], A<br>Po[3], A<br>Po[5], A | P0[7], AI<br>OCDE<br>OCDO<br>Vdd<br>P0[6], AI<br>P0[2], AI<br>P0[0], AI<br>P0[0], AI                                                                                        |

| 2                  | I/O     | I      | P2[7]           |                                                                              |                    |           |                                | n slod                           | P0 00 00 00 00 00 00 00 00 00 00 00 00 0                                                                                                                                    |

| 3                  | I/O     | Ι      | P2[5]           | Crystal output (XOut)                                                        |                    |           |                                | 46                               | 4 4 4 4 4 6 8 8 6 36 P2[6],AI                                                                                                                                               |

| 4                  | I/O     | I      | P2[3]           | Crystal input (XIn)                                                          |                    |           | A E 2                          |                                  | 35 <b>=</b> P2[4],AI                                                                                                                                                        |

| 5                  | I/O     | I      | P2[1]           |                                                                              |                    | AI, X     | (Out, P2[5] = 3                |                                  | 34 <b>□</b> P2[2],AI                                                                                                                                                        |

| 6                  | I/O     | I      | P4[3]           |                                                                              |                    |           | XIn , P2[3] = 4                |                                  | 33 <b>=</b> P2[0],AI                                                                                                                                                        |

| 7                  | I/O     | I      | P4[1]           |                                                                              |                    |           | AI, P2[1] = 5                  |                                  | 32 <b>=</b> P4[2],Al<br>QFN 31 <b>=</b> P4[0],Al                                                                                                                            |

| 8                  | I/O     | I      | P3[7]           |                                                                              |                    |           | AI, P4[3] = 6<br>AI, P4[1] = 7 |                                  | QFN 31= P4[0],AI<br>(Top View) 30= P3[6],AI                                                                                                                                 |

| 9                  | I/O     | I      | P3[5]           |                                                                              |                    |           | AI, P3[7] = 8                  |                                  | 29 <b>=</b> P3[4], Al                                                                                                                                                       |

| 10                 | I/O     | I      | P3[3]           |                                                                              |                    |           | AI, P3[5] 🗖 9                  |                                  | 28 <b>=</b> P3[2],AI                                                                                                                                                        |

| 11                 | I/O     | I      | P3[1]           |                                                                              |                    |           | AI, P3[3] = 10                 | 1                                | 27 <b>=</b> P3[0], Al                                                                                                                                                       |

| 12                 | IOHR    | I      | P1[7]           | I <sup>2</sup> C SCL, SPI SS                                                 |                    |           | AI, P3[1] = 11                 | m <del>st</del> i0 v0            | 26 <b>■</b> XRES<br>► ∞ • 0 = 3 = 3 = 3 = 25 <b>■</b> P1[6], Al                                                                                                             |

| 13                 | IOHR    | Ι      | P1[5]           | I <sup>2</sup> C SDA, SPI MISO                                               |                    | 20002, 01 |                                |                                  |                                                                                                                                                                             |

| 14 <sup>[26]</sup> |         |        | CCLK            | OCD CPU clock output                                                         | -                  |           | -                              | []<br>[]<br>[]                   | T[1]<br>D + D<br>D - D<br>1[0]<br>1[2]<br>1[2]                                                                                                                              |

| 15 <sup>[26]</sup> |         |        | HCLK            | OCD high speed clock output                                                  | -                  |           | ć                              | H BO SH I                        | OSI, P1[1]<br>VSS<br>D + 1<br>D - 1<br>D - 1<br>Vdd<br>AI, P1[2]<br>JLK, P1[4]<br>JLK, P1[4]                                                                                |

| 16                 | IOHR    | 1      | P1[3]           | SPI CLK.                                                                     | -                  |           | Ç                              | K, A                             | PI(1)<br>Vss<br>D +<br>D -<br>D -<br>D -<br>D -<br>AL, P1(0)<br>AL, P1(2)<br>EXTGLK, P1(4)                                                                                  |

| 17                 | IOHR    | 1      | P1[1]           | ISSP CLK <sup>[27],</sup> I <sup>2</sup> C SCL, SPI                          | -                  |           |                                |                                  | SPI<br>, SPI                                                                                                                                                                |

|                    |         | -      | [.]             | MOSI                                                                         |                    |           |                                | HCLK BY CLK, AI, PT[3]           | AI,ISSP CLK <sup>6</sup> , I2C SCL, SPI MOSI, P1[1]<br>Vsv<br>D +<br>AI,ISSP DATA', I2C SDA, SPI CLK, P1[0]<br>AI, ISSP DATA', I2C SDA, SPI CLK, P1[1]<br>AI, EXTCLK, P1[2] |

| 18                 | Po      | wer    | V <sub>SS</sub> | Ground connection                                                            |                    |           |                                |                                  | , 120                                                                                                                                                                       |

| 19                 | I/O     |        | D+              | USB D+                                                                       |                    |           | ŝ                              | 2                                | ATA                                                                                                                                                                         |

| 20                 | I/O     |        | D-              | USB D-                                                                       |                    |           |                                |                                  | SP C                                                                                                                                                                        |

| 21                 | Po      | wer    | V <sub>DD</sub> | Supply voltage                                                               |                    |           |                                |                                  | AI,IS                                                                                                                                                                       |

| 22                 | IOHR    | I      | P1[0]           | ISSP DATA <sup>[27]</sup> , I <sup>2</sup> C SDA, SPI<br>CLK <sup>[28]</sup> |                    |           |                                | [27]                             | [27, 28]<br>,                                                                                                                                                               |

| 23                 | IOHR    | Ι      | P1[2]           |                                                                              | Pin<br>No.         | Digital   | Analog                         | Name                             | Description                                                                                                                                                                 |

| 24                 | IOHR    | Ι      | P1[4]           | Optional external clock input<br>(EXTCLK)                                    | 37                 | IOH       | I                              | P0[0]                            |                                                                                                                                                                             |

| 25                 | IOHR    | I      | P1[6]           |                                                                              | 38                 | IOH       | I                              | P0[2]                            |                                                                                                                                                                             |

| 26                 | In      | put    | XRES            | Active high external reset with internal pull-down                           | 39                 | IOH       | I                              | P0[4]                            |                                                                                                                                                                             |

| 27                 | I/O     | I      | P3[0]           |                                                                              | 40                 | IOH       | I                              | P0[6]                            |                                                                                                                                                                             |

| 28                 | I/O     | Ι      | P3[2]           |                                                                              | 41                 | P         | ower                           | V <sub>DD</sub>                  | Supply voltage                                                                                                                                                              |

| 29                 | I/O     | I      | P3[4]           |                                                                              | 42 <sup>[26]</sup> |           |                                | OCDO                             | OCD even data I/O                                                                                                                                                           |

| 30                 | I/O     | Ι      | P3[6]           |                                                                              | 43 <sup>[26]</sup> |           |                                | OCDE                             | OCD odd data output                                                                                                                                                         |

| 31                 | I/O     | Ι      | P4[0]           |                                                                              | 44                 | IOH       |                                | P0[7]                            |                                                                                                                                                                             |

| 32                 | I/O     | Ι      | P4[2]           |                                                                              | 45                 | IOH       | I                              | P0[5]                            |                                                                                                                                                                             |

| 33                 | I/O     | I      | P2[0]           |                                                                              | 46                 | IOH       | I                              | P0[3]                            |                                                                                                                                                                             |

| 34                 | I/O     | I      | P2[2]           |                                                                              | 47                 | P         | ower                           | V <sub>SS</sub>                  | Ground connection                                                                                                                                                           |

| 35                 | I/O     | I      | P2[4]           |                                                                              | 48                 | IOH       | I                              | P0[1]                            |                                                                                                                                                                             |

| 36                 | I/O     | Ι      | P2[6]           | NC = No Connection H = 5 mA High                                             | СР                 |           | ower                           | V <sub>SS</sub>                  | Center pad must be connected to ground                                                                                                                                      |

Table 7. Pin Definitions – CY8C240093 <sup>[24, 25]</sup>

**LEGEND** A = Analog, I = Input, O = Output, NC = No Connection H = 5 mA High Output Drive, R = Regulated Output.

#### Notes

23.36 GPIOs.

24. This part is available in limited quantities for In-Circuit Debugging during prototype development. It is not available in production volumes.

25. The center pad (CP) on the QFN package must be connected to ground (V<sub>SS</sub>) for best mechanical, thermal, and electrical performance. If not connected to ground, it must be electrically floated and not connected to any other signal.

26. This pin (associated with OCD part only) is required for connecting the device to ICE-Cube In-Circuit Emulator for firmware debugging purpose. To know more about the usage of ICE-Cube, refer to CY3215-DK PSoC<sup>®</sup> IN-CIRCUIT EMULATOR KIT GUIDE.

27. On Power-up, the SDA(P10)] drives a strong high for 256 sleep clock cycles and drives resistive low for the next 256 sleep clock cycles. The SCL(P1[1]) line drives resistive low for 512 sleep clock cycles and both the pins transition to High impedance state. On reset, after XRES de- asserts, the SDA and the SCL lines drive resistive low for 8 sleep clock cycles and transition to high impedance state. In both cases, a pull-up resistance on these lines combines with the pull-down resistance (5.6K ohm) and form a potential divider. Hence, during power-up or reset event, P1[1] and P1[0] may disturb the I2C bus. Use alternate pins if you encounter issues.

28. Alternate SPI clock.

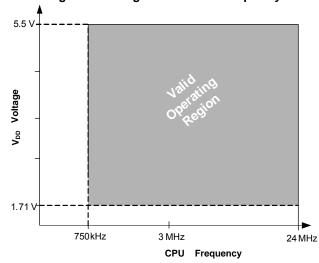

## **Electrical Specifications (CY8C24193/493)**

This section presents the DC and AC electrical specifications of the CY8C24193/493 PSoC devices. For the latest electrical specifications, confirm that you have the most recent datasheet by visiting the web at http://www.cypress.com/psoc.

#### Figure 8. Voltage versus CPU Frequency

## Absolute Maximum Ratings (CY8C24193/493)

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested.

#### Table 8. Absolute Maximum Ratings

| Symbol           | Description                                | Conditions                                                                                                                                                                          | Min                | Тур | Max                   | Units |

|------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-----------------------|-------|

| T <sub>STG</sub> | Storage temperature                        | Higher storage temperatures reduce data retention time. Recommended Storage Temperature is +25 °C ± 25 °C. Extended duration storage temperatures above 85 °C degrades reliability. |                    | +25 | +125                  | °C    |

| V <sub>DD</sub>  | Supply voltage relative to V <sub>SS</sub> | _                                                                                                                                                                                   | -0.5               | -   | +6.0                  | V     |

| V <sub>IO</sub>  | DC input voltage                           | -                                                                                                                                                                                   | $V_{\rm SS} - 0.5$ | -   | V <sub>DD</sub> + 0.5 | V     |

| V <sub>IOZ</sub> | DC voltage applied to tristate             | -                                                                                                                                                                                   | $V_{SS} - 0.5$     | -   | V <sub>DD</sub> + 0.5 | V     |

| I <sub>MIO</sub> | Maximum current into any port pin          | _                                                                                                                                                                                   | -25                | -   | +50                   | mA    |

| ESD              | Electro static discharge voltage           | Human body model ESD                                                                                                                                                                | 2000               | -   | -                     | V     |

| LU               | Latch up current                           | In accordance with JESD78 standard                                                                                                                                                  | -                  | -   | 200                   | mA    |

## **Operating Temperature (CY8C24193/493)**

#### Table 9. Operating Temperature

| Symbol         | Description                  | Conditions                                                                                                                                                                                       | Min | Тур | Max  | Units |

|----------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|-------|

| T <sub>A</sub> | Ambient temperature          | -                                                                                                                                                                                                | -40 | -   | +85  | °C    |

| Т <sub>С</sub> | Commercial temperature range | -                                                                                                                                                                                                | 0   |     | 70   | °C    |

| TJ             | Operational die temperature  | The temperature rise from ambient to junction<br>is package specific. See the Thermal<br>Impedances on page 49. The user must limit<br>the power consumption to comply with this<br>requirement. | -40 | _   | +100 | °C    |

## Table 12. 2.4 V to 3.0 V DC GPIO Specifications

| Symbol                | Description                                                                       | Conditions                                                                                                                                                                          | Min                    | Тур  | Max  | Units |

|-----------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------|-------|

| R <sub>PU</sub>       | Pull-up resistor                                                                  | -                                                                                                                                                                                   | 4                      | 5.60 | 8    | kΩ    |

| V <sub>OH1</sub>      | High output voltage<br>Port 2 or 3 pins                                           | $I_{OH}$ < 10 $\mu$ A, maximum of 10 mA source current in all I/Os                                                                                                                  | V <sub>DD</sub> - 0.20 | _    | _    | V     |

| V <sub>OH2</sub>      | High output voltage<br>Port 2 or 3 Pins                                           | I <sub>OH</sub> = 0.2 mA, maximum of 10 mA<br>source current in all I/Os                                                                                                            | V <sub>DD</sub> - 0.40 | _    | _    | V     |

| V <sub>OH3</sub>      | High output voltage<br>Port 0 or 1 pins with LDO regulator<br>Disabled for port 1 | $I_{OH}$ < 10 $\mu$ A, maximum of 10 mA source current in all I/Os                                                                                                                  | V <sub>DD</sub> - 0.20 | -    | -    | V     |

| V <sub>OH4</sub>      | High output voltage<br>Port 0 or 1 pins with LDO regulator<br>Disabled for Port 1 | I <sub>OH</sub> = 2 mA, maximum of 10 mA source<br>current in all I/Os                                                                                                              | V <sub>DD</sub> - 0.50 | -    | -    | V     |

| V <sub>OH5A</sub>     | High output voltage<br>Port 1 pins with LDO enabled for 1.8 V<br>out              | $I_{OH}$ < 10 $\mu$ A, V <sub>DD</sub> > 2.4 V, maximum of 20 mA source current in all I/Os                                                                                         | 1.50                   | 1.80 | 2.10 | V     |

| V <sub>OH6A</sub>     | High output voltage<br>Port 1 pins with LDO enabled for 1.8 V<br>out              | $I_{OH}$ = 1 mA, $V_{DD}$ > 2.4 V, maximum of<br>20 mA source current in all I/Os                                                                                                   | 1.20                   |      | -    | V     |

| V <sub>OL</sub>       | Low output voltage                                                                | $I_{OL}$ = 10 mA, maximum of 30 mA sink<br>current on even port pins (for example,<br>P0[2] and P1[4]) and 30 mA sink<br>current on odd port pins (for example,<br>P0[3] and P1[5]) | _                      | -    | 0.75 | V     |

| V <sub>IL</sub>       | Input low voltage                                                                 | -                                                                                                                                                                                   | -                      | -    | 0.72 | V     |

| V <sub>IH</sub>       | Input high voltage                                                                | -                                                                                                                                                                                   | 1.40                   | _    |      | V     |

| V <sub>H</sub>        | Input hysteresis voltage                                                          | -                                                                                                                                                                                   | _                      | 80   | -    | mV    |

| IIL                   | Input leakage (absolute value)                                                    | -                                                                                                                                                                                   | -                      | 1    | 1000 | nA    |

| C <sub>PIN</sub>      | Capacitive load on pins                                                           | Package and pin dependent<br>Temp = 25 °C                                                                                                                                           | 0.50                   | 1.70 | 7    | pF    |

| V <sub>ILLVT2.5</sub> | Input Low Voltage with low threshold<br>enable set, Enable for Port1              | Bit3 of IO_CFG1 set to enable low threshold voltage of Port1 input                                                                                                                  | 0.7                    | V    | _    |       |

| V <sub>IHLVT2.5</sub> | Input High Voltage with low threshold<br>enable set, Enable for Port1             | Bit3 of IO_CFG1 set to enable low<br>threshold voltage of Port1 input                                                                                                               | 1.2                    |      | _    | V     |

## ADC Electrical Specifications (CY8C24193/493)

## Table 18. ADC User Module Electrical Specifications

| Symbol                 | Description                  | Conditions                                                                                                   | Min                       | Тур                       | Max                       | Units |

|------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|-------|

| Input                  | •                            |                                                                                                              | •                         |                           |                           |       |

| V <sub>IN</sub>        | Input voltage range          |                                                                                                              | 0                         | -                         | VREFADC                   | V     |

| C <sub>IIN</sub>       | Input capacitance            | -                                                                                                            | -                         | -                         | 5                         | pF    |

| R <sub>IN</sub>        | Input resistance             | Equivalent switched cap input<br>resistance for 8-, 9-, or 10-bit<br>resolution                              | 1/(500fF ×<br>data clock) | 1/(400fF ×<br>data clock) | 1/(300fF ×<br>data clock) | Ω     |

| Reference              | •                            |                                                                                                              | •                         |                           |                           |       |

| V <sub>REFADC</sub>    | ADC reference voltage        | -                                                                                                            | 1.14                      | _                         | 1.26                      | V     |

| <b>Conversion Rate</b> | •<br>•                       |                                                                                                              |                           |                           | •                         |       |

| F <sub>CLK</sub>       | Data clock                   | Source is chip's internal main<br>oscillator. See AC Chip-Level<br>Specifications on page 25 for<br>accuracy | 2.25                      | -                         | 6                         | MHz   |

| S8                     | 8-bit sample rate            | Data clock set to 6 MHz.<br>sample rate = 0.001/<br>(2^Resolution/Data Clock)                                | -                         | 23.43                     | _                         | ksps  |

| S10                    | 10-bit sample rate           | Data clock set to 6 MHz.<br>sample rate = 0.001/<br>(2^resolution/data clock)                                | -                         | 5.85                      | _                         | ksps  |

| DC Accuracy            |                              |                                                                                                              |                           |                           |                           |       |

| RES                    | Resolution                   | Can be set to 8, 9, or 10 bit                                                                                | 8                         | -                         | 10                        | bits  |

| DNL                    | Differential nonlinearity    | -                                                                                                            | -1                        | _                         | +2                        | LSB   |

| INL                    | Integral nonlinearity        | -                                                                                                            | -2                        | -                         | +2                        | LSB   |

| E <sub>OFFSET</sub>    | Offset error                 | 8-bit resolution                                                                                             | 0                         | 3.20                      | 19.20                     | LSB   |

|                        | 10-bit resolution 0          |                                                                                                              | 0                         | 12.80                     | 76.80                     | LSB   |

| E <sub>GAIN</sub>      | Gain error                   | For any resolution                                                                                           | -5                        | -                         | +5                        | %FSR  |

| Power                  |                              |                                                                                                              |                           |                           |                           |       |

| I <sub>ADC</sub>       | Operating current            | -                                                                                                            | -                         | 2.10                      | 2.60                      | mA    |

| PSRR                   | Power supply rejection ratio | PSRR (V <sub>DD</sub> > 3.0 V)                                                                               | -                         | 24                        | -                         | dB    |

|                        |                              | PSRR (V <sub>DD</sub> < 3.0 V)                                                                               | -                         | 30                        | -                         | dB    |

## DC POR and LVD Specifications (CY8C24193/493)

The following table lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

| Symbol            | Description                      | Conditions                                                       | Min                  | Тур  | Max  | Units |

|-------------------|----------------------------------|------------------------------------------------------------------|----------------------|------|------|-------|

| V <sub>POR0</sub> | 1.66 V selected in PSoC Designer |                                                                  | 1.61                 | 1.66 | 1.71 | V     |

| V <sub>POR1</sub> | 2.36 V selected in PSoC Designer | during startup, reset from the XRES pin, or reset from watchdog. | -                    | 2.36 | 2.41 |       |

| V <sub>POR2</sub> | 2.60 V selected in PSoC Designer | reset nom waterladg.                                             | -                    | 2.60 | 2.66 |       |

| V <sub>POR3</sub> | 2.82 V selected in PSoC Designer |                                                                  | -                    | 2.82 | 2.95 |       |

| V <sub>LVD0</sub> | 2.45 V selected in PSoC Designer | -                                                                | 2.40                 | 2.45 | 2.51 | V     |

| V <sub>LVD1</sub> | 2.71 V selected in PSoC Designer |                                                                  | 2.64 <sup>[46]</sup> | 2.71 | 2.78 |       |

| V <sub>LVD2</sub> | 2.92 V selected in PSoC Designer |                                                                  | 2.85 <sup>[47]</sup> | 2.92 | 2.99 |       |

| V <sub>LVD3</sub> | 3.02 V selected in PSoC Designer |                                                                  | 2.95 <sup>[48]</sup> | 3.02 | 3.09 |       |

| V <sub>LVD4</sub> | 3.13 V selected in PSoC Designer |                                                                  | 3.06                 | 3.13 | 3.20 |       |

| V <sub>LVD5</sub> | 1.90 V selected in PSoC Designer |                                                                  | 1.84                 | 1.90 | 2.32 |       |

| V <sub>LVD6</sub> | 1.80 V selected in PSoC Designer |                                                                  | 1.75 <sup>[49]</sup> | 1.80 | 1.84 |       |

| V <sub>LVD7</sub> | 4.73 V selected in PSoC Designer |                                                                  | 4.62                 | 4.73 | 4.83 |       |

#### DC Programming Specifications (CY8C24193/493)

The following table lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

#### Table 20. DC Programming Specifications

| Symbol                | Description                                                                                       | Conditions                                                                                                                         | Min             | Тур | Max                    | Units |

|-----------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|------------------------|-------|

| V <sub>DDIWRITE</sub> | Supply voltage for flash write operations                                                         | -                                                                                                                                  | 1.71            | -   | 5.25                   | V     |

| I <sub>DDP</sub>      | Supply current during<br>programming or verify                                                    | -                                                                                                                                  | _               | 5   | 25                     | mA    |

| V <sub>ILP</sub>      | Input low voltage during<br>programming or verify                                                 | See appropriate DC GPIO Specifications (CY8C24093/293/393/693) on page 33                                                          | _               | -   | V <sub>IL</sub>        | V     |

| V <sub>IHP</sub>      | Input high voltage during<br>programming or verify                                                | See appropriate DC GPIO Specifications (CY8C24093/293/393/693) on page 33                                                          | V <sub>IH</sub> | -   | _                      | V     |

| I <sub>ILP</sub>      | Input current when Applying V <sub>ILP</sub><br>to P1[0] or P1[1] during<br>programming or verify | Driving internal pull-down resistor                                                                                                | -               | -   | 0.2                    | mA    |

| I <sub>IHP</sub>      | Input current when applying V <sub>IHP</sub> to P1[0] or P1[1] during programming or verify       | Driving internal pull-down resistor                                                                                                | -               | _   | 1.5                    | mA    |

| V <sub>OLP</sub>      | Output low voltage during<br>programming or verify                                                |                                                                                                                                    | _               | -   | V <sub>SS</sub> + 0.75 | V     |

| V <sub>OHP</sub>      | Output high voltage during<br>programming or verify                                               | See appropriate DC GPIO Specifications (CY8C24093/293/393/693) on page 33. For $V_{DD}$ > 3V use $V_{OH4}$ in Table 36 on page 33. | V <sub>OH</sub> | -   | V <sub>DD</sub>        | V     |

| Flash <sub>ENPB</sub> | Flash write endurance                                                                             | Erase/write cycles per block                                                                                                       | 50,000          | -   | -                      | -     |

| Flash <sub>DR</sub>   | Flash data retention                                                                              | Following maximum Flash write cycles;<br>ambient temperature of 55 °C                                                              | 20              | -   | _                      | Years |

#### Notes

32. Always greater than 50 mV above  $V_{PPOR1}$  voltage for falling supply. 33. Always greater than 50 mV above  $V_{PPOR2}$  voltage for falling supply. 34. Always greater than 50 mV above  $V_{PPOR3}$  voltage for falling supply. 35. Always greater than 50 mV above  $V_{PPOR0}$  voltage for falling supply.

## DC I<sup>2</sup>C Specifications (CY8C24193/493)

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 3.0 V to 5.5 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 2.4 V to 3.0 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 1.71 V to 2.4 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

#### Table 21. DC I<sup>2</sup>C Specifications<sup>[36]</sup>

| Symbol             | Description      | Conditions                                                  | Min                    | Тур | Max                                        | Units |

|--------------------|------------------|-------------------------------------------------------------|------------------------|-----|--------------------------------------------|-------|

| V <sub>ILI2C</sub> | Input low level  | $3.1 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}$  | -                      | _   | $0.25 \times V_{DD}$                       | V     |

|                    |                  | $2.5 \text{ V} \le \text{V}_{\text{DD}} \le 3.0 \text{ V}$  | _                      | _   | $0.3 \times V_{DD}$                        | V     |

|                    |                  | $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.4 \text{ V}$ | _                      | _   | $0.3 \times V_{DD}$                        | V     |

| V <sub>IHI2C</sub> | Input high level | 1.71 V ≤ V <sub>DD</sub> ≤ 5.5 V                            | 0.65 × V <sub>DD</sub> | -   | V <sub>DD</sub> +<br>0.7 V <sup>[37]</sup> | V     |

#### Shield Driver DC Specifications (CY8C24193/493)

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 3.0 V to 5.5 V and -40 °C  $\leq T_A \leq 85$  °C, 2.4 V to 3.0 V and -40 °C  $\leq T_A \leq 85$  °C, or 1.71 V to 2.4 V and -40 °C  $\leq T_A \leq 85$  °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

#### Table 22. Shield Driver DC Specifications

| Symbol             | Description             | Conditions                                                 | Min   | Тур | Max   | Units |

|--------------------|-------------------------|------------------------------------------------------------|-------|-----|-------|-------|

| V <sub>Ref</sub>   | Reference buffer output | $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}$ | 0.942 | _   | 1.106 | V     |

| V <sub>RefHi</sub> | Reference buffer output | $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}$ | 1.104 | _   | 1.296 | V     |

#### DC IDAC Specifications (CY8C24193/493)

The following table lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

#### Table 23. DC IDAC Specifications (8-bit IDAC)

| Symbol       | Description               | Min | Тур | Max | Units | Notes                 |

|--------------|---------------------------|-----|-----|-----|-------|-----------------------|

| IDAC_DNL     | Differential nonlinearity | –1  | -   | 1   | LSB   |                       |

| IDAC_DNL     | Integral nonlinearity     | -2  | -   | 2   | LSB   |                       |

| IDAC_Current | Range = 4x                | 138 | -   | 169 | μA    | DAC setting = 127 dec |

|              | Range = 8x                | 138 | -   | 169 | μA    | DAC setting = 64 dec  |

#### Table 24. DC IDAC Specifications (7-bit IDAC)

| Symbol       | Description               | Min | Тур | Max | Units | Notes                 |

|--------------|---------------------------|-----|-----|-----|-------|-----------------------|

| IDAC_DNL     | Differential nonlinearity | –1  | -   | 1   | LSB   |                       |

| IDAC_DNL     | Integral nonlinearity     | -2  | -   | 2   | LSB   |                       |

| IDAC_Current | Range = 4x                | 137 | -   | 168 | μA    | DAC setting = 127 dec |

|              | Range = 8x                | 138 | -   | 169 | μA    | DAC setting = 64 dec  |

Notes

36. Pull-up resistors on I2C interface cannot be connected to a supply voltage that is more than 0.7 V higher than the CY8C24x93 power supply. See the CY8C24x93 Silicon Errata document for more details.

37. Please refer to Item # 6 of the CY8C24x93 Family.

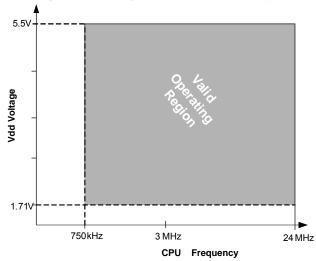

## Electrical Specifications (CY8C24093/293/393/693)

This section presents the DC and AC electrical specifications of the CY8C24093/293/393/693 PSoC devices. For the latest electrical specifications, confirm that you have the most recent datasheet by visiting the web at http://www.cypress.com/psoc.

#### Figure 16. Voltage versus CPU Frequency

## Absolute Maximum Ratings (CY8C24093/293/393/693)

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested.

#### Table 33. Absolute Maximum Ratings

| Symbol                           | Description                         | Conditions                                                                                                                                                                                      | Min                   | Тур | Max                   | Units |

|----------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----|-----------------------|-------|

| T <sub>STG</sub>                 | Storage temperature                 | Higher storage temperatures reduce data<br>retention time. Recommended Storage<br>Temperature is +25 °C ± 25 °C. Extended<br>duration storage temperatures above 85 °C<br>degrades reliability. | -55                   | +25 | +125                  | °C    |

| V <sub>DD</sub>                  | Supply voltage relative to $V_{SS}$ | -                                                                                                                                                                                               | -0.5                  | _   | +6.0                  | V     |

| V <sub>IO</sub>                  | DC input voltage                    | _                                                                                                                                                                                               | V <sub>SS</sub> – 0.5 | —   | V <sub>DD</sub> + 0.5 | V     |

| V <sub>IOZ</sub> <sup>[42]</sup> | DC voltage applied to tristate      | -                                                                                                                                                                                               | $V_{\rm SS} - 0.5$    | _   | V <sub>DD</sub> + 0.5 | V     |

| I <sub>MIO</sub>                 | Maximum current into any port pin   | -                                                                                                                                                                                               | -25                   | _   | +50                   | mA    |

| ESD                              | Electrostatic discharge voltage     | Human body model ESD                                                                                                                                                                            | 2000                  | —   | -                     | V     |

| LU                               | Latch-up current                    | In accordance with JESD78 standard                                                                                                                                                              | -                     | —   | 200                   | mA    |

#### Operating Temperature (CY8C24093/293/393/693)

#### Table 34. Operating Temperature

| Symbol         | Description                  | Conditions                                                                                                                                                                             | Min | Тур | Max  | Units |

|----------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|-------|

| T <sub>A</sub> | Ambient temperature          | -                                                                                                                                                                                      | -40 | -   | +85  | °C    |

| Т <sub>С</sub> | Commercial temperature range | -                                                                                                                                                                                      | 0   |     | 70   | °C    |

| TJ             | Operational die temperature  | The temperature rise from ambient to junction is package specific. Refer the Thermal Impedances on page 49. The user must limit the power consumption to comply with this requirement. | -40 | _   | +100 | °C    |

#### Note

42. Port1 pins are hot-swap capable with I/O configured in High-Z mode, and pin input voltage above V<sub>DD</sub>.

## DC GPIO Specifications (CY8C24093/293/393/693)

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 3.0 V to 5.5 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 2.4 V to 3.0 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 1.71 V to 2.4 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 C and are for design guidance only.

| Symbol                | Description                                                                       | Conditions                                                                                                                                                                                            | Min                    | Тур   | Max  | Units |

|-----------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------|------|-------|

| R <sub>PU</sub>       | Pull-up resistor                                                                  | -                                                                                                                                                                                                     | 4                      | 5.60  | 8    | kΩ    |

| V <sub>OH1</sub>      | High output voltage<br>Port 2 or 3 or 4 pins                                      | $I_{OH} \le 10 \ \mu$ A, maximum of 10 mA source current in all I/Os                                                                                                                                  | V <sub>DD</sub> – 0.20 | -     | -    | V     |

| V <sub>OH2</sub>      | High output voltage<br>Port 2 or 3 or 4 pins                                      | I <sub>OH</sub> = 1 mA, maximum of 20 mA source<br>current in all I/Os                                                                                                                                | V <sub>DD</sub> – 0.90 | -     | _    | V     |

| V <sub>OH3</sub>      | High output voltage<br>Port 0 or 1 pins with LDO regulator<br>Disabled for port 1 | $I_{OH}$ < 10 $\mu$ A, maximum of 10 mA source current in all I/Os                                                                                                                                    | V <sub>DD</sub> – 0.20 | -     | -    | V     |

| V <sub>OH4</sub>      | High output voltage<br>Port 0 or 1 pins with LDO regulator<br>Disabled for port 1 | I <sub>OH</sub> = 5 mA, maximum of 20 mA source<br>current in all I/Os                                                                                                                                | V <sub>DD</sub> – 0.90 | -     | -    | V     |

| V <sub>OH5</sub>      | High output voltage<br>Port 1 Pins with LDO Regulator Enabled<br>for 3 V out      | $I_{OH}$ < 10 $\mu$ A, V <sub>DD</sub> > 3.1 V, maximum of 4 I/Os all sourcing 5 mA                                                                                                                   | 2.85                   | 3.00  | 3.30 | V     |

| V <sub>OH6</sub>      | High output voltage<br>Port 1 pins with LDO regulator enabled for<br>3 V out      | $I_{OH}$ = 5 mA, $V_{DD}$ > 3.1 V, maximum of 20 mA source current in all I/Os                                                                                                                        | 2.20                   | -     | -    | V     |

| V <sub>OH7</sub>      | High output voltage<br>Port 1 pins with LDO enabled for 2.5 V out                 | $I_{OH}$ < 10 $\mu$ A, V <sub>DD</sub> > 2.7 V, maximum of 20 mA source current in all I/Os                                                                                                           | 2.35                   | 2.50  | 2.75 | V     |

| V <sub>OH8</sub>      | High output voltage<br>Port 1 pins with LDO enabled for 2.5 V out                 | I <sub>OH</sub> = 2 mA, V <sub>DD</sub> > 2.7 V, maximum of 20 mA<br>source current in all I/Os                                                                                                       | 1.90                   | -     | Ι    | V     |

| V <sub>OH9</sub>      | High output voltage<br>Port 1 pins with LDO enabled for 1.8 V out                 | $I_{OH}$ < 10 $\mu$ A, $V_{DD}$ > 2.7 V, maximum of 20 mA source current in all I/Os                                                                                                                  | 1.60                   | 1.80  | 2.10 | V     |

| V <sub>OH10</sub>     | High output voltage<br>Port 1 pins with LDO enabled for 1.8 V out                 |                                                                                                                                                                                                       | 1.20                   | -     | -    | V     |

| V <sub>OL</sub>       | Low output voltage                                                                | $I_{OL}$ = 25 mA, $V_{DD}$ > 3.3 V, maximum of<br>60 mA sink current on even port pins (for<br>example, P0[2] and P1[4]) and 60 mA sink<br>current on odd port pins (for example, P0[3]<br>and P1[5]) | _                      | -     | 0.75 | V     |

| V <sub>IL</sub>       | Input low voltage                                                                 | -                                                                                                                                                                                                     | -                      | -     | 0.80 | V     |

| V <sub>IH</sub>       | Input high voltage                                                                | -                                                                                                                                                                                                     | 2.00                   | -     | -    | V     |

| V <sub>H</sub>        | Input hysteresis voltage                                                          | -                                                                                                                                                                                                     | _                      | 80    | I    | mV    |

| IIL                   | Input leakage (Absolute Value)                                                    | -                                                                                                                                                                                                     | _                      | 0.001 | 1    | μΑ    |

| C <sub>PIN</sub>      | Pin capacitance                                                                   | Package and pin dependent<br>Temp = 25 °C                                                                                                                                                             | 0.50                   | 1.70  | 7    | pF    |

| V <sub>ILLVT3.3</sub> | Input Low Voltage with low threshold<br>enable set, Enable for Port1              | Bit3 of IO_CFG1 set to enable low threshold voltage of Port1 input                                                                                                                                    | 0.8                    | V     | -    | -     |

| V <sub>IHLVT3.3</sub> | Input High Voltage with low threshold<br>enable set, Enable for Port1             | Bit3 of IO_CFG1 set to enable low threshold voltage of Port1 input                                                                                                                                    | 1.4                    | 1     |      | V     |

| V <sub>ILLVT5.5</sub> | Input Low Voltage with low threshold<br>enable set, Enable for Port1              | Bit3 of IO_CFG1 set to enable low threshold voltage of Port1 input                                                                                                                                    | 0.8                    | V     | 1    | -     |

| V <sub>IHLVT5.5</sub> | Input High Voltage with low threshold<br>enable set, Enable for Port1             | Bit3 of IO_CFG1 set to enable low threshold voltage of Port1 input                                                                                                                                    | 1.7                    | _     | _    | V     |

## Comparator User Module Electrical Specifications (CY8C24093/293/393/693)

The following table lists the guaranteed maximum and minimum specifications. Unless stated otherwise, the specifications are for the entire device voltage and temperature operating range: –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 1.71 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V.

Table 42. Comparator User Module Electrical Specifications

| Symbol            | Description              | Conditions                                  | Min | Тур | Max | Units |

|-------------------|--------------------------|---------------------------------------------|-----|-----|-----|-------|

| t <sub>COMP</sub> | Comparator response time | 50 mV overdrive                             | -   | 70  | 100 | ns    |

| Offset            |                          | Valid from 0.2 V to V <sub>DD</sub> – 0.2 V | -   | 2.5 | 30  | mV    |

| Current           |                          | Average DC current, 50 mV<br>overdrive      | -   | 20  | 80  | μA    |

| PSRR              | Supply voltage > 2 V     | Power supply rejection ratio                | -   | 80  | -   | dB    |

| FORK              | Supply voltage < 2 V     | Power supply rejection ratio                | -   | 40  | -   | dB    |

| Input range       |                          | -                                           | 0   |     | 1.5 | V     |

#### ADC Electrical Specifications (CY8C24093/293/393/693)

#### Table 43. ADC User Module Electrical Specifications

| Symbol              | Description                  | Conditions                                                                                     | Min                       | Тур                       | Max                       | Units |

|---------------------|------------------------------|------------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|-------|

| Input               |                              |                                                                                                |                           |                           |                           |       |

| V <sub>IN</sub>     | Input voltage range          | -                                                                                              | 0                         | _                         | VREFADC                   | V     |

| C <sub>IIN</sub>    | Input capacitance            | -                                                                                              | -                         | -                         | 5                         | pF    |

| R <sub>IN</sub>     | Input resistance             | Equivalent switched cap input resistance for 8-, 9-, or 10-bit resolution                      | 1/(500fF ×<br>data clock) | 1/(400fF ×<br>data clock) | 1/(300fF ×<br>data clock) | Ω     |

| Reference           |                              |                                                                                                |                           |                           |                           |       |

| V <sub>REFADC</sub> | ADC reference voltage        | -                                                                                              | 1.14                      | -                         | 1.26                      | V     |

| Conversion F        | Rate                         |                                                                                                | •                         |                           |                           |       |

| F <sub>CLK</sub>    | Data clock                   | Source is chip's internal main<br>oscillator. See AC Chip-Level<br>Specifications for accuracy | 2.25                      | _                         | 6                         | MHz   |

| S8                  | 8-bit sample rate            | Data clock set to 6 MHz. sample<br>rate = 0.001/ (2 <sup>A</sup> Resolution/Data<br>Clock)     | -                         | 23.43                     | _                         | ksps  |

| S10                 | 10-bit sample rate           | Data clock set to 6 MHz. sample<br>rate = 0.001/ (2 <sup>resolution</sup> /data<br>clock)      | _                         | 5.85                      | _                         | ksps  |

| DC Accuracy         | /                            |                                                                                                |                           |                           |                           | 1     |

| RES                 | Resolution                   | Can be set to 8-, 9-, or 10-bit                                                                | 8                         | -                         | 10                        | bits  |

| DNL                 | Differential nonlinearity    | -                                                                                              | -1                        | _                         | +2                        | LSB   |

| INL                 | Integral nonlinearity        | -                                                                                              | -2                        | -                         | +2                        | LSB   |

| E <sub>OFFSET</sub> | Offset error                 | 8-bit resolution                                                                               | 0                         | 3.20                      | 19.20                     | LSB   |

|                     |                              | 10-bit resolution                                                                              | 0                         | 12.80                     | 76.80                     | LSB   |

| E <sub>GAIN</sub>   | Gain error                   | For any resolution                                                                             | -5                        | -                         | +5                        | %FSR  |

| Power               | •                            | · ·                                                                                            |                           | •                         | •                         |       |

| I <sub>ADC</sub>    | Operating current            | -                                                                                              | -                         | 2.10                      | 2.60                      | mA    |

| PSRR                | Power supply rejection ratio | PSRR (V <sub>DD</sub> > 3.0 V)                                                                 | -                         | 24                        | -                         | dB    |

|                     |                              | PSRR (V <sub>DD</sub> < 3.0 V)                                                                 | -                         | 30                        | -                         | dB    |

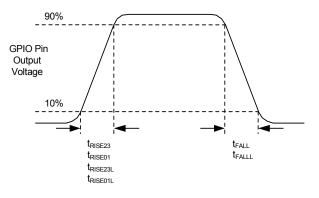

## AC GPIO Specifications (CY8C24093/293/393/693)

The following table lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges. **Table 50. AC GPIO Specifications**

| Symbol               | Description                                                                | Conditions                                                             | Min | Тур | Max                                                                                           | Units |

|----------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------|-----|-----|-----------------------------------------------------------------------------------------------|-------|

| F <sub>GPIO</sub>    | GPIO operating frequency                                                   | Normal strong mode Port 0, 1                                           | 0   | -   | 6 MHz for                                                                                     | MHz   |

|                      |                                                                            |                                                                        | 0   | -   | 1.71 V <v<sub>DD &lt; 2.40 V<br/>12 MHz for<br/>2.40 V &lt; V<sub>DD</sub>&lt; 5.50 V</v<sub> | MHz   |

| t <sub>RISE23</sub>  | Rise time, strong mode, Cload = 50 pF<br>Port 2 or 3 or 4 pins             | V <sub>DD</sub> = 3.0 to 3.6 V, 10% to 90%                             | 15  | -   | 80                                                                                            | ns    |

| t <sub>RISE23L</sub> | Rise time, strong mode low supply,<br>Cload = 50 pF, Port 2 or 3 or 4 pins | V <sub>DD</sub> = 1.71 to 3.0 V, 10% to 90%                            | 15  | Ι   | 80                                                                                            | ns    |

| t <sub>RISE01</sub>  | Rise time, strong mode, Cload = 50 pF<br>Ports 0 or 1                      | V <sub>DD</sub> = 3.0 to 3.6 V, 10% to 90%<br>LDO enabled or disabled  | 10  | -   | 50                                                                                            | ns    |

| t <sub>RISE01L</sub> | Rise time, strong mode low supply,<br>Cload = 50 pF, Ports 0 or 1          | V <sub>DD</sub> = 1.71 to 3.0 V, 10% to 90%<br>LDO enabled or disabled | 10  | -   | 80                                                                                            | ns    |

| t <sub>FALL</sub>    | Fall time, strong mode, Cload = 50 pF<br>all ports                         | V <sub>DD</sub> = 3.0 to 3.6 V, 10% to 90%                             | 10  | _   | 50                                                                                            | ns    |

| t <sub>FALLL</sub>   | Fall time, strong mode low supply,<br>Cload = 50 pF, all ports             | V <sub>DD</sub> = 1.71 to 3.0 V, 10% to 90%                            | 10  | l   | 70                                                                                            | ns    |

## Figure 17. GPIO Timing Diagram

#### Table 51. AC Characteristics – USB Data Timings

| Symbol             | Description                                             | Conditions         | Min        | Тур | Max        | Units |

|--------------------|---------------------------------------------------------|--------------------|------------|-----|------------|-------|

| t <sub>DRATE</sub> | Full speed data rate                                    | Average bit rate   | 12 – 0.25% | 12  | 12 + 0.25% | MHz   |

| t <sub>JR1</sub>   | Receiver jitter tolerance                               | To next transition | -18.5      | -   | 18.5       | ns    |

| t <sub>JR2</sub>   | Receiver jitter tolerance                               | To pair transition | -9.0       | _   | 9          | ns    |

| t <sub>DJ1</sub>   | FS Driver jitter                                        | To next transition | -3.5       | _   | 3.5        | ns    |

| t <sub>DJ2</sub>   | FS Driver jitter                                        | To pair transition | -4.0       | -   | 4.0        | ns    |

| t <sub>FDEOP</sub> | Source jitter for differential transition               | To SE0 transition  | -2.0       | -   | 5          | ns    |

| t <sub>FEOPT</sub> | Source SE0 interval of EOP                              | -                  | 160.0      | -   | 175        | ns    |

| t <sub>FEOPR</sub> | Receiver SE0 interval of EOP                            | -                  | 82.0       | -   | -          | ns    |

| t <sub>FST</sub>   | Width of SE0 interval during<br>differential transition | -                  | -          | _   | 14         | ns    |

#### Table 52. AC Characteristics – USB Driver

| Symbol                            | Description                     | Conditions | Min  | Тур | Max  | Units |

|-----------------------------------|---------------------------------|------------|------|-----|------|-------|

| t <sub>FR</sub>                   | Transition rise time            | 50 pF      | 4    | _   | 20   | ns    |

| t <sub>FF</sub>                   | Transition fall time            | 50 pF      | 4    | _   | 20   | ns    |

| t <sub>FRFM</sub> <sup>[52]</sup> | Rise/fall time matching         | -          | 90   | _   | 111  | %     |

| V <sub>CRS</sub>                  | Output signal crossover voltage | -          | 1.30 | -   | 2.00 | V     |

#### AC Comparator Specifications (CY8C24093/293/393/693)

The following table lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

#### Table 53. AC Low Power Comparator Specifications