#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XF

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | M8C                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 24MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI                                                       |

| Peripherals                | LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 34                                                                          |

| Program Memory Size        | 16KB (16K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                                |

| Data Converters            | A/D 1x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 48-UFQFN Exposed Pad                                                        |

| Supplier Device Package    | 48-QFN (6x6)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c24393-24lqxi |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

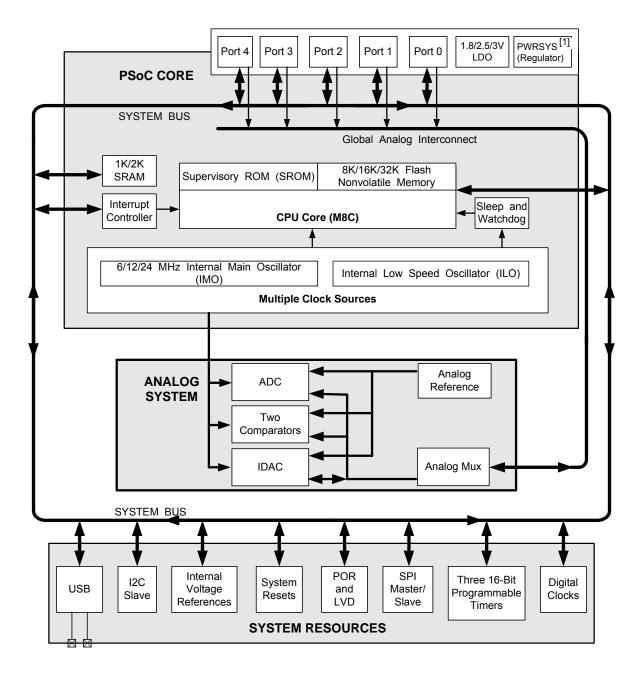

## Logic Block Diagram

## **PSoC<sup>®</sup>** Functional Overview

The PSoC family consists of on-chip controller devices, which are designed to replace multiple traditional microcontroller unit (MCU)-based components with one, low cost single-chip programmable component. A PSoC device includes configurable analog and digital blocks, and programmable interconnect. This architecture allows the user to create customized peripheral configurations, to match the requirements of each individual application. Additionally, a fast CPU, Flash program memory, SRAM data memory, and configurable I/O are included in a range of convenient pinouts.

The architecture for this device family, as shown in the Logic Block Diagram on page 2, consists of three main areas:

- The Core

- Analog System

- System Resources (including a full-speed USB port).

A common, versatile bus allows connection between I/O and the analog system.

Depending on the PSoC package, up to 36 GPIO are included in the CY8C24x93 PSoC device. The GPIO provides access to the MCU and analog mux.

### **PSoC Core**

The PSoC Core is a powerful engine that supports a rich instruction set. It encompasses SRAM for data storage, an interrupt controller, sleep and watchdog timers, and IMO and ILO. The CPU core, called the M8C, is a powerful processor with speeds up to 24 MHz. The M8C is a 4-MIPS, 8-bit Harvard-architecture microprocessor.

### Analog system

The analog system is composed of an ADC, two comparators and an IDAC. It has an internal 0.8 V, 1 V or 1.2 V analog reference. All the pins can be configured to connect to the analog system.

### ADC

The ADC in the CY8C24x93 device is an incremental analog-to-digital converter with a range of 8 to 10 bits supporting signed and unsigned data formats. The input to the ADC can be from any pin.

IDAC

The IDAC can provide current source up to  $512 \mu$ A to any GPIO pin. In the CY8C24x93 family of devices 4 ranges of current source can be implemented that can vary in 255 steps, and are connected to analog mux bus.

### Table 1. IDAC Ranges

| Range | Full Scale Range in µA |

|-------|------------------------|

| 1x    | 64                     |

| 2x    | 128                    |

| 4x    | 256                    |

| 8x    | 512                    |

### Comparator

The CY8C24x93 family has two high-speed, low-power comparators. The comparators have three voltage references, 0.8 V, 1.0 V and 1.2 V. Comparator inputs can be connected from any pin through the analog mux bus. The comparator output can be read in firmware for processing or routed out via specific pins (P1\_0 or P1\_4).

The output of the two comparators can be combined with 2-input logic functions. The combinatorial output can be optionally combined with a latched value and routed to a pin output or to the interrupt controller. The input multiplexers and the comparator are controller through the CMP User Module.

### Analog Multiplexer System

The Analog Mux Bus can connect to every GPIO pin and can be internally connected to the ADC, Comprators or the IDAC.

Other multiplexer applications include:

- Chip-wide mux that allows analog input from any I/O pin.

- Crosspoint connection between any I/O pin combinations.

### **Additional System Resources**

System resources provide additional capability, such as configurable USB and I2C slave, SPI master/slave communication interface, three 16-bit programmable timers, software 8-bit PWM, low voltage detect, power on reset, and various system resets supported by the M8C.

The merits of each system resource are listed here:

- The I<sup>2</sup>C slave/SPI master-slave module provides 50/100/400 kHz communication over two wires. SPI communication over three or four wires runs at speeds of 46.9 kHz to 3 MHz (lower for a slower system clock).

- Low-voltage detection (LVD) interrupts can signal the application of falling voltage levels, while the advanced power-on-reset (POR) circuit eliminates the need for a system supervisor.

- A register-controlled bypass mode allows the user to disable the LDO regulator.

- An 8-bit Software PWM is provided for applications like buzzer control or lighting control. A 16-bit Timer acts as the input clock to the PWM. The ISR increments a software counter (8-bit), checks for PWM compare condition and toggles a GPIO accordingly. PWM Output is available on all GPIOs.

## **Development Tools**

PSoC Designer<sup>™</sup> is the revolutionary integrated design environment (IDE) that you can use to customize PSoC to meet your specific application requirements. PSoC Designer software accelerates system design and time to market. Develop your applications using a library of precharacterized analog and digital peripherals (called user modules) in a drag-and-drop design environment. Then, customize your design by leveraging the dynamically generated application programming interface (API) libraries of code. Finally, debug and test your designs with the integrated debug environment, including in-circuit emulation and standard software debug features. PSoC Designer includes:

- Application editor graphical user interface (GUI) for device and user module configuration and dynamic reconfiguration

- Extensive user module catalog

- Integrated source-code editor (C and assembly)

- Free C compiler with no size restrictions or time limits

- Built-in debugger

- In-circuit emulation

- Built-in support for communication interfaces:

- Hardware and software I<sup>2</sup>C slaves and masters

- □ Full-speed USB 2.0

- □ Up to four full-duplex universal asynchronous receiver/transmitters (UARTs), SPI master and slave, and wireless

PSoC Designer supports the entire library of PSoC 1 devices and runs on Windows XP, Windows Vista, and Windows 7.

### **PSoC Designer Software Subsystems**

### Design Entry

In the chip-level view, choose a base device to work with. Then select different onboard analog and digital components that use the PSoC blocks, which are called user modules. Examples of user modules are analog-to-digital converters (ADCs), digital-to-analog converters (DACs), amplifiers, and filters. Configure the user modules for your chosen application and connect them to each other and to the proper pins. Then generate your project. This prepopulates your project with APIs and libraries that you can use to program your application.

The tool also supports easy development of multiple configurations and dynamic reconfiguration. Dynamic reconfiguration makes it possible to change configurations at run time. In essence, this lets you to use more than 100 percent of PSoC's resources for an application.

#### Code Generation Tools

The code generation tools work seamlessly within the PSoC Designer interface and have been tested with a full range of debugging tools. You can develop your design in C, assembly, or a combination of the two.

**Assemblers**. The assemblers allow you to merge assembly code seamlessly with C code. Link libraries automatically use absolute addressing or are compiled in relative mode, and linked with other software modules to get absolute addressing.

**C Language Compilers**. C language compilers are available that support the PSoC family of devices. The products allow you to create complete C programs for the PSoC family devices. The optimizing C compilers provide all of the features of C, tailored to the PSoC architecture. They come complete with embedded libraries providing port and bus operations, standard keypad and display support, and extended math functionality.

#### Debugger

PSoC Designer has a debug environment that provides hardware in-circuit emulation, allowing you to test the program in a physical system while providing an internal view of the PSoC device. Debugger commands allow you to read and program and read and write data memory, and read and write I/O registers. You can read and write CPU registers, set and clear breakpoints, and provide program run, halt, and step control. The debugger also lets you to create a trace buffer of registers and memory locations of interest.

#### Online Help System

The online help system displays online, context-sensitive help. Designed for procedural and quick reference, each functional subsystem has its own context-sensitive help. This system also provides tutorials and links to FAQs and an Online Support Forum to aid the designer.

#### In-Circuit Emulator

A low-cost, high-functionality in-circuit emulator (ICE) is available for development support. This hardware can program single devices.

The emulator consists of a base unit that connects to the PC using a USB port. The base unit is universal and operates with all PSoC devices. Emulation pods for each device family are available separately. The emulation pod takes the place of the PSoC device in the target board and performs full-speed (24 MHz) operation.

## **Pinouts**

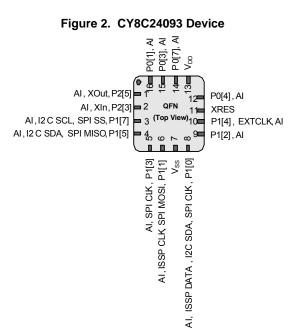

## 16-pin QFN (13 GPIOs) [2]

| Table 2. | Pin Definitions – CY8C24093 <sup>[3]</sup> | 3] |

|----------|--------------------------------------------|----|

|----------|--------------------------------------------|----|

| Pin | Ту      | pe     | Name            | Description                                                                |

|-----|---------|--------|-----------------|----------------------------------------------------------------------------|

| No. | Digital | Analog | Name            | Description                                                                |

| 1   | I/O     | I      | P2[5]           | Crystal output (XOut)                                                      |

| 2   | I/O     | I      | P2[3]           | Crystal input (XIn)                                                        |

| 3   | IOHR    | I      | P1[7]           | I <sup>2</sup> C SCL, SPI SS                                               |

| 4   | IOHR    | I      | P1[5]           | I <sup>2</sup> C SDA, SPI MISO                                             |

| 5   | IOHR    | I      | P1[3]           | SPI CLK                                                                    |

| 6   | IOHR    | I      | P1[1]           | ISSP CLK <sup>[4]</sup> , I <sup>2</sup> C SCL, SPI<br>MOSI                |

| 7   | Po      | wer    | $V_{SS}$        | Ground connection                                                          |

| 8   | IOHR    | I      | P1[0]           | ISSP DATA <sup>[4]</sup> , I <sup>2</sup> C SDA, SPI<br>CLK <sup>[5]</sup> |

| 9   | IOHR    | I      | P1[2]           |                                                                            |

| 10  | IOHR    | I      | P1[4]           | Optional external clock<br>(EXTCLK)                                        |

| 11  | Inj     | put    | XRES            | Active high external reset with internal pull-down                         |

| 12  | IOH     | I      | P0[4]           |                                                                            |

| 13  | Po      | wer    | V <sub>DD</sub> | Supply voltage                                                             |

| 14  | IOH     | I      | P0[7]           |                                                                            |

| 15  | IOH     | I      | P0[3]           |                                                                            |

| 16  | IOH     | I      | P0[1]           |                                                                            |

**LEGEND** A = Analog, I = Input, O = Output, OH = 5 mA High Output Drive, R = Regulated Output.

Notes

No center pad.

13 GPIOs.

5. Alternate SPI clock.

Is GP103.

In Schlos.

On power-up, the SDA(P1[0]) drives a strong high for 256 sleep clock cycles and drives resistive low for the next 256 sleep clock cycles. The SCL(P1[1]) line drives resistive low for 512 sleep clock cycles and both the pins transition to high impedance state. On reset, after XRES de-asserts, the SDA and the SCL lines drive resistive low for 8 sleep clock cycles and transition to high impedance state. Hence, during power-up or reset event, P1[1] and P1[0] may disturb the I<sup>2</sup>C bus. Use alternate pins if you encounter issues.

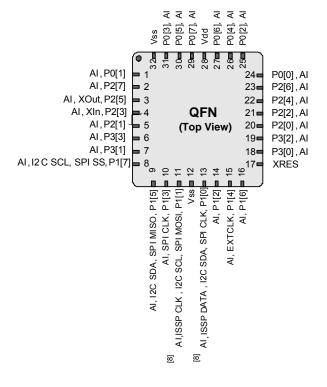

### 32-pin QFN (28 GPIOs) [6]

### Table 3. Pin Definitions – CY8C24193<sup>[7]</sup>

| Pin | Ту      | ре     | Name            | ne Description                                                             |  |

|-----|---------|--------|-----------------|----------------------------------------------------------------------------|--|

| No. | Digital | Analog | Name            | Description                                                                |  |

| 1   | IOH     | I      | P0[1]           |                                                                            |  |

| 2   | I/O     | I      | P2[7]           |                                                                            |  |

| 3   | I/O     | I      | P2[5]           | Crystal output (XOut)                                                      |  |

| 4   | I/O     | I      | P2[3]           | Crystal input (XIn)                                                        |  |

| 5   | I/O     | I      | P2[1]           |                                                                            |  |

| 6   | I/O     | I      | P3[3]           |                                                                            |  |

| 7   | I/O     | I      | P3[1]           |                                                                            |  |

| 8   | IOHR    | I      | P1[7]           | I <sup>2</sup> C SCL, SPI SS                                               |  |

| 9   | IOHR    | I      | P1[5]           | I <sup>2</sup> C SDA, SPI MISO                                             |  |

| 10  | IOHR    | I      | P1[3]           | SPI CLK.                                                                   |  |

| 11  | IOHR    | I      | P1[1]           | ISSP CLK <sup>[8]</sup> , I <sup>2</sup> C SCL, SPI MOSI.                  |  |

| 12  | Pov     | wer    | V <sub>SS</sub> | Ground connection.                                                         |  |

| 13  | IOHR    | ļ      | P1[0]           | ISSP DATA <sup>[8]</sup> , I <sup>2</sup> C SDA,<br>SPI CLK <sup>[9]</sup> |  |

| 14  | IOHR    | I      | P1[2]           |                                                                            |  |

| 15  | IOHR    | I      | P1[4]           | Optional external clock input<br>(EXTCLK)                                  |  |

| 16  | IOHR    | I      | P1[6]           |                                                                            |  |

| 17  | Inp     | out    | XRES            | Active high external reset with internal pull-down                         |  |

| 18  | I/O     | I      | P3[0]           |                                                                            |  |

| 19  | I/O     | I      | P3[2]           |                                                                            |  |

| 20  | I/O     | I      | P2[0]           |                                                                            |  |

| 21  | I/O     | I      | P2[2]           |                                                                            |  |

| 22  | I/O     | I      | P2[4]           |                                                                            |  |

| 23  | I/O     | I      | P2[6]           |                                                                            |  |

| 24  | IOH     | I      | P0[0]           |                                                                            |  |

| 25  | IOH     | I      | P0[2]           |                                                                            |  |

| 26  | IOH     | I      | P0[4]           |                                                                            |  |

| 27  | IOH     | I      | P0[6]           |                                                                            |  |

| 28  | Pov     | wer    | V <sub>DD</sub> | Supply voltage                                                             |  |

| 29  | IOH     | I      | P0[7]           |                                                                            |  |

| 30  | IOH     | I      | P0[5]           |                                                                            |  |

| 31  | IOH     | I      | P0[3]           |                                                                            |  |

| 32  | Pov     | wer    | V <sub>SS</sub> | Ground connection                                                          |  |

| CP  | Pov     | wer    | V <sub>SS</sub> | Center pad must be connected to ground                                     |  |

### Figure 3. CY8C24193

**LEGEND** A = Analog, I = Input, O = Output, OH = 5 mA High Output Drive, R = Regulated Output.

### Notes

6. 28 GPIOs.

The center pad (CP) on the QFN package must be connected to ground (V<sub>SS</sub>) for best mechanical, thermal, and electrical performance. If not connected to ground, it must be electrically floated and not connected to any other signal.

8. On power-up, the SDA(P1[0]) drives a strong high for 256 sleep clock cycles and drives resistive low for the next 256 sleep clock cycles. The SCL(P1[1]) line drives resistive low for 512 sleep clock cycles and both the pins transition to high impedance state. On reset, after XRES de-asserts, the SDA and the SCL lines drive resistive low for 8 sleep clock cycles and transition to high impedance state. Hence, during power-up or reset event, P1[1] and P1[0] may disturb the I2C bus. Use alternate pins if you encounter issues.

9. Alternate SPI clock.

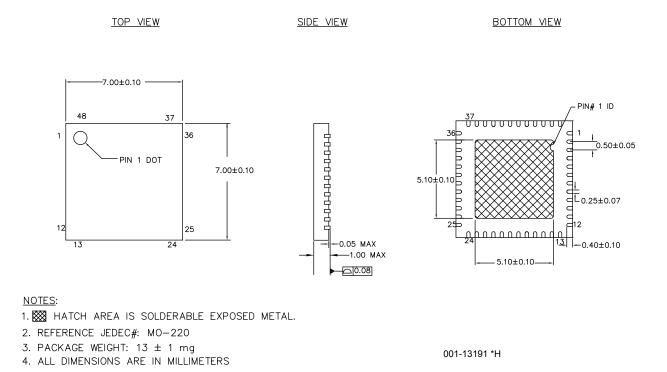

### 48-pin QFN (OCD) (36 GPIOs) [23]

The 48-pin QFN part is for the CY8C240093 On-Chip Debug (OCD). Note that this part is only used for in-circuit debugging.

| Pin<br>No.         | Digital | Analog | Name            | Description                                                                  |                    |           | Figu                           |                                  | /8C240093                                                                                                                                                                   |

|--------------------|---------|--------|-----------------|------------------------------------------------------------------------------|--------------------|-----------|--------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 <sup>[26]</sup>  |         |        | OCDOE           | OCD mode direction pin                                                       |                    |           | ·                              | Po[5], A<br>Po[3], A<br>Po[5], A | P0[7], AI<br>OCDE<br>OCDO<br>Vdd<br>P0[6], AI<br>P0[2], AI<br>P0[0], AI<br>P0[0], AI                                                                                        |

| 2                  | I/O     | I      | P2[7]           |                                                                              |                    |           |                                | n slod                           | P0 00 00 00 00 00 00 00 00 00 00 00 00 0                                                                                                                                    |

| 3                  | I/O     | Ι      | P2[5]           | Crystal output (XOut)                                                        |                    |           |                                | 46                               | 4 4 4 4 4 6 8 8 6 36 P2[6],AI                                                                                                                                               |

| 4                  | I/O     | I      | P2[3]           | Crystal input (XIn)                                                          |                    |           | A E 2                          |                                  | 35 <b>=</b> P2[4],AI                                                                                                                                                        |

| 5                  | I/O     | I      | P2[1]           |                                                                              |                    | AI, X     | (Out, P2[5] = 3                |                                  | 34 <b>□</b> P2[2],AI                                                                                                                                                        |

| 6                  | I/O     | I      | P4[3]           |                                                                              |                    |           | XIn , P2[3] = 4                |                                  | 33 <b>=</b> P2[0],AI                                                                                                                                                        |

| 7                  | I/O     | I      | P4[1]           |                                                                              |                    |           | AI, P2[1] = 5                  |                                  | 32 <b>=</b> P4[2],Al<br>QFN 31 <b>=</b> P4[0],Al                                                                                                                            |

| 8                  | I/O     | I      | P3[7]           |                                                                              |                    |           | AI, P4[3] = 6<br>AI, P4[1] = 7 |                                  | QFN 31 P4[0],AI<br>(Top View) 30 P3[6],AI                                                                                                                                   |

| 9                  | I/O     | I      | P3[5]           |                                                                              |                    |           | AI, P3[7] = 8                  |                                  | 29 <b>=</b> P3[4], Al                                                                                                                                                       |

| 10                 | I/O     | I      | P3[3]           |                                                                              |                    |           | AI, P3[5] 🗖 9                  |                                  | 28 <b>=</b> P3[2],AI                                                                                                                                                        |

| 11                 | I/O     | I      | P3[1]           |                                                                              |                    |           | AI, P3[3] = 10                 | 1                                | 27 <b>=</b> P3[0], Al                                                                                                                                                       |

| 12                 | IOHR    | I      | P1[7]           | I <sup>2</sup> C SCL, SPI SS                                                 |                    |           | AI, P3[1] = 11                 | m <del>st</del> i0 v0            | 26 <b>■</b> XRES<br>► ∞ • 0 = 3 = 3 = 3 = 25 <b>■</b> P1[6], Al                                                                                                             |

| 13                 | IOHR    | Ι      | P1[5]           | I <sup>2</sup> C SDA, SPI MISO                                               |                    | 20002, 01 |                                |                                  |                                                                                                                                                                             |

| 14 <sup>[26]</sup> |         |        | CCLK            | OCD CPU clock output                                                         | -                  |           | -                              | []<br>[]<br>[]                   | T[1]<br>D + D<br>D - D<br>1[0]<br>1[2]<br>1[2]                                                                                                                              |

| 15 <sup>[26]</sup> |         |        | HCLK            | OCD high speed clock output                                                  | -                  |           | ć                              | H BO SH I                        | OSI, P1[1]<br>VSS<br>D + 1<br>D - 1<br>D - Vdd<br>Vdd<br>AI, P1[2]<br>JLK, P1[4]<br>JLK, P1[4]                                                                              |

| 16                 | IOHR    | 1      | P1[3]           | SPI CLK.                                                                     | -                  |           | Ç                              | K, A                             | PI(1)<br>Vss<br>D +<br>D -<br>D -<br>D -<br>D -<br>AL, P1(0)<br>AL, P1(2)<br>EXTCLK, P1(4)                                                                                  |

| 17                 | IOHR    | 1      | P1[1]           | ISSP CLK <sup>[27],</sup> I <sup>2</sup> C SCL, SPI                          | -                  |           |                                |                                  | SPI<br>, SPI                                                                                                                                                                |

|                    |         | -      | [.]             | MOSI                                                                         |                    |           |                                | HCLK BY CLK, AI, PT[3]           | AI,ISSP CLK <sup>6</sup> , I2C SCL, SPI MOSI, P1[1]<br>Vsv<br>D +<br>AI,ISSP DATA', I2C SDA, SPI CLK, P1[0]<br>AI, ISSP DATA', I2C SDA, SPI CLK, P1[1]<br>AI, EXTCLK, P1[2] |

| 18                 | Po      | wer    | V <sub>SS</sub> | Ground connection                                                            |                    |           |                                |                                  | , 120                                                                                                                                                                       |

| 19                 | I/O     |        | D+              | USB D+                                                                       |                    |           | ŝ                              | 2                                | ATA                                                                                                                                                                         |

| 20                 | I/O     |        | D-              | USB D-                                                                       |                    |           |                                |                                  | SP C                                                                                                                                                                        |

| 21                 | Po      | wer    | V <sub>DD</sub> | Supply voltage                                                               |                    |           |                                |                                  | AI,IS                                                                                                                                                                       |

| 22                 | IOHR    | I      | P1[0]           | ISSP DATA <sup>[27]</sup> , I <sup>2</sup> C SDA, SPI<br>CLK <sup>[28]</sup> |                    |           |                                | [27]                             | [27, 28]<br>,                                                                                                                                                               |

| 23                 | IOHR    | Ι      | P1[2]           |                                                                              | Pin<br>No.         | Digital   | Analog                         | Name                             | Description                                                                                                                                                                 |

| 24                 | IOHR    | Ι      | P1[4]           | Optional external clock input<br>(EXTCLK)                                    | 37                 | IOH       | I                              | P0[0]                            |                                                                                                                                                                             |

| 25                 | IOHR    | I      | P1[6]           |                                                                              | 38                 | IOH       | I                              | P0[2]                            |                                                                                                                                                                             |

| 26                 | In      | put    | XRES            | Active high external reset with internal pull-down                           | 39                 | IOH       | I                              | P0[4]                            |                                                                                                                                                                             |

| 27                 | I/O     | I      | P3[0]           |                                                                              | 40                 | IOH       | I                              | P0[6]                            |                                                                                                                                                                             |

| 28                 | I/O     | Ι      | P3[2]           |                                                                              | 41                 | P         | ower                           | V <sub>DD</sub>                  | Supply voltage                                                                                                                                                              |

| 29                 | I/O     | I      | P3[4]           |                                                                              | 42 <sup>[26]</sup> |           |                                | OCDO                             | OCD even data I/O                                                                                                                                                           |

| 30                 | I/O     | Ι      | P3[6]           |                                                                              | 43 <sup>[26]</sup> |           |                                | OCDE                             | OCD odd data output                                                                                                                                                         |

| 31                 | I/O     | Ι      | P4[0]           |                                                                              | 44                 | IOH       |                                | P0[7]                            |                                                                                                                                                                             |

| 32                 | I/O     | Ι      | P4[2]           |                                                                              | 45                 | IOH       | I                              | P0[5]                            |                                                                                                                                                                             |

| 33                 | I/O     | I      | P2[0]           |                                                                              | 46                 | IOH       | I                              | P0[3]                            |                                                                                                                                                                             |

| 34                 | I/O     | I      | P2[2]           |                                                                              | 47                 | P         | ower                           | V <sub>SS</sub>                  | Ground connection                                                                                                                                                           |

| 35                 | I/O     | I      | P2[4]           |                                                                              | 48                 | IOH       | I                              | P0[1]                            |                                                                                                                                                                             |

| 36                 | I/O     | Ι      | P2[6]           | NC = No Connection H = 5 mA High                                             | СР                 |           | ower                           | V <sub>SS</sub>                  | Center pad must be connected to ground                                                                                                                                      |

Table 7. Pin Definitions – CY8C240093 <sup>[24, 25]</sup>

**LEGEND** A = Analog, I = Input, O = Output, NC = No Connection H = 5 mA High Output Drive, R = Regulated Output.

#### Notes

23.36 GPIOs.

24. This part is available in limited quantities for In-Circuit Debugging during prototype development. It is not available in production volumes.

25. The center pad (CP) on the QFN package must be connected to ground (V<sub>SS</sub>) for best mechanical, thermal, and electrical performance. If not connected to ground, it must be electrically floated and not connected to any other signal.

26. This pin (associated with OCD part only) is required for connecting the device to ICE-Cube In-Circuit Emulator for firmware debugging purpose. To know more about the usage of ICE-Cube, refer to CY3215-DK PSoC<sup>®</sup> IN-CIRCUIT EMULATOR KIT GUIDE.

27. On Power-up, the SDA(P10)] drives a strong high for 256 sleep clock cycles and drives resistive low for the next 256 sleep clock cycles. The SCL(P1[1]) line drives resistive low for 512 sleep clock cycles and both the pins transition to High impedance state. On reset, after XRES de- asserts, the SDA and the SCL lines drive resistive low for 8 sleep clock cycles and transition to high impedance state. In both cases, a pull-up resistance on these lines combines with the pull-down resistance (5.6K ohm) and form a potential divider. Hence, during power-up or reset event, P1[1] and P1[0] may disturb the I2C bus. Use alternate pins if you encounter issues.

28. Alternate SPI clock.

### DC Chip-Level Specifications (CY8C24193/493)

The following table lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

#### Table 10. DC Chip-Level Specifications

| Symbol                              | Description                                   | Conditions                                                                         | Min  | Тур  | Max  | Units |

|-------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------|------|------|------|-------|

| V <sub>DD</sub> <sup>[29, 43]</sup> | Supply voltage                                | See table DC POR and LVD Specifications (CY8C24093/293/393/693) on page 37         | 1.71 | -    | 5.50 | V     |

| I <sub>DD24</sub>                   | Supply current, IMO = 24 MHz                  | Conditions are V <sub>DD</sub> $\leq$ 3.0 V, T <sub>A</sub> = 25 °C, CPU = 24 MHz. | -    | 2.88 | 4.00 | mA    |

| I <sub>DD12</sub>                   | Supply current, IMO = 12 MHz                  | Conditions are V <sub>DD</sub> $\leq$ 3.0 V, T <sub>A</sub> = 25 °C, CPU = 12 MHz. | -    | 1.71 | 2.60 | mA    |

| I <sub>DD6</sub>                    | Supply current, IMO = 6 MHz                   | Conditions are V <sub>DD</sub> $\leq$ 3.0 V, T <sub>A</sub> = 25 °C, CPU = 6 MHz.  | -    | 1.16 | 1.80 | mA    |

| I <sub>SB0</sub>                    | Deep sleep current                            | $V_{DD}\!\leq\!3.0$ V, $T_{A}$ = 25 °C, I/O regulator turned off                   | _    | 0.10 | 1.1  | μΑ    |

| I <sub>SB1</sub>                    | Standby current with POR, LVD and sleep timer | $V_{DD}\!\le\!3.0$ V, $T_A$ = 25 °C, I/O regulator turned off                      | -    | 1.07 | 1.50 | μΑ    |

| I <sub>SBI2C</sub>                  | Standby current with I <sup>2</sup> C enabled | Conditions are V <sub>DD</sub> = 3.3 V, T <sub>A</sub> = 25 °C and CPU = 24 MHz    | -    | 1.64 | _    | μΑ    |

Notes

Notes

29. When V<sub>DD</sub> remains in the range from 1.71 V to 1.9 V for more than 50 µs, the slew rate when moving from the 1.71 V to 1.9 V range to greater than 2 V must be slower than 1 V/500 µs to avoid triggering POR. The only other restriction on slew rates for any other voltage range or transition is the SR<sub>POWER\_UP</sub> parameter.

30. If powering down in standby sleep mode, to properly detect and recover from a V<sub>DD</sub> brown out condition any of the following actions must be taken:

a. Bring the device out of sleep before powering down.

b. Assure that V<sub>DD</sub> falls below 100 mV before powering back up.

c. Set the No Buzz bit in the OSC\_CR0 register to keep the voltage monitoring circuit powered during sleep.

d. Increase the buzz rate to assure that the falling edge of V<sub>DD</sub> is captured. The rate is configured through the PSSDC bits in the SLP\_CFG register. For the referenced registers, refer to the Technical Reference Manual. In deep sleep/standby sleep mode, additional low power voltage monitoring circuitry allows V<sub>DD</sub> brown out conditions to be detected and resets the device when V<sub>DD</sub> goes lower than 1.1 V at edge rates slower than 1 V/ms.

### DC GPIO Specifications (CY8C24093/293/393/693)

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 3.0 V to 5.5 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 2.4 V to 3.0 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 1.71 V to 2.4 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 C and are for design guidance only.

| Symbol                | Description                                                                       | Conditions                                                                                                                                                                                            | Min                    | Тур   | Max  | Units |

|-----------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------|------|-------|

| R <sub>PU</sub>       | Pull-up resistor                                                                  | -                                                                                                                                                                                                     | 4                      | 5.60  | 8    | kΩ    |

| V <sub>OH1</sub>      | High output voltage<br>Port 2 or 3 or 4 pins                                      | $I_{OH} \le 10 \ \mu$ A, maximum of 10 mA source current in all I/Os                                                                                                                                  | V <sub>DD</sub> – 0.20 | -     | -    | V     |

| V <sub>OH2</sub>      | High output voltage<br>Port 2 or 3 or 4 pins                                      | I <sub>OH</sub> = 1 mA, maximum of 20 mA source<br>current in all I/Os                                                                                                                                | V <sub>DD</sub> – 0.90 | -     | _    | V     |

| V <sub>OH3</sub>      | High output voltage<br>Port 0 or 1 pins with LDO regulator<br>Disabled for port 1 | I <sub>OH</sub> < 10 μA, maximum of 10 mA source<br>current in all I/Os                                                                                                                               | V <sub>DD</sub> – 0.20 | -     | -    | V     |

| V <sub>OH4</sub>      | High output voltage<br>Port 0 or 1 pins with LDO regulator<br>Disabled for port 1 | I <sub>OH</sub> = 5 mA, maximum of 20 mA source<br>current in all I/Os                                                                                                                                | V <sub>DD</sub> – 0.90 | -     | -    | V     |

| V <sub>OH5</sub>      | High output voltage<br>Port 1 Pins with LDO Regulator Enabled<br>for 3 V out      | $I_{OH}$ < 10 $\mu$ A, V <sub>DD</sub> > 3.1 V, maximum of 4 I/Os all sourcing 5 mA                                                                                                                   | 2.85                   | 3.00  | 3.30 | V     |

| V <sub>OH6</sub>      | High output voltage<br>Port 1 pins with LDO regulator enabled for<br>3 V out      | $I_{OH}$ = 5 mA, $V_{DD}$ > 3.1 V, maximum of 20 mA source current in all I/Os                                                                                                                        | 2.20                   | -     | -    | V     |

| V <sub>OH7</sub>      | High output voltage<br>Port 1 pins with LDO enabled for 2.5 V out                 | $I_{OH}$ < 10 $\mu$ A, V <sub>DD</sub> > 2.7 V, maximum of 20 mA source current in all I/Os                                                                                                           | 2.35                   | 2.50  | 2.75 | V     |

| V <sub>OH8</sub>      | High output voltage<br>Port 1 pins with LDO enabled for 2.5 V out                 | I <sub>OH</sub> = 2 mA, V <sub>DD</sub> > 2.7 V, maximum of 20 mA<br>source current in all I/Os                                                                                                       | 1.90                   | -     | Ι    | V     |

| V <sub>OH9</sub>      | High output voltage<br>Port 1 pins with LDO enabled for 1.8 V out                 | $I_{OH}$ < 10 $\mu$ A, V <sub>DD</sub> > 2.7 V, maximum of 20 mA source current in all I/Os                                                                                                           | 1.60                   | 1.80  | 2.10 | V     |

| V <sub>OH10</sub>     | High output voltage<br>Port 1 pins with LDO enabled for 1.8 V out                 |                                                                                                                                                                                                       | 1.20                   | -     | -    | V     |

| V <sub>OL</sub>       | Low output voltage                                                                | $I_{OL}$ = 25 mA, $V_{DD}$ > 3.3 V, maximum of<br>60 mA sink current on even port pins (for<br>example, P0[2] and P1[4]) and 60 mA sink<br>current on odd port pins (for example, P0[3]<br>and P1[5]) | _                      | -     | 0.75 | V     |

| V <sub>IL</sub>       | Input low voltage                                                                 | -                                                                                                                                                                                                     | -                      | -     | 0.80 | V     |

| V <sub>IH</sub>       | Input high voltage                                                                | -                                                                                                                                                                                                     | 2.00                   | -     | -    | V     |

| V <sub>H</sub>        | Input hysteresis voltage                                                          | -                                                                                                                                                                                                     | _                      | 80    | I    | mV    |

| IIL                   | Input leakage (Absolute Value)                                                    | -                                                                                                                                                                                                     | _                      | 0.001 | 1    | μΑ    |

| C <sub>PIN</sub>      | Pin capacitance                                                                   | Package and pin dependent<br>Temp = 25 °C                                                                                                                                                             | 0.50                   | 1.70  | 7    | pF    |

| V <sub>ILLVT3.3</sub> | Input Low Voltage with low threshold<br>enable set, Enable for Port1              | Bit3 of IO_CFG1 set to enable low threshold voltage of Port1 input                                                                                                                                    | 0.8                    | V     | -    | -     |

| V <sub>IHLVT3.3</sub> | Input High Voltage with low threshold<br>enable set, Enable for Port1             | Bit3 of IO_CFG1 set to enable low threshold voltage of Port1 input                                                                                                                                    | 1.4                    | 1     |      | V     |

| V <sub>ILLVT5.5</sub> | Input Low Voltage with low threshold<br>enable set, Enable for Port1              | Bit3 of IO_CFG1 set to enable low threshold voltage of Port1 input                                                                                                                                    | 0.8                    | V     | 1    | -     |

| V <sub>IHLVT5.5</sub> | Input High Voltage with low threshold<br>enable set, Enable for Port1             | Bit3 of IO_CFG1 set to enable low threshold voltage of Port1 input                                                                                                                                    | 1.7                    | _     | _    | V     |

## Table 37. 2.4 V to 3.0 V DC GPIO Specifications

| Symbol                | Description                                                                       | Conditions                                                                                                                                                                  | Min                    | Тур  | Max  | Units |

|-----------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------|-------|

| R <sub>PU</sub>       | Pull-up resistor                                                                  | _                                                                                                                                                                           | 4                      | 5.60 | 8    | kΩ    |

| V <sub>OH1</sub>      | High output voltage<br>Port 2 or 3 or 4 pins                                      | I <sub>OH</sub> < 10 μA, maximum of 10 mA source<br>current in all I/Os                                                                                                     | V <sub>DD</sub> – 0.20 | -    | -    | V     |

| V <sub>OH2</sub>      | High output voltage<br>Port 2 or 3 or 4 pins                                      | I <sub>OH</sub> = 0.2 mA, maximum of 10 mA source<br>current in all I/Os                                                                                                    | V <sub>DD</sub> – 0.40 | -    | -    | V     |

| V <sub>OH3</sub>      | High output voltage<br>Port 0 or 1 pins with LDO regulator<br>Disabled for port 1 | I <sub>OH</sub> < 10 μA, maximum of 10 mA source<br>current in all I/Os                                                                                                     | V <sub>DD</sub> – 0.20 | _    | _    | V     |

| V <sub>OH4</sub>      | High output voltage<br>Port 0 or 1 pins with LDO regulator<br>Disabled for Port 1 | I <sub>OH</sub> = 2 mA, maximum of 10 mA source<br>current in all I/Os                                                                                                      | V <sub>DD</sub> – 0.50 | _    | -    | V     |

| V <sub>OH5A</sub>     | High output voltage<br>Port 1 pins with LDO enabled for 1.8 V out                 | I <sub>OH</sub> < 10 μA, V <sub>DD</sub> > 2.4 V, maximum of<br>20 mA source current in all I/Os                                                                            | 1.50                   | 1.80 | 2.10 | V     |

| V <sub>OH6A</sub>     | High output voltage<br>Port 1 pins with LDO enabled for 1.8 V out                 | I <sub>OH</sub> = 1 mA, V <sub>DD</sub> > 2.4 V, maximum of 20 mA source current in all I/Os                                                                                | 1.20                   | -    | -    | V     |

| V <sub>OL</sub>       | Low output voltage                                                                | IOL = 10 mA, maximum of 30 mA sink<br>current on even port pins (for example,<br>P0[2] and P1[4]) and 30 mA sink current on<br>odd port pins (for example, P0[3] and P1[5]) | -                      | _    | 0.75 | V     |

| V <sub>IL</sub>       | Input low voltage                                                                 | _                                                                                                                                                                           | -                      | -    | 0.72 | V     |

| V <sub>IH</sub>       | Input high voltage                                                                | -                                                                                                                                                                           | 1.40                   | _    |      | V     |

| V <sub>H</sub>        | Input hysteresis voltage                                                          | -                                                                                                                                                                           | -                      | 80   | -    | mV    |

| IIL                   | Input leakage (absolute value)                                                    | -                                                                                                                                                                           | -                      | 1    | 1000 | nA    |

| C <sub>PIN</sub>      | Capacitive load on pins                                                           | Package and pin dependent<br>Temp = 25 °C                                                                                                                                   | 0.50                   | 1.70 | 7    | pF    |

| V <sub>ILLVT2.5</sub> | Input Low Voltage with low threshold<br>enable set, Enable for Port1              | Bit3 of IO_CFG1 set to enable low threshold voltage of Port1 input                                                                                                          | 0.7                    | V    | -    |       |

| V <sub>IHLVT2.5</sub> | Input High Voltage with low threshold<br>enable set, Enable for Port1             | Bit3 of IO_CFG1 set to enable low threshold voltage of Port1 input                                                                                                          | 1.2                    |      | -    | V     |

### Table 38. 1.71 V to 2.4 V DC GPIO Specifications

| Symbol           | Description                                                                       | Conditions                                                                                                                                                                         | Min                    | Тур  | Max  | Units |

|------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|------|-------|

| R <sub>PU</sub>  | Pull-up resistor                                                                  | -                                                                                                                                                                                  | 4                      | 5.60 | 8    | kΩ    |

| V <sub>OH1</sub> | High output voltage<br>Port 2 or 3 or 4 pins                                      | I <sub>OH</sub> = 10 μA, maximum of 10 mA source current in all I/Os                                                                                                               | V <sub>DD</sub> – 0.20 | -    | _    | V     |

| V <sub>OH2</sub> | High output voltage<br>Port 2 or 3 or 4 pins                                      | I <sub>OH</sub> = 0.5 mA, maximum of 10 mA source current in all I/Os                                                                                                              | V <sub>DD</sub> – 0.50 | -    | _    | V     |

| V <sub>OH3</sub> | High output voltage<br>Port 0 or 1 pins with LDO regulator<br>Disabled for Port 1 | I <sub>OH</sub> = 100 μA, maximum of 10 mA<br>source current in all I/Os                                                                                                           | V <sub>DD</sub> – 0.20 | -    | _    | V     |

| V <sub>OH4</sub> | High output voltage<br>Port 0 or 1 Pins with LDO Regulator<br>Disabled for Port 1 | I <sub>OH</sub> = 2 mA, maximum of 10 mA source<br>current in all I/Os                                                                                                             | V <sub>DD</sub> – 0.50 | -    | _    | V     |

| V <sub>OL</sub>  | Low output voltage                                                                | $I_{OL}$ = 5 mA, maximum of 20 mA sink<br>current on even port pins (for example,<br>P0[2] and P1[4]) and 30 mA sink<br>current on odd port pins (for example,<br>P0[3] and P1[5]) |                        | -    | 0.40 | V     |

### Comparator User Module Electrical Specifications (CY8C24093/293/393/693)

The following table lists the guaranteed maximum and minimum specifications. Unless stated otherwise, the specifications are for the entire device voltage and temperature operating range: –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 1.71 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V.

Table 42. Comparator User Module Electrical Specifications

| Symbol            | Description              | Conditions                                  | Min | Тур | Max | Units |

|-------------------|--------------------------|---------------------------------------------|-----|-----|-----|-------|

| t <sub>COMP</sub> | Comparator response time | 50 mV overdrive                             | -   | 70  | 100 | ns    |

| Offset            |                          | Valid from 0.2 V to V <sub>DD</sub> – 0.2 V | -   | 2.5 | 30  | mV    |

| Current           |                          | Average DC current, 50 mV<br>overdrive      | -   | 20  | 80  | μA    |

| PSRR              | Supply voltage > 2 V     | Power supply rejection ratio                | -   | 80  | -   | dB    |

| FORK              | Supply voltage < 2 V     | Power supply rejection ratio                | -   | 40  | -   | dB    |

| Input range       |                          | -                                           | 0   |     | 1.5 | V     |

### ADC Electrical Specifications (CY8C24093/293/393/693)

### Table 43. ADC User Module Electrical Specifications

| Symbol              | Description                  | Conditions                                                                                     | Min                       | Тур                       | Max                       | Units |

|---------------------|------------------------------|------------------------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|-------|

| Input               |                              |                                                                                                |                           |                           |                           |       |

| V <sub>IN</sub>     | Input voltage range          | -                                                                                              | 0                         | _                         | VREFADC                   | V     |

| C <sub>IIN</sub>    | Input capacitance            | -                                                                                              | -                         | -                         | 5                         | pF    |

| R <sub>IN</sub>     | Input resistance             | Equivalent switched cap input resistance for 8-, 9-, or 10-bit resolution                      | 1/(500fF ×<br>data clock) | 1/(400fF ×<br>data clock) | 1/(300fF ×<br>data clock) | Ω     |

| Reference           |                              |                                                                                                |                           |                           |                           |       |

| V <sub>REFADC</sub> | ADC reference voltage        | -                                                                                              | 1.14                      | -                         | 1.26                      | V     |

| Conversion F        | Rate                         |                                                                                                | •                         |                           |                           |       |

| F <sub>CLK</sub>    | Data clock                   | Source is chip's internal main<br>oscillator. See AC Chip-Level<br>Specifications for accuracy | 2.25                      | _                         | 6                         | MHz   |

| S8                  | 8-bit sample rate            | Data clock set to 6 MHz. sample<br>rate = 0.001/ (2 <sup>A</sup> Resolution/Data<br>Clock)     | 23.43                     | _                         | ksps                      |       |

| S10                 | 10-bit sample rate           | Data clock set to 6 MHz. sample<br>rate = 0.001/ (2 <sup>resolution</sup> /data<br>clock)      | _                         | 5.85                      | _                         | ksps  |

| DC Accuracy         | /                            |                                                                                                |                           |                           |                           | 1     |

| RES                 | Resolution                   | Can be set to 8-, 9-, or 10-bit                                                                | 8                         | -                         | 10                        | bits  |

| DNL                 | Differential nonlinearity    | -                                                                                              | -1                        | _                         | +2                        | LSB   |

| INL                 | Integral nonlinearity        | -                                                                                              | -2                        | -                         | +2                        | LSB   |

| E <sub>OFFSET</sub> | Offset error                 | 8-bit resolution                                                                               | 0                         | 3.20                      | 19.20                     | LSB   |

|                     |                              | 10-bit resolution                                                                              | 0                         | 12.80                     | 76.80                     | LSB   |

| E <sub>GAIN</sub>   | Gain error                   | For any resolution                                                                             | -5                        | -                         | +5                        | %FSR  |

| Power               | •                            | · ·                                                                                            |                           | •                         | •                         |       |

| I <sub>ADC</sub>    | Operating current            | -                                                                                              | -                         | 2.10                      | 2.60                      | mA    |

| PSRR                | Power supply rejection ratio | PSRR (V <sub>DD</sub> > 3.0 V)                                                                 | -                         | 24                        | -                         | dB    |

|                     |                              | PSRR (V <sub>DD</sub> < 3.0 V)                                                                 | -                         | 30                        | -                         | dB    |

### DC POR and LVD Specifications (CY8C24093/293/393/693)

The following table lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

### Table 44. DC POR and LVD Specifications

| Symbol            | Description                      | Conditions                                                       | Min                  | Тур  | Max  | Units |

|-------------------|----------------------------------|------------------------------------------------------------------|----------------------|------|------|-------|

| V <sub>POR0</sub> | 1.66 V selected in PSoC Designer | $V_{DD}$ must be greater than or equal                           | 1.61                 | 1.66 | 1.71 | V     |

| V <sub>POR1</sub> | 2.36 V selected in PSoC Designer | to 1.71 V during startup, reset from the XRES pin, or reset from | -                    | 2.36 | 2.41 |       |

| V <sub>POR2</sub> | 2.60 V selected in PSoC Designer | watchdog.                                                        | -                    | 2.60 | 2.66 | 1     |

| V <sub>POR3</sub> | 2.82 V selected in PSoC Designer | _                                                                | -                    | 2.82 | 2.95 | 1     |

| V <sub>LVD0</sub> | 2.45 V selected in PSoC Designer | -                                                                | 2.40                 | 2.45 | 2.51 | V     |

| V <sub>LVD1</sub> | 2.71 V selected in PSoC Designer |                                                                  | 2.64 <sup>[46]</sup> | 2.71 | 2.78 |       |

| V <sub>LVD2</sub> | 2.92 V selected in PSoC Designer |                                                                  | 2.85 <sup>[47]</sup> | 2.92 | 2.99 |       |

| V <sub>LVD3</sub> | 3.02 V selected in PSoC Designer |                                                                  | 2.95 <sup>[48]</sup> | 3.02 | 3.09 |       |

| V <sub>LVD4</sub> | 3.13 V selected in PSoC Designer |                                                                  | 3.06                 | 3.13 | 3.20 |       |

| V <sub>LVD5</sub> | 1.90 V selected in PSoC Designer |                                                                  | 1.84                 | 1.90 | 2.32 |       |

| V <sub>LVD6</sub> | 1.80 V selected in PSoC Designer |                                                                  | 1.75 <sup>[49]</sup> | 1.80 | 1.84 | 1     |

| V <sub>LVD7</sub> | 4.73 V selected in PSoC Designer |                                                                  | 4.62                 | 4.73 | 4.83 | 1     |

### DC Programming Specifications (CY8C24093/293/393/693)

The following table lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

### Table 45. DC Programming Specifications

| Symbol                | Description                                                                                       | Conditions                                                                                                                          | Min             | Тур | Max                    | Units |

|-----------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|------------------------|-------|

| V <sub>DDIWRITE</sub> | Supply voltage for flash write operations                                                         | -                                                                                                                                   | 1.71            | -   | 5.25                   | V     |

| I <sub>DDP</sub>      | Supply current during<br>programming or verify                                                    | -                                                                                                                                   | -               | 5   | 25                     | mA    |

| V <sub>ILP</sub>      | Input low voltage during<br>programming or verify                                                 | See the appropriate DC GPIO<br>Specifications (CY8C24093/293/393/693)<br>on page 33                                                 | -               | -   | V <sub>IL</sub>        | V     |

| V <sub>IHP</sub>      | Input high voltage during<br>programming or verify                                                | See the appropriate DC GPIO<br>Specifications (CY8C24093/293/393/693)<br>on page 33                                                 | V <sub>IH</sub> | _   | -                      | V     |

| I <sub>ILP</sub>      | Input current when Applying V <sub>ILP</sub><br>to P1[0] or P1[1] during<br>programming or verify | Driving internal pull-down resistor                                                                                                 | -               | -   | 0.2                    | mA    |

| I <sub>IHP</sub>      | Input current when applying V <sub>IHP</sub><br>to P1[0] or P1[1] during<br>programming or verify | Driving internal pull-down resistor                                                                                                 | -               | -   | 1.5                    | mA    |

| V <sub>OLP</sub>      | Output low voltage during<br>programming or verify                                                |                                                                                                                                     | -               | -   | V <sub>SS</sub> + 0.75 | V     |

| V <sub>OHP</sub>      | Output high voltage during<br>programming or verify                                               | See appropriate DC GPIO Specifications (CY8C24093/293/393/693) on page 33. For $V_{DD}$ > 3 V use $V_{OH4}$ in Table 34 on page 31. | V <sub>OH</sub> | _   | V <sub>DD</sub>        | V     |

| Flash <sub>ENPB</sub> | Flash write endurance                                                                             | Erase/write cycles per block                                                                                                        | 50,000          | _   | -                      | -     |

| Flash <sub>DR</sub>   | Flash data retention                                                                              | Following maximum Flash write cycles;<br>ambient temperature of 55 °C                                                               | 20              | -   | -                      | Years |

#### Notes

- 46. Always greater than 50 mV above V<sub>PPOR1</sub> voltage for falling supply. 47. Always greater than 50 mV above V<sub>PPOR2</sub> voltage for falling supply. 48. Always greater than 50 mV above V<sub>PPOR3</sub> voltage for falling supply. 49. Always greater than 50 mV above V<sub>PPOR0</sub> voltage for falling supply.

## DC I<sup>2</sup>C Specifications (CY8C24093/293/393/693)

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 3.0 V to 5.5 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 2.4 V to 3.0 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 1.71 V to 2.4 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

### Table 46. DC I<sup>2</sup>C Specifications

| Symbol             | Description      | Conditions                                                  | Min                  | Тур | Max                   | Units |

|--------------------|------------------|-------------------------------------------------------------|----------------------|-----|-----------------------|-------|

| V <sub>ILI2C</sub> | Input low level  | $3.1 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}$  | -                    | -   | $0.25 \times V_{DD}$  | V     |

|                    |                  | $2.5 \text{ V} \le \text{V}_{\text{DD}} \le 3.0 \text{ V}$  | _                    | _   | 0.3 × V <sub>DD</sub> | V     |

|                    |                  | $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.4 \text{ V}$ | _                    | _   | 0.3 × V <sub>DD</sub> | V     |

| V <sub>IHI2C</sub> | Input high level | 1.71 V ≤ V <sub>DD</sub> ≤ 5.5 V                            | $0.65 \times V_{DD}$ | _   | _                     | V     |

### DC Reference Buffer Specifications (CY8C24093/293/393/693)

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 3.0 V to 5.5 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, 2.4 V to 3.0 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 1.71 V to 2.4 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

#### Table 47. DC Reference Buffer Specifications

| Symbol             | Description             | Conditions                                                 | Min | Тур | Max  | Units |

|--------------------|-------------------------|------------------------------------------------------------|-----|-----|------|-------|

| V <sub>Ref</sub>   | Reference buffer output | $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}$ | 1   | _   | 1.05 | V     |

| V <sub>RefHi</sub> | Reference buffer output | $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}$ | 1.2 | _   | 1.25 | V     |

### DC IDAC Specifications (CY8C24093/293/393/693)

The following table lists guaranteed maximum and minimum specifications for the entire voltage and temperature ranges.

### Table 48. DC IDAC Specifications

| Symbol    | Description               | Min   | Тур | Max   | Units | Notes                 |

|-----------|---------------------------|-------|-----|-------|-------|-----------------------|

| IDAC_DNL  | Differential nonlinearity | -4.5  | -   | +4.5  | LSB   |                       |

| IDAC_INL  | Integral nonlinearity     | -5    | -   | +5    | LSB   |                       |

| IDAC_Gain | Range = 0.5x              | 6.64  | -   | 22.46 | μA    | DAC setting = 128 dec |

| (Source)  | Range = 1x                | 14.5  | -   | 47.8  | μA    |                       |

|           | Range = 2x                | 42.7  | -   | 92.3  | μA    |                       |

|           | Range = 4x                | 91.1  | -   | 170   | μA    | DAC setting = 128 dec |

|           | Range = 8x                | 184.5 | _   | 426.9 | μA    | DAC setting = 128 dec |

### Table 51. AC Characteristics – USB Data Timings

| Symbol             | Description                                             | Conditions         | Min        | Тур | Max        | Units |

|--------------------|---------------------------------------------------------|--------------------|------------|-----|------------|-------|

| t <sub>DRATE</sub> | Full speed data rate                                    | Average bit rate   | 12 – 0.25% | 12  | 12 + 0.25% | MHz   |

| t <sub>JR1</sub>   | Receiver jitter tolerance                               | To next transition | -18.5      | -   | 18.5       | ns    |

| t <sub>JR2</sub>   | Receiver jitter tolerance                               | To pair transition | -9.0       | _   | 9          | ns    |

| t <sub>DJ1</sub>   | FS Driver jitter                                        | To next transition | -3.5       | -   | 3.5        | ns    |

| t <sub>DJ2</sub>   | FS Driver jitter                                        | To pair transition | -4.0       | -   | 4.0        | ns    |