Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 32MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                        |

| Number of I/O              | 37                                                                     |

| Program Memory Size        | 32KB (32K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 2K x 8                                                                 |

| RAM Size                   | 4K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-UFQFN Exposed Pad                                                   |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l100c6u6a |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

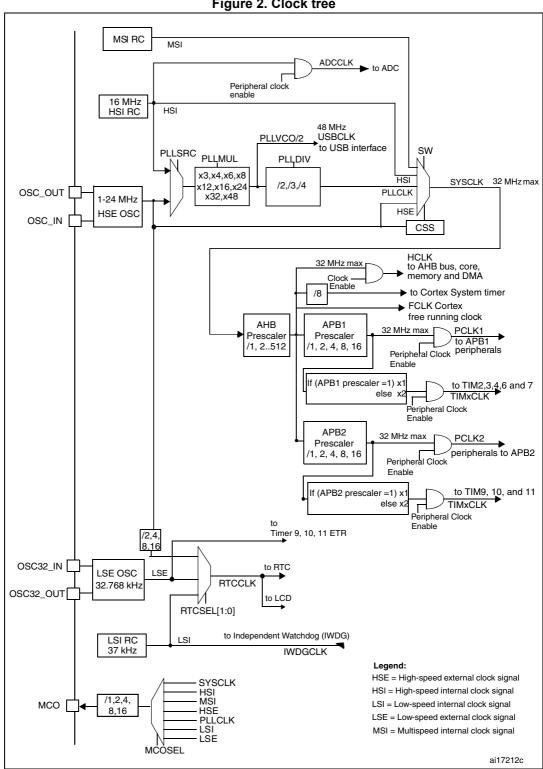

Figure 2. Clock tree

# 3.14 Timers and watchdogs

The ultra-low-power STM32L100x6/8/B-A devices include six general-purpose timers, two basic timers and two watchdog timers.

Table 7 compares the features of the general-purpose and basic timers.

| Timer                  | Counter resolution | Counter<br>type         | Prescaler<br>factor                   | DMA request generation | Capture/compare<br>channels | Complementary<br>outputs |  |  |  |  |

|------------------------|--------------------|-------------------------|---------------------------------------|------------------------|-----------------------------|--------------------------|--|--|--|--|

| TIM2,<br>TIM3,<br>TIM4 | 16-bit             | Up,<br>down,<br>up/down | Any integer<br>between 1<br>and 65536 | Yes                    | 4                           | No                       |  |  |  |  |

| TIM9                   | 16-bit             | Up,<br>down,<br>up/down | Any integer<br>between 1<br>and 65536 | No                     | 2                           | No                       |  |  |  |  |

| TIM10,<br>TIM11        | 16-bit             | Up                      | Any integer<br>between 1<br>and 65536 | No                     | 1                           | No                       |  |  |  |  |

| TIM6,<br>TIM7          | 16-bit             | Up                      | Any integer<br>between 1<br>and 65536 | Yes                    | 0                           | No                       |  |  |  |  |

Table 7. Timer feature comparison

# 3.14.5 Window watchdog (WWDG)

The window watchdog is based on a 7-bit down-counter that can be set as free-running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the main clock. It has an early warning interrupt capability and the counter can be frozen in debug mode.

# 3.15 Communication interfaces

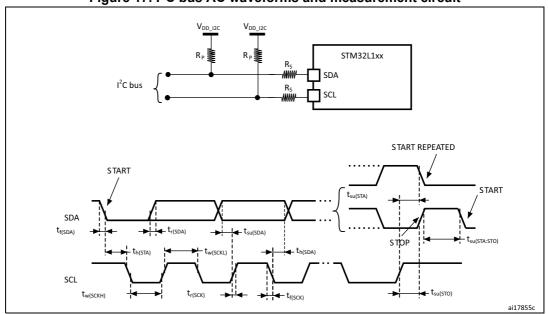

# 3.15.1 I<sup>2</sup>C bus

Up to two I<sup>2</sup>C bus interfaces can operate in multimaster and slave modes. They can support standard and fast modes.

They support dual slave addressing (7-bit only) and both 7- and 10-bit addressing in master mode. A hardware CRC generation/verification is embedded.

They can be served by DMA and they support SM Bus 2.0/PM Bus.

# 3.15.2 Universal synchronous/asynchronous receiver transmitter (USART)

All USART interfaces are able to communicate at speeds of up to 4 Mbit/s. They provide hardware management of the CTS and RTS signals and are ISO 7816 compliant. They support IrDA SIR ENDEC and have LIN Master/Slave capability.

All USART interfaces can be served by the DMA controller.

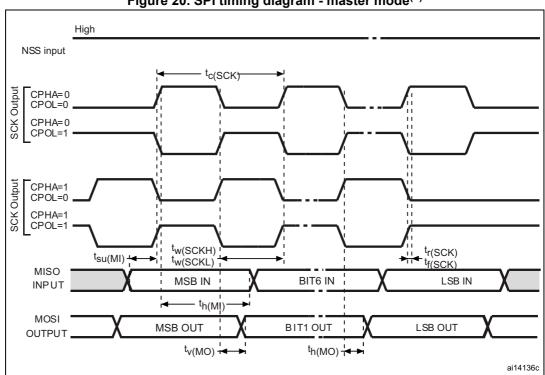

# 3.15.3 Serial peripheral interface (SPI)

Up to two SPIs are able to communicate at up to 16 Mbits/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame is configurable to 8 bits or 16 bits. The hardware CRC generation/verification supports basic SD Card/MMC modes.

Both SPIs can be served by the DMA controller.

# 3.15.4 Universal serial bus (USB)

The STM32L100x6/8/B-A devices embed a USB device peripheral compatible with the USB full speed 12 Mbit/s. The USB interface implements a full speed (12 Mbit/s) function interface. It has software-configurable endpoint setting and supports suspend/resume. The dedicated 48 MHz clock is generated from the internal main PLL (the clock source must use a HSE crystal oscillator).

STM32L100x6/8/B-A

DocID025966 Rev 5

577

37/102

|           |                |                    |          |            |        | Digital alterna | te functior | number         |           |           |        |            |            |          |          |

|-----------|----------------|--------------------|----------|------------|--------|-----------------|-------------|----------------|-----------|-----------|--------|------------|------------|----------|----------|

| Dentmann  | AFIO0          | AFIO1              | AFIO2    | AFIO3      | AFIO4  | AFIO5           | AFOI6       | AFIO7          | AFI<br>O8 | AFI<br>O9 | AFIO11 | AFIO<br>12 | AFIO<br>13 | AFIO14   | AFIO15   |

| Port name |                | Alternate function |          |            |        |                 |             |                |           |           |        |            |            |          |          |

|           | SYSTEM         | TIM2               | TIM3/4   | TIM9/10/11 | I2C1/2 | SPI1/2          | N/A         | USART<br>1/2/3 | N/A       | N/A       | LCD    | N/A        | N/A        | RI       | SYSTEM   |

| BOOT0     | BOOT0          | -                  | -        | -          | -      | -               | -           | -              | -         | -         | -      | -          | -          | -        | -        |

| NRST      | NRST           | -                  | -        | -          | -      | -               | -           | -              | -         | -         | -      | -          | -          | -        | -        |

| PA0-WKUP1 | -              | TIM2_CH1_ETR       | -        | -          | -      | -               | -           | USART2_CTS     | -         | -         | -      | -          | -          | TIMx_IC1 | EVENTOUT |

| PA1       | -              | TIM2_CH2           | -        | -          | -      | -               | -           | USART2_RTS     | -         | -         | [SEG0] | -          | -          | TIMx_IC2 | EVENTOUT |

| PA2       | -              | TIM2_CH3           | -        | TIM9_CH1   | -      | -               | -           | USART2_TX      | -         | -         | [SEG1] | -          | -          | TIMx_IC3 | EVENTOUT |

| PA3       | -              | TIM2_CH4           | -        | TIM9_CH2   | -      | -               | -           | USART2_RX      | -         | -         | [SEG2] | -          | -          | TIMx_IC4 | EVENTOUT |

| PA4       | -              | -                  | -        | -          | -      | SPI1_NSS        | -           | USART2_CK      | -         | -         | -      | -          | -          | TIMx_IC1 | EVENTOUT |

| PA5       | -              | TIM2_CH1_ETR       | -        | -          | -      | SPI1_SCK        | -           | -              | -         | -         | -      | -          | -          | TIMx_IC2 | EVENTOUT |

| PA6       | -              | -                  | TIM3_CH1 | TIM10_CH1  | -      | SPI1_MISO       | -           | -              | -         | -         | [SEG3] | -          | -          | TIMx_IC3 | EVENTOUT |

| PA7       | -              | -                  | TIM3_CH2 | TIM11_CH1  | -      | SPI1_MOSI       | -           | -              | -         | -         | [SEG4] | -          | -          | TIMx_IC4 | EVENTOUT |

| PA8       | МСО            | -                  | -        | -          | -      | -               | -           | USART1_CK      | -         | -         | [COM0] | -          | -          | TIMx_IC1 | EVENTOUT |

| PA9       | -              | -                  | -        | -          | -      | -               | -           | USART1_TX      | -         | -         | [COM1] | -          | -          | TIMx_IC2 | EVENTOUT |

| PA10      | -              | -                  | -        | -          | -      | -               | -           | USART1_RX      | -         | -         | [COM2] | -          | -          | TIMx_IC3 | EVENTOUT |

| PA11      | -              | -                  | -        | -          | -      | SPI1_MISO       | -           | USART1_CTS     | -         | -         | -      | -          | -          | TIMx_IC4 | EVENTOUT |

| PA12      | -              | -                  | -        | -          | -      | SPI1_MOSI       | -           | USART1_RTS     | -         | -         | -      | -          | -          | TIMx_IC1 | EVENTOUT |

| PA13      | JTMS-<br>SWDIO | -                  | -        | -          | -      | -               | -           | -              | -         | -         | -      | -          | -          | TIMx_IC2 | EVENTOUT |

| PA14      | JTCK-<br>SWCLK | -                  | -        | -          | -      | -               | -           | -              | -         | -         | -      | -          | -          | TIMx_IC3 | EVENTOUT |

| PA15      | JTDI           | TIM2_CH1_ETR       | -        | -          | -      | SPI1_NSS        | -           | -              | -         | -         | SEG17  | -          | -          | TIMx_IC4 | EVENTOUT |

| PB0       | -              | -                  | TIM3_CH3 | -          | -      | -               | -           | -              | -         | -         | [SEG5] | -          | -          | -        | EVENTOUT |

| PB1       | -              | -                  | TIM3_CH4 | -          | -      | -               | -           | -              | -         | -         | [SEG6] | -          | -          | -        | EVENTOUT |

| PB2       | BOOT1          | -                  | -        | -          | -      | -               | -           | -              | -         | -         | -      | -          | -          | -        | EVENTOUT |

| PB3       | JTDO           | TIM2_CH2           | -        | -          | -      | SPI1_SCK        | -           | -              | -         | -         | [SEG7] | -          | -          | -        | EVENTOUT |

Table 10. Alternate function input/output

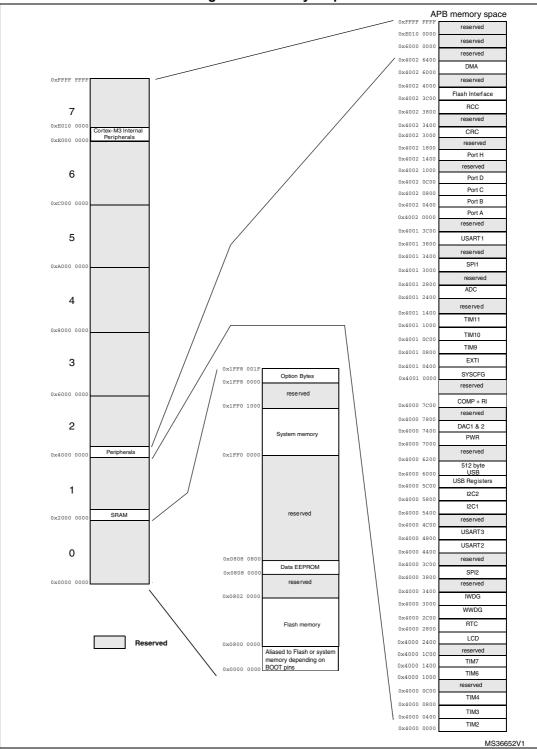

# 5 Memory mapping

The memory map is shown in the following figure.

Figure 5. Memory map

DocID025966 Rev 5

# 6 Electrical characteristics

# 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

## 6.1.1 Minimum and maximum values

Unless otherwise specified the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean $\pm 3\sigma$ ).

Please refer to device ErrataSheet for possible latest changes of electrical characteristics.

# 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 3.0$  V (for the 1.8 V  $\leq V_{DD} \leq 3.6$  V voltage range). They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean $\pm 2\sigma$ ).

### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

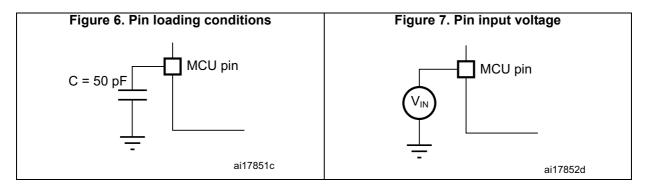

### 6.1.4 Loading capacitor

The loading conditions used for pin parameter measurement are shown in Figure 6.

## 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 7.

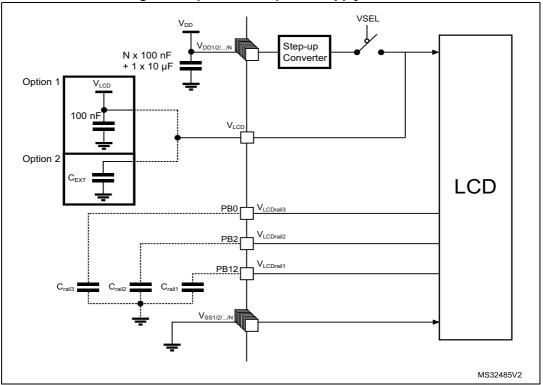

# 6.1.7 Optional LCD power supply scheme

### Figure 9. Optional LCD power supply scheme

- 1. Option 1: LCD power supply is provided by a dedicated VLCD supply source, VSEL switch is open.

- 2. Option 2: LCD power supply is provided by the internal step-up converter, VSEL switch is closed, an external capacitance is needed for correct behavior of this converter.

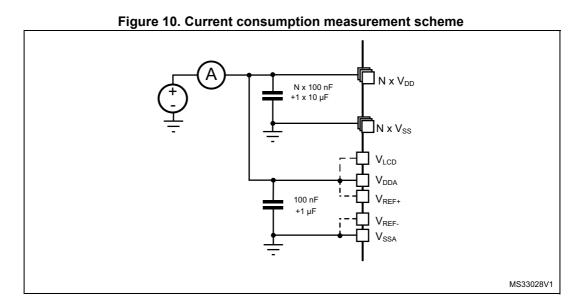

# 6.1.8 Current consumption measurement

# 6.3.4 Supply current characteristics

The current consumption is a function of several parameters and factors such as the operating voltage, ambient temperature, I/O pin loading, device software configuration, operating frequencies, I/O pin switching rate, program location in memory and executed binary code. The current consumption is measured as described in *Figure 10: Current consumption measurement scheme*.

All Run-mode current consumption measurements given in this section are performed with a reduced code that gives a consumption equivalent to Dhrystone 2.1 code, unless otherwise specified.

The current consumption values are derived from the tests performed under ambient temperature  $T_A=25^{\circ}C$  and  $V_{DD}$  supply voltage conditions summarized in *Table 14: General operating conditions*, unless otherwise specified.

The MCU is placed under the following conditions:

- All I/O pins are configured in analog input mode.

- All peripherals are disabled except when explicitly mentioned.

- The Flash memory access time, 64-bit access and prefetch is adjusted depending on f<sub>HCLK</sub> frequency and voltage range to provide the best CPU performance.

- When the peripherals are enabled  $f_{APB1} = f_{APB2} = f_{AHB}$ .

- When PLL is ON, the PLL inputs are equal to HSI = 16 MHz (if internal clock is used) or HSE = 16 MHz (if HSE bypass mode is used).

- The HSE user clock applied to OSC\_IN input follows the characteristics specified in *Table 27: High-speed external user clock characteristics*.

- For maximum current consumption  $V_{DD} = V_{DDA} = 3.6$  V is applied to all supply pins.

- For typical current consumption V<sub>DD</sub> = V<sub>DDA</sub> = 3.0 V is applied to all supply pins if not specified otherwise.

| Symbol               | Parameter  | Cond                                           | litions                                            | f <sub>HCLK</sub> | Тур   | Max <sup>(1)</sup> | Unit |

|----------------------|------------|------------------------------------------------|----------------------------------------------------|-------------------|-------|--------------------|------|

|                      |            |                                                |                                                    | 1 MHz             | 215   | 285                |      |

|                      |            |                                                | Range 3, V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | 2 MHz             | 400   | 490                | μA   |

|                      |            |                                                |                                                    | 4 MHz             | 725   | 1000               |      |

|                      |            | $f_{HSE} = f_{HCLK}$<br>up to 16 MHz, included |                                                    | 4 MHz             | 0.915 | 1.3                |      |

|                      |            | f <sub>HSE</sub> = f <sub>HCLK</sub> /2 above  | Range 2, V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 8 MHz             | 1.75  | 2.15               |      |

| Supply<br>current in | Supply     | 16 MHz<br>(PLL ON) <sup>(2)</sup>              |                                                    | 16 MHz            | 3.4   | 4                  |      |

|                      |            | ( 0)                                           |                                                    | 8 MHz             | 2.1   | 2.9                |      |

| I <sub>DD (Run</sub> | Run mode,  | ode<br>kecuted                                 | Range 1, V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 16 MHz            | 4.2   | 5.2                |      |

| from Flash)          | executed   |                                                |                                                    | 32 MHz            | 8.25  | 9.6                | _    |

|                      | from Flash |                                                | Range 2, V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz            | 3.5   | 4.4                | mA   |

|                      |            |                                                | Range 1, V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz            | 8.2   | 10.2               |      |

|                      |            | MSI clock, 65 kHz                              |                                                    | 65 kHz            | 0.041 | 0.085              |      |

|                      |            | MSI clock, 524 kHz                             | Range 3, V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | 524 kHz           | 0.125 | 0.180              |      |

|                      |            | MSI clock, 4.2 MHz                             |                                                    | 4.2 MHz           | 0.775 | 0.935              |      |

### Table 18. Current consumption in Run mode, code with data processing running from Flash

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register).

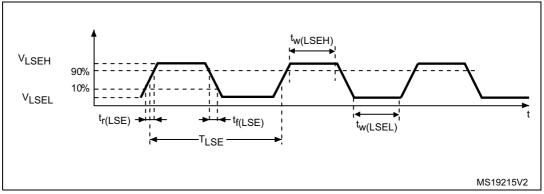

### Low-speed external user clock generated from an external source

The characteristics given in the following table result from tests performed using a lowspeed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 14*.

| Symbol                                       | Parameter                                      | Min                | Тур    | Max                | Unit |

|----------------------------------------------|------------------------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                         | User external clock source frequency           | 1                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage          | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | -    |

| V <sub>LSEL</sub>                            | OSC32_IN input pin low level voltage           | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | -    |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time                      | 465                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | t <sub>r(LSE)</sub> OSC32 IN rise or fall time |                    | -      | 10                 | 115  |

| C <sub>IN(LSE)</sub>                         | OSC32_IN input capacitance                     | -                  | 0.6    | -                  | pF   |

| Table 28. Low-speed external user clock characteristics | -speed external user clock characteristics <sup>(1)</sup> |

|---------------------------------------------------------|-----------------------------------------------------------|

|---------------------------------------------------------|-----------------------------------------------------------|

1. Guaranteed by design.

### Figure 12. Low-speed external clock source AC timing diagram

### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 1 to 24 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 29*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Table 29. HSE os | cillator characteristics <sup>(1)(2)</sup> |

|------------------|--------------------------------------------|

|------------------|--------------------------------------------|

| Symbol              | Parameter            | Conditions | Min Typ |     | Мах | Unit |

|---------------------|----------------------|------------|---------|-----|-----|------|

| f <sub>OSC_IN</sub> | Oscillator frequency | -          | 1       |     | 24  | MHz  |

| R <sub>F</sub>      | Feedback resistor    | -          |         | 200 | -   | kΩ   |

| Symbol                                | Parameter                          | Condition                                | Тур | Max | Unit  |

|---------------------------------------|------------------------------------|------------------------------------------|-----|-----|-------|

|                                       |                                    | MSI range 0                              | -   | 40  |       |

|                                       |                                    | MSI range 1                              | -   | 20  |       |

|                                       |                                    | MSI range 2                              | -   | 10  |       |

|                                       |                                    | MSI range 3                              | -   | 4   |       |

| t <sub>STAB(MSI)</sub> <sup>(2)</sup> | MSI oscillator stabilization time  | MSI range 4                              | -   | 2.5 | 110   |

|                                       |                                    | MSI range 5                              | -   | 2   | μs    |

|                                       |                                    | MSI range 6,<br>Voltage range 1<br>and 2 | -   | 2   |       |

|                                       |                                    | MSI range 3,<br>Voltage Range 3          | -   | 3   |       |

| fourness                              | MSI oscillator frequency overshoot | Any range to range 5                     | -   | 4   | MHz   |

| f <sub>OVER(MSI)</sub>                |                                    | Any range to range 6                     | -   | 6   | IVIHZ |

Table 33. MSI oscillator characteristics (continued)

1. This is a deviation for an individual part, once the initial frequency has been measured.

2. Guaranteed by characterization results.

# 6.3.8 PLL characteristics

The parameters given in *Table 34* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Table 34. | PLL | chara | cteristics |

|-----------|-----|-------|------------|

|-----------|-----|-------|------------|

| Cumhal                 | Devenuetor                                              |     | l l mit                   |       |      |

|------------------------|---------------------------------------------------------|-----|---------------------------|-------|------|

| Symbol                 | Parameter                                               | Min | in Typ Max <sup>(1)</sup> |       | Unit |

| £                      | PLL input clock <sup>(2)</sup>                          | 2   | -                         | 24    | MHz  |

| f <sub>PLL_IN</sub>    | PLL input clock duty cycle                              | 45  | -                         | 55    | %    |

| f <sub>PLL_OUT</sub>   | PLL output clock                                        | 2   | -                         | 32    | MHz  |

| t <sub>LOCK</sub>      | PLL lock time<br>PLL input = 16 MHz<br>PLL VCO = 96 MHz | -   | 115                       | 160   | μs   |

| Jitter                 | Cycle-to-cycle jitter                                   | -   | -                         | ± 600 | ps   |

| I <sub>DDA</sub> (PLL) | DA(PLL) Current consumption on V <sub>DDA</sub>         |     | 220                       | 450   |      |

| I <sub>DD</sub> (PLL)  | Current consumption on $V_{DD}$                         | -   | 120                       | 150   | μA   |

1. Guaranteed by characterization results.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{\mathsf{PLL\_OUT}}$ .

# 6.3.9 Memory characteristics

The characteristics are given at  $T_{\textrm{A}}$  = -40 to 85 °C unless otherwise specified.

### **RAM** memory

| Table | 35. | RAM | and | hardware        | reaisters |

|-------|-----|-----|-----|-----------------|-----------|

| 10010 | ••• |     | ana | indi di di di o | regiotore |

| Symb | ol Par      | ameter                  | Conditions           | Min | Тур | Max | Unit |

|------|-------------|-------------------------|----------------------|-----|-----|-----|------|

| VRM  | Data retent | ion mode <sup>(1)</sup> | STOP mode (or RESET) | 1.8 | -   | -   | V    |

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

### Flash memory and data EEPROM

| Symbol                                                                                        | Parameter                                             | Conditions                                      | Min  | Тур  | Max <sup>(1)</sup> | Unit |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------|------|------|--------------------|------|

| V <sub>DD</sub>                                                                               | Operating voltage<br>Read / Write / Erase             | -                                               | 1.8  | -    | 3.6                | ۷    |

| t <sub>prog</sub> Programming / erasing time for<br>byte / word / double word / half-<br>page | Erasing                                               | -                                               | 3.28 | 3.94 |                    |      |

|                                                                                               | •                                                     | Programming                                     | -    | 3.28 | 3.94               | ms   |

|                                                                                               | Average current during whole program/erase operation  | T - 25 °C V - 3 6 V                             | -    | 300  | -                  | μA   |

| I <sub>DD</sub>                                                                               | Maximum current (peak) during program/erase operation | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -    | 1.5  | 2.5                | mA   |

### Table 36. Flash memory and data EEPROM characteristics

1. Guaranteed by design.

### Table 37. Flash memory, data EEPROM endurance and data retention

| Symbol                          | Parameter                                                                      | Conditions                | Value              |     |     | Unit    |

|---------------------------------|--------------------------------------------------------------------------------|---------------------------|--------------------|-----|-----|---------|

|                                 | Farameter                                                                      | Conditions                | Min <sup>(1)</sup> | Тур | Max | Unit    |

| N <sub>CYC</sub> <sup>(2)</sup> | Cycling (erase / write)<br>Program memory                                      | $T_A = -40^{\circ}C$ to   | 1                  | -   | -   | kovolos |

| N <sub>CYC</sub> <sup>(-)</sup> | Cycling (erase / write)<br>EEPROM data memory                                  | 85 °C                     | 100                | -   | -   | kcycles |

| t <sub>RET</sub> <sup>(2)</sup> | Data retention (program memory) after<br>1 kcycle at T <sub>A</sub> = 85 °C    | T - +85 °C                | 10                 | -   | -   | years   |

|                                 | Data retention (EEPROM data memory) after 100 kcycles at $T_A = 85 \text{ °C}$ | T <sub>RET</sub> = +85 °C | 10                 | -   | -   |         |

1. Guaranteed by characterization results.

2. Characterization is done according to JEDEC JESD22-A117.

57

# 6.3.10 EMC characteristics

Susceptibility tests are performed on a sample basis during the device characterization.

### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 38*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                     | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | $V_{DD}$ = 3.3 V, LQFP100, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-2 | 3B              |

| V <sub>EFTB</sub> | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | $V_{DD} = 3.3$ V, LQFP100, T <sub>A</sub> = +25 °C,<br>f <sub>HCLK</sub> = 32 MHz<br>conforms to IEC 61000-4-4 | 4A              |

### Table 38. EMS characteristics

### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

### Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical data corruption (control registers...)

### Prequalification trials

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the NRST pin or the oscillator pins for 1 second.

### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to  $\pm 8$  mA, and sink or source up to  $\pm 20$  mA (with the non-standard V<sub>OL</sub>/V<sub>OH</sub> specifications given in *Table 44*.

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in *Section 6.2*:

- The sum of the currents sourced by all the I/Os on V<sub>DD</sub>, plus the maximum Run consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 12*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub> plus the maximum Run consumption of the MCU sunk on V<sub>SS</sub> cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 12*).

### **Output voltage levels**

Unless otherwise specified, the parameters given in *Table 44* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*. All I/Os are CMOS and TTL compliant.

| Symbol                            | Parameter                                | Conditions                      | Min                   | Мах  | Unit |

|-----------------------------------|------------------------------------------|---------------------------------|-----------------------|------|------|

| V <sub>OL</sub> <sup>(1)(2)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = 8 mA          | -                     | 0.4  |      |

| V <sub>OH</sub> <sup>(3)(2)</sup> | Output high level voltage for an I/O pin | 2.7 V < V <sub>DD</sub> < 3.6 V | V <sub>DD</sub> -0.4  | -    |      |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = 4 mA          | -                     | 0.45 | v    |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | 1.8 V < V <sub>DD</sub> < 2.7 V | V <sub>DD</sub> -0.45 | -    | v    |

| V <sub>OL</sub> <sup>(1)(4)</sup> | Output low level voltage for an I/O pin  | I <sub>IO</sub> = 20 mA         | -                     | 1.3  |      |

| V <sub>OH</sub> <sup>(3)(4)</sup> | Output high level voltage for an I/O pin | 2.7 V < V <sub>DD</sub> < 3.6 V | V <sub>DD</sub> -1.3  | -    |      |

#### Table 44. Output voltage characteristics

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 12* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. Guaranteed by test in production.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in *Table 12* and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

4. Guaranteed by characterization results.

Figure 17. I<sup>2</sup>C bus AC waveforms and measurement circuit

- 1.  $R_S$  = series protection resistors

- 2.  $R_P$  = pull-up resistors

- 3.  $V_{DD_{12C}} = 12C$  bus supply

- 4. Measurement points are done at CMOS levels: 0.3V<sub>DD</sub> and 0.7V<sub>DD</sub>.

| £ (/,L)_\              | I2C_CCR value           |

|------------------------|-------------------------|

| f <sub>SCL</sub> (kHz) | R <sub>P</sub> = 4.7 kΩ |

| 400                    | 0x801B                  |

| 300                    | 0x8024                  |

| 200                    | 0x8035                  |

| 100                    | 0x00A0                  |

| 50                     | 0x0140                  |

| 20                     | 0x0320                  |

# Table 49. SCL frequency $(f_{PCLK1} = 32 \text{ MHz}, V_{DD} = V_{DD_12C} = 3.3 \text{ V})^{(1)(2)}$

1.  $R_P$  = External pull-up resistance,  $f_{SCL}$  =  $I^2C$  speed.

For speeds around 200 kHz, the tolerance on the achieved speed is of ±5%. For other speed ranges, the tolerance on the achieved speed is ±2%. These variations depend on the accuracy of the external components used to design the application.

### **SPI characteristics**

Unless otherwise specified, the parameters given in the following table are derived from tests performed under ambient temperature,  $f_{PCLKx}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

Refer to Section 6.3.12: I/O current injection characteristics for more details on the input/output alternate function characteristics (NSS, SCK, MOSI, MISO).

| Symbol                                                                     | Parameter                        | Parameter Conditions       |                           | Max <sup>(2)</sup>        | Unit |  |

|----------------------------------------------------------------------------|----------------------------------|----------------------------|---------------------------|---------------------------|------|--|

| _                                                                          |                                  | Master mode                | -                         | 16                        |      |  |

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>                                  | SPI clock frequency              | Slave mode                 | -                         | 16                        | MHz  |  |

|                                                                            |                                  | Slave transmitter          | -                         | 12 <sup>(3)</sup>         |      |  |

| t <sub>r(SCK)</sub> <sup>(2)</sup><br>t <sub>f(SCK)</sub> <sup>(2)</sup>   | SPI clock rise and fall time     | Capacitive load: C = 30 pF | -                         | 6                         | ns   |  |

| DuCy(SCK)                                                                  | SPI slave input clock duty cycle | Slave mode                 | 30                        | 70                        | %    |  |

| t <sub>su(NSS)</sub>                                                       | NSS setup time                   | Slave mode                 | 4t <sub>HCLK</sub>        | -                         |      |  |

| t <sub>h(NSS)</sub>                                                        | NSS hold time                    | Slave mode                 | 2t <sub>HCLK</sub>        | -                         |      |  |

| t <sub>w(SCKH)</sub> <sup>(2)</sup><br>t <sub>w(SCKL)</sub> <sup>(2)</sup> | SCK high and low time            | Master mode                | t <sub>SCK</sub> /2–<br>5 | t <sub>SCK</sub> /2+<br>3 |      |  |

| t <sub>su(MI)</sub> <sup>(2)</sup>                                         | Data input setup time            | Master mode                | 5                         | -                         |      |  |

| t <sub>su(SI)</sub> <sup>(2)</sup>                                         | Data input setup time            | Slave mode                 | 6                         | -                         |      |  |

| t <sub>h(MI)</sub> <sup>(2)</sup>                                          | Data input hold time             | Master mode                | 5                         | -                         | ns   |  |

| t <sub>h(SI)</sub> <sup>(2)</sup>                                          |                                  | Slave mode                 | 5                         | -                         |      |  |

| t <sub>a(SO)</sub> <sup>(4)</sup>                                          | Data output access time          | Slave mode                 | 0                         | 3t <sub>HCLK</sub>        |      |  |

| t <sub>v(SO)</sub> (2)                                                     | Data output valid time           | Slave mode                 | -                         | 33                        |      |  |

| t <sub>v(MO)</sub> <sup>(2)</sup>                                          | Data output valid time           | Master mode                | -                         | 6.5                       |      |  |

| t <sub>h(SO)</sub> <sup>(2)</sup>                                          | Data output hold time            | Slave mode                 | 17                        | -                         |      |  |

| t <sub>h(MO)</sub> <sup>(2)</sup>                                          | Data output hold time            | Master mode                | 0.5                       | -                         |      |  |

| Table 50. SPI characteristics <sup>(1</sup> | I) | ) |

|---------------------------------------------|----|---|

|---------------------------------------------|----|---|

1. The characteristics above are given for voltage Range 1.

2. Guaranteed by characterization results.

3. The maximum SPI clock frequency in slave transmitter mode is given for an SPI slave input clock duty cycle (DuCy(SCK)) ranging between 40 to 60%.

4. Min time is for the minimum time to drive the output and max time is for the maximum time to validate the data.

Figure 20. SPI timing diagram - master mode<sup>(1)</sup>

1. Measurement points are done at CMOS levels:  $0.3V_{\text{DD}}$  and  $0.7V_{\text{DD}}$

### **USB** characteristics

The USB interface is USB-IF certified (full speed).

#### Table 51. USB startup time

| Symbol                              | Symbol Parameter             |   | Unit |

|-------------------------------------|------------------------------|---|------|

| t <sub>STARTUP</sub> <sup>(1)</sup> | USB transceiver startup time | 1 | μs   |

1. Guaranteed by design.

# 6.3.18 DAC electrical specifications

Data guaranteed by design, unless otherwise specified.

| Symbol                          | Parameter                                           | Conditions<br>-                                                            |                                                                            | Min | Тур             | Max                        | Unit  |

|---------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------|-----|-----------------|----------------------------|-------|

| V <sub>DDA</sub>                | Analog supply voltage                               |                                                                            |                                                                            | 1.8 | -               | 3.6                        | V     |

| (4)                             | Current consumption on                              | No load, mid                                                               | No load, middle code (0x800)                                               |     | 330             | 540                        | μA    |

| I <sub>DDA</sub> <sup>(1)</sup> | V <sub>DDA</sub> supply<br>V <sub>DDA</sub> = 3.3 V | No load, wor                                                               | rst code (0xF1C)                                                           | -   | 540             | 870                        | μA    |

| RL                              | Resistive load                                      | DAC output                                                                 | Connected to $\mathrm{V}_{\mathrm{SSA}}$                                   | 5   | -               | -                          | kΩ    |

| • • •                           |                                                     | buffer ON                                                                  | Connected to $V_{DDA}$                                                     | 25  | -               | -                          |       |

| CL                              | Capacitive load                                     | DAC output                                                                 | buffer ON                                                                  | -   | -               | 50                         | pF    |

| R <sub>O</sub>                  | Output impedance                                    | DAC output                                                                 | buffer OFF                                                                 | 12  | 16              | 20                         | kΩ    |

| V                               | Voltage on DAC_OUT                                  | DAC output                                                                 | buffer ON                                                                  | 0.2 | -               | V <sub>DDA</sub> –<br>0.2  | V     |

| V <sub>DAC_OUT</sub>            | output                                              | DAC output buffer OFF                                                      |                                                                            | 0.5 | -               | V <sub>DDA</sub> –<br>1LSB | mV    |

| DNL <sup>(1)</sup>              | Differential non linearity <sup>(2)</sup>           | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON |                                                                            | _   | 1.5             | 3                          |       |

| DITE                            |                                                     | No R <sub>L</sub> , C <sub>L</sub> ≤50 pF<br>DAC output buffer OFF         |                                                                            | -   | 1.5             | 3                          |       |

| INL <sup>(1)</sup>              | Integral non linearity <sup>(3)</sup>               | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON |                                                                            | -   | 2               | 4                          |       |

|                                 |                                                     | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                |                                                                            | -   | 2               | 4                          | LSB   |

| Offset <sup>(1)</sup>           | Offset error at code 0x800 <sup>(4)</sup>           | $C_L \le 50 \text{ pF, F}$<br>DAC output                                   | F, $R_L \ge 5 k\Omega$ but buffer ON                                       |     | ±10             | ±25                        |       |

| Unset 7                         |                                                     | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                |                                                                            | -   | ±5              | ±8                         |       |

| Offset1 <sup>(1)</sup>          | Offset error at code 0x001 <sup>(5)</sup>           | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                |                                                                            | -   | ±1.5            | ±5                         |       |

| dOffset/dT <sup>(1)</sup>       | Offset error temperature                            | $V_{DDA} = 3.3V, T_A = 0$ to 50 ° C<br>DAC output buffer OFF               |                                                                            | -20 | -10             | 0                          | µV/°C |

|                                 | coefficient (code 0x800)                            | V <sub>DDA</sub> = 3.3V<br>DAC output                                      | ′, T <sub>A</sub> = 0 to 50 ° C<br>buffer ON                               | 0   | 20              |                            |       |

| Gain <sup>(1)</sup>             | Gain error <sup>(6)</sup>                           |                                                                            | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON |     | +0.1 /<br>-0.2% | +0.2 / -<br>0.5%           | %     |

|                                 |                                                     | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                |                                                                            | -   | +0 / -<br>0.2%  | +0 / -<br>0.4%             | /0    |

| Table | 58  | DAC | characteristics |

|-------|-----|-----|-----------------|

| Table | 50. | DAO | Characteristics |

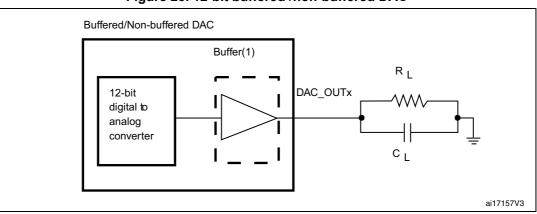

Figure 25. 12-bit buffered /non-buffered DAC

1. The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

# 6.3.19 Comparator

| Symbol                   | Parameter                                                            | Conditions                                                                | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit      |

|--------------------------|----------------------------------------------------------------------|---------------------------------------------------------------------------|--------------------|-----|--------------------|-----------|

| V <sub>DDA</sub>         | Analog supply voltage                                                | -                                                                         | 1.8                |     | 3.6                | V         |

| R <sub>400K</sub>        | R <sub>400K</sub> value                                              | -                                                                         | -                  | 400 | -                  | kΩ        |

| R <sub>10K</sub>         | R <sub>10K</sub> value                                               | -                                                                         | -                  | 10  | -                  | N22       |

| V <sub>IN</sub>          | Comparator 1 input voltage range                                     | -                                                                         | 0.6                | -   | V <sub>DDA</sub>   | V         |

| t <sub>START</sub>       | Comparator startup time                                              | -                                                                         | -                  | 7   | 10                 | 110       |

| td                       | Propagation delay <sup>(2)</sup>                                     | -                                                                         | -                  | 3   | 10                 | μs        |

| Voffset                  | Comparator offset                                                    | -                                                                         | -                  | ±3  | ±10                | mV        |

| d <sub>Voffset</sub> /dt | Comparator offset<br>variation in worst voltage<br>stress conditions | $V_{DDA} = 3.6 V$ $V_{IN+} = 0 V$ $V_{IN-} = V_{REFINT}$ $T_{A} = 25 ° C$ | 0                  | 1.5 | 10                 | mV/1000 h |

| I <sub>COMP1</sub>       | Current consumption <sup>(3)</sup>                                   | -                                                                         | -                  | 160 | 260                | nA        |

Table 59. Comparator 1 characteristics

1. Guaranteed by characterization results.

2. The delay is characterized for 100 mV input step with 10 mV overdrive on the inverting input, the noninverting input set to the reference.

3. Comparator consumption only. Internal reference voltage not included.

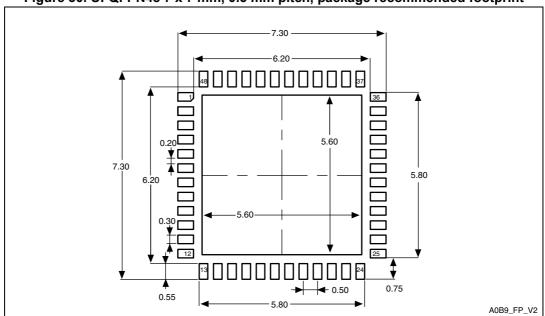

| Symbol | millimeters |       |       | inches <sup>(1)</sup> |        |        |

|--------|-------------|-------|-------|-----------------------|--------|--------|

|        | Min         | Тур   | Мах   | Min                   | Тур    | Max    |

| А      | 0.500       | 0.550 | 0.600 | 0.0197                | 0.0217 | 0.0236 |

| A1     | 0.000       | 0.020 | 0.050 | 0.0000                | 0.0008 | 0.0020 |

| D      | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |

| E      | 6.900       | 7.000 | 7.100 | 0.2717                | 0.2756 | 0.2795 |

| D2     | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |

| E2     | 5.500       | 5.600 | 5.700 | 0.2165                | 0.2205 | 0.2244 |

| L      | 0.300       | 0.400 | 0.500 | 0.0118                | 0.0157 | 0.0197 |

| Т      | -           | 0.152 | -     | -                     | 0.0060 | -      |

| b      | 0.200       | 0.250 | 0.300 | 0.0079                | 0.0098 | 0.0118 |

| е      | -           | 0.500 | -     | -                     | 0.0197 | -      |

| ddd    | -           | -     | 0.080 | -                     | -      | 0.0031 |

Table 63. UFQFPN48 7 x 7 mm, 0.5 mm pitch, package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# Figure 30. UFQFPN48 7 x 7 mm, 0.5 mm pitch, package recommended footprint

1. Dimensions are in millimeters.