Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusActiveCore ProcessorARM@ Cortex@-M3Core Size32-Bit Single-CoreSpeed32MHzConnectivityPC, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, DMA, LCD, POR, PWM, WDTNumber of I/O51Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 20x12b; D/A 2x12bOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP (10x10)     | Details                    |                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed32/HzConnectivityPC, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, DMA, LCD, POR, PWM, WDTNumber of I/O51Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 20x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10) | Product Status             | Active                                                                 |

| Speed32MHzConnectivityI²C, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, DMA, LCD, POR, PWM, WDTNumber of I/O51Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 20x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP (10x10)                                                         | Core Processor             | ARM® Cortex®-M3                                                        |

| ConnectivityIPC, SPI, UART/USART, USBPeripheralsBrown-out Detect/Reset, DMA, LCD, POR, PWM, WDTNumber of I/O51Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 20x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                     | Core Size                  | 32-Bit Single-Core                                                     |

| PeripheralsBrown-out Detect/Reset, DMA, LCD, POR, PWM, WDTNumber of I/O51Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 20x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                          | Speed                      | 32MHz                                                                  |

| Number of I/O51Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 20x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                    | Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                 |

| Program Memory Size128KB (128K x 8)Program Memory TypeFLASHEEPROM Size2K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 20x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP (10x10)                                                                                                                                                                                 | Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                        |

| Program Memory TypeFLASHEEPROM Size2K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 20x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                                                                      | Number of I/O              | 51                                                                     |

| EEPROM Size2K x 8RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 20x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFP (10x10)                                                                                                                                                                                                                                            | Program Memory Size        | 128KB (128K x 8)                                                       |

| RAM Size16K x 8Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 20x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                                                                                                               | Program Memory Type        | FLASH                                                                  |

| Voltage - Supply (Vcc/Vdd)1.8V ~ 3.6VData ConvertersA/D 20x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                                                                                                                              | EEPROM Size                | 2K x 8                                                                 |

| Data ConvertersA/D 20x12b; D/A 2x12bOscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                                                                                                                                                                   | RAM Size                   | 16K x 8                                                                |

| Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10×10)                                                                                                                                                                                                                                                                                                                       | Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                            |

| Operating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                                                                                                                                                                                                                              | Data Converters            | A/D 20x12b; D/A 2x12b                                                  |

| Mounting TypeSurface MountPackage / Case64-LQFPSupplier Device Package64-LQFP (10x10)                                                                                                                                                                                                                                                                                                                                                                                    | Oscillator Type            | Internal                                                               |

| Package / Case     64-LQFP       Supplier Device Package     64-LQFP (10x10)                                                                                                                                                                                                                                                                                                                                                                                             | Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Supplier Device Package     64-LQFP (10x10)                                                                                                                                                                                                                                                                                                                                                                                                                              | Mounting Type              | Surface Mount                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Package / Case             | 64-LQFP                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Supplier Device Package    | 64-LQFP (10x10)                                                        |

| Purchase URL https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l100rbt6a                                                                                                                                                                                                                                                                                                                                                                                      | Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32l100rbt6a |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Contents

| 1 | Intro | duction  |                                                                  | 8    |

|---|-------|----------|------------------------------------------------------------------|------|

| 2 | Desc  | ription  |                                                                  | 9    |

|   | 2.1   | Device   | overview                                                         | . 10 |

|   | 2.2   | Ultra-lo | w-power device continuum                                         | 11   |

|   |       | 2.2.1    | Performance                                                      | 11   |

|   |       | 2.2.2    | Shared peripherals                                               | 11   |

|   |       | 2.2.3    | Common system strategy                                           | 11   |

|   |       | 2.2.4    | Features                                                         | 11   |

| 3 | Fund  | tional o | verview                                                          | . 12 |

|   | 3.1   | Low-po   | wer modes                                                        | . 13 |

|   | 3.2   | ARM®     | Cortex <sup>®</sup> -M3 core with MPU                            | . 17 |

|   | 3.3   | Reset a  | and supply management                                            | . 18 |

|   |       | 3.3.1    | Power supply schemes                                             | 18   |

|   |       | 3.3.2    | Power supply supervisor                                          | 18   |

|   |       | 3.3.3    | Voltage regulator                                                | 19   |

|   |       | 3.3.4    | Boot modes                                                       | 19   |

|   | 3.4   | Clock n  | nanagement                                                       | . 20 |

|   | 3.5   | Low-po   | wer real-time clock and backup registers                         | . 22 |

|   | 3.6   | GPIOs    | (general-purpose inputs/outputs)                                 | . 22 |

|   | 3.7   | Memor    | ies                                                              | . 23 |

|   | 3.8   | DMA (c   | lirect memory access)                                            | . 23 |

|   | 3.9   | LCD (lie | quid crystal display)                                            | . 24 |

|   | 3.10  | ADC (a   | nalog-to-digital converter)                                      | . 24 |

|   |       | 3.10.1   | Internal voltage reference (V <sub>REFINT</sub> )                | 24   |

|   | 3.11  | DAC (d   | igital-to-analog converter)                                      | . 25 |

|   | 3.12  | Ultra-lo | w-power comparators and reference voltage                        | . 25 |

|   | 3.13  | Routing  | g interface                                                      | . 25 |

|   | 3.14  | Timers   | and watchdogs                                                    | . 26 |

|   |       | 3.14.1   | General-purpose timers (TIM2, TIM3, TIM4, TIM9, TIM10 and TIM11) |      |

|   |       | 3.14.2   | Basic timers (TIM6 and TIM7)                                     |      |

|   |       | 3.14.3   | SysTick timer                                                    |      |

|   |       |          |                                                                  |      |

| Table 49.         Table 50.         Table 51.         Table 52.         Table 53.         Table 54.         Table 55.         Table 56.         Table 57.         Table 58.         Table 59.         Table 60.         Table 61.         Table 62. | SCL frequency ( $f_{PCLK1}$ = 32 MHz, $V_{DD}$ = VDD_I2C = 3.3 V).78SPI characteristics79USB startup time.81USB DC electrical characteristics82USB: full speed electrical characteristics82ADC clock frequency83ADC characteristics83ADC accuracy.84Maximum source impedance $R_{AIN}$ max86DAC characteristics87Comparator 1 characteristics89Comparator 2 characteristics90LCD controller characteristics91LQFP64 10 x 10 mm, 64-pin low-profile quad flat package mechanical data.92UEOEDN48 7 x 7 mm0 5 mm pitch package mechanical data.92 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 61.                                                                                                                                                                                                                                           | LCD controller characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Table 62.<br>Table 63.<br>Table 64.<br>Table 65.                                                                                                                                                                                                    | UQFP64 10 X 10 mm, 64-pin low-profile quad flat package mechanical data                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Table 66.                                                                                                                                                                                                                                           | Document revision history                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# 3.1 Low-power modes

The ultra-low-power STM32L100x6/8/B-A devices support dynamic voltage scaling to optimize its power consumption in run mode. The voltage from the internal low-drop regulator that supplies the logic can be adjusted according to the system's maximum operating frequency and the external voltage supply:

- In Range 1 (V<sub>DD</sub> range limited to 2.0-3.6 V), the CPU runs at up to 32 MHz (refer to Table 18 for consumption).

- In Range 2 (full V<sub>DD</sub> range), the CPU runs at up to 16 MHz (refer to *Table 18* for consumption)

- In Range 3 (full V<sub>DD</sub> range), the CPU runs at up to 4 MHz (generated only with the multispeed internal RC oscillator clock source). Refer to *Table 18* for consumption.

Seven low-power modes are provided to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

• Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

Sleep mode power consumption: refer to Table 20.

Low-power Run mode

This mode is achieved with the multispeed internal (MSI) RC oscillator set to the minimum clock (less than 131 kHz), execution from SRAM or Flash memory, and internal regulator in low-power mode to minimize the regulator's operating current. In the low-power Run mode, the clock frequency and the number of enabled peripherals are both limited.

Low-power Run mode consumption: refer to Table 21.

• Low-power Sleep mode

This mode is achieved by entering the Sleep mode with the internal voltage regulator in low-power mode to minimize the regulator's operating current. In the low-power Sleep mode, both the clock frequency and the number of enabled peripherals are limited; a typical example would be to have a timer running at 32 kHz.

When wakeup is triggered by an event or an interrupt, the system reverts to the run mode with the regulator on.

Low-power Sleep mode consumption: refer to *Table 22*.

• Stop mode with RTC

Stop mode achieves the lowest power consumption while retaining the RAM and register contents and real time clock. All clocks in the  $V_{CORE}$  domain are stopped, the PLL, MSI RC, HSI RC and HSE crystal oscillators are disabled. The LSE or LSI is still running. The voltage regulator is in the low-power mode.

The device can be woken up from Stop mode by any of the EXTI line, in 8 µs. The EXTI line source can be one of the 16 external lines. It can be the PVD output, the Comparator 1 event or Comparator 2 event (if internal reference voltage is on), it can be the RTC alarm(s), the USB wakeup, the RTC tamper events, the RTC timestamp event or the RTC wakeup.

Stop mode without RTC

Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, LSE and HSE crystal oscillators are disabled. The voltage regulator is in the low-power mode. The device can be woken up from Stop mode by any of the EXTI line, in 8 µs. The EXTI

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Stop mode, it is possible to automatically switch off the internal reference voltage ( $V_{REFINT}$ ) in Stop mode. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

Note: The start-up time at power-on is typically 3.3 ms.

The device features an embedded programmable voltage detector (PVD) that monitors the  $V_{DD}/V_{DDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD}/V_{DDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD}/V_{DDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

# 3.3.3 Voltage regulator

The regulator has three operation modes: main (MR), low-power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32K osc, RCC\_CSR).

# 3.3.4 Boot modes

At startup, boot pins are used to select one of three boot options:

- Boot from Flash memory

- Boot from System Memory

- Boot from embedded RAM

The boot loader is located in System Memory. It is used to reprogram the Flash memory by using USART1 or USART2. See the application note "STM32 microcontroller system memory boot mode" (AN2606) for details.

# 3.9 LCD (liquid crystal display)

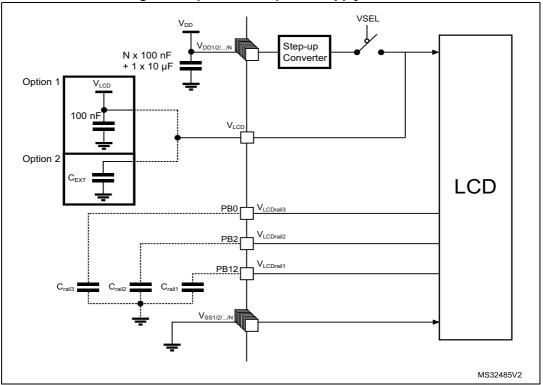

The LCD drives up to 8 common terminals and 32 segment terminals to drive up to 224 pixels.

- Internal step-up converter to guarantee functionality and contrast control irrespective of V<sub>DD</sub>. This converter can be deactivated, in which case the V<sub>LCD</sub> pin is used to provide the voltage to the LCD

- Supports static, 1/2, 1/3, 1/4 and 1/8 duty

- Supports static, 1/2, 1/3 and 1/4 bias

- Phase inversion to reduce power consumption and EMI

- Up to 8 pixels can be programmed to blink

- Unneeded segments and common pins can be used as general I/O pins

- LCD RAM can be updated at any time owing to a double-buffer

- The LCD controller can operate in Stop mode

- V<sub>LCD</sub> rail decoupling capability

|                       |                      | Bias                 |                      |       |

|-----------------------|----------------------|----------------------|----------------------|-------|

|                       |                      | Pin                  |                      |       |

|                       | 1/2                  | 1/3                  | 1/4                  | • ••• |

| V <sub>LCDrail1</sub> | 1/2 V <sub>LCD</sub> | 2/3 V <sub>LCD</sub> | 1/2 V <sub>LCD</sub> | PB2   |

| V <sub>LCDrail2</sub> | NA                   | 1/3 V <sub>LCD</sub> | 1/4 V <sub>LCD</sub> | PB12  |

| V <sub>LCDrail3</sub> | NA                   | NA                   | 3/4 V <sub>LCD</sub> | PB0   |

# Table 6. V<sub>LCD</sub> rail decoupling

# 3.10 ADC (analog-to-digital converter)

A 12-bit analog-to-digital converters is embedded into STM32L100x6/8/B-A devices with up to 20 external channels, performing conversions in single-shot or scan mode. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

The events generated by the general-purpose timers (TIMx) can be internally connected to the ADC start trigger and injection trigger, to allow the application to synchronize A/D conversions and timers. An injection mode allows high priority conversions to be done by interrupting a scan mode which runs in as a background task.

The ADC includes a specific low-power mode. The converter is able to operate at maximum speed even if the CPU is operating at a very low frequency and has an auto-shutdown function. The ADC's runtime and analog front-end current consumption are thus minimized whatever the MCU operating mode.

# 3.10.1 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and Comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. It

| Pi     | ins      |                   |                         |               |                                                  | Pin functions                                 | 5                       |

|--------|----------|-------------------|-------------------------|---------------|--------------------------------------------------|-----------------------------------------------|-------------------------|

| LQFP64 | UFQFPN48 | Pin name          | Pin type <sup>(1)</sup> | I/O structure | Main<br>function <sup>(2)</sup><br>(after reset) | Alternate functions                           | Additional<br>functions |

| 55     | 39       | PB3               | I/O                     | FT            | JTDO                                             | TIM2_CH2/PB3/SPI1_SCK/<br>LCD_SEG7/JTDO       | COMP2_INM               |

| 56     | 40       | PB4               | I/O                     | FT            | NJTRST                                           | TIM3_CH1/PB4/SPI1_MISO/<br>LCD_SEG8/NJTRST    | COMP2_INP               |

| 57     | 41       | PB5               | I/O                     | FT            | PB5                                              | I2C1_SMBA/TIM3_CH2/<br>SPI1_MOSI/LCD_SEG9     | COMP2_INP               |

| 58     | 42       | PB6               | I/O                     | FT            | PB6                                              | I2C1_SCL/TIM4_CH1/<br>USART1_TX               |                         |

| 59     | 43       | PB7               | I/O                     | FT            | PB7                                              | I2C1_SDA/TIM4_CH2<br>/USART1_RX               | PVD_IN                  |

| 60     | 44       | BOOT0             | I                       | В             | BOOT0                                            | -                                             | -                       |

| 61     | 45       | PB8               | I/O                     | FT            | PB8                                              | TIM4_CH3/I2C1_SCL/<br>LCD_SEG16/<br>TIM10_CH1 | -                       |

| 62     | 46       | PB9               | I/O                     | FT            | PB9                                              | TIM4_CH4/I2C1_SDA/<br>LCD_COM3/<br>TIM11_CH1  | -                       |

| 63     | 47       | $V_{SS_3}$        | S                       | -             | V <sub>SS_3</sub>                                | -                                             | -                       |

| 64     | 48       | V <sub>DD_3</sub> | S                       | -             | V <sub>DD_3</sub>                                | _                                             | -                       |

Table 9. STM32L100x6/8/B-A pin definitions (continued)

1. I = input, O = output, S = supply.

Function availability depends on the chosen device. For devices having reduced peripheral counts, it is always the lower number of peripheral that is included. For example, if a device has only one SPI and two USARTs, they will be called SPI1 and USART1 & USART2, respectively. Refer to *Table 2 on page 10*.

The PC14 and PC15 I/Os are only configured as OSC32\_IN/OSC32\_OUT when the LSE oscillator is on (by setting the LSEON bit in the RCC\_CSR register). The LSE oscillator pins OSC32\_IN/OSC32\_OUT can be used as general-purpose PC14/PC15 I/Os, respectively, when the LSE oscillator is off (after reset, the LSE oscillator is off). The LSE has priority over the GPIO function. For more details, refer to Using the OSC32\_IN/OSC32\_OUT pins as GPIO PC14/PC15 port pins section in the STM32L1xxxx reference manual (RM0038).

4. The PH0 and PH1 I/Os are only configured as OSC\_IN/OSC\_OUT when the HSE oscillator is on (by setting the HSEON bit in the RCC\_CR register). The HSE oscillator pins OSC\_IN/OSC\_OUT can be used as general-purpose PH0/PH1 I/Os, respectively, when the HSE oscillator is off (after reset, the HSE oscillator is off). The HSE has priority over the GPIO function.

# 6.1.7 Optional LCD power supply scheme

## Figure 9. Optional LCD power supply scheme

- 1. Option 1: LCD power supply is provided by a dedicated VLCD supply source, VSEL switch is open.

- 2. Option 2: LCD power supply is provided by the internal step-up converter, VSEL switch is closed, an external capacitance is needed for correct behavior of this converter.

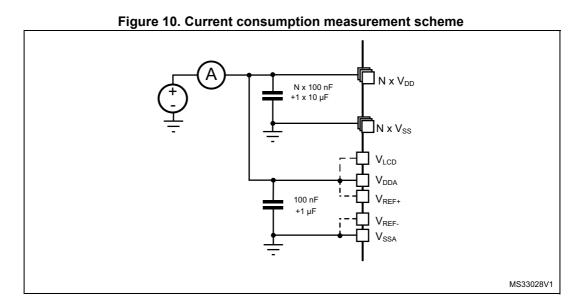

# 6.1.8 Current consumption measurement

4. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_J$  max (see *Table 64: Thermal characteristics on page 98*).

# 6.3.2 Embedded reset and power control block characteristics

The parameters given in the following table are derived from the tests performed under the ambient temperature condition summarized in the following table.

| Symbol                               | Parameter                      | Conditions                          | Min  | Тур  | Max  | Unit |

|--------------------------------------|--------------------------------|-------------------------------------|------|------|------|------|

|                                      | V <sub>DD</sub> rise time rate | BOR detector enabled                | 0    | -    | ∞    |      |

| t <sub>VDD</sub> <sup>(1)</sup>      | V fall time rate               | BOR detector enabled                | 20   | -    | ~    | µs/V |

|                                      | V <sub>DD</sub> fall time rate | BOR detector disabled               | 0    | -    | 1000 |      |

| T <sub>RSTTEMPO</sub> <sup>(1)</sup> | Reset temporization            | V <sub>DD</sub> rising, BOR enabled | -    | 2    | 3.3  | ms   |

| Power on/power down reset            |                                | Falling edge                        | 1    | 1.5  | 1.65 | V    |

| V <sub>POR/PDR</sub>                 | threshold                      | Rising edge                         | 1.3  | 1.5  | 1.65 | V    |

| V <sub>BOR0</sub>                    | Brown-out reset threshold 0    | Falling edge                        | 1.67 | 1.7  | 1.74 |      |

|                                      |                                | Rising edge                         | 1.69 | 1.76 | 1.8  |      |

| M                                    | Brown-out reset threshold 1    | Falling edge                        | 1.87 | 1.93 | 1.97 |      |

| V <sub>BOR1</sub>                    | Brown-out reset threshold T    | Rising edge                         | 1.96 | 2.03 | 2.07 |      |

| M                                    | Brown-out reset threshold 2    | Falling edge                        | 2.22 | 2.30 | 2.35 | V    |

| V <sub>BOR2</sub>                    | BIOWII-OULTESEL LITESHOLU Z    | Rising edge                         | 2.31 | 2.41 | 2.44 | v    |

| M                                    | Brown-out reset threshold 3    | Falling edge                        | 2.45 | 2.55 | 2.60 |      |

| V <sub>BOR3</sub>                    |                                | Rising edge                         | 2.54 | 2.66 | 2.7  |      |

| N .                                  | Brown-out reset threshold 4    | Falling edge                        | 2.68 | 2.8  | 2.85 |      |

| V <sub>BOR4</sub>                    |                                | Rising edge                         | 2.78 | 2.9  | 2.95 |      |

Table 15. Embedded reset and power control block characteristics

| Symbol          | Parameter            | Cond                                                                                                                | litions                                               | f <sub>HCLK</sub> | Тур  | Max <sup>(1)</sup> | Unit |

|-----------------|----------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------|------|--------------------|------|

|                 |                      |                                                                                                                     | Range 3,                                              | 1 MHz             | 50   | 155                |      |

|                 |                      |                                                                                                                     | V <sub>CORE</sub> =1.2 V                              | 2 MHz             | 78.5 | 235                |      |

|                 |                      |                                                                                                                     | VOS[1:0] = 11                                         | 4 MHz             | 140  | 370 <sup>(3)</sup> |      |

|                 |                      | f <sub>HSE</sub> = f <sub>HCLK</sub> up to<br>16 MHz included,                                                      | Range 2,                                              | 4 MHz             | 165  | 375                |      |

|                 |                      | f <sub>HSE</sub> = f <sub>HCLK</sub> /2                                                                             | V <sub>CORE</sub> =1.5 V                              | 8 MHz             | 310  | 530                |      |

|                 |                      | above 16 MHz (PLL ON) <sup>(2)</sup>                                                                                | VOS[1:0] = 10                                         | 16 MHz            | 590  | 1000               |      |

|                 | Quantu               |                                                                                                                     | Range 1,                                              | 8 MHz             | 350  | 615                |      |

|                 | Supply<br>current in |                                                                                                                     | V <sub>CORE</sub> =1.8 V                              | 16 MHz            | 680  | 1200               |      |

|                 | Sleep                |                                                                                                                     | VOS[1:0] = 01                                         | 32 MHz            | 1600 | 2350               | μA   |

|                 | mode,<br>Flash OFF   | HSI clock source                                                                                                    | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz            | 640  | 970                |      |

| I <sub>DD</sub> |                      | (16 MHz)                                                                                                            | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz            | 1600 | 2350               |      |

|                 |                      | MSI clock, 65 kHz                                                                                                   | Range 3,                                              | 65 kHz            | 19   | 60                 |      |

|                 |                      | MSI clock, 524 kHz                                                                                                  | V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11             | 524 kHz           | 33   | 90                 |      |

|                 |                      | MSI clock, 4.2 MHz                                                                                                  |                                                       | 4.2 MHz           | 145  | 210                |      |

| (Sleep)         |                      | $f_{HSE} = f_{HCLK}$ up to<br>16 MHz included,<br>$f_{HSE} = f_{HCLK}/2$<br>above 16 MHz (PLL<br>ON) <sup>(2)</sup> | Range 3,<br>V <sub>CORE</sub> =1.2 V<br>VOS[1:0] = 11 | 1 MHz             | 60.5 | 145                |      |

|                 |                      |                                                                                                                     |                                                       | 2 MHz             | 89.5 | 225                |      |

|                 |                      |                                                                                                                     |                                                       | 4 MHz             | 150  | 360                |      |

|                 |                      |                                                                                                                     | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 4 MHz             | 180  | 370                |      |

|                 |                      |                                                                                                                     |                                                       | 8 MHz             | 320  | 490                |      |

|                 | Supply               |                                                                                                                     |                                                       | 16 MHz            | 605  | 895                |      |

|                 |                      |                                                                                                                     | Range 1,                                              | 8 MHz             | 380  | 565                |      |

|                 | current in           |                                                                                                                     | V <sub>CORE</sub> =1.8 V                              | 16 MHz            | 695  | 1070               |      |

|                 | Sleep                |                                                                                                                     | VOS[1:0] = 01                                         | 32 MHz            | 1600 | 2200               | μA   |

|                 | mode,<br>Flash ON    | HSI clock source                                                                                                    | Range 2,<br>V <sub>CORE</sub> =1.5 V<br>VOS[1:0] = 10 | 16 MHz            | 650  | 970                |      |

|                 |                      | (16 MHz)                                                                                                            | Range 1,<br>V <sub>CORE</sub> =1.8 V<br>VOS[1:0] = 01 | 32 MHz            | 1600 | 2320               |      |

|                 |                      | MSI clock, 65 kHz                                                                                                   | Range 3,                                              | 65 kHz            | 29.5 | 65                 |      |

|                 |                      | MSI clock, 524 kHz                                                                                                  | V <sub>CORE</sub> =1.2V                               | 524 kHz           | 44   | 80                 |      |

|                 |                      | MSI clock, 4.2 MHz                                                                                                  | VOS[1:0] = 11                                         | 4.2 MHz           | 155  | 220                |      |

Table 20. Current consumption in Sleep mode

1. Guaranteed by characterization results, unless otherwise specified.

2. Oscillator bypassed (HSEBYP = 1 in RCC\_CR register)

3. Guaranteed by test in production.

- 1. The typical values are given for  $V_{DD}$  = 3.0 V and max values are given for  $V_{DD}$  = 3.6 V, unless otherwise specified.

- 2. Guaranteed by characterization results, unless otherwise specified.

- 3. LCD enabled with external VLCD, static duty, division ratio = 256, all pixels active, no LCD connected.

- 4. LCD enabled with external VLCD, 1/8 duty, 1/3 bias, division ratio = 64, all pixels active, no LCD connected.

- 5. Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8pF loading capacitors.

- When MSI = 64 kHz, the RMS current is measured over the first 15 μs following the wakeup event. For the remaining time

of the wakeup period, the current is similar to the Run mode current.

| Table 24. Typical and maximum current consumptions in Standby mode |                                                                            |                                                             |                                                             |                    |               |      |  |  |

|--------------------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|--------------------|---------------|------|--|--|

| Symbol                                                             | Parameter                                                                  | Conditions                                                  |                                                             | Тур <sup>(1)</sup> | Max<br>(1)(2) | Unit |  |  |

|                                                                    |                                                                            |                                                             | T <sub>A</sub> = -40 °C to 25 °C<br>V <sub>DD</sub> = 1.8 V | 0.865              | -             |      |  |  |

|                                                                    |                                                                            | RTC clocked by LSI (no                                      | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$                     | 1.11               | 1.9           |      |  |  |

|                                                                    |                                                                            | independent watchdog)                                       | T <sub>A</sub> = 55 °C                                      | 1.15               | 2.2           |      |  |  |

| I <sub>DD</sub>                                                    |                                                                            |                                                             | T <sub>A</sub> = 85 °C                                      | 1.35               | 4             |      |  |  |

|                                                                    |                                                                            |                                                             | T <sub>A</sub> = -40 °C to 25 °C<br>V <sub>DD</sub> = 1.8 V | 0.97               | -             |      |  |  |

|                                                                    |                                                                            | RTC clocked by LSE (no independent watchdog) <sup>(3)</sup> | $T_A = -40 \text{ °C to } 25 \text{ °C}$                    | 1.28               | -             | μA   |  |  |

|                                                                    |                                                                            | independent watchdog)                                       | T <sub>A</sub> = 55 °C                                      | 1.4                | -             | -    |  |  |

|                                                                    |                                                                            |                                                             | T <sub>A</sub> = 85 °C                                      | 1.7                | -             |      |  |  |

|                                                                    |                                                                            | Independent watchdog<br>and LSI enabled                     | $T_A = -40 \text{ °C to } 25 \text{ °C}$                    | 1.0                | 1.7           |      |  |  |

| I <sub>DD</sub>                                                    | Supply current in Standby mode with RTC disabled                           |                                                             | $T_A = -40 \ ^\circ C$ to 25 $^\circ C$                     | 0.277              | 0.6           |      |  |  |

| (Standby)                                                          | mode with RTC disabled                                                     | Independent watchdog<br>and LSI OFF                         | T <sub>A</sub> = 55 °C                                      | 0.31               | 0.9           |      |  |  |

|                                                                    |                                                                            |                                                             | T <sub>A</sub> = 85 °C                                      | 0.52               | 2.75          |      |  |  |

| I <sub>DD (WU</sub><br>from<br>Standby)                            | RMS supply current during<br>wakeup time when exiting<br>from Standby mode | -                                                           | V <sub>DD</sub> = 3.0 V<br>T <sub>A</sub> = -40 °C to 25 °C | 1                  | -             | mA   |  |  |

#### Table 24. Typical and maximum current consumptions in Standby mode

1. The typical values are given for  $V_{DD}$  = 3.0 V and max values are given for  $V_{DD}$  = 3.6 V, unless otherwise specified.

2. Guaranteed by characterization results, unless otherwise specified.

Based on characterization done with a 32.768 kHz crystal (MC306-G-06Q-32.768, manufacturer JFVNY) with two 6.8pF loading capacitors.

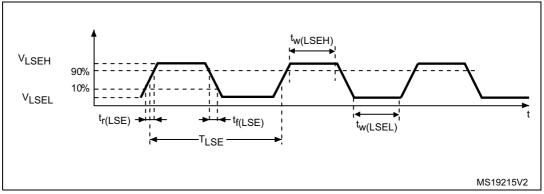

### Low-speed external user clock generated from an external source

The characteristics given in the following table result from tests performed using a lowspeed external clock source, and under ambient temperature and supply voltage conditions summarized in *Table 14*.

| Symbol                                       | Parameter                             | Min                | Тур    | Max                | Unit |

|----------------------------------------------|---------------------------------------|--------------------|--------|--------------------|------|

| f <sub>LSE_ext</sub>                         | User external clock source frequency  | 1                  | 32.768 | 1000               | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage | 0.7V <sub>DD</sub> | -      | V <sub>DD</sub>    | -    |

| V <sub>LSEL</sub>                            | OSC32_IN input pin low level voltage  | V <sub>SS</sub>    | -      | 0.3V <sub>DD</sub> | -    |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time             | 465                | -      | -                  | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | OSC32_IN rise or fall time            | -                  | -      | 10                 | 115  |

| C <sub>IN(LSE)</sub>                         | OSC32_IN input capacitance            | -                  | 0.6    | -                  | pF   |

| Table 28. Low-speed external user clock characteristics | -speed external user clock characteristics <sup>(1)</sup> |

|---------------------------------------------------------|-----------------------------------------------------------|

|---------------------------------------------------------|-----------------------------------------------------------|

1. Guaranteed by design.

#### Figure 12. Low-speed external clock source AC timing diagram

## High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 1 to 24 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on characterization results obtained with typical external components specified in *Table 29*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Table 29. HSE os | cillator characteristics <sup>(1)(2)</sup> |

|------------------|--------------------------------------------|

|------------------|--------------------------------------------|

| Symbol              | Parameter            | Conditions | Min | Тур | Мах | Unit |

|---------------------|----------------------|------------|-----|-----|-----|------|

| f <sub>OSC_IN</sub> | Oscillator frequency | -          | 1   |     | 24  | MHz  |

| R <sub>F</sub>      | Feedback resistor    | -          |     | 200 | -   | kΩ   |

| Symbol                                | Parameter                         | Condition                                | Тур | Max | Unit |

|---------------------------------------|-----------------------------------|------------------------------------------|-----|-----|------|

|                                       |                                   | MSI range 0                              | -   | 40  |      |

|                                       |                                   | MSI range 1                              | -   | 20  |      |

|                                       |                                   | MSI range 2                              | -   | 10  |      |

|                                       |                                   | MSI range 3                              | -   | 4   |      |

| + (2)                                 | MSI oscillator stabilization time | MSI range 4                              | -   | 2.5 | 110  |

| t <sub>STAB(MSI)</sub> <sup>(2)</sup> |                                   | MSI range 5                              | -   | 2   | μs   |

|                                       |                                   | MSI range 6,<br>Voltage range 1<br>and 2 | -   | 2   |      |

|                                       |                                   | MSI range 3,<br>Voltage Range 3          |     | 3   |      |

| fourness                              | Any range to<br>range 5           |                                          | -   | 4   | MHz  |

| f <sub>OVER(MSI)</sub>                |                                   | Any range to range 6                     | -   | - 6 |      |

Table 33. MSI oscillator characteristics (continued)

1. This is a deviation for an individual part, once the initial frequency has been measured.

2. Guaranteed by characterization results.

# 6.3.8 PLL characteristics

The parameters given in *Table 34* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 14*.

| Table 34. | PLL | chara | cteristics |

|-----------|-----|-------|------------|

|-----------|-----|-------|------------|

| Symbol                 | Parameter                                               | Value |     |                    | Unit |

|------------------------|---------------------------------------------------------|-------|-----|--------------------|------|

| Symbol                 | Parameter                                               | Min   | Тур | Max <sup>(1)</sup> | Unit |

| f                      | PLL input clock <sup>(2)</sup>                          | 2     | -   | 24                 | MHz  |

| f <sub>PLL_IN</sub>    | PLL input clock duty cycle                              | 45    | -   | 55                 | %    |

| f <sub>PLL_OUT</sub>   | PLL output clock                                        | 2     | -   | 32                 | MHz  |

| t <sub>LOCK</sub>      | PLL lock time<br>PLL input = 16 MHz<br>PLL VCO = 96 MHz | -     | 115 | 160                | μs   |

| Jitter                 | Cycle-to-cycle jitter                                   | -     | -   | ± 600              | ps   |

| I <sub>DDA</sub> (PLL) | Current consumption on V <sub>DDA</sub>                 | -     | 220 | 450                |      |

| I <sub>DD</sub> (PLL)  | Current consumption on $V_{DD}$                         | -     | 120 | 150                | μA   |

1. Guaranteed by characterization results.

2. Take care of using the appropriate multiplier factors so as to have PLL input clock values compatible with the range defined by  $f_{\mathsf{PLL}\_\mathsf{OUT}}$ .

# 6.3.9 Memory characteristics

The characteristics are given at  $T_{\textrm{A}}$  = -40 to 85 °C unless otherwise specified.

## **RAM** memory

| Table | 35. | RAM | and | hardware        | reaisters |

|-------|-----|-----|-----|-----------------|-----------|

| 10010 | ••• |     | ana | indi di di di o | regiotore |

| Symb | ol Par      | ameter                  | Conditions           | Min | Тур | Max | Unit |

|------|-------------|-------------------------|----------------------|-----|-----|-----|------|

| VRM  | Data retent | ion mode <sup>(1)</sup> | STOP mode (or RESET) | 1.8 | -   | -   | V    |

1. Minimum supply voltage without losing data stored in RAM (in Stop mode or under Reset) or in hardware registers (only in Stop mode).

# Flash memory and data EEPROM

| Symbol            | Parameter                                             | Conditions                                      | Min | Тур  | Max <sup>(1)</sup> | Unit |

|-------------------|-------------------------------------------------------|-------------------------------------------------|-----|------|--------------------|------|

| V <sub>DD</sub>   | Operating voltage<br>Read / Write / Erase             | -                                               | 1.8 | -    | 3.6                | V    |

|                   | Programming / erasing time for                        | Erasing                                         | -   | 3.28 | 3.94               |      |

| t <sub>prog</sub> | byte / word / double word / half-<br>page             | Programming                                     | -   | 3.28 | 3.94               | ms   |

|                   | Average current during whole program/erase operation  | T - 25 °C V - 3 6 V                             | -   | 300  | -                  | μA   |

| I <sub>DD</sub>   | Maximum current (peak) during program/erase operation | T <sub>A</sub> = 25 °C, V <sub>DD</sub> = 3.6 V | -   | 1.5  | 2.5                | mA   |

#### Table 36. Flash memory and data EEPROM characteristics

1. Guaranteed by design.

## Table 37. Flash memory, data EEPROM endurance and data retention

| Symbol                          | Parameter                                                                      | Conditions                | Value              |     |     | Unit    |

|---------------------------------|--------------------------------------------------------------------------------|---------------------------|--------------------|-----|-----|---------|

| Symbol                          | Farameter                                                                      | Conditions                | Min <sup>(1)</sup> | Тур | Мах | Unit    |

| N <sub>CYC</sub> <sup>(2)</sup> | Cycling (erase / write)<br>Program memory                                      | $T_A = -40^{\circ}C$ to   | 1                  | -   | -   | kovolos |

| INCYC Y                         | Cycling (erase / write)<br>EEPROM data memory                                  | 85 °C                     | 100                | -   | -   | kcycles |

| t <sub>RET</sub> <sup>(2)</sup> | Data retention (program memory) after<br>1 kcycle at T <sub>A</sub> = 85 °C    | T - +85 °C                | 10                 | -   | -   | voare   |

| 'RET`                           | Data retention (EEPROM data memory) after 100 kcycles at $T_A = 85 \text{ °C}$ | T <sub>RET</sub> = +85 °C | 10                 | -   | -   | years   |

1. Guaranteed by characterization results.

2. Characterization is done according to JEDEC JESD22-A117.

57

| <b>•</b> • •                   |                                      | <b>a</b>                                                              | <b>Aa:</b> (1)      | · · (1)             |      |  |  |  |

|--------------------------------|--------------------------------------|-----------------------------------------------------------------------|---------------------|---------------------|------|--|--|--|

| Symbol                         | Parameter                            | Conditions                                                            | Min. <sup>(1)</sup> | Max. <sup>(1)</sup> | Unit |  |  |  |

| Input leve                     | Input levels                         |                                                                       |                     |                     |      |  |  |  |

| $V_{DD}$                       | USB operating voltage <sup>(2)</sup> | -                                                                     | 3.0                 | 3.6                 | V    |  |  |  |

| V <sub>DI</sub> <sup>(3)</sup> | Differential input sensitivity       | I(USB_DP, USB_DM)                                                     | 0.2                 | -                   |      |  |  |  |

| V <sub>CM</sub> <sup>(3)</sup> | Differential common mode range       | Includes V <sub>DI</sub> range                                        | 0.8                 | 2.5                 | V    |  |  |  |

| $V_{SE}^{(3)}$                 | Single ended receiver threshold      | -                                                                     | 1.3                 | 2.0                 |      |  |  |  |

| Output le                      | vels                                 |                                                                       |                     |                     |      |  |  |  |

| V <sub>OL</sub> <sup>(4)</sup> | Static output level low              | ${\sf R}_{\sf L}$ of 1.5 k $\Omega$ to 3.6 ${\sf V}^{(5)}$            | -                   | 0.3                 | V    |  |  |  |

| V <sub>OH</sub> <sup>(4)</sup> | Static output level high             | ${\sf R}_{\sf L}$ of 15 ${\sf k}\Omega$ to ${\sf V}_{\sf SS}{}^{(5)}$ | 2.8                 | 3.6                 |      |  |  |  |

|                                |                                      | *                                                                     | •                   |                     |      |  |  |  |

Table 52. USB DC electrical characteristics

1. All the voltages are measured from the local ground potential.

2. To be compliant with the USB 2.0 full speed electrical specification, the USB\_DP (D+) pin should be pulled up with a 1.5 k $\Omega$  resistor to a 3.0-to-3.6 V voltage range.

3. Guaranteed by characterization results.

4. Guaranteed by test in production.

5.  $\ensuremath{\,R_L}$  is the load connected on the USB drivers.

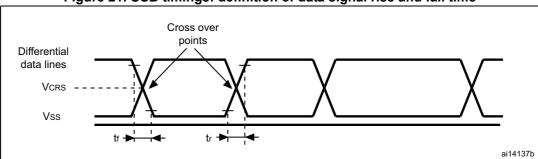

#### Figure 21. USB timings: definition of data signal rise and fall time

## Table 53. USB: full speed electrical characteristics

|                                          | Driver characteristics <sup>(1)</sup> |                                |     |     |    |  |  |  |  |

|------------------------------------------|---------------------------------------|--------------------------------|-----|-----|----|--|--|--|--|

| Symbol Parameter Conditions Min Max Unit |                                       |                                |     |     |    |  |  |  |  |

| t <sub>r</sub>                           | Rise time <sup>(2)</sup>              | C <sub>L</sub> = 50 pF         | 4   | 20  | ns |  |  |  |  |

| t <sub>f</sub>                           | Fall Time <sup>(2)</sup>              | C <sub>L</sub> = 50 pF         | 4   | 20  | ns |  |  |  |  |

| t <sub>rfm</sub>                         | Rise/ fall time matching              | t <sub>r</sub> /t <sub>f</sub> | 90  | 110 | %  |  |  |  |  |

| V <sub>CRS</sub>                         | Output signal crossover voltage       | -                              | 1.3 | 2.0 | V  |  |  |  |  |

1. Guaranteed by design.

2. Measured from 10% to 90% of the data signal. For more detailed informations, please refer to USB Specification section 7 (version 2.0).

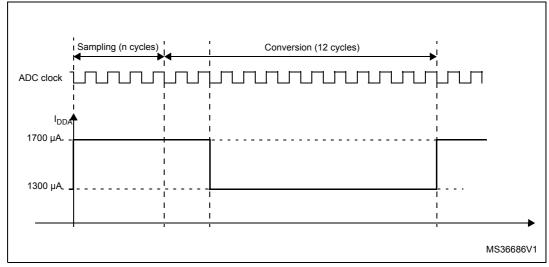

# Figure 24. Maximum dynamic current consumption on V<sub>DDA</sub> supply pin during ADC conversion

# Table 57. Maximum source impedance $R_{AIN} max^{(1)}$

|            |                                                                                                                                                                                                             | R <sub>AIN</sub> max | k (kOhm)                         |             |                                                         |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------------------|-------------|---------------------------------------------------------|

| Ts<br>(µs) | Multiplexe                                                                                                                                                                                                  | d channels           | Direct o                         | hannels     | Ts (cycles)<br>f <sub>ADC</sub> = 16 MHz <sup>(2)</sup> |

|            | $2.4 \text{ V} < \text{V}_{\text{DDA}} < 3.6 \text{ V}  1.8 \text{ V} < \text{V}_{\text{DDA}} < 2.4 \text{ V}  2.4 \text{ V} < \text{V}_{\text{DDA}} < 3.3 \text{ V}  1.8 \text{ V} < \text{V}_{\text{DD}}$ |                      | 1.8 V < V <sub>DDA</sub> < 2.4 V | ADC         |                                                         |

| 0.25       | Not allowed                                                                                                                                                                                                 | Not allowed          | 0.7                              | Not allowed | 4                                                       |

| 0.5625     | 0.8                                                                                                                                                                                                         | Not allowed          | 2.0                              | 1.0         | 9                                                       |

| 1          | 2.0                                                                                                                                                                                                         | 0.8                  | 4.0                              | 3.0         | 16                                                      |

| 1.5        | 3.0                                                                                                                                                                                                         | 1.8                  | 6.0                              | 4.5         | 24                                                      |

| 3          | 6.8                                                                                                                                                                                                         | 4.0                  | 15.0                             | 10.0        | 48                                                      |

| 6          | 15.0                                                                                                                                                                                                        | 10.0                 | 30.0                             | 20.0        | 96                                                      |

| 12         | 32.0                                                                                                                                                                                                        | 25.0                 | 50.0                             | 40.0        | 192                                                     |

| 24         | 50.0                                                                                                                                                                                                        | 50.0                 | 50.0                             | 50.0        | 384                                                     |

1. Guaranteed by design.

2. Number of samples calculated for  $f_{ADC}$  = 16 MHz. For  $f_{ADC}$  = 8 and 4 MHz the number of sampling cycles can be reduced with respect to the minimum sampling time Ts (us).

# General PCB design guidelines

Power supply decoupling should be performed as shown in *Figure 8*. The 100 nF capacitors should be ceramic (good quality). They should be placed as close as possible to the chip.

| Symbol                  | Parameter                                                                                                                                                    | Conditions                                                                  | Min | Тур | Max | Unit    |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----|-----|-----|---------|

| dGain/dT <sup>(1)</sup> | Gain error temperature                                                                                                                                       | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer OFF             | -10 | -2  | 0   | - μV/°C |

| uGaill/uT               | coefficient                                                                                                                                                  | $V_{DDA} = 3.3V$ , $T_A = 0$ to 50 ° C<br>DAC output buffer ON              | -40 | -8  | 0   |         |

| TUE <sup>(1)</sup>      | Total unadjusted error                                                                                                                                       | $C_L \le 50 \text{ pF, } R_L \ge 5 \text{ k}\Omega$<br>DAC output buffer ON | -   | 12  | 30  | - LSB   |

|                         |                                                                                                                                                              | No $R_L$ , $C_L \le 50 \text{ pF}$<br>DAC output buffer OFF                 | -   | 8   | 12  |         |

| t <sub>SETTLING</sub>   | Settling time (full scale: for a<br>12-bit code transition<br>between the lowest and the<br>highest input codes till<br>DAC_OUT reaches final<br>value ±1LSB | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                          | -   | 7   | 12  | μs      |

| Update rate             | Max frequency for a correct<br>DAC_OUT change (95% of<br>final value) with 1 LSB<br>variation in the input code                                              | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                          | -   | -   | 1   | Msps    |

| t <sub>WAKEUP</sub>     | Wakeup time from off state<br>(setting the ENx bit in the<br>DAC Control register) <sup>(7)</sup>                                                            | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                          | -   | 9   | 15  | μs      |

| PSRR+                   | V <sub>DDA</sub> supply rejection ratio<br>(static DC measurement)                                                                                           | $C_L \le 50 \text{ pF}, R_L \ge 5 \text{ k}\Omega$                          | -   | -60 | -35 | dB      |

#### Table 58. DAC characteristics (continued)

1. Guaranteed by characterization results.

2. Difference between two consecutive codes - 1 LSB.

3. Difference between measured value at Code i and the value at Code i on a line drawn between Code 0 and last Code 4095.

- 4. Difference between the value measured at Code (0x800) and the ideal value =  $V_{DDA}/2$ .

- 5. Difference between the value measured at Code (0x001) and the ideal value.

- 6. Difference between ideal slope of the transfer function and measured slope computed from code 0x000 and 0xFFF when buffer is OFF, and from code giving 0.2 V and ( $V_{DDA} 0.2$ ) V when buffer is ON.

- 7. In buffered mode, the output can overshoot above the final value for low input code (starting from min value).

# 7 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

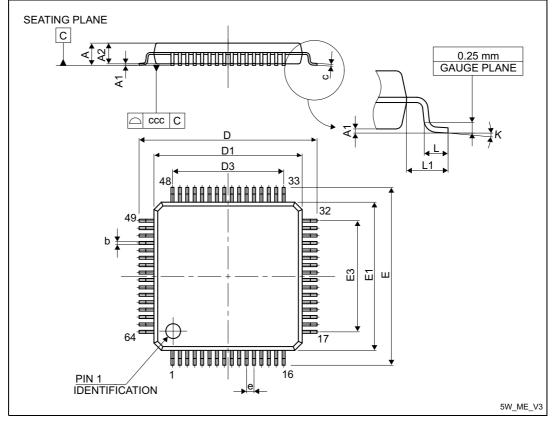

# 7.1 LQFP64 10 x 10 mm, 64-pin low-profile quad flat package information

Figure 26. LQFP64 10 x 10 mm, 64-pin low-profile quad flat package outline

1. Drawing is not to scale.

| Symbol |        |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |

|--------|--------|-------|-------------|-------|--------|-----------------------|--------|--|

|        | Symbol | Min   | Min Typ Max |       | Тур    | Min                   | Max    |  |

|        | А      | -     | -           | 1.600 | -      | -                     | 0.0630 |  |

|        | A1     | 0.050 | -           | 0.150 | 0.0020 | -                     | 0.0059 |  |

|        | A2     | 1.350 | 1.400       | 1.450 | 0.0531 | 0.0551                | 0.0571 |  |

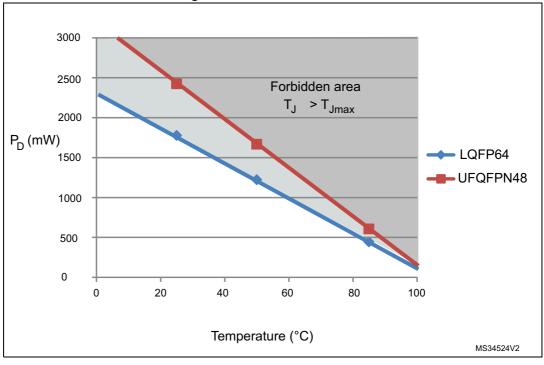

# 7.3 Thermal characteristics

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$T_J \max = T_A \max + (P_D \max \times \Theta_{JA})$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- $\Theta_{JA}$  is the package junction-to-ambient thermal resistance, in ° C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I}/\mathsf{O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma ((\mathsf{V}_{\mathsf{DD}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

Table 64. Thermal characteristics

| Symbol          | Parameter                                                                 | Value | Unit |

|-----------------|---------------------------------------------------------------------------|-------|------|

| Θ <sub>JA</sub> | Thermal resistance junction-ambient<br>LQFP64 - 10 x 10 mm / 0.5 mm pitch | 45    | °C/W |

|                 | Thermal resistance junction-ambient<br>UFQFPN48 - 7 x 7 mm / 0.5 mm pitch | 33    | 0/11 |

#### Figure 32. Thermal resistance

# 9 Revision history

| Table 66. Document revision history |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|-------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|