# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 16MHz                                                                   |

| Connectivity               | I²C, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 23                                                                      |

| Program Memory Size        | 8KB (4K x 16)                                                           |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 32-TQFP                                                                 |

| Supplier Device Package    | 32-TQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega88-15ad |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

In order to maximize performance and parallelism, the AVR<sup>®</sup> uses a Harvard architecture – with separate memories and buses for program and data. Instructions in the program memory are executed with a single level pipelining. While one instruction is being executed, the next instruction is pre-fetched from the program memory. This concept enables instructions to be executed in every clock cycle. The program memory is in-system reprogrammable flash memory.

The fast-access register file contains  $32 \times 8$ -bit general purpose working registers with a single clock cycle access time. This allows single-cycle arithmetic logic unit (ALU) operation. In a typical ALU operation, two operands are output from the register file, the operation is executed, and the result is stored back in the register file – in one clock cycle.

Six of the 32 registers can be used as three 16-bit indirect address register pointers for data space addressing – enabling efficient address calculations. One of the these address pointers can also be used as an address pointer for look up tables in flash program memory. These added function registers are the 16-bit X-, Y-, and Z-register, described later in this section.

The ALU supports arithmetic and logic operations between registers or between a constant and a register. Single register operations can also be executed in the ALU. After an arithmetic operation, the status register is updated to reflect information about the result of the operation.

Program flow is provided by conditional and unconditional jump and call instructions, able to directly address the whole address space. Most AVR instructions have a single 16-bit word format. Every program memory address contains a 16- or 32-bit instruction.

Program flash memory space is divided in two sections, the boot program section and the application program section. Both sections have dedicated lock bits for write and read/write protection. The SPM instruction that writes into the application flash memory section must reside in the boot program section.

During interrupts and subroutine calls, the return address program counter (PC) is stored on the stack. The stack is effectively allocated in the general data SRAM, and consequently the stack size is only limited by the total SRAM size and the usage of the SRAM. All user programs must initialize the SP in the reset routine (before subroutines or interrupts are executed). The stack pointer (SP) is read/write accessible in the I/O space. The data SRAM can easily be accessed through the five different addressing modes supported in the AVR architecture.

The memory spaces in the AVR architecture are all linear and regular memory maps.

A flexible interrupt module has its control registers in the I/O space with an additional global interrupt enable bit in the status register. All interrupts have a separate interrupt vector in the interrupt vector table. The interrupts have priority in accordance with their interrupt vector position. The lower the interrupt vector address, the higher the priority.

The I/O memory space contains 64 addresses for CPU peripheral functions as control registers, SPI, and other I/O functions. The I/O memory can be accessed directly, or as the data space locations following those of the register file, 0x20 - 0x5F. In addition, the ATmega88/168 has extended I/O space from 0x60 - 0xFF in SRAM where only the ST/STS/STD and LD/LDS/LDD instructions can be used.

# 4.3 ALU – Arithmetic Logic Unit

The high-performance AVR ALU operates in direct connection with all the 32 general purpose working registers. Within a single clock cycle, arithmetic operations between general purpose registers or between a register and an immediate are executed. The ALU operations are divided into three main categories – arithmetic, logical, and bit-functions. Some implementations of the architecture also provide a powerful multiplier supporting both signed/unsigned multiplication and fractional format. See the "Instruction Set" section for a detailed description.

The CKSEL0 fuse together with the SUT1..0 fuses select the start-up times as shown in Table 6-4.

| Oscillator Source / Power<br>Conditions | Start-up Time from Power-<br>down and Power-save | Additional Delay from<br>Reset (V <sub>CC</sub> = 5.0V) | CKSEL0 | SUT10 |

|-----------------------------------------|--------------------------------------------------|---------------------------------------------------------|--------|-------|

| Ceramic resonator, fast rising power    | 258CK                                            | 14CK + 4.1ms <sup>(1)</sup>                             | 0      | 00    |

| Ceramic resonator, slowly rising power  | 258CK                                            | 14CK + 65ms <sup>(1)</sup>                              | 0      | 01    |

| Ceramic resonator, BOD enabled          | 1KCK                                             | 14CK <sup>(2)</sup>                                     | 0      | 10    |

| Ceramic resonator, fast rising power    | 1KCK                                             | 14CK + 4.1ms <sup>(2)</sup>                             | 0      | 11    |

| Ceramic resonator, slowly rising power  | 1KCK                                             | 14CK + 65ms <sup>(2)</sup>                              | 1      | 00    |

| Crystal oscillator, BOD enabled         | 16KCK                                            | 14CK                                                    | 1      | 01    |

| Crystal oscillator, fast rising power   | 16KCK                                            | 14CK + 4.1ms                                            | 1      | 10    |

| Crystal oscillator, slowly rising power | 16KCK                                            | 14CK + 65ms                                             | 1      | 11    |

Table 6-4. Start-up Times for the Low Power Crystal Oscillator Clock Selection

Notes: 1. These options should only be used when not operating close to the maximum frequency of the device, and only if frequency stability at start-up is not important for the application. These options are not suitable for crystals.

2. These options are intended for use with ceramic resonators and will ensure frequency stability at start-up. They can also be used with crystals when not operating close to the maximum frequency of the device, and if frequency stability at start-up is not important for the application.

# 6.4 Full Swing Crystal Oscillator

Pins XTAL1 and XTAL2 are input and output, respectively, of an inverting amplifier which can be configured for use as an on-chip oscillator, as shown in Figure 6-2 on page 25. Either a quartz crystal or a ceramic resonator may be used.

This crystal oscillator is a full swing oscillator, with rail-to-rail swing on the XTAL2 output. This is useful for driving other clock inputs and in noisy environments. The current consumption is higher than the Section 6.3 "Low Power Crystal Oscillator" on page 25. Note that the full swing crystal oscillator will only operate for  $V_{CC}$  = 2.7 to 5.5V.

C1 and C2 should always be equal for both crystals and resonators. The optimal value of the capacitors depends on the crystal or resonator in use, the amount of stray capacitance, and the electromagnetic noise of the environment. Some initial guidelines for choosing capacitors for use with crystals are given in Table 6-6 on page 27. For ceramic resonators, the capacitor values given by the manufacturer should be used.

The operating mode is selected by the fuses CKSEL3..1 as shown in Table 6-5.

#### Table 6-5. Full Swing Crystal Oscillator operating modes<sup>(2)</sup>

| Frequency Range <sup>(1)</sup> (MHz)                                           | CKSEL31 | Recommended Range for Capacitors C1 and C2 (pF) |  |  |  |  |

|--------------------------------------------------------------------------------|---------|-------------------------------------------------|--|--|--|--|

| 0.4 - 20                                                                       | 011     | 12 - 22                                         |  |  |  |  |

| Notes 1. The frequency represents an inclusion visities. Actual values are TRD |         |                                                 |  |  |  |  |

Notes: 1. The frequency ranges are preliminary values. Actual values are TBD.

If 8MHz frequency exceeds the specification of the device (depends on V<sub>CC</sub>), the CKDIV8 fuse can be

programmed in order to divide the internal frequency by 8. It must be ensured that the resulting divided clock

meets the frequency specification of the device.

# 14.6.2 Compare Match Blocking by TCNT1 Write

All CPU writes to the TCNT1 register will block any compare match that occurs in the next timer clock cycle, even when the timer is stopped. This feature allows OCR1x to be initialized to the same value as TCNT1 without triggering an interrupt when the Timer/Counter clock is enabled.

# 14.6.3 Using the Output Compare Unit

Since writing TCNT1 in any mode of operation will block all compare matches for one timer clock cycle, there are risks involved when changing TCNT1 when using any of the output compare channels, independent of whether the Timer/Counter is running or not. If the value written to TCNT1 equals the OCR1x value, the compare match will be missed, resulting in incorrect waveform generation. Do not write the TCNT1 equal to TOP in PWM modes with variable TOP values. The compare match for the TOP will be ignored and the counter will continue to 0xFFFF. Similarly, do not write the TCNT1 value equal to BOTTOM when the counter is downcounting.

The setup of the OC1x should be performed before setting the data direction register for the port pin to output. The easiest way of setting the OC1x value is to use the force output compare (FOC1x) strobe bits in normal mode. The OC1x register keeps its value even when changing between waveform generation modes.

Be aware that the COM1x1:0 bits are not double buffered together with the compare value. Changing the COM1x1:0 bits will take effect immediately.

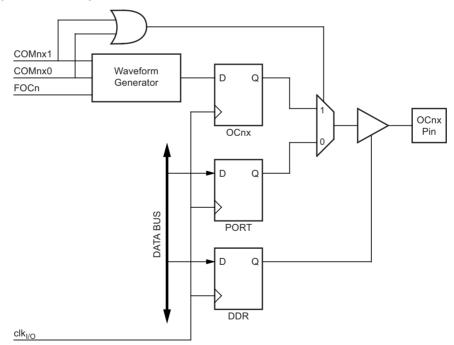

# 14.7 Compare Match Output Unit

The compare output mode (COM1x1:0) bits have two functions. The waveform generator uses the COM1x1:0 bits for defining the output compare (OC1x) state at the next compare match. Secondly the COM1x1:0 bits control the OC1x pin output source. Figure 14-5 shows a simplified schematic of the logic affected by the COM1x1:0 bit setting. The I/O registers, I/O bits, and I/O pins in the figure are shown in bold. Only the parts of the general I/O port control registers (DDR and PORT) that are affected by the COM1x1:0 bits are shown. When referring to the OC1x state, the reference is for the internal OC1x register, not the OC1x pin. If a system reset occur, the OC1x register is reset to "0".

#### Figure 14-5. Compare Match Output Unit, Schematic

The general I/O port function is overridden by the output compare (OC1x) from the waveform generator if either of the COM1x1:0 bits are set. However, the OC1x pin direction (input or output) is still controlled by the data direction register (DDR) for the port pin. The data direction register bit for the OC1x pin (DDR\_OC1x) must be set as output before the OC1x value is visible on the pin. The port override function is generally independent of the waveform generation mode, but there are some exceptions. Refer to Table 14-2 on page 111, Table 14-3 on page 112 and Table 14-4 on page 112 for details.

The design of the output compare pin logic allows initialization of the OC1x state before the output is enabled. Note that some COM1x1:0 bit settings are reserved for certain modes of operation. See Section 14.10 "16-bit Timer/Counter Register Description" on page 111

The COM1x1:0 bits have no effect on the input capture unit.

# 14.7.1 Compare Output Mode and Waveform Generation

The waveform generator uses the COM1x1:0 bits differently in normal, CTC, and PWM modes. For all modes, setting the COM1x1:0 = 0 tells the waveform generator that no action on the OC1x register is to be performed on the next compare match. For compare output actions in the non-PWM modes refer to Table 14-2 on page 111. For fast PWM mode refer to Table 14-3 on page 112, and for phase correct and phase and frequency correct PWM refer to Table 14-4 on page 112.

A change of the COM1x1:0 bits state will have effect at the first compare match after the bits are written. For non-PWM modes, the action can be forced to have immediate effect by using the FOC1x strobe bits.

# 14.8 Modes of Operation

The mode of operation, i.e., the behavior of the Timer/Counter and the output compare pins, is defined by the combination of the waveform generation mode (WGM13:0) and compare output mode (COM1x1:0) bits. The compare output mode bits do not affect the counting sequence, while the waveform generation mode bits do. The COM1x1:0 bits control whether the PWM output generated should be inverted or not (inverted or non-inverted PWM). For non-PWM modes the COM1x1:0 bits control whether the output should be set, cleared or toggle at a compare match (see Section 14.7 "Compare Match Output Unit" on page 102)

For detailed timing information refer to Section 14.9 "Timer/Counter Timing Diagrams" on page 109.

# 14.8.1 Normal Mode

The simplest mode of operation is the normal mode (WGM13:0 = 0). In this mode the counting direction is always up (incrementing), and no counter clear is performed. The counter simply overruns when it passes its maximum 16-bit value (MAX = 0xFFF) and then restarts from the BOTTOM (0x0000). In normal operation the Timer/Counter overflow flag (TOV1) will be set in the same timer clock cycle as the TCNT1 becomes zero. The TOV1 flag in this case behaves like a 17th bit, except that it is only set, not cleared. However, combined with the timer overflow interrupt that automatically clears the TOV1 flag, the timer resolution can be increased by software. There are no special cases to consider in the normal mode, a new counter value can be written anytime.

The input capture unit is easy to use in normal mode. However, observe that the maximum interval between the external events must not exceed the resolution of the counter. If the interval between events are too long, the timer overflow interrupt or the prescaler must be used to extend the resolution for the capture unit.

The output compare units can be used to generate interrupts at some given time. Using the output compare to generate waveforms in normal mode is not recommended, since this will occupy too much of the CPU time.

# 14.8.2 Clear Timer on Compare Match (CTC) Mode

In clear timer on compare or CTC mode (WGM13:0 = 4 or 12), the OCR1A or ICR1 register are used to manipulate the counter resolution. In CTC mode the counter is cleared to zero when the counter value (TCNT1) matches either the OCR1A (WGM13:0 = 4) or the ICR1 (WGM13:0 = 12). The OCR1A or ICR1 define the top value for the counter, hence also its resolution. This mode allows greater control of the compare match output frequency. It also simplifies the operation of counting external events.

The timing diagram for the CTC mode is shown in Figure 14-6 on page 104. The counter value (TCNT1) increases until a compare match occurs with either OCR1A or ICR1, and then counter (TCNT1) is cleared.

# 15.9 Asynchronous operation of the Timer/Counter

# 15.9.1 Asynchronous Operation of Timer/Counter2

When Timer/Counter2 operates asynchronously, some considerations must be taken.

- Warning: When switching between asynchronous and synchronous clocking of Timer/Counter2, the timer registers TCNT2, OCR2x, and TCCR2x might be corrupted. A safe procedure for switching clock source is:

- a. Disable the Timer/Counter2 interrupts by clearing OCIE2x and TOIE2.

- b. Select clock source by setting AS2 as appropriate.

- c. Write new values to TCNT2, OCR2x, and TCCR2x.

- d. To switch to asynchronous operation: Wait for TCN2xUB, OCR2xUB, and TCR2xUB.

- e. Clear the Timer/Counter2 interrupt flags.

- f. Enable interrupts, if needed.

- The CPU main clock frequency must be more than four times the oscillator frequency.

- When writing to one of the registers TCNT2, OCR2x, or TCCR2x, the value is transferred to a temporary register, and latched after two positive edges on TOSC1. The user should not write a new value before the contents of the temporary register have been transferred to its destination. Each of the five mentioned registers have their individual temporary register, which means that e.g. writing to TCNT2 does not disturb an OCR2x write in progress. To detect that a transfer to the destination register has taken place, the asynchronous status register – ASSR has been implemented.

- When entering power-save or ADC noise reduction mode after having written to TCNT2, OCR2x, or TCCR2x, the user must wait until the written register has been updated if Timer/Counter2 is used to wake up the device. Otherwise, the MCU will enter sleep mode before the changes are effective. This is particularly important if any of the output compare2 interrupt is used to wake up the device, since the output compare function is disabled during writing to OCR2x or TCNT2. If the write cycle is not finished, and the MCU enters sleep mode before the corresponding OCR2xUB bit returns to zero, the device will never receive a compare match interrupt, and the MCU will not wake up.

- If Timer/Counter2 is used to wake the device up from power-save or ADC noise reduction mode, precautions must be

taken if the user wants to re-enter one of these modes: The interrupt logic needs one TOSC1 cycle to be reset. If the

time between wake-up and re-entering sleep mode is less than one TOSC1 cycle, the interrupt will not occur, and the

device will fail to wake up. If the user is in doubt whether the time before re-entering power-save or ADC noise

reduction mode is sufficient, the following algorithm can be used to ensure that one TOSC1 cycle has elapsed:

- a. Write a value to TCCR2x, TCNT2, or OCR2x.

- b. Wait until the corresponding update busy flag in ASSR returns to zero.

- c. Enter power-save or ADC noise reduction mode.

- When the asynchronous operation is selected, the 32.768kHz oscillator for Timer/Counter2 is always running, except in power-down and standby modes. After a power-up reset or wake-up from power-down or standby mode, the user should be aware of the fact that this oscillator might take as long as one second to stabilize. The user is advised to wait for at least one second before using Timer/Counter2 after power-up or wake-up from power-down or standby mode. The contents of all Timer/Counter2 registers must be considered lost after a wake-up from power-down or standby mode due to unstable clock signal upon start-up, no matter whether the oscillator is in use or a clock signal is applied to the TOSC1 pin.

- Description of wake up from power-save or ADC noise reduction mode when the timer is clocked asynchronously: When the interrupt condition is met, the wake up process is started on the following cycle of the timer clock, that is, the timer is always advanced by at least one before the processor can read the counter value. After wake-up, the MCU is halted for four cycles, it executes the interrupt routine, and resumes execution from the instruction following SLEEP.

# • Bit 5..1 - Res: Reserved Bits

These bits are reserved bits in the Atmel® ATmega88/168 and will always read as zero.

#### • Bit 0 - SPI2X: Double SPI Speed Bit

When this bit is written logic one the SPI speed (SCK frequency) will be doubled when the SPI is in master mode (see Table 16-4 on page 141). This means that the minimum SCK period will be two CPU clock periods. When the SPI is configured as Slave, the SPI is only guaranteed to work at  $f_{osc}/4$  or lower.

The SPI interface on the Atmel ATmega88/168 is also used for program memory and EEPROM downloading or uploading. See Section 24.8 "Serial Downloading" on page 248 for serial programming and verification.

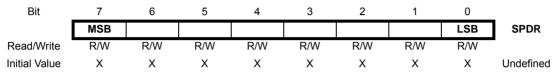

#### 16.1.5 SPI Data Register – SPDR

The SPI data register is a read/write register used for data transfer between the register file and the SPI shift register. Writing to the register initiates data transmission. Reading the register causes the shift register receive buffer to be read.

# 16.2 Data Modes

There are four combinations of SCK phase and polarity with respect to serial data, which are determined by control bits CPHA and CPOL. The SPI data transfer formats are shown in Figure 16-3 on page 143 and Figure 16-4 on page 143. Data bits are shifted out and latched in on opposite edges of the SCK signal, ensuring sufficient time for data signals to stabilize. This is clearly seen by summarizing Figure 16-2 on page 140 and Table 16-3 on page 141, as done below.

|                | Leading Edge     | Trailing eDge    | SPI Mode |

|----------------|------------------|------------------|----------|

| CPOL=0, CPHA=0 | Sample (rising)  | Setup (falling)  | 0        |

| CPOL=0, CPHA=1 | Setup (rising)   | Sample (falling) | 1        |

| CPOL=1, CPHA=0 | Sample (falling) | Setup (rising)   | 2        |

| CPOL=1, CPHA=1 | Setup (falling)  | Sample (rising)  | 3        |

#### Table 16-5. CPOL Functionality

# 17.1 Overview

A simplified block diagram of the USART Transmitter is shown in Figure 17-1. CPU accessible I/O Registers and I/O pins are shown in bold.

Note: 1. Refer to Figure 1-1 on page 3 and Table 10-9 on page 67 for USART0 pin placement.

The dashed boxes in the block diagram separate the three main parts of the USART (listed from the top): clock generator, transmitter and receiver. Control registers are shared by all units. The clock generation logic consists of synchronization logic for external clock input used by synchronous slave operation, and the baud rate generator. The XCKn (transfer clock) pin is only used by synchronous transfer mode. The transmitter consists of a single write buffer, a serial shift register, parity generator and control logic for handling different serial frame formats. The write buffer allows a continuous transfer of data without any delay between frames. The receiver is the most complex part of the USART module due to its clock and data recovery units. The receiver units are used for asynchronous data reception. In addition to the recovery units, the receiver includes a parity checker, control logic, a shift register and a two level receive buffer (UDRn). The receiver supports the same frame formats as the transmitter, and can detect frame error, data overrun and parity errors.

# Atmel

# 18.5 Data Transfer

Using the USART in MSPI mode requires the transmitter to be enabled, i.e. the TXENn bit in the UCSRnB register is set to one. When the transmitter is enabled, the normal port operation of the TxDn pin is overridden and given the function as the transmitter's serial output. Enabling the receiver is optional and is done by setting the RXENn bit in the UCSRnB register to one. When the receiver is enabled, the normal pin operation of the RxDn pin is overridden and given the function as the receiver's serial input. The XCKn will in both cases be used as the transfer clock.

After initialization the USART is ready for doing data transfers. A data transfer is initiated by writing to the UDRn I/O location. This is the case for both sending and receiving data since the transmitter controls the transfer clock. The data written to UDRn is moved from the transmit buffer to the shift register when the shift register is ready to send a new frame.

Note: To keep the input buffer in sync with the number of data bytes transmitted, the UDRn register must be read once for each byte transmitted. The input buffer operation is identical to normal USART mode, i.e. if an overflow occurs the character last received will be lost, not the first data in the buffer. This means that if four bytes are transferred, byte 1 first, then byte 2, 3, and 4, and the UDRn is not read before all transfers are completed, then byte 3 to be received will be lost, and not byte 1.

The following code examples show a simple USART in MSPIM mode transfer function based on polling of the data register empty (UDREn) flag and the receive complete (RXCn) flag. The USART has to be initialized before the function can be used. For the assembly code, the data to be sent is assumed to be stored in register R16 and the data received will be available in the same register (R16) after the function returns.

The function simply waits for the transmit buffer to be empty by checking the UDREn flag, before loading it with new data to be transmitted. The function then waits for data to be present in the receive buffer by checking the RXCn flag, before reading the buffer and returning the value.

| Assembly Code Example <sup>(1)</sup>                                    |  |  |  |  |  |

|-------------------------------------------------------------------------|--|--|--|--|--|

| USART_MSPIM_Transfer:                                                   |  |  |  |  |  |

| ; Wait for empty transmit buffer                                        |  |  |  |  |  |

| <b>sbis</b> UCSRnA, UDREn                                               |  |  |  |  |  |

| <b>rjmp</b> USART_MSPIM_Transfer                                        |  |  |  |  |  |

| ; Put data (r16) into buffer, sends the data                            |  |  |  |  |  |

| out UDRn,r16                                                            |  |  |  |  |  |

| ; Wait for data to be received                                          |  |  |  |  |  |

| USART_MSPIM_Wait_RXCn:                                                  |  |  |  |  |  |

| sbis UCSRnA, RXCn                                                       |  |  |  |  |  |

| <b>rjmp</b> USART_MSPIM_Wait_RXCn                                       |  |  |  |  |  |

| ; Get and return received data from buffer                              |  |  |  |  |  |

| in r16, UDRn                                                            |  |  |  |  |  |

| ret                                                                     |  |  |  |  |  |

| C Code Example <sup>(1)</sup>                                           |  |  |  |  |  |

| unsigned char USART_Receive(void)                                       |  |  |  |  |  |

| {                                                                       |  |  |  |  |  |

| /* Wait for empty transmit buffer */                                    |  |  |  |  |  |

| <pre>while (!(UCSRnA &amp; (1&lt;<udren)));< pre=""></udren)));<></pre> |  |  |  |  |  |

| /* Put data into buffer, sends the data */                              |  |  |  |  |  |

| UDRn = data;                                                            |  |  |  |  |  |

| /* Wait for data to be received */                                      |  |  |  |  |  |

| <pre>while (!(UCSRnA &amp; (1&lt;<rxcn)));< pre=""></rxcn)));<></pre>   |  |  |  |  |  |

| /* Get and return received data from buffer */                          |  |  |  |  |  |

| return UDRn;                                                            |  |  |  |  |  |

| }                                                                       |  |  |  |  |  |

Note: 1. The example code assumes that the part specific header file is included. For I/O registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

# 19. 2-wire Serial Interface

# 19.1 Features

- Simple yet powerful and flexible communication interface, only two bus lines needed

- Both master and slave operation supported

- Device can operate as transmitter or receiver

- 7-bit address space allows up to 128 different slave addresses

- Multi-master arbitration support

- Up to 400kHz data transfer speed

- Slew-rate limited output drivers

- Noise suppression circuitry rejects spikes on bus lines

- Fully programmable slave address with general call support

- Address recognition causes wake-up when AVR® is in sleep mode

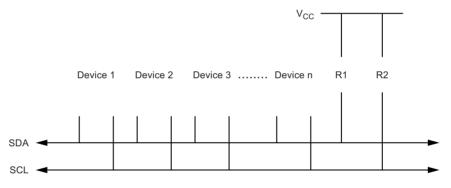

# 19.2 2-wire Serial Interface Bus Definition

The 2-wire serial interface (TWI) is ideally suited for typical microcontroller applications. The TWI protocol allows the systems designer to interconnect up to 128 different devices using only two bi-directional bus lines, one for clock (SCL) and one for data (SDA). The only external hardware needed to implement the bus is a single pull-up resistor for each of the TWI bus lines. All devices connected to the bus have individual addresses, and mechanisms for resolving bus contention are inherent in the TWI protocol.

#### Figure 19-1. TWI Bus Interconnection

# 19.2.1 TWI Terminology

The following definitions are frequently encountered in this section.

#### Table 19-1. TWI Terminology

| Term        | Description                                                                                       |

|-------------|---------------------------------------------------------------------------------------------------|

| Master      | The device that initiates and terminates a transmission. The Master also generates the SCL clock. |

| Slave       | The device addressed by a Master.                                                                 |

| Transmitter | The device placing data on the bus.                                                               |

| Receiver    | The device reading data from the bus.                                                             |

The PRTWI bit in Section 7.7.1 "Power Reduction Register - PRR" on page 35 must be written to zero to enable the 2-wire serial interface.

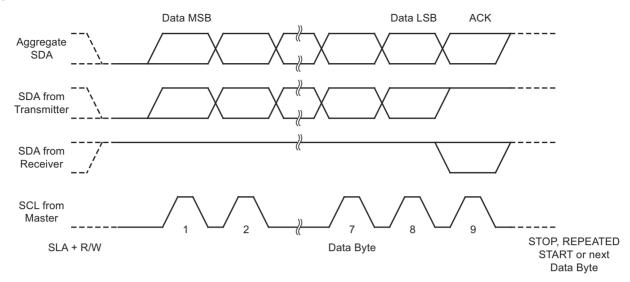

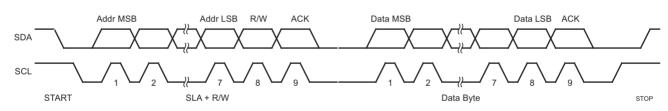

#### 19.3.5 Combining Address and Data Packets into a Transmission

A transmission basically consists of a START condition, a SLA+R/W, one or more data packets and a STOP condition. An empty message, consisting of a START followed by a STOP condition, is illegal. Note that the Wired-ANDing of the SCL line can be used to implement handshaking between the master and the slave. The slave can extend the SCL low period by pulling the SCL line low. This is useful if the clock speed set up by the master is too fast for the slave, or the slave needs extra time for processing between the data transmissions. The slave extending the SCL low period will not affect the SCL high period, which is determined by the master. As a consequence, the slave can reduce the TWI data transfer speed by prolonging the SCL duty cycle.

Figure 19-6 shows a typical data transmission. Note that several data bytes can be transmitted between the SLA+R/W and the STOP condition, depending on the software protocol implemented by the application software.

#### Figure 19-6. Typical Data Transmission

#### 19.4 Multi-master Bus Systems, Arbitration and Synchronization

The TWI protocol allows bus systems with several masters. Special concerns have been taken in order to ensure that transmissions will proceed as normal, even if two or more masters initiate a transmission at the same time. Two problems arise in multi-master systems:

- An algorithm must be implemented allowing only one of the masters to complete the transmission. All other masters should cease transmission when they discover that they have lost the selection process. This selection process is called arbitration. When a contending master discovers that it has lost the arbitration process, it should immediately switch to slave mode to check whether it is being addressed by the winning master. The fact that multiple masters have started transmission at the same time should not be detectable to the slaves, i.e. the data being transferred on the bus must not be corrupted.

- Different masters may use different SCL frequencies. A scheme must be devised to synchronize the serial clocks from all masters, in order to let the transmission proceed in a lockstep fashion. This will facilitate the arbitration process.

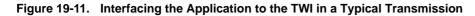

- The first step in a TWI transmission is to transmit a START condition. This is done by writing a specific value into TWCR, instructing the TWI hardware to transmit a START condition. Which value to write is described later on. However, it is important that the TWINT bit is set in the value written. Writing a one to TWINT clears the flag. The TWI will not start any operation as long as the TWINT bit in TWCR is set. Immediately after the application has cleared TWINT, the TWI will initiate transmission of the START condition.

- 2. When the START condition has been transmitted, the TWINT flag in TWCR is set, and TWSR is updated with a status code indicating that the START condition has successfully been sent.

- 3. The application software should now examine the value of TWSR, to make sure that the START condition was successfully transmitted. If TWSR indicates otherwise, the application software might take some special action, like calling an error routine. Assuming that the status code is as expected, the application must load SLA+W into TWDR. Remember that TWDR is used both for address and data. After TWDR has been loaded with the desired SLA+W, a specific value must be written to TWCR, instructing the TWI hardware to transmit the SLA+W present in TWDR. Which value to write is described later on. However, it is important that the TWINT bit is set in the value written. Writing a one to TWINT clears the flag. The TWI will not start any operation as long as the TWINT bit in TWCR is set. Immediately after the application has cleared TWINT, the TWI will initiate transmission of the address packet.

- 4. When the address packet has been transmitted, the TWINT flag in TWCR is set, and TWSR is updated with a status code indicating that the address packet has successfully been sent. The status code will also reflect whether a slave acknowledged the packet or not.

- 5. The application software should now examine the value of TWSR, to make sure that the address packet was successfully transmitted, and that the value of the ACK bit was as expected. If TWSR indicates otherwise, the application software might take some special action, like calling an error routine. Assuming that the status code is as expected, the application must load a data packet into TWDR. Subsequently, a specific value must be written to TWCR, instructing the TWI hardware to transmit the data packet present in TWDR. Which value to write is described later on. However, it is important that the TWINT bit is set in the value written. Writing a one to TWINT clears the flag. The TWI will not start any operation as long as the TWINT bit in TWCR is set. Immediately after the application has cleared TWINT, the TWI will initiate transmission of the data packet.

- 6. When the data packet has been transmitted, the TWINT flag in TWCR is set, and TWSR is updated with a status code indicating that the data packet has successfully been sent. The status code will also reflect whether a slave acknowledged the packet or not.

Table 19-3. Code Example (Continued)

| No. | Assem                        | bly Code Example                                                          | C Example                                                                                                                 | Comments                                                                                                           |

|-----|------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| 6   | wait3:<br>in<br>sbrs<br>rjmp | r16,TWCR<br>r16,TWINT<br>wait3                                            | while (!(TWCR & (1< <twint)))<br>;</twint)))<br>                                                                          | Wait for TWINT flag set. This indicates that the DATA has been transmitted, and ACK/NACK has been received.        |

|     | in<br>andi<br>cpi<br>brne    | r16,TWSR<br>r16,0xF8<br>r16, MT_DATA_ACK<br>ERROR                         | if ((TWSR & 0xF8) !=<br>MT_DATA_ACK)<br>ERROR();                                                                          | Check value of TWI status<br>register. Mask prescaler bits. If<br>status different from<br>MT_DATA_ACK go to ERROR |

| /   | `                            | r16,<br>/INT) (1< <twen) <br><twsto)<br>TWCR, r16</twsto)<br></twen) <br> | TWCR = (1< <twint) (1<<twen) <br>(1&lt;<twsto);< th=""><th>Transmit STOP condition</th></twsto);<></twint) (1<<twen) <br> | Transmit STOP condition                                                                                            |

# 19.8 Transmission Modes

The TWI can operate in one of four major modes. These are named master transmitter (MT), master receiver (MR), slave transmitter (ST) and slave receiver (SR). Several of these modes can be used in the same application. As an example, the TWI can use MT mode to write data into a TWI EEPROM, MR mode to read the data back from the EEPROM. If other masters are present in the system, some of these might transmit data to the TWI, and then SR mode would be used. It is the application software that decides which modes are legal.

The following sections describe each of these modes. Possible status codes are described along with figures detailing data transmission in each of the modes. These figures contain the following abbreviations:

- S: START condition

- Rs: REPEATED START condition

- R: Read bit (high level at SDA)

- W: Write bit (low level at SDA)

- A: Acknowledge bit (low level at SDA)

- A: Not acknowledge bit (high level at SDA)

- Data: 8-bit data byte

- P: STOP condition

- SLA: Slave address

In Figure 19-13 on page 189 to Figure 19-19 on page 198, circles are used to indicate that the TWINT flag is set. The numbers in the circles show the status code held in TWSR, with the prescaler bits masked to zero. At these points, actions must be taken by the application to continue or complete the TWI transfer. The TWI transfer is suspended until the TWINT flag is cleared by software.

When the TWINT flag is set, the status code in TWSR is used to determine the appropriate software action. For each status code, the required software action and details of the following serial transfer are given in Table 19-4 on page 188 to Table 19-7 on page 197. Note that the prescaler bits are masked to zero in these tables.

# 19.8.1 Master Transmitter Mode

In the master transmitter mode, a number of data bytes are transmitted to a slave receiver (see Figure 19-12 on page 187). In order to enter a master mode, a START condition must be transmitted. The format of the following address packet determines whether master transmitter or master receiver mode is to be entered. If SLA+W is transmitted, MT mode is entered, if SLA+R is transmitted, MR mode is entered. All the status codes mentioned in this section assume that the prescaler bits are zero or are masked to zero

After a repeated START condition (state 0x10) the 2-wire serial interface can access the same slave again, or a new slave without transmitting a STOP condition. Repeated START enables the master to switch between slaves, master transmitter mode and master receiver mode without losing control of the bus.

|                         |                                                                    | Application Software Response                                                    |                  |                  |                  |                  |                                                                                                                                                                                                                                                                                         |

|-------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------|------------------|------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Status Code<br>(TWSR)   | Status of the 2-wire<br>Serial Bus and 2-wire                      | To/from TWDR                                                                     |                  | To               | WCR              |                  |                                                                                                                                                                                                                                                                                         |

| Prescaler<br>Bits are 0 | Serial Interface<br>Hardware                                       |                                                                                  | STA              | ѕто              | TWINT            | TWEA             | Next Action Taken by TWI Hardware                                                                                                                                                                                                                                                       |

| 0x08                    | A START condition has<br>been transmitted                          | Load SLA+W                                                                       | 0                | 0                | 1                | Х                | SLA+W will be transmitted;<br>ACK or NOT ACK will be received                                                                                                                                                                                                                           |

| 0x10                    | A repeated START<br>condition has been<br>transmitted              | Load SLA+W<br>or<br>Load SLA+R                                                   | 0<br>0           | 0                | 1                | x<br>x           | SLA+W will be transmitted;<br>ACK or NOT ACK will be received<br>SLA+R will be transmitted;<br>logic will switch to master receiver mode                                                                                                                                                |

| 0x18                    | SLA+W has been<br>transmitted;<br>ACK has been received            | Load data byte or<br>No TWDR action<br>or No TWDR<br>action or<br>No TWDR action | 0<br>1<br>0<br>1 | 0<br>0<br>1<br>1 | 1<br>1<br>1      | X<br>X<br>X<br>X | Data byte will be transmitted and ACK or<br>NOT ACK will be received<br>Repeated START will be transmitted<br>STOP condition will be transmitted and<br>TWSTO flag will be reset<br>STOP condition followed by a START<br>condition will be transmitted and TWSTO<br>flag will be reset |

| 0x20                    | SLA+W has been<br>transmitted;<br>NOT ACK has been<br>received     | Load data byte or<br>No TWDR action<br>or No TWDR<br>action or<br>No TWDR action | 0<br>1<br>0<br>1 | 0<br>0<br>1<br>1 | 1<br>1<br>1      | x<br>x<br>x<br>x | Data byte will be transmitted and ACK or<br>NOT ACK will be received<br>Repeated START will be transmitted<br>STOP condition will be transmitted and<br>TWSTO flag will be reset<br>STOP condition followed by a START<br>condition will be transmitted and TWSTO<br>flag will be reset |

| 0x28                    | Data byte has been<br>transmitted;<br>ACK has been received        | Load data byte or<br>No TWDR action<br>or No TWDR<br>action or<br>No TWDR action | 0<br>1<br>0<br>1 | 0<br>0<br>1<br>1 | 1<br>1<br>1<br>1 | X<br>X<br>X<br>X | Data byte will be transmitted and ACK or<br>NOT ACK will be received<br>repeated START will be transmitted<br>STOP condition will be transmitted and<br>TWSTO flag will be reset<br>STOP condition followed by a START<br>condition will be transmitted and TWSTO flag<br>will be reset |

| 0x30                    | Data byte has been<br>transmitted;<br>NOT ACK has been<br>received | Load data byte or<br>No TWDR action<br>or No TWDR<br>action or<br>No TWDR action | 0<br>1<br>0<br>1 | 0<br>0<br>1<br>1 | 1<br>1<br>1      | X<br>X<br>X<br>X | Data byte will be transmitted and ACK or<br>NOT ACK will be received<br>Repeated START will be transmitted<br>STOP condition will be transmitted and<br>TWSTO flag will be reset<br>STOP condition followed by a START<br>condition will be transmitted and TWSTO flag<br>will be reset |

| 0x38                    | Arbitration lost in SLA+W or data bytes                            | No TWDR action<br>or<br>No TWDR action                                           | 0<br>1           | 0<br>0           | 1<br>1           | x<br>x           | 2-wire serial bus will be released and not<br>addressed slave mode entered<br>A START condition will be transmitted when<br>the bus becomes free                                                                                                                                        |

#### Table 19-4. Status Codes for Master Transmitter Mode

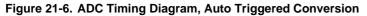

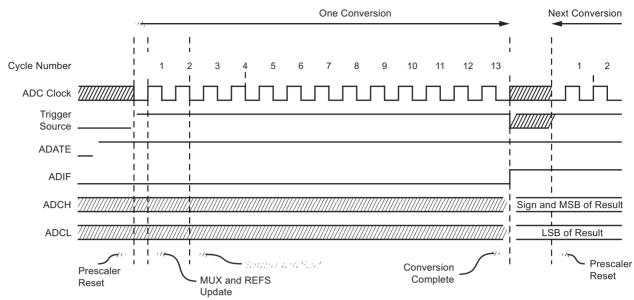

Figure 21-7. ADC Timing Diagram, Free Running Conversion

Table 21-1. ADC Conversion Time

| Condition                        | Sample & Hold (Cycles from Start of Conversion) | Conversion Time (Cycles) |

|----------------------------------|-------------------------------------------------|--------------------------|

| First conversion                 | 13.5                                            | 25                       |

| Normal conversions, single ended | 1.5                                             | 13                       |

| Auto triggered conversions       | 2                                               | 13.5                     |

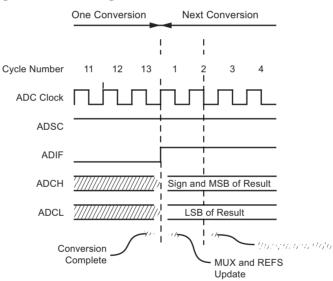

# 21.5.2 Analog Noise Canceling Techniques

Digital circuitry inside and outside the device generates EMI which might affect the accuracy of analog measurements. If conversion accuracy is critical, the noise level can be reduced by applying the following techniques:

- a. Keep analog signal paths as short as possible. Make sure analog tracks run over the analog ground plane, and keep them well away from high-speed switching digital tracks.

- b. The AV<sub>CC</sub> pin on the device should be connected to the digital V<sub>CC</sub> supply voltage via an LC network as shown in Figure 21-9.

- c. Use the ADC noise canceler function to reduce induced noise from the CPU.

- d. If any ADC [3..0] port pins are used as digital outputs, it is essential that these do not switch while a conversion is in progress. However, using the 2-wire interface (ADC4 and ADC5) will only affect the conversion on ADC4 and ADC5 and not the other ADC channels.

# 23.7.14 ATmega168 Boot Loader Parameters

In Table 23-9 through Table 23-11, the parameters used in the description of the self programming are given.

| BOOTSZ1 | BOOTSZ0 | Boot Size  | Pages | Application<br>Flash Section | Boot Loader<br>Flash Section | End Application<br>Section | Boot Reset<br>Address (Start<br>Boot Loader<br>Section) |

|---------|---------|------------|-------|------------------------------|------------------------------|----------------------------|---------------------------------------------------------|

| 1       | 1       | 128 words  | 2     | 0x0000 - 0x1F7F              | 0x1F80 - 0x1FFF              | 0x1F7F                     | 0x1F80                                                  |

| 1       | 0       | 256 words  | 4     | 0x0000 -<br>0x1EFF           | 0x1F00 - 0x1FFF              | 0x1EFF                     | 0x1F00                                                  |

| 0       | 1       | 512 words  | 8     | 0x0000 -<br>0x1DFF           | 0x1E00 -<br>0x1FFF           | 0x1DFF                     | 0x1E00                                                  |

| 0       | 0       | 1024 words | 16    | 0x0000 -<br>0x1BFF           | 0x1C00 -<br>0x1FFF           | 0x1BFF                     | 0x1C00                                                  |

Table 23-9. Boot Size Configuration, ATmega168

Note: The different BOOTSZ fuse configurations are shown in Figure 23-2 on page 223.

#### Table 23-10. Read-While-Write Limit, ATmega168

| Section                           | Pages | Address         |

|-----------------------------------|-------|-----------------|

| Read-while-write section (RWW)    | 112   | 0x0000 - 0x1BFF |

| No read-while-rite section (NRWW) | 16    | 0x1C00 - 0x1FFF |

For details about these two section, see Section 23.3.2 "NRWW – No Read-While-Write Section" on page 222 and Section 23.3.1 "RWW – Read-While-Write Section" on page 222.

| Variable |          | Corresponding Z-value <sup>(1)</sup> | Description                                                                                                           |

|----------|----------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| PCMSB    | 12       |                                      | Most significant bit in the program counter. (The program counter is 12 bits PC[11:0])                                |

| PAGEMSB  |          |                                      | Most significant bit which is used to address the words within one page (64 words in a page requires 6 bits PC [5:0]) |

| ZPCMSB   |          | Z13                                  | Bit in Z-register that is mapped to PCMSB. Because Z0 is not used, the ZPCMSB equals PCMSB + 1.                       |

| ZPAGEMSB |          | Z6                                   | Bit in Z-register that is mapped to PAGEMSB. Because Z0 is not used, the ZPAGEMSB equals PAGEMSB + 1.                 |

| PCPAGE   | PC[12:6] | Z13:Z7                               | Program counter page address: page select, for page erase and page write                                              |

| PCWORD   | PC[5:0]  | Z6:Z1                                | Program counter word address: Word select, for filling temporary buffer (must be zero during page write operation)    |

Note: 1. Z15:Z14: always ignored

Z0: should be zero for all SPM commands, byte select for the LPM instruction. See Section 23.6 "Addressing the Flash During Self-Programming" on page 226 for details about the use of Z-pointer during self-Programming.

# 25.7 LIN Re-synchronization Algorithm

# 25.8 Synchronization Algorithm

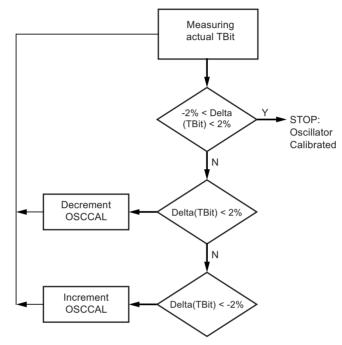

The possibility to change the value of OSCCAL during the oscillator operation allows for in-situ calibration of the slave node to entering Master frames. The principle of operation is to measure the TBit during the SYNCH byte and to change the calibration value of OSCCAL to recover from local frequency drifts due to local voltage or temperature deviation. The algorithm used for the synchronization of the internal RC oscillator is depicted in Figure 25-3 on page 255.

#### Figure 25-3. Dichotomic Algorithm Used for LIN Slave Clock Re-synchronization

Figure 27-25. Analog to Digital Converter INL versus V<sub>CC</sub>

# 27.8 Grade 0 Qualification

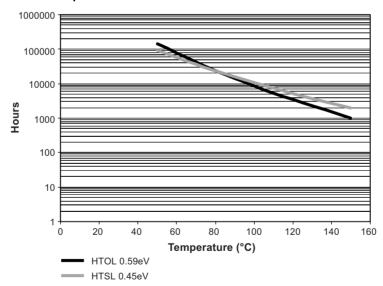

The ATmega88/ATmega168 Automotive has been developed and manufactured according to the most stringent quality assurance requirements of ISO-TS-16949 and verified during product qualification as per AEC-Q100 grade 0.

AEC-Q100 qualification relies on temperature accelerated stress testing. High temperature field usage however may result in less significant stress test acceleration. In order to prevent the risk that ATmega88/ATmega168 Automotive lifetime would not satisfy the application end-of-life reliability requirements, Atmel<sup>®</sup> has extended the testing, whenever applicable (High Temperature Operating Life Test, High Temperature Storage Life, Data Retention, Thermal Cycles), far beyond the AEC-Q100 requirements. Thereby, Atmel verified the ATmega88/ATmega168 Automotive has a long safe lifetime period after the grade 0 qualification acceptance limits.

The valid domain calculation depends on the activation energy of the potential failure mechanism that is considered. Examples are given in Figure 27-26. Therefore any temperature mission profile which could exceed the AEC-Q100 equivalence domain shall be submitted to Atmel for a thorough reliability analysis.

# Figure 27-26. AEC-Q100 Lifetime Equivalence

# 28. Register Summary (Continued)

|             | Name     | Bit 7                | Bit 6                  | Bit 5   | Bit 4                   | Bit 3          | Bit 2                 | Bit 1    | Bit 0     | Page |

|-------------|----------|----------------------|------------------------|---------|-------------------------|----------------|-----------------------|----------|-----------|------|

| (0x70)      | TIMSK2   | -                    | -                      | -       | -                       | -              | OCIE2B                | OCIE2A   | TOIE2     | 131  |

| (0x6F)      | TIMSK1   | -                    | -                      | ICIE1   | _                       | -              | OCIE1B                | OCIE1A   | TOIE1     | 115  |

| (0x6E)      | TIMSK0   | -                    | -                      | -       | _                       | _              | OCIE0B                | OCIE0A   | TOIE0     | 89   |

| (0x6D)      | PCMSK2   | PCINT23              | PCINT22                | PCINT21 | PCINT20                 | PCINT19        | PCINT18               | PCINT17  | PCINT16   | 74   |

| (0x6C)      | PCMSK1   | -                    | PCINT14                | PCINT13 | PCINT12                 | PCINT11        | PCINT10               | PCINT9   | PCINT8    | 74   |

| (0x6B)      | PCMSK0   | PCINT7               | PCINT6                 | PCINT5  | PCINT4                  | PCINT3         | PCINT2                | PCINT1   | PCINT0    | 74   |

| (0x6A)      | Reserved | -                    | -                      | _       | —                       | -              | -                     | -        | —         |      |

| (0x69)      | EICRA    | -                    | _                      | _       | —                       | ISC11          | ISC10                 | ISC01    | ISC00     | 71   |

| (0x68)      | PCICR    | l                    | _                      | _       | _                       | -              | PCIE2                 | PCIE1    | PCIE0     |      |

| (0x67)      | Reserved | -                    | _                      | _       | —                       | -              | -                     | -        | —         |      |

| (0x66)      | OSCCAL   |                      |                        |         | Oscillator calib        | ration registe | er                    |          | •         | 29   |

| (0x65)      | Reserved | l                    | _                      | _       | —                       | -              | -                     | -        | -         |      |

| (0x64)      | PRR      | PRTWI                | PRTIM2                 | PRTIM0  | —                       | PRTIM1         | PRSPI                 | PRUSART0 | PRADC     | 35   |

| (0x63)      | Reserved | -                    | -                      | _       | —                       | -              | -                     | -        | —         |      |

| (0x62)      | Reserved | l                    | _                      | _       | —                       | -              | _                     | -        | -         |      |

| (0x61)      | CLKPR    | CLKPCE               | _                      | _       | —                       | CLKPS3         | CLKPS2                | CLKPS1   | CLKPS0    | 31   |

| (0x60)      | WDTCSR   | WDIF                 | WDIE                   | WDP3    | WDCE                    | WDE            | WDP2                  | WDP1     | WDP0      | 46   |

| 0x3F (0x5F) | SREG     | I                    | Т                      | Н       | S                       | V              | Ν                     | Z        | С         | 10   |

| 0x3E (0x5E) | SPH      | -                    | -                      | _       | —                       | -              | (SP10) <sup>(5)</sup> | SP9      | SP8       | 12   |

| 0x3D (0x5D) | SPL      | SP7                  | SP6                    | SP5     | SP4                     | SP3            | SP2                   | SP1      | SP0       | 12   |

| 0x3C (0x5C) | Reserved | -                    | -                      | _       | -                       | _              | -                     | -        | -         |      |

| 0x3B (0x5B) | Reserved | -                    | _                      | _       | —                       | -              | -                     | -        | -         |      |

| 0x3A (0x5A) | Reserved | -                    | _                      | _       | —                       | -              | -                     | -        | -         |      |

| 0x39 (0x59) | Reserved | -                    | -                      | -       | -                       | -              | -                     | -        | -         |      |

| 0x38 (0x58) | Reserved | -                    | -                      | -       | -                       | -              | -                     | -        | -         |      |

| 0x37 (0x57) | SPMCSR   | SPMIE                | (RWWSB) <sup>(5)</sup> | _       | (RWWSRE) <sup>(5)</sup> | BLBSET         | PGWRT                 | PGERS    | SELFPRGEN | 225  |

| 0x36 (0x56) | Reserved | -                    | -                      | _       | -                       | _              | -                     | -        | -         |      |

| 0x35 (0x55) | MCUCR    | -                    | _                      | _       | PUD                     | -              | -                     | IVSEL    | IVCE      |      |

| 0x34 (0x54) | MCUSR    | -                    | -                      | -       | —                       | WDRF           | BORF                  | EXTRF    | PORF      |      |

| 0x33 (0x53) | SMCR     | -                    | _                      | -       | —                       | SM2            | SM1                   | SM0      | SE        | 33   |

| 0x32 (0x52) | Reserved | -                    | -                      | -       | —                       | -              | -                     | -        | —         |      |

| 0x31 (0x51) | Reserved | -                    | -                      | -       | —                       | -              | -                     | -        | -         |      |

| 0x30 (0x50) | ACSR     | ACD                  | ACBG                   | ACO     | ACI                     | ACIE           | ACIC                  | ACIS1    | ACIS0     | 202  |

| 0x2F (0x4F) | Reserved | -                    | -                      | -       | —                       | -              | -                     | -        | —         |      |

| 0x2E (0x4E) | SPDR     | SPI Data Register 14 |                        |         |                         | 142            |                       |          |           |      |

Notes: 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

- 2. I/O registers within the address range 0x00 0x1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions.

- 3. Some of the status flags are cleared by writing a logical one to them. Note that, unlike most other AVR<sup>®</sup>, the CBI and SBI instructions will only operate on the specified bit, and can therefore be used on registers containing such status flags. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

- 4. When using the I/O specific commands IN and OUT, the I/O addresses 0x00 0x3F must be used. When addressing I/O registers as data space using LD and ST instructions, 0x20 must be added to these addresses. The ATmega88/168 is a complex microcontroller with more peripheral units than can be supported within the 64 location reserved in opcode for the IN and OUT instructions. For the extended I/O space from 0x60 0xFF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

- 5. Only valid for Atmel<sup>®</sup> ATmega88/168

# 30. Ordering Information

# 30.1 ATmega88

| Speed (MHz)       | Power Supply | Ordering Code  | Package <sup>(1)</sup> | Operation Range            |

|-------------------|--------------|----------------|------------------------|----------------------------|

| 16 <sup>(2)</sup> | 2.7V to 5.5V | ATmega88-15MT2 | PN                     | Extended (-40°C to +150°C) |

| 16 <sup>(2)</sup> | 2.7V to 5.5V | ATmega88-15AD  | MA                     | Extended (-40°C to +150°C) |

Notes: 1. Pb-free packaging, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also halide free and fully green.

2. See Figure 25-1 on page 254.

# 30.2 ATmega168

| Speed (MHz)       | Power Supply | Ordering Code  | Package <sup>(1)</sup> | Operation Range            |

|-------------------|--------------|----------------|------------------------|----------------------------|

| 16 <sup>(2)</sup> | 2.7V to 5.5V | ATmega168-15MD | PN                     | Extended (–40°C to +150°C) |

| 16 <sup>(2)</sup> | 2.7V to 5.5V | ATmega168-15AD | MA                     | Extended (-40°C to +150°C) |

Notes: 1. Pb-free packaging, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also halide free and fully green.

2. See Figure 25-1 on page 254.

# 30.3 Package information

|    | Package Information                                                                                                                      |

|----|------------------------------------------------------------------------------------------------------------------------------------------|

| MA | 32 - Lead, 7mm $\times$ 7mm body size, 1.0mm body thickness 0.8mm lead pitch, thin profile plastic quad flat package (TQFP)              |

| PN | 32-pad, 5 $\times$ 5 $\times$ 1.0mm body, lead pitch 0.50mm, quad flat no-lead/micro lead frame package (QFN/MLF): E2/D2 3.1 $\pm 0.1mm$ |