Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | 8051                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 36                                                                      |

| Program Memory Size        | 4KB (4K x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-TQFP                                                                 |

| Supplier Device Package    | 44-TQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89lp51-20au |

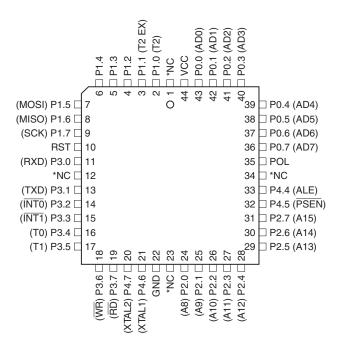

#### 1.3 44-lead PLCC

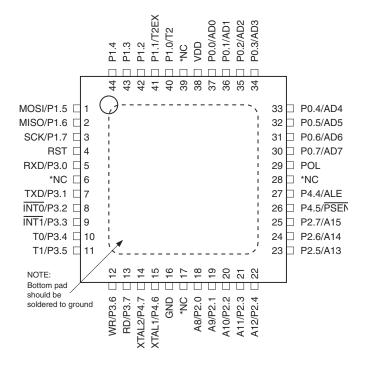

### 1.4 44-pad VQFN/QFN/MLF

# 1.5 Pin Description

Table 1-1.AT89LP51/52 Pin Description

|      | Pin Number |      |      |        |            |                                                                                                                                                                                                                  |

|------|------------|------|------|--------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFP | PLCC       | PDIP | VQFN | Symbol | Туре       | Description                                                                                                                                                                                                      |

| 1    | 7          | 6    | 1    | P1.5   | I/O<br>I/O | P1.5: I/O Port 1 bit 5.  MOSI: SPI master-out/slave-in. In UART SPI mode this pin is an output. During In- System Programming, this pin is an input.                                                             |

| 2    | 8          | 7    | 2    | P1.6   | I/O<br>I/O | P1.6: I/O Port 1 bit 6.  MISO: SPI master-in/slave-out. In UART SPI mode this pin is an input. During In- System Programming, this pin is an output.                                                             |

| 3    | 9          | 8    | 3    | P1.7   | I/O<br>I/O | P1.7: I/O Port 1 bit 7. SCK: SPI Clock. In UART SPI mode this pin is an output. During In-System Programming, this pin is an input.                                                                              |

| 4    | 10         | 9    | 4    | RST    | I/O        | <b>RST</b> : External Reset input (Reset polarity depends on POL pin. See "External Reset" on page 33.). The RST pin can output a pulse when the internal Watchdog reset is active.                              |

| 5    | 11         | 10   | 5    | P3.0   | I/O<br>I   | P3.0: I/O Port 3 bit 0. RXD: Serial Port Receiver Input.                                                                                                                                                         |

| 6    | 12         |      | 6    |        | NC         | Not internally connected                                                                                                                                                                                         |

| 7    | 13         | 11   | 7    | P3.1   | I/O<br>O   | P3.1: I/O Port 3 bit 1. TXD: Serial Port Transmitter Output.                                                                                                                                                     |

| 8    | 14         | 12   | 8    | P3.2   | I/O<br>I   | P3.2: I/O Port 3 bit 2.  INT0: External Interrupt 0 Input or Timer 0 Gate Input.                                                                                                                                 |

| 9    | 15         | 13   | 9    | P3.3   | I/O<br>I   | P3.3: I/O Port 3 bit 3.  INT1: External Interrupt 1 Input or Timer 1 Gate Input                                                                                                                                  |

| 10   | 16         | 14   | 10   | P3.4   | I/O<br>I/O | P3.4: I/O Port 3 bit 4. T1: Timer/Counter 0 External input or output.                                                                                                                                            |

| 11   | 17         | 15   | 1    | P3.5   | I/O<br>I/O | P3.5: I/O Port 3 bit 5. T1: Timer/Counter 1 External input or output.                                                                                                                                            |

| 12   | 18         | 16   | 12   | P3.6   | I/O<br>O   | P3.6: I/O Port 3 bit 6.  WR: External memory interface Write Strobe (active-low).                                                                                                                                |

| 13   | 19         | 17   | 13   | P3.7   | I/O<br>O   | P3.7: I/O Port 3 bit 7.  RD: External memory interface Read Strobe (active-low).                                                                                                                                 |

| 14   | 20         | 18   | 14   | P4.7   | I/O<br>O   | P4.7: I/O Port 4 bit 7.  XTAL2: Output from inverting oscillator amplifier. It may be used as a port pin if the internal RC oscillator or external clock is selected as the clock source.                        |

| 15   | 21         | 19   | 15   | P4.6   | I/O<br>I   | P4.6: I/O Port 4 bit 6.  XTAL1: Input to the inverting oscillator amplifier and internal clock generation circuits.  It may be used as a port pin if the internal RC oscillator is selected as the clock source. |

| 16   | 22         | 20   | 16   | GND    | I          | Ground                                                                                                                                                                                                           |

| 17   | 23         |      | 17   |        | NC         | Not internally connected                                                                                                                                                                                         |

| 18   | 24         | 21   | 18   | P2.0   | I/O<br>O   | P2.0: I/O Port 2 bit 0. A8: External memory interface Address bit 8.                                                                                                                                             |

| 19   | 25         | 22   | 19   | P2.1   | I/O<br>O   | P2.1: I/O Port 2 bit 1. A9: External memory interface Address bit 9.                                                                                                                                             |

| 20   | 26         | 23   | 20   | P2.1   | I/O<br>O   | P2.2: I/O Port 2 bit 2. A10: External memory interface Address bit 10.                                                                                                                                           |

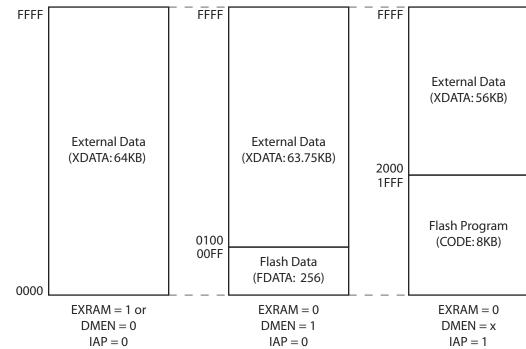

address space as shown in Figure 3-6. These memory spaces may require configuration before the CPU can access them. The AT89LP51/52 includes 256 bytes of nonvolatile Flash data memory (FDATA).

#### 3.3.1 XDATA

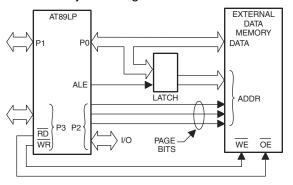

The external data memory space can accommodate up to 64KB of external memory. The AT89LP51/52 uses the standard 8051 external data memory interface with the upper address byte on Port 2, the lower address byte and data in/out multiplexed on Port 0, and the ALE,  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  strobes. XDATA can be accessed with both 16-bit (MOVX @DPTR) and 8-bit (MOVX @Ri) addresses. See Section 3.3.3 on page 18 for more details of the external memory interface.

Some internal data memory spaces are mapped into portions of the XDATA address space. In this case the lower address ranges will access internal resources instead of external memory. Addresses above the range implemented internally will default to XDATA. The AT89LP51/52 supports up to 63.75K or 56K bytes of external memory when using the internally mapped memories. Setting the EXRAM bit (AUXR.1) to one will force all MOVX instructions to access the entire 64KB XDATA regardless of their address (See "AUXR – Auxiliary Control Register" on page 20).

Figure 3-6. External Data Memory Map

#### 3.3.2 FDATA

The Flash Data Memory is a portion of the external memory space implemented as an internal nonvolatile data memory. Flash Data Memory is enabled by setting the DMEN bit (MEMCON.3) to one. When IAP = 0 and DMEN = 1, the Flash Data Memory is mapped into the FDATA space, at the bottom of the external memory address space, from 0000H to 00FFH. (See Figure 3-6). MOVX instructions to this address range will access the internal nonvolatile memory. FDATA is

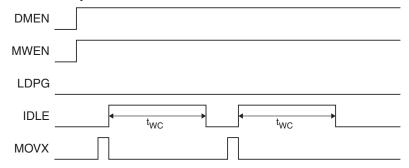

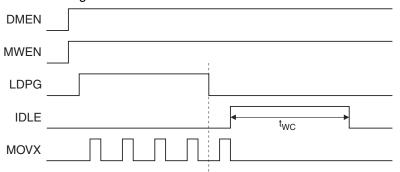

The LDPG bit (MEMCON.5) allows multiple data bytes to be loaded to the temporary page buffer. While LDPG = 1, MOVX @DPTR,A instructions will load data to the page buffer, but will not start a write sequence. Note that a previously loaded byte must not be reloaded prior to the write sequence. To write the half page into the memory, LDPG must first be cleared and then a MOVX @DPTR,A with the final data byte is issued. The address of the final MOVX determines which half page will be written. If a MOVX @DPTR,A instruction is issued while LDPG = 0 without loading any previous bytes, only a single byte will be written. The page buffer is reset after each write operation. Figures 3-8 and Figure 3-9 on page 17 show the difference between byte writes and page writes.

Figure 3-9. FDATA Page Write

The auto-erase bit AERS (MEMCON.6) can be set to one to perform a page erase automatically at the beginning of any write sequence. The page erase will erase the entire page, i.e. both the low and high half pages. However, the write operation paired with the auto-erase can only program one of the half pages. A second write cycle without auto-erase is required to update the other half page.

Frequently just a few bytes within a page must be updated while maintaining the state of the other bytes. There are two options for handling this situation that allow the Flash Data memory to emulate a traditional EEPROM memory. The simplest method is to copy the entire page into a buffer allocated in RAM, modify the desired byte locations in the RAM buffer, and then load and write back first the low half page (with auto-erase) and then the high half page to the Flash memory. This option requires that at least one page size of RAM is available as a temporary buffer. The second option is to store only one half page in RAM. The unmodified bytes of the other page are loaded directly into the Flash memory's temporary load buffer before loading the updated values of the modified bytes. For example, if just the low half page needs modification, the user must first store the high half page to RAM, followed by reading and loading the unaffected bytes of the low half page into the page buffer. Then the modified bytes of the low half page are stored

AT89LP

P1

P0

EXTERNAL DATA

MEMORY

DATA

ADDR

ADDR

RD

WR

P2

WE OE

Figure 3-10. External Data Memory 16-bit Linear Address Mode

Figure 3-11 shows a hardware configuration for accessing 256-byte blocks of external RAM using an 8-bit paged address. Port 0 serves as a multiplexed address/data bus to the RAM. The ALE strobe is used to latch the address byte into an external register so that Port 0 can be freed for data input/output. The Port 2 I/O lines (or other ports) can provide control lines to page the memory; however, this operation is not handled automatically by hardware. The software application must change the Port 2 register when appropriate to access different pages. The MOVX @Ri instructions use Paged Address mode.

Figure 3-11. External Data Memory 8-bit Paged Address Mode

Note that prior to using the external memory interface,  $\overline{WR}$  (P3.6) and  $\overline{RD}$  (P3.7) must be configured as outputs. See Section 10.1 "Port Configuration" on page 41. P0 and P2 are configured automatically to push-pull output mode when outputting address or data and P0 is automatically tristated when inputting data regardless of the port configuration. The Port 0 configuration will determine the idle state of Port 0 when not accessing the external memory.

Figure 3-12 and Figure 3-13 show examples of external data memory write and read cycles, respectively. The address on P0 and P2 is stable at the falling edge of ALE. The idle state of ALE is controlled by DISALE (AUXR.0). When DISALE = 0 the ALE toggles at a constant rate when not accessing external memory. When DISALE = 1 the ALE is weakly pulled high. DISALE must be one in order to use P4.4 as a general-purpose I/O. The WS bits in AUXR can extended the  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  strobes by 1, 2 or 3 cycles as shown in Figures 3-16, 3-17 and 3-18. If a longer strobe is required, the application can scale the system clock with the clock divider to meet the requirements (See Section 6.4 on page 31).

#### 8.2.1 Interrupt Recovery from Power-down

Two external interrupt sources may be configured to terminate Power-down mode: external interrupts INTO (P3.2) and INT1 (P3.3). To wake up by external interrupt INTO or INT1, that interrupt must be enabled by setting EXO or EX1 in IE and must be configured for level-sensitive operation by clearing ITO or IT1.

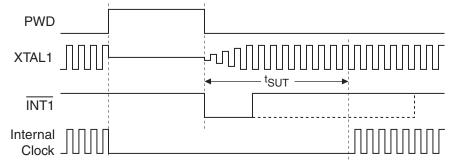

When terminating Power-down by an interrupt, two different wake-up modes are available. When PWDEX in PCON is one, the wake-up period is internally timed as shown in Figure 8-1. At the falling edge on the interrupt pin, Power-down is exited, the oscillator is restarted, and an internal timer begins counting. The internal clock will not be allowed to propagate to the CPU until after the timer has timed out. After the time-out period the interrupt service routine will begin. The time-out period is controlled by the Start-up Timer Fuses (see Table 7-1 on page 33). The interrupt pin need not remain low for the entire time-out period.

**Figure 8-1.** Interrupt Recovery from Power-down (PWDEX = 1)

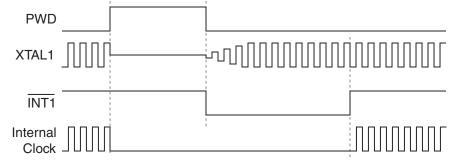

When PWDEX = "0", the wake-up period is controlled externally by the interrupt. Again, at the falling edge on the interrupt pin, power-down is exited and the oscillator is restarted. However, the internal clock will not propagate until the rising edge of the interrupt pin as shown in Figure 8-2. The interrupt pin should be held low long enough for the selected clock source to stabilize. After the rising edge on the pin the interrupt service routine will be executed.

**Figure 8-2.** Interrupt Recovery from Power-down (PWDEX = 0)

### 8.2.2 Reset Recovery from Power-down

The wake-up from Power-down through an external reset is similar to the interrupt with PWDEX = "1". At the rising edge of RST, Power-down is exited, the oscillator is restarted, and an internal timer begins counting as shown in Figure 8-3. The internal clock will not be allowed to propagate to the CPU until after the timer has timed out. The time-out period is controlled by the Start-up Timer Fuses. (See Table 7-1 on page 33). If RST returns low before the time-out, a two clock cycle internal reset is generated when the internal clock restarts. Otherwise, the device will remain in reset until RST is brought low.

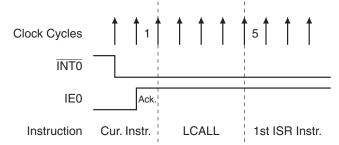

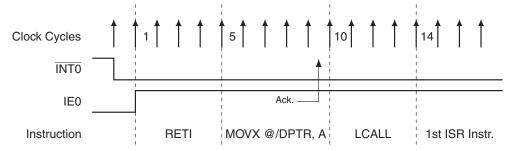

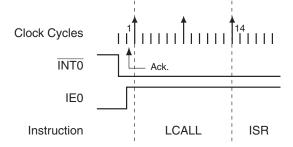

instruction is 5 cycles long. If the instruction in progress is RETI, the additional wait time cannot be more than 9 cycles (a maximum of 4 more cycles to complete the instruction in progress, plus a maximum of 5 cycles to complete the next instruction). Thus, in a single-interrupt system, the response time is always more than 5 clock cycles and less than 14 clock cycles. See Figure 9-1 and Figure 9-2.

Figure 9-1. Minimum Interrupt Response Time (Fast Mode)

Figure 9-2. Maximum Interrupt Response Time (Fast Mode)

Figure 9-3. Minimum Interrupt Response Time (Compatibility Mode)

Figure 9-4. Maximum Interrupt Response Time (Compatibility Mode)

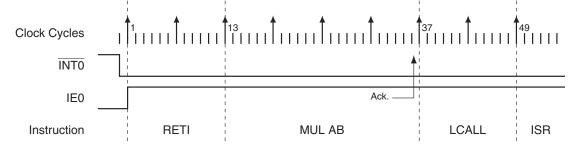

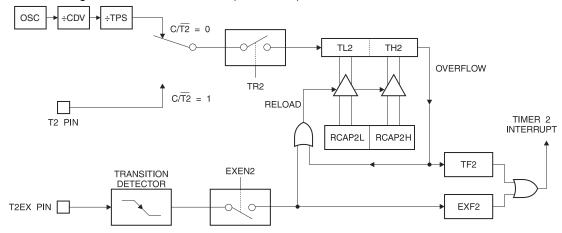

Figure 12-2. Timer 2 Diagram: Auto-Reload Mode (DCEN = 0)

Figure 12-3. Timer 2 Waveform: Auto-Reload Mode (DCEN = 0)

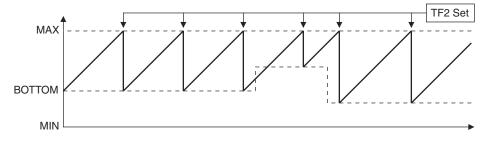

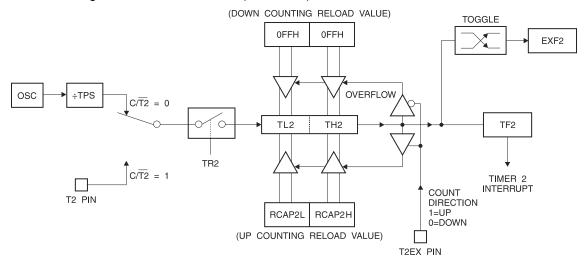

### 12.3.2 Up or Down Counter

Setting DCEN = 1 enables Timer 2 to count up or down, as shown in Figure 12-5. In this mode, the T2EX pin controls the direction of the count (if EXEN2 = 1). A logic 1 at T2EX makes Timer 2 count up. When  $T2CM_{1-0} = 00B$ , the timer will overflow at MAX and set the TF2 bit. This overflow also causes BOTTOM, the 16-bit value in RCAP2H and RCAP2L, to be reloaded into the timer registers, TH2 and TL2, respectively. A logic 0 at T2EX makes Timer 2 count down. The timer underflows when TH2 and TL2 equal BOTTOM, the 16-bit value stored in RCAP2H and RCAP2L. The underflow sets the TF2 bit and causes MAX to be reloaded into the timer registers. The EXF2 bit toggles whenever Timer 2 overflows or underflows and can be used as a 17th bit of resolution. In this operating mode, EXF2 does not flag an interrupt.

The behavior of Timer 2 when DCEN is enabled is shown in Figure 12-4.

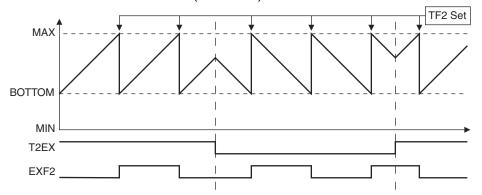

Figure 12-4. Timer 2 Waveform: Auto-Reload Mode (DCEN = 1)

Figure 12-5. Timer 2 Diagram: Auto-Reload Mode (DCEN = 1)

The timer overflow/underflow rate for up-down counting mode is the same as for up counting mode, provided that the count direction does not change. Changes to the count direction may result in longer or shorter periods between time-outs.

#### 12.4 Baud Rate Generator

Timer 2 is selected as the baud rate generator by setting TCLK and/or RCLK in T2CON (Table 12-3). Note that the baud rates for transmit and receive can be different if Timer 2 is used for the receiver or transmitter and Timer 1 is used for the other function. Setting RCLK and/or TCLK puts Timer 2 into its baud rate generator mode, as shown in Figure 12-6.

The baud rate generator mode is similar to the auto-reload mode, in that a rollover in TH2 causes the Timer 2 registers to be reloaded with the 16-bit value in registers RCAP2H and RCAP2L, which are preset by software.

The baud rates in UART Modes 1 and 3 are determined by Timer 2's overflow rate according to the following equation.

Modes 1 and 3 Baud Rates =

$$\frac{\text{Timer 2 Overflow Rate}}{16}$$

The Timer can be configured for either timer or counter operation. In most applications, it is configured for timer operation ( $CP/\overline{T2} = 0$ ). The baud rate formulas are given below.

$$\frac{\text{Modes 1, 3}}{\text{Baud Rate}} = \frac{\text{System Frequency}}{16 \times (\text{TPS} + 1) \times [65536 - (\text{RCAP2H,RCAP2L})]}$$

where (RCAP2H, RCAP2L) is the content of RCAP2H and RCAP2L taken as a 16-bit unsigned integer.

Timer 2 as a baud rate generator is shown in Figure 12-6. This figure is valid only if RCLK or TCLK = 1 in T2CON. Note that a rollover in TH2 does not set TF2 and will not generate an interrupt. Note too, that if EXEN2 is set, a 1-to-0 transition in T2EX will set EXF2 but will not cause a reload from (RCAP2H, RCAP2L) to (TH2, TL2). Thus when Timer 2 is in use as a baud rate generator, T2EX can be used as an extra external interrupt. Also note that the Baud Rate and Frequency Generator modes may be used simultaneously.

# 13. External Interrupts

The INTO (P3.2) and INT1 (P3.3) pins of the AT89LP51/52 may be used as external interrupt sources. The external interrupts can be programmed to be level-activated or transition-activated by setting or clearing bit IT1 or IT0 in Register TCON. If ITx = 0, external interrupt x is triggered by a detected low at the  $\overline{\text{INTx}}$  pin. If  $\overline{\text{ITx}} = 1$ , external interrupt x is edge-triggered. In this mode if successive samples of the INTx pin show a high in one cycle and a low in the next cycle, interrupt request flag IEx in TCON is set. Flag bit IEx then requests the interrupt. Since the external interrupt pins are sampled once each clock cycle, an input high or low should hold for at least 2 system periods to ensure sampling. If the external interrupt is transition-activated, the external source has to hold the request pin high for at least two clock cycles, and then hold it low for at least two clock cycles to ensure that the transition is seen so that interrupt request flag IEx will be set. IEx will be automatically cleared by the CPU when the service routine is called if generated in edge-triggered mode. If the external interrupt is level-activated, the external source has to hold the request active until the requested interrupt is actually generated. Then the external source must deactivate the request before the interrupt service routine is completed, or else another interrupt will be generated. Both INTO and INT1 may wake up the device from the Power-down state.

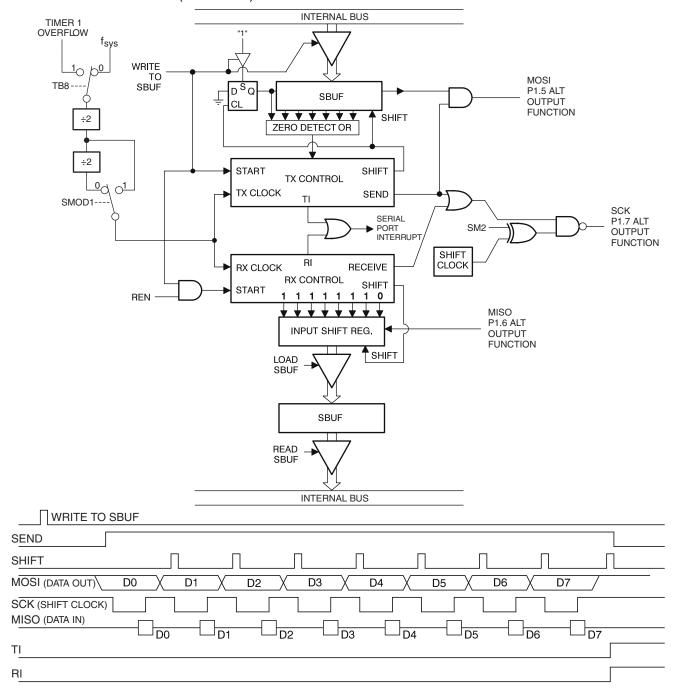

# 14. Serial Interface (UART)

The serial interface on the AT89LP51/52 implements a Universal Asynchronous Receiver/Transmitter (UART). The UART has the following features:

- Full-duplex Operation

- 8 or 9 Data Bits

- Framing Error Detection

- Multiprocessor Communication Mode with Automatic Address Recognition

- Baud Rate Generator Using Timer 1 or Timer 2

- Interrupt on Receive Buffer Full or Transmission Complete

- Synchronous SPI or TWI Master Emulation

The serial interface is full-duplex, which means it can transmit and receive simultaneously. It is also receive-buffered, which means it can begin receiving a second byte before a previously received byte has been read from the receive register. (However, if the first byte still has not been read when reception of the second byte is complete, one of the bytes will be lost.) The serial port receive and transmit registers are both accessed at the Special Function Register SBUF. Writing to SBUF loads the transmit register, and reading SBUF accesses a physically separate receive register. The serial port can operate in the following four modes.

- Mode 0: Serial data enters and exits through RXD. TXD outputs the shift clock. Eight data bits are transmitted/received, with the LSB first. The baud rate is programmable to 1/6 or 1/3 the system frequency in Compatibility mode, 1/4 or 1/2 the system frequency in Fast mode, or variable based on Time 1.

- **Mode 1:** 10 bits are transmitted (through TXD) or received (through RXD): a start bit (0), 8 data bits (LSB first), and a stop bit (1). On receive, the stop bit goes into RB8 in the Special Function Register SCON. The baud rate is variable based on Timer 1 or Timer 2.

- Mode 2: 11 bits are transmitted (through TXD) or received (through RXD): a start bit (0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (1). On transmit, the 9th data bit (TB8 in SCON) can be assigned the value of "0" or "1". For example, the parity bit (P, in the PSW) can be moved into TB8. On receive, the 9th data bit goes into RB8 in the

Figure 14-5. Serial Port Mode 0 (Three-Wire)

# 15. Programmable Watchdog Timer

The programmable Watchdog Timer (WDT) protects the system from incorrect execution by triggering a system reset when it times out after the software has failed to feed the timer prior to the timer overflow. By Default the WDT counts CPU clock cycles. The prescaler bits, PS0, PS1 and PS2 in SFR WDTCON are used to set the period of the Watchdog Timer from 16K to 2048K clock cycles. The Timer Prescaler can also be used to lengthen the time-out period (see Table 6-2 on page 31) The WDT is disabled by Reset and during Power-down mode. When the WDT times out without being serviced, an internal RST pulse is generated to reset the CPU. See Table 15-1 for the available WDT period selections.

| Tational of Time and Selection |                    |                       |                |  |  |  |  |  |  |

|--------------------------------|--------------------|-----------------------|----------------|--|--|--|--|--|--|

|                                | WDT Prescaler Bits | Period <sup>(1)</sup> |                |  |  |  |  |  |  |

| PS2                            | PS1                | PS0                   | (Clock Cycles) |  |  |  |  |  |  |

| 0                              | 0                  | 0                     | 16K            |  |  |  |  |  |  |

| 0                              | 0                  | 1                     | 32K            |  |  |  |  |  |  |

| 0                              | 1                  | 0                     | 64K            |  |  |  |  |  |  |

| 0                              | 1                  | 1                     | 128K           |  |  |  |  |  |  |

| 1                              | 0                  | 0                     | 256K           |  |  |  |  |  |  |

| 1                              | 0                  | 1                     | 512K           |  |  |  |  |  |  |

| 1                              | 1                  | 0                     | 1024K          |  |  |  |  |  |  |

| 1                              | 1                  | 1                     | 2048K          |  |  |  |  |  |  |

Table 15-1.

Watchdog Timer Time-out Period Selection

Note: 1. The WDT time-out period is dependent on the system clock frequency.

Time-out Period =

$$\frac{2^{(PS+14)}}{System\ Frequency} \times (TPS+1)$$

The Watchdog Timer consists of a 14-bit timer with 7-bit programmable prescaler. Writing the sequence 1EH/E1H to the WDTRST register enables the timer. When the WDT is enabled, the WDTEN bit in WDTCON will be set to "1". To prevent the WDT from generating a reset when if overflows, the watchdog feed sequence must be written to WDTRST before the end of the time-out period. To feed the watchdog, two write instructions must be sequentially executed successfully. Between the two write instructions, SFR reads are allowed, but writes are not allowed. The instructions should move 1EH to the WDTRST register and then 1EH to the WDTRST register. An incorrect feed or enable sequence will cause an immediate watchdog reset. The program sequence to feed or enable the watchdog timer is as follows:

MOV WDTRST, #01Eh MOV WDTRST, #0E1h

#### 15.1 Software Reset

A Software Reset of the AT89LP51/52 is accomplished by writing the software reset sequence 5AH/A5H to the WDTRST SFR. The WDT does not need to be enabled to generate the software reset. A normal software reset will set the SWRST flag in WDTCON. However, if at any time an incorrect sequence is written to WDTRST (i.e. anything other than 1EH/E1H or 5AH/A5H), a software reset will immediately be generated and both the SWRST and WDTOVF flags will be set. In this manner an intentional software reset may be distinguished from a software error-generated reset. The program sequence to generate a software reset is as follows:

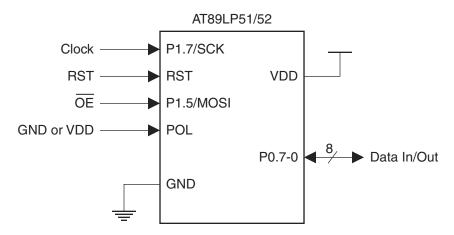

The Parallel interface is a special mode of the serial interface, i.e. the serial interface is used to enable the parallel interface. After enabling the interface serially over P1.7/SCK and P1.5/MOSI, P1.5 is reconfigured as an active-low output enable ( $\overline{OE}$ ) for data on Port 0. When  $\overline{OE} = 1$ , command, address and write data bytes are input on Port 0 and sampled at the rising edge of SCK. When  $\overline{OE} = 0$ , read data bytes are output on Port 0 and should be sampled on the falling edge of SCK. The P1.7/SCK and RST pins continue to function in the same manner. With the addition of VDD and GND, the parallel interface requires a minimum of fourteen connections as shown in Figure 17-2. Note that a connection to P1.6/MISO is not required for using the parallel interface.

Figure 17-2. Parallel Programming Device Connections

The Programming Interface is the only means of externally programming the AT89LP51/52 microcontroller. The Interface can be used to program the device both in-system and in a standalone serial programmer. The Interface does not require any clock other than SCK and is not limited by the system clock frequency. During Programming the system clock source of the target device can operate normally.

When designing a system where In-System Programming will be used, the following observations must be considered for correct operation:

- The ISP interface uses the SPI clock mode 0 (CPOL = 0, CPHA = 0) exclusively with a maximum frequency of 5 MHz.

- The AT89LP51/52 will enter programming mode only when its reset line (RST) is active. To simplify this operation, it is recommended that the target reset can be controlled by the In-System programmer. To avoid problems, the In-System programmer should be able to keep the entire target system reset for the duration of the programming cycle. The target system should never attempt to drive the three SPI lines while reset is active.

- The ISP Enable Fuse must be set to allow programming during any reset period. If the ISP Fuse is disabled, ISP may only be entered at POR. To enter programming the RST pin must be driven active prior to the end of Power-On Reset (POR). After POR has completed the device will remain in ISP mode until RST is brought inactive. Once the initial ISP session has ended, the power to the target device must be cycled OFF and ON to enter another session. Note that if this method is required, an active-low reset polarity is recommended.

- For standalone programmers, an active-low reset polarity is recommended (POL = 0). RST may then be tied directly to GND to ensure correct entry into Programming mode regardless of the device settings.

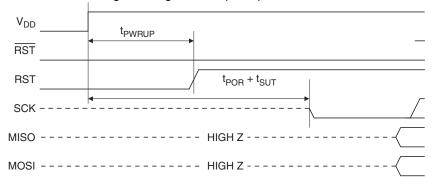

Figure 17-9. Serial Programming Power-up Sequence

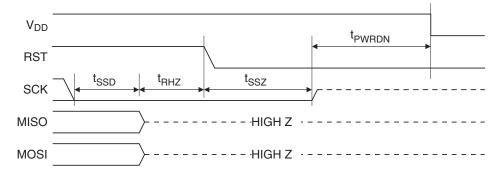

### 17.9.2 Power-down Sequence

Execute this sequence to power-down the device after programming.

- 1. Drive SCK low.

- 2. Wait at least t<sub>SSD</sub> and Tristate MOSI.

- 3. Wait at least  $t_{RHZ}$  and drive RST low.

- 4. Wait at least t<sub>SSZ</sub> and tristate SCK.

- 5. Wait no more than  $t_{PWRDN}$  and power off VDD.

Figure 17-10. Serial Programming Power-down Sequence

#### 17.9.3 ISP Start Sequence

Execute this sequence to exit CPU execution mode and enter ISP mode when the device has passed Power-On Reset and is already operational.

- 1. Drive RST high.

- 2. Wait  $t_{RLZ} + t_{STL}$ .

- 3. Drive SCK low.

- 4. Start programming session.

- 2. Minimum V<sub>DD</sub> for Power-down is 2V.

- 3. Inputs are TTL-compatible when  $V_{DD}$  is  $5V \pm 10\%$

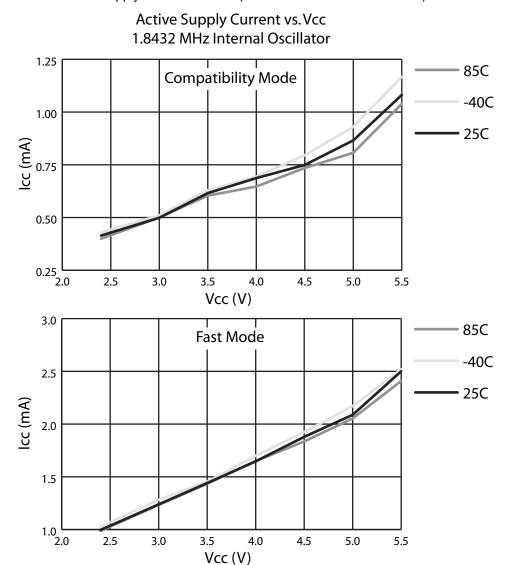

# 18.3 Typical Characteristics

The following charts show typical behavior. These figures are not tested during manufacturing. All current consumption measurements are performed with all I/O pins configured as quasi-bidirectional (with internal pull-ups). A square wave generator with rail-to-rail output is used as an external clock source for consumption versus frequency measurements.

### **18.3.1** Supply Current (Internal Oscillator)

Figure 18-1. Active Supply Current vs. Vcc (1.8432 MHz Internal Oscillator)

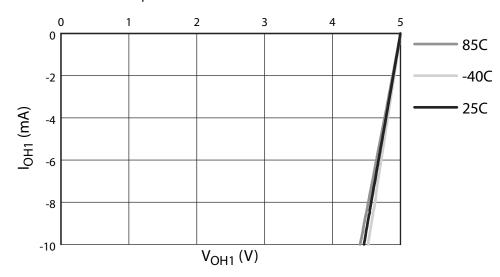

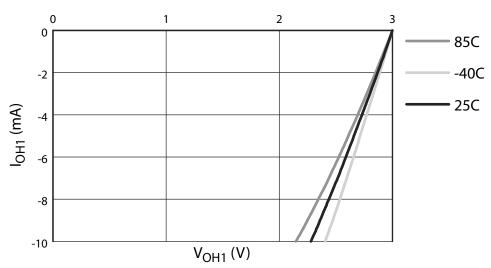

# 18.3.5 Push-Pull Output

Figure 18-9. Push-Pull Output I-V Source Characteristic at 5V

Figure 18-10. Push-Pull Output I-V Source Characteristic at 3V

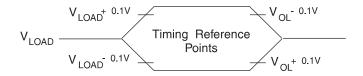

### 18.8.2 Float Waveform<sup>(1)</sup>

Note: 1. For timing purposes, a port pin is no longer floating when a 100 mV change from load voltage occurs. A port pin begins to float when 100 mV change from the loaded V<sub>OH</sub>/V<sub>OL</sub> level occurs.

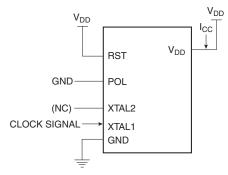

# 18.8.3 I<sub>CC</sub> Test Condition, Active Mode, All Other Pins are Disconnected<sup>(1)</sup>

Notes: 1. For active supply current measurements all ports are configured in quasi-bidirectional mode. Timers 0, 1 and 2 are configured to be free running in their default timer modes. The CPU executes a simple random number generator that accesses RAM and SFR bus, and exercises the ALU and hardware multiplier.

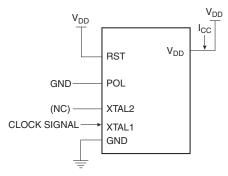

## 18.8.4 I<sub>CC</sub> Test Condition, Idle Mode, All Other Pins are Disconnected

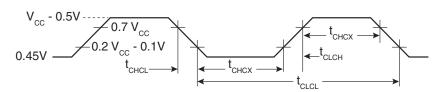

### 18.8.5 Clock Signal Waveform for $I_{CC}$ Tests in Active and Idle Modes, $t_{CLCH} = t_{CHCL} = 5$ ns

### 20.3 44J - PLCC

10/04/01

0.533

1.270 TYP

| 0005 Onels and Davidson                    | TITLE                                              | DRAWING NO. | REV. |

|--------------------------------------------|----------------------------------------------------|-------------|------|

| 2325 Orchard Parkway<br>San Jose, CA 95131 | 44J, 44-lead, Plastic J-leaded Chip Carrier (PLCC) | 44J         | В    |

В1

е

0.330

material condition at the upper or lower parting line. 3. Lead coplanarity is 0.004" (0.102 mm) maximum.

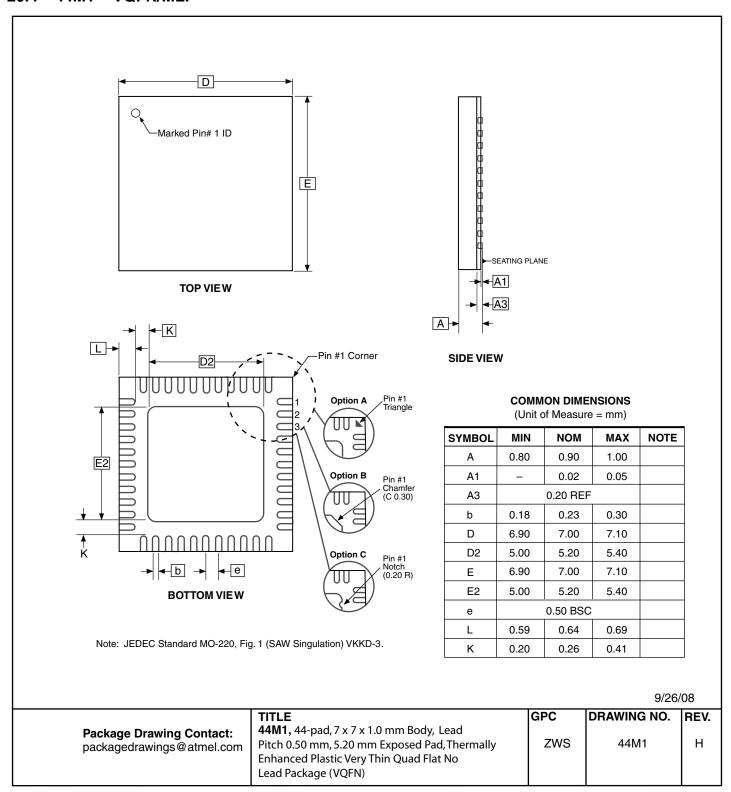

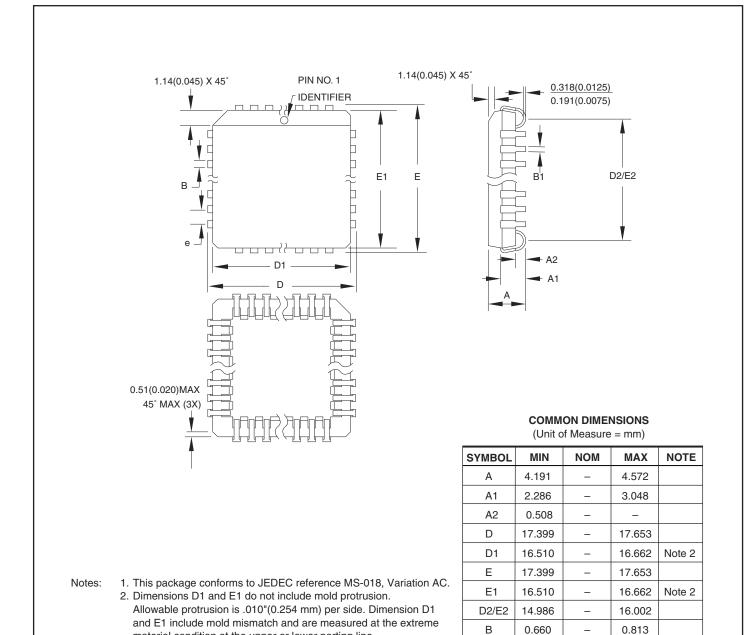

#### 20.4 44M1 - VQFN/MLF