Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 8051                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                              |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 36                                                                      |

| Program Memory Size        | 4KB (4K x 8)                                                            |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 256 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.4V ~ 5.5V                                                             |

| Data Converters            | -                                                                       |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at89lp51-20pu |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

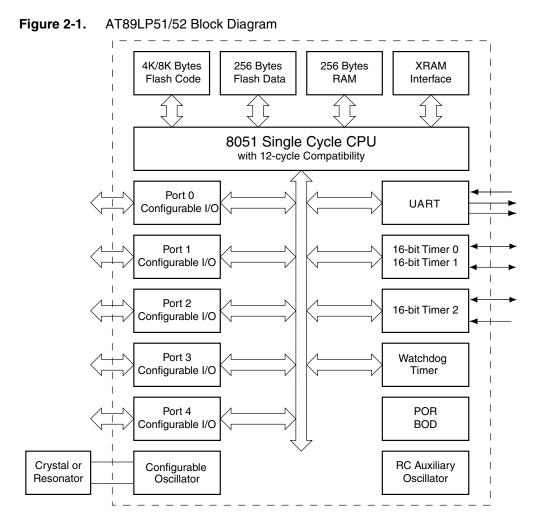

# 2. Overview

The AT89LP51/52 is a low-power, high-performance CMOS 8-bit microcontroller with 4K/8K bytes of In-System Programmable Flash program memory and 256 bytes of Flash data memory. The device is manufactured using Atmel's high-density nonvolatile memory technology and is compatible with the industry-standard 80C52 instruction set.

The AT89LP51/52 is built around an enhanced CPU core that can fetch a single byte from memory every clock cycle. In the classic 8051 architecture, each fetch requires 6 clock cycles, forcing instructions to execute in 12, 24 or 48 clock cycles. In the AT89LP51/52 CPU, instructions need only 1 to 4 clock cycles providing 6 to 12 times more throughput than the standard 8051. Seventy percent of instructions need only as many clock cycles as they have bytes to execute, and most of the remaining instructions require only one additional clock. The enhanced CPU core is capable of 20 MIPS throughput whereas the classic 8051 CPU can deliver only 4 MIPS at the same current consumption. Conversely, at the same throughput as the classic 8051, the new CPU core runs at a much lower speed and thereby greatly reducing power consumption and EMI. The AT89LP51/52 also includes a compatibility mode that will enable classic 12 clock per machine cycle operation for true timing compatibility with AT89S51/52.

The AT89LP51/52 provides the following standard features: 4K/8K bytes of In-System Programmable Flash program memory, 256 bytes of Flash data memory, 256 bytes of RAM, up to 36 I/O lines, three 16-bit timer/counters, a programmable watchdog timer, a full-duplex serial port, an on-chip crystal oscillator, an internal 1.8432 MHz auxiliary oscillator, and a four-level, six-vector interrupt system. A block diagram is shown in Figure 2-1.

#### **Key Benefits:**

- Full software and timing compatibility with AT89S52 means no changes to existing software, including fetching from external ROM or read/write from/to external RAM

- Disable compatibility mode to achieve on average 9 times more throughput at the same current consumption and frequency as AT89S52; or lower the clock frequency 9 times and achieve the same speed as AT89S52 but with more than 5 times less current consumption

- Save even more power and the cost of a quartz crystal by using the internal 1.8432 MHz RC oscillator, which is Vcc and temperature compensated well enough to ensure proper UART serial communications. Together with the built-in POR and the BOD circuits, you do not need any external components for AT89LP52 to provide the reset and clock functions

- All three timer/counters of the AT89LP51/52, Timer 0, Timer 1 and Timer 2, can be configured to toggle a port pin on overflow for clock/waveform generation. Unlike AT89S51, Timer 2 is also present on AT89LP51

- The enhanced full-duplex UART of the AT89LP51/52 includes Framing Error Detection and Automatic Address Recognition. In addition, enhancements to Mode 0 allow hardware accelerated emulation of a master SPI or TWI

- Use In-Application Programming to alter the built-in 8K Flash program memory while executing the application, in effect making it possible to have programmable data tables embedded in the program code. Or use the 256-byte Flash Data memory for nonvolatile data storage

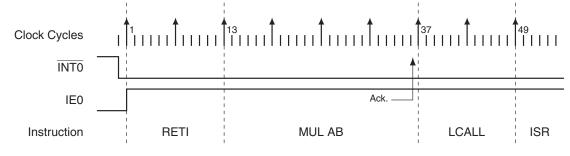

- Each 8-bit I/O port of the AT89LP51/52 can be independently configured in one of four operating modes. In quasi-bidirectional mode, the port operates as in the classic 8051. In input-only mode, the port is tristated. Push-pull output mode provides full CMOS drivers and open-drain mode provides just a pull-down. Unlike other 8051s, this allows Port 0 to operate with on-chip pull-ups if desired

# 2.1 Block Diagram

# 2.2 System Configuration

The AT89LP51/52 supports several system configuration options. Nonvolatile options are set through user fuses that must be programmed through the flash programming interface. Volatile options are controlled by software through individual bits of special function registers (SFRs). The AT89LP51/52 must be properly configured before correct operation can occur.

#### 2.2.1 Fuse Options

Table 2-1 lists the fusable options for the AT89LP51/52. These options maintain their state even when the device is powered off, but can only be changed with an external device programmer. For more information, see Section 17.7 "User Configuration Fuses" on page 86.

access the code memory. The User Signature Array may also be modified by the In-Application Programming interface. When IAP = 1 and SIGEN = 1, MOVX @DPTR instructions will access the array (See Section 3.4 on page 23).

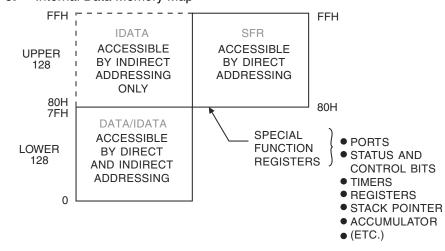

### 3.2 Internal Data Memory

The AT89LP51/52 contains 256 bytes of general SRAM data memory plus 128 bytes of I/O memory mapped into a single 8-bit address space. Access to the internal data memory does not require any configuration. The internal data memory has three address spaces: DATA, IDATA and SFR; as shown in Figure 3-5. Some portions of external data memory are also implemented internally. See "External Data Memory" below for more information.

#### Figure 3-5. Internal Data Memory Map

#### 3.2.1 DATA

The first 128 bytes of RAM are directly addressable by an 8-bit address (00H–7FH) included in the instruction. The lowest 32 bytes of DATA memory are grouped into 4 banks of 8 registers each. The RS0 and RS1 bits (PSW.3 and PSW.4) select which register bank is in use. Instructions using register addressing will only access the currently specified bank. The lower 128 bit addresses are also mapped into DATA addresses 20H–2FH.

3.2.2 IDATA

The full 256 byte internal RAM can be indirectly addressed using the 8-bit pointers R0 and R1. The first 128 bytes of IDATA include the DATA space. The hardware stack is also located in the IDATA space.

3.2.3 SFR

The upper 128 direct addresses (80H–FFH) access the I/O registers. I/O registers on AT89LP devices are referred to as Special Function Registers. The SFRs can only be accessed through direct addressing. All SFR locations are not implemented. See Section 4. for a listed of available SFRs.

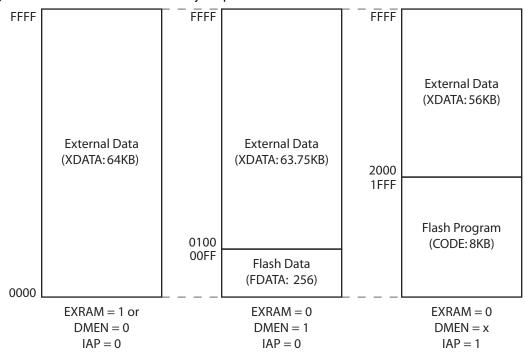

#### 3.3 External Data Memory

AT89LP microcontrollers support a 16-bit external memory address space for up to 64K bytes of external data memory (XDATA). The external memory space is accessed with the MOVX instructions. Some internal data memory resources are mapped into portions of the external

# 14 AT89LP51/52 I

address space as shown in Figure 3-6. These memory spaces may require configuration before the CPU can access them. The AT89LP51/52 includes 256 bytes of nonvolatile Flash data memory (FDATA).

#### 3.3.1 XDATA

The external data memory space can accommodate up to 64KB of external memory. The AT89LP51/52 uses the standard 8051 external data memory interface with the upper address byte on Port 2, the lower address byte and data in/out multiplexed on Port 0, and the ALE,  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  strobes. XDATA can be accessed with both 16-bit (MOVX @DPTR) and 8-bit (MOVX @Ri) addresses. See Section 3.3.3 on page 18 for more details of the external memory interface.

Some internal data memory spaces are mapped into portions of the XDATA address space. In this case the lower address ranges will access internal resources instead of external memory. Addresses above the range implemented internally will default to XDATA. The AT89LP51/52 supports up to 63.75K or 56K bytes of external memory when using the internally mapped memories. Setting the EXRAM bit (AUXR.1) to one will force all MOVX instructions to access the entire 64KB XDATA regardless of their address (See "AUXR – Auxiliary Control Register" on page 20).

Figure 3-6. External Data Memory Map

#### 3.3.2 FDATA

The Flash Data Memory is a portion of the external memory space implemented as an internal nonvolatile data memory. Flash Data Memory is enabled by setting the DMEN bit (MEMCON.3) to one. When IAP = 0 and DMEN = 1, the Flash Data Memory is mapped into the FDATA space, at the bottom of the external memory address space, from 0000H to 00FFH. (See Figure 3-6). MOVX instructions to this address range will access the internal nonvolatile memory. FDATA is

# 3.4 In-Application Programming (IAP)

The AT89LP51/52 supports In-Application Programming (IAP), allowing the program memory to be modified during execution. IAP can be used to modify the user application on the fly or to use program memory for nonvolatile data storage. The same page structure write protocol for FDATA also applies to IAP (See Section 3.3.2.1 "Write Protocol" on page 16). The CPU is always placed in idle while modifying the program memory. When the write completes, the CPU will continue executing with the instruction after the MOVX @DPTR,A instruction that started the write.

To enable access to the program memory, the IAP bit (MEMCON.7) must be set to one and the IAP User Fuse must be enabled. The IAP User Fuse can disable all IAP operations. When this fuse is disabled, the IAP bit will be forced to 0. While IAP is enabled, all MOVX @DPTR instructions will access the CODE space instead of EDATA/FDATA/XDATA. IAP also allows reprogramming of the User Signature Array when SIGEN = 1. The IAP access settings are summarized in Table 3-4 and Table 3-5.

| IAP | SIGEN | DMEN | MOVX @DPTR                               | MOVC @DPTR                              |

|-----|-------|------|------------------------------------------|-----------------------------------------|

| 0   | 0     | 0    | XDATA (0000–FFFFH)                       | CODE (0000–1FFFH)<br>XCODE (2000–FFFFH) |

| 0   | 0     | 1    | FDATA (0000–00FFH)<br>XDATA (0100–FFFFH) | CODE (0000–1FFFH)<br>XCODE (2000–FFFFH) |

| 0   | 1     | 0    | XDATA (0000–FFFFH)                       | SIG (0000–01FFH)                        |

| 0   | 1     | 1    | FDATA (0000–00FFH)<br>XDATA (0100–FFFFH) | SIG (0000–01FFH)                        |

| 1   | 0     | х    | CODE (0000–1FFFH)<br>XDATA (2000–FFFFH)  | CODE (0000–1FFFH)<br>XCODE (2000–FFFFH) |

| 1   | 1     | х    | SIG (0000–01FFH)<br>XDATA (2000–FFFFH)   | SIG (0000–01FFH)                        |

Table 3-4.

IAP Access Settings for AT89LP52

| Table 3-5. | IAP Access Settings for AT89LP51 |

|------------|----------------------------------|

|------------|----------------------------------|

| IAP | SIGEN | DMEN | MOVX @DPTR                               | MOVC @DPTR                              |

|-----|-------|------|------------------------------------------|-----------------------------------------|

| 0   | 0     | 0    | XDATA (0000–FFFFH)                       | CODE (0000–0FFFH)<br>XCODE (1000–FFFFH) |

| 0   | 0     | 1    | FDATA (0000–00FFH)<br>XDATA (0100–FFFFH) | CODE (0000–0FFFH)<br>XCODE (1000–FFFFH) |

| 0   | 1     | 0    | XDATA (0000–FFFFH)                       | SIG (0000–01FFH)                        |

| 0   | 1     | 1    | FDATA (0000–00FFH)<br>XDATA (0100–FFFFH) | SIG (0000–01FFH)                        |

| 1   | 0     | х    | CODE (0000–0FFFH)<br>XDATA (1000–FFFFH)  | CODE (0000–0FFFH)<br>XCODE (1000–FFFFH) |

| 1   | 1     | х    | SIG (0000–01FFH)<br>XDATA (1000–FFFFH)   | SIG (0000–01FFH)                        |

Note: When In-Application programming is not required, it is recommended that the IAP User Fuse be disabled.

| Table 5-2. | Data Pointer Decrement Behavior |

|------------|---------------------------------|

|------------|---------------------------------|

|      |      | Equivalent Operation for INC DPTR and INC /DPTR |           |           |           |  |  |  |

|------|------|-------------------------------------------------|-----------|-----------|-----------|--|--|--|

|      |      | DPS                                             | 6 = 0     | DPS       | 6 = 1     |  |  |  |

| DPD1 | DPD0 | INC DPTR                                        | INC /DPTR | INC DPTR  | INC /DPTR |  |  |  |

| 0    | 0    | INC DPTR0                                       | INC DPTR1 | INC DPTR1 | INC DPTR0 |  |  |  |

| 0    | 1    | DEC DPTR0                                       | INC DPTR1 | INC DPTR1 | DEC DPTR0 |  |  |  |

| 1    | 0    | INC DPTR0                                       | DEC DPTR1 | DEC DPTR1 | INC DPTR0 |  |  |  |

| 1    | 1    | DEC DPTR0                                       | DEC DPTR1 | DEC DPTR1 | DEC DPTR0 |  |  |  |

| AUXR   | AUXR1 = A2H Reset Value = 0000 00X0B                                                                                                                                                                                                                           |                                                  |              |      |       |   |   |     |  |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------|------|-------|---|---|-----|--|

| Not Bi | t Addressable                                                                                                                                                                                                                                                  |                                                  |              |      |       |   |   |     |  |

|        | DPU1                                                                                                                                                                                                                                                           | DPU0                                             | DPD1         | DPD0 | SIGEN | 0 | - | DPS |  |

| Bit    | 7                                                                                                                                                                                                                                                              | 6                                                | 5            | 4    | 3     | 2 | 1 | 0   |  |

| Symbol | Function                                                                                                                                                                                                                                                       |                                                  |              |      |       |   |   |     |  |

| DPU1   | DPTR1 base                                                                                                                                                                                                                                                     | 1 Update. Whe<br>ed on DPD1. If<br>= 0, DPTR1 is | DPD1 = 0 the |      |       |   |   |     |  |

| DPU0   | Data Pointer 0 Update. When set, MOVX @DPTR and MOVC @DPTR instructions that use DPTR0 will also update DPTR0 based on DPD0. If DPD0 = 0 the operation is post-increment and if DPD0 = 1 the operation is post-decrement. When DPU0 = 0, DPTR0 is not updated. |                                                  |              |      |       |   |   |     |  |

| DPD1   | Data Pointer 1 Decrement. When set, INC DPTR instructions targeted to DPTR1 will decrement DPTR1. When cleared, INC DPTR instructions will increment DPTR1. DPD1 also determines the direction of auto-update for DPTR1 when DPU1 = 1.                         |                                                  |              |      |       |   |   |     |  |

| DPD0   | Data Pointer 0 Decrement. When set, INC DPTR instructions targeted to DPTR0 will decrement DPTR0. When cleared, INC DPTR instructions will increment DPTR0. DPD0 also determines the direction of auto-update for DPTR0 when DPU0 = 1.                         |                                                  |              |      |       |   |   |     |  |

| SIGEN  | Signature Enable. When SIGEN = 1 all MOVC @DPTR instructions and all IAP accesses will target the signature array memory. When SIGEN = 0, all MOVC and IAP accesses target CODE memory.                                                                        |                                                  |              |      |       |   |   |     |  |

| DPS    |                                                                                                                                                                                                                                                                | Select. DPS se<br>0 and /DPTR w                  |              | •    |       |   |   |     |  |

The data pointer update bits, DPU1 and DPU0, allow MOVX @DPTR and MOVC @DPTR instructions to update the selected data pointer automatically in a post-increment or post-decrement fashion. The direction of update depends on the DPD1 and DPD0 bits as shown in Table 5-4. These bits can be used to make block copy routines more efficient.

|      |      | Update Operation for MOVX and MOVC (DPU1 = 1 & DPU0 = 1) |         |         |         |  |  |  |

|------|------|----------------------------------------------------------|---------|---------|---------|--|--|--|

|      |      | DPS                                                      | S = 0   | DPS     | 6 = 1   |  |  |  |

| DPD1 | DPD0 | DPTR                                                     | /DPTR   | DPTR    | /DPTR   |  |  |  |

| 0    | 0    | DPTR0++                                                  | DPTR1++ | DPTR1++ | DPTR0++ |  |  |  |

| 0    | 1    | DPTR0                                                    | DPTR1++ | DPTR1++ | DPTR0   |  |  |  |

| 1    | 0    | DPTR0++                                                  | DPTR1   | DPTR1   | DPTR0++ |  |  |  |

| 1    | 1    | DPTR0                                                    | DPTR1   | DPTR1   | DPTR0   |  |  |  |

Table 5-4.Data Pointer Auto-Update

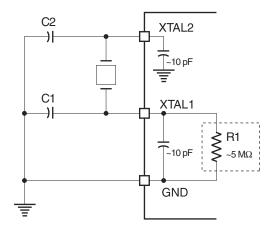

An optional 5 M $\Omega$  on-chip resistor can be connected between XTAL1 and GND. This resistor can improve the startup characteristics of the oscillator especially at higher frequencies. The resistor can be enabled/disabled with the R1 User Fuse (See "User Configuration Fuses" on page 86.)

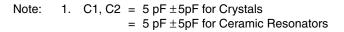

### 6.2 External Clock Source

The external clock option disables the oscillator amplifier and allows XTAL1 to be driven directly by an external clock source as shown in Figure 6-3. XTAL2 may be left unconnected, used as general purpose I/O P4.7, or configured to output a divided version of the system clock.

Figure 6-3. External Clock Drive Configuration

## 6.3 Internal RC Oscillator

The AT89LP51/52 has an Internal Auxiliary oscillator tuned to 1.8432 MHz  $\pm$ 2.0%. When enabled as the clock source, XTAL1 and XTAL2 may be used as P4.6 and P4.7 respectively.

CPU when an interrupt is generated. The timer and UART peripherals continue to function during Idle. If these functions are not needed during idle, they should be explicitly disabled by clearing the appropriate control bits in their respective SFRs. The watchdog may be selectively enabled or disabled during Idle by setting/clearing the WDIDLE bit. The Brown-out Detector is always active during Idle. Any enabled interrupt source or reset may terminate Idle mode. When exiting Idle mode with an interrupt, the interrupt will immediately be serviced, and following RETI the next instruction to be executed will be the one following the instruction that put the device into Idle.

The power consumption during Idle mode can be further reduced by prescaling down the system clock using the System Clock Divider (Section 6.4 on page 31). Be aware that the clock divider will affect all peripheral functions and baud rates may need to be adjusted to maintain their rate with the new clock frequency.

| Table 8-1. | PCON – Power Control Register |

|------------|-------------------------------|

|------------|-------------------------------|

| PCON   | PCON = 87H Reset Value = 000X 0000                                           |                                                                                                                                                                 |       |     |     |     |    |     |  |  |

|--------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-----|-----|----|-----|--|--|

| Not Bi | t Addressable                                                                |                                                                                                                                                                 |       |     |     |     |    |     |  |  |

|        | SMOD1                                                                        | SMOD0                                                                                                                                                           | PWDEX | POF | GF1 | GF0 | PD | IDL |  |  |

| Bit    | 7                                                                            | 6                                                                                                                                                               | 5     | 4   | 3   | 2   | 1  | 0   |  |  |

| Symbol | Function                                                                     |                                                                                                                                                                 |       |     |     |     |    |     |  |  |

| SMOD1  | Double Baud Rate bit. Doubles the baud rate of the UART in Modes 1, 2, or 3. |                                                                                                                                                                 |       |     |     |     |    |     |  |  |

| SMOD0  |                                                                              | Frame Error Select. When SMOD0 = 1, SCON.7 is SM0. When SMOD0 = 1, SCON.7 is FE. Note that FE will be set after a frame error regardless of the state of SMOD0. |       |     |     |     |    |     |  |  |

|          | -                                                                                                                                                                        |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWDEX    | Power-down Exit Mode. When PWDEX = 0, wake up from Power-down is externally controlled. When PWDEX = 1, wake up from Power-down is internally timed.                     |

| POF      | Power Off Flag. POF is set to "1" during power up (i.e. cold reset). It can be set or reset under software control and is not affected by RST or BOD (i.e. warm resets). |

| GF1, GF0 | General-purpose Flags                                                                                                                                                    |

| PD       | Power-down bit. Setting this bit activates power-down operation. The PD bit is cleared automatically by hardware when waking up from power-down.                         |

# IDL Idle Mode bit. Setting this bit activates Idle mode operation. The IDL bit is cleared automatically by hardware when waking up from idle

# 8.2 Power-down Mode

Setting the Power-down (PD) bit in PCON enters Power-down mode. Power-down mode stops the oscillator, disables the BOD and powers down the Flash memory in order to minimize power consumption. Only the power-on circuitry will continue to draw power during Power-down. During Power-down, the power supply voltage may be reduced to the RAM keep-alive voltage. The RAM contents will be retained, but the SFR contents are not guaranteed once  $V_{DD}$  has been reduced. Power-down may be exited by external reset, power-on reset, or certain enabled interrupts.

vectored to. The Timer 2 Interrupt is generated by a logic OR of bits TF2 and EXF2 in register T2CON. Neither of these flags is cleared by hardware when the CPU vectors to the service routine. The service routine normally must determine whether TF2 or EXF2 generated the interrupt and that bit must be cleared by software.

The Serial Port Interrupt is generated by the logic OR of RI and TI in SCON. Neither of these flags is cleared by hardware when the CPU vectors to the service routine. The service routine normally must determine whether RI or TI generated the interrupt and that bit must be cleared by software.

All of the bits that generate interrupts can be set or cleared by software, with the same result as though they had been set or cleared by hardware. That is, interrupts can be generated and pending interrupts can be canceled in software.

| · · · · · · · · · · · · · · · · · · · |                   |                |  |

|---------------------------------------|-------------------|----------------|--|

| Interrupt                             | Source            | Vector Address |  |

| System Reset                          | RST or POR or BOD | 0000H          |  |

| External Interrupt 0                  | IEO               | 0003H          |  |

| Timer 0 Overflow                      | TF0               | 000BH          |  |

| External Interrupt 1                  | IE1               | 0013H          |  |

| Timer 1 Overflow                      | TF1               | 001BH          |  |

| Serial Port Interrupt                 | RI or TI          | 0023H          |  |

| Timer 2 Interrupt                     | TF2 or EXF2       | 002BH          |  |

Table 9-1. Interrupt Vector Addresses

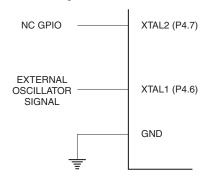

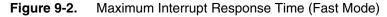

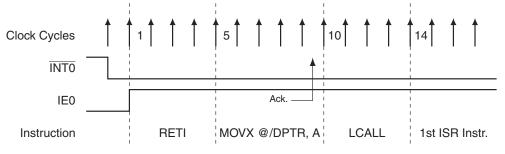

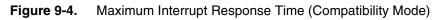

# 9.1 Interrupt Response Time

The interrupt flags may be set by their hardware in any clock cycle. The interrupt controller polls the flags in the last clock cycle of the instruction in progress. If one of the flags was set in the preceding cycle, the polling cycle will find it and the interrupt system will generate an LCALL to the appropriate service routine as the next instruction, provided that the interrupt is not blocked by any of the following conditions: an interrupt of equal or higher priority level is already in progress; the instruction in progress is RETI or any write to the IE, IP or IPH registers; the CPU is currently forced into idle by an IAP or FDATA write. Each of these conditions will block the generation of the LCALL to the interrupt service routine. The second condition ensures that if the instruction in progress is RETI or any access to IE, IP or IPH, then at least one more instruction will be executed before any interrupt is vectored to. The polling cycle is repeated at the last cycle of each instruction, and the values polled are the values that were present at the previous clock cycle. If an active interrupt flag is not being serviced because of one of the above conditions and is no longer active when the blocking condition is removed, the denied interrupt will not be serviced. In other words, the fact that the interrupt flag was once active but not serviced is not remembered. Every polling cycle is new.

If a request is active and conditions are met for it to be acknowledged, a hardware subroutine call to the requested service routine will be the next instruction executed. The call itself takes four cycles. Thus, a minimum of five complete clock cycles elapsed between activation of an interrupt request and the beginning of execution of the first instruction of the service routine. A longer response time results if the request is blocked by one of the previously listed conditions. If an interrupt of equal or higher priority level is already in progress, the additional wait time depends on the nature of the other interrupt's service routine. If the instruction in progress is not in its final clock cycle, the additional wait time cannot be more than 4 cycles, since the longest

instruction is 5 cycles long. If the instruction in progress is RETI, the additional wait time cannot be more than 9 cycles (a maximum of 4 more cycles to complete the instruction in progress, plus a maximum of 5 cycles to complete the next instruction). Thus, in a single-interrupt system, the response time is always more than 5 clock cycles and less than 14 clock cycles. See Figure 9-1 and Figure 9-2.

Figure 9-1. Minimum Interrupt Response Time (Fast Mode)

Figure 10-2. Input Only

Figure 10-3. Input Circuit for P3.2, P3.3, P4.6 and P4.7

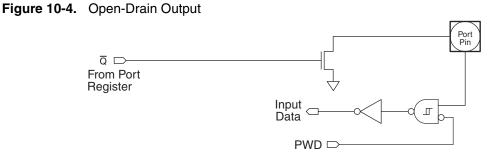

#### 10.1.3 Open-drain Output

The open-drain output configuration turns off all pull-ups and only drives the pull-down transistor of the port pin when the port latch contains a logic "0". To be used as a logic output, a port configured in this manner must have an external pull-up, typically a resistor tied to  $V_{DD}$ . The pull-down for this mode is the same as for the quasi-bidirectional mode. The open-drain port configuration is shown in Figure 10-4. The input circuitry of P3.2, P3.3, P4.6 and P4.7 is not disabled during Power-down (see Figure 10-3) and therefore these pins should not be left floating during Power-down when configured in this mode.

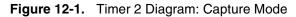

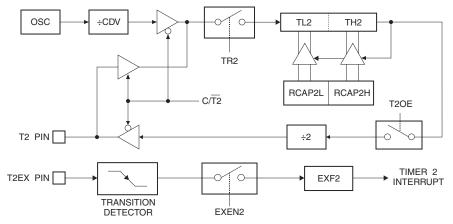

# 12.2 Capture Mode

In the Capture mode, Timer 2 is a fixed 16-bit timer or counter that counts up from MIN to MAX. An overflow from MAX to MIN sets bit TF2 in T2CON. If EXEN2 = 1, a 1-to-0 transition at external input T2EX also causes the current value in TH2 and TL2 to be captured into RCAP2H and RCAP2L, respectively. In addition, the transition at T2EX causes bit EXF2 in T2CON to be set. The EXF2 and TF2 bits can generate an interrupt. Capture mode is illustrated in Figure 12-1. The Timer 2 overflow rate in Capture mode is given by the following equation:

Capture Mode: Time-out Period =  $\frac{65536}{\text{System Frequency}} \times (\text{TPS} + 1)$

# 12.3 Auto-Reload Mode

Timer 2 can be programmed to count up or down when configured in its 16-bit auto-reload mode. This feature is invoked by the DCEN (Down Counter Enable) bit located in the SFR T2MOD (see Table 12-4). Upon reset, the DCEN bit is set to 0 so that timer 2 will default to count up. When DCEN is set, Timer 2 can count up or down, depending on the value of the T2EX pin. A summary of the Auto-Reload behaviors is listed in Table 12-5.

Table 12-5.

Summary of Auto-Reload Modes

| DCEN | T2EX | Direction | Behavior                        |

|------|------|-----------|---------------------------------|

| 0    | Х    | Up        | BOTTOM                          |

| 1    | 0    | Down      | MAX                             |

| 1    | 1    | Up        | BOTTOM – MAX overflow to BOTTOM |

#### 12.3.1 Up Counter

Figure 12-2 shows Timer 2 automatically counting up when DCEN = 0. In this mode Timer 2 counts up to MAX and then sets the TF2 bit upon overflow. The overflow also causes the timer registers to be reloaded with BOTTOM, the 16-bit value in RCAP2H and RCAP2L. If EXEN2 = 1, a 16-bit reload can be triggered either by an overflow or by a 1-to-0 transition at external input T2EX. This transition also sets the EXF2 bit. Both the TF2 and EXF2 bits can generate an interrupt. The Timer 2 overflow rate for this mode is given in the following equation:

Auto-Reload Mode:

DCEN = 0

Time-out Period =

$$\frac{65536 - \{RCAP2H, RCAP2L\}}{System Frequency} \times (TPS + 1)$$

Figure 12-6. Timer 2 in Baud Rate Generator Mode

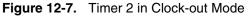

### 12.5 Frequency Generator (Programmable Clock Out)

Timer 2 can generate a 50% duty cycle clock on T2 (P1.0), as shown in Figure 13.. This pin, besides being a regular I/O pin, has two alternate functions. It can be programmed to input the external clock for Timer/Counter 2 or to toggle its output at every timer overflow. To configure the Timer/Counter 2 as a clock generator, bit C/T2 (T2CON.1) must be cleared and bit T2OE (T2MOD.1) must be set. Bit TR2 (T2CON.2) starts and stops the timer. The clock-out frequency depends on the system frequency and the reload value of Timer 2 capture registers (RCAP2H, RCAP2L), as shown in the following equation.

Clock Out Frequency =  $\frac{\text{System Frequency}}{2 \times [65536 - (\text{RCAP2H}, \text{RCAP2L})]}$

In the frequency generator mode, Timer 2 roll-overs will not generate an interrupt. This behavior is similar to when Timer 2 is used as a baud-rate generator. It is possible to use Timer 2 as a baud-rate generator and a clock generator simultaneously. Note, however, that the baud-rate and clock-out frequencies cannot be determined independently from one another since they both use RCAP2H and RCAP2L.

AT89LP51/52

### 14.6 More About Mode 1

Ten bits are transmitted (through TXD), or received (through RXD): a start bit (0), 8 data bits (LSB first), and a stop bit (1). On receive, the stop bit goes into RB8 in SCON. In the AT89LP51/52, the baud rate is determined either by the Timer 1 overflow rate, the TImer 2 overflow rate, or both. In this case one timer is for transmit and the other is for receive. Figure 14-6 shows a simplified functional diagram of the serial port in Mode 1 and associated timings for transmit and receive.

Transmission is initiated by any instruction that uses SBUF as a destination register. The "write to SBUF" signal also loads a "1" into the 9th bit position of the transmit shift register and flags the TX Control unit that a transmission is requested. Transmission actually commences at S1P1 of the machine cycle following the next rollover in the divide-by-16 counter. Thus, the bit times are synchronized to the divide-by-16 counter, not to the "write to SBUF" signal.

The transmission begins when SEND is activated, which puts the start bit at TXD. One bit time later, DATA is activated, which enables the output bit of the transmit shift register to TXD. The first shift pulse occurs one bit time after that.

As data bits shift out to the right, "0"s are clocked in from the left. When the MSB of the data byte is at the output position of the shift register, the "1" that was initially loaded into the 9th position is just to the left of the MSB, and all positions to the left of that contain "0"s. This condition flags the TX Control unit to do one last shift, then deactivate SEND and set TI. This occurs at the tenth divide-by-16 rollover after "write to SBUF."

Reception is initiated by a 1-to-0 transition detected at RXD. For this purpose, RXD is sampled at a rate of 16 times the established baud rate. When a transition is detected, the divide-by-16 counter is immediately reset, and 1FFH is written into the input shift register. Resetting the divide-by-16 counter aligns its roll-overs with the boundaries of the incoming bit times.

The 16 states of the counter divide each bit time into 16ths. At the 7th, 8th, and 9th counter states of each bit time, the bit detector samples the value of RXD. The value accepted is the value that was seen in at least 2 of the 3 samples. This is done to reject noise. In order to reject false bits, if the value accepted during the first bit time is not 0, the receive circuits are reset and the unit continues looking for another 1-to-0 transition. If the start bit is valid, it is shifted into the input shift register, and reception of the rest of the frame proceeds.

As data bits come in from the right, "1"s shift out to the left. When the start bit arrives at the leftmost position in the shift register, (which is a 9-bit register in Mode 1), it flags the RX Control block to do one last shift, load SBUF and RB8, and set RI. The signal to load SBUF and RB8 and to set RI is generated if, and only if, the following conditions are met at the time the final shift pulse is generated.

#### RI = 0 and

Either SM2 = 0, or the received stop bit = 1

If either of these two conditions is not met, the received frame is irretrievably lost. If both conditions are met, the stop bit goes into RB8, the 8 data bits go into SBUF, and RI is activated. At this time, whether or not the above conditions are met, the unit continues looking for a 1-to-0 transition in RXD.

# 14.7 More About Modes 2 and 3

Eleven bits are transmitted (through TXD), or received (through RXD): a start bit (0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (1). On transmit, the 9th data bit (TB8) can be assigned the value of "0" or "1". On receive, the 9th data bit goes into RB8 in SCON. The baud rate is programmable to either 1/16 or 1/32 of the oscillator frequency in Mode 2. Mode 3 may have a variable baud rate generated from either Timer 1 or Timer 2, depending on the state of RCLK and TCLK.

Figures 14-7 and 14-8 show a functional diagram of the serial port in Modes 2 and 3. The receive portion is exactly the same as in Mode 1. The transmit portion differs from Mode 1 only in the 9th bit of the transmit shift register.

Transmission is initiated by any instruction that uses SBUF as a destination register. The "write to SBUF" signal also loads TB8 into the 9th bit position of the transmit shift register and flags the TX Control unit that a transmission is requested. Transmission commences at S1P1 of the machine cycle following the next rollover in the divide-by-16 counter. Thus, the bit times are synchronized to the divide-by-16 counter, not to the "write to SBUF" signal.

The transmission begins when SEND is activated, which puts the start bit at TXD. One bit time later, DATA is activated, which enables the output bit of the transmit shift register to TXD. The first shift pulse occurs one bit time after that. The first shift clocks a "1" (the stop bit) into the 9th bit position of the shift register. Thereafter, only "0"s are clocked in. Thus, as data bits shift out to the right, "0"s are clocked in from the left. When TB8 is at the output position of the shift register, then the stop bit is just to the left of TB8, and all positions to the left of that contain "0"s. This condition flags the TX Control unit to do one last shift, then deactivate SEND and set TI. This occurs at the 11th divide-by-16 rollover after "write to SBUF."

Reception is initiated by a 1-to-0 transition detected at RXD. For this purpose, RXD is sampled at a rate of 16 times the established baud rate. When a transition is detected, the divide-by-16 counter is immediately reset, and 1FFH is written to the input shift register.

At the 7th, 8th and 9th counter states of each bit time, the bit detector samples the value of RXD. The value accepted is the value that was seen in at least 2 of the 3 samples. If the value accepted during the first bit time is not 0, the receive circuits are reset and the unit continues looking for another 1-to-0 transition. If the start bit proves valid, it is shifted into the input shift register, and reception of the rest of the frame proceeds.

As data bits come in from the right, "1"s shift out to the left. When the start bit arrives at the leftmost position in the shift register (which in Modes 2 and 3 is a 9-bit register), it flags the RX Control block to do one last shift, load SBUF and RB8, and set RI. The signal to load SBUF and RB8 and to set RI is generated if, and only if, the following conditions are met at the time the final shift pulse is generated:

$$RI = 0$$

, and

Either SM2 = 0 or the received 9th data bit = 1

If either of these conditions is not met, the received frame is irretrievably lost, and RI is not set. If both conditions are met, the received 9th data bit goes into RB8, and the first 8 data bits go into SBUF. One bit time later, whether the above conditions were met or not, the unit continues looking for a 1-to-0 transition at the RXD input.

Note that the value of the received stop bit is irrelevant to SBUF, RB8, or RI.

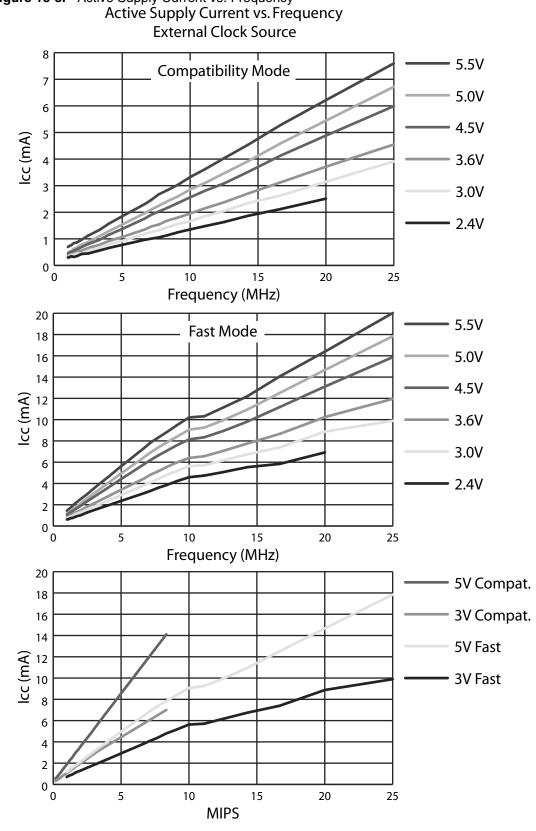

#### 18.3.2 Supply Current (External Clock)

Figure 18-3. Active Supply Current vs. Frequency

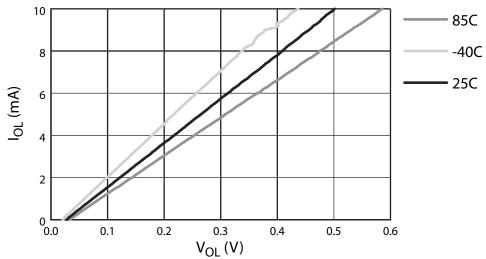

Figure 18-11. Push-Pull Output I-V Sink Characteristic at 5V

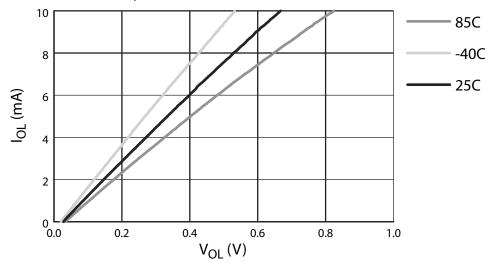

Figure 18-12. Push-Pull Output I-V Sink Characteristic at 3V

Note: The  $I_{OL}/V_{OL}$  characteristic applies to Push-Pull, Quasi-Bidirectional and Open-Drain modes.

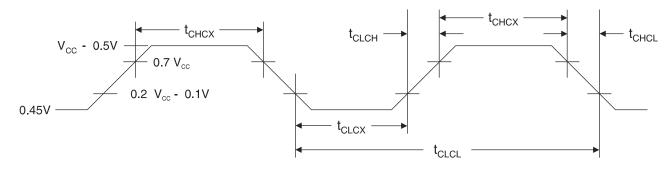

# **18.4 Clock Characteristics**

The values shown in this table are valid for  $T_A = -40^{\circ}C$  to  $85^{\circ}C$  and  $V_{DD} = 2.4$  to 5.5V, unless otherwise noted.

#### Figure 18-13. External Clock Drive Waveform

100 **AT89LP51/52**

# 19. Ordering Information

| Speed<br>(MHz) | Power<br>Supply | Code Memory | Ordering Code                                                    | Package                    | Operation Range                 |

|----------------|-----------------|-------------|------------------------------------------------------------------|----------------------------|---------------------------------|

| 20             | 2.4V to 5.5V    | 4KB         | AT89LP51-20AU<br>AT89LP51-20PU<br>AT89LP51-20JU<br>AT89LP51-20MU | 44A<br>40P6<br>44J<br>44M1 | Industrial<br>(-40° C to 85° C) |

| 20             | 2.4V to 5.5V    | 8KB         | AT89LP52-20AU<br>AT89LP52-20PU<br>AT89LP52-20JU<br>AT89LP52-20MU | 44A<br>40P6<br>44J<br>44M1 | Industrial<br>(-40° C to 85° C) |

# 19.1 Green Package Option (Pb/Halide-free)

| Package Types |                                                                                     |  |  |

|---------------|-------------------------------------------------------------------------------------|--|--|

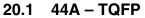

| 44 <b>A</b>   | 44-lead, Thin Plastic Quad Flat Package (TQFP)                                      |  |  |

| 40P6          | 40-lead, 0.600" Wide, Plastic Dual Inline Package (PDIP)                            |  |  |

| 44J           | 44-lead, Plastic J-leaded Chip Carrier (PLCC)                                       |  |  |

| 44M1          | 44-pad, 7 x 7 x 1.0 mm Body, Plastic Very Thin Quad Flat No Lead Package (VQFN/MLF) |  |  |

# 20. Packaging Information

# Table of Contents (Continued)

| 15 | Progra  | ammable Watchdog Timer                  | 73  |

|----|---------|-----------------------------------------|-----|

|    | 15.1    | Software Reset                          | 73  |

| 16 | Instruc | ction Set Summary                       | 75  |

| 17 | Progra  | amming the Flash Memory                 |     |

|    | 17.1    | Physical Interface                      |     |

|    | 17.2    | Memory Organization                     |     |

|    | 17.3    | Command Format                          |     |

|    | 17.4    | Status Register                         |     |

|    | 17.5    | DATA Polling                            |     |

|    | 17.6    | Flash Security                          |     |

|    | 17.7    | User Configuration Fuses                |     |

|    | 17.8    | User Signature                          |     |

|    | 17.9    | Programming Interface Timing            |     |

| 18 | Electri | cal Characteristics                     |     |

|    | 18.1    | Absolute Maximum Ratings*               |     |

|    | 18.2    | DC Characteristics                      |     |

|    | 18.3    | Typical Characteristics                 |     |

|    | 18.4    | Clock Characteristics                   |     |

|    | 18.5    | Reset Characteristics                   |     |

|    | 18.6    | External Memory Characteristics         |     |

|    | 18.7    | Serial Port Timing: Shift Register Mode |     |

|    | 18.8    | Test Conditions                         |     |

| 19 | Orderi  | ng Information                          | 107 |

|    | 19.1    | Green Package Option (Pb/Halide-free)   |     |

| 20 | Packa   | ging Information                        | 108 |

|    | 20.1    | 44A – TQFP                              |     |

|    | 20.2    | 40P6 – PDIP                             |     |

|    | 20.3    | 44J – PLCC                              |     |

|    | 20.4    | 44M1 – VQFN/MLF                         |     |

| 21 | Revisi  | on History                              | 112 |

|    | Table o | of Contents                             | i   |