Welcome to **E-XFL.COM**

Understanding <u>Embedded - DSP (Digital Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

# **Applications of Embedded - DSP (Digital Signal Processors)**

| Details                 |                                                               |

|-------------------------|---------------------------------------------------------------|

| Product Status          | Obsolete                                                      |

| Туре                    | Floating Point                                                |

| Interface               | AIF, I <sup>2</sup> C, I2S, SPI, TDM, UART                    |

| Clock Rate              | 260MHz                                                        |

| Non-Volatile Memory     | Boot ROM (32kB)                                               |

| On-Chip RAM             | 676 kB                                                        |

| Voltage - I/O           | 1.80V                                                         |

| Voltage - Core          | 1.20V                                                         |

| Operating Temperature   | -40°C ~ 85°C (TA)                                             |

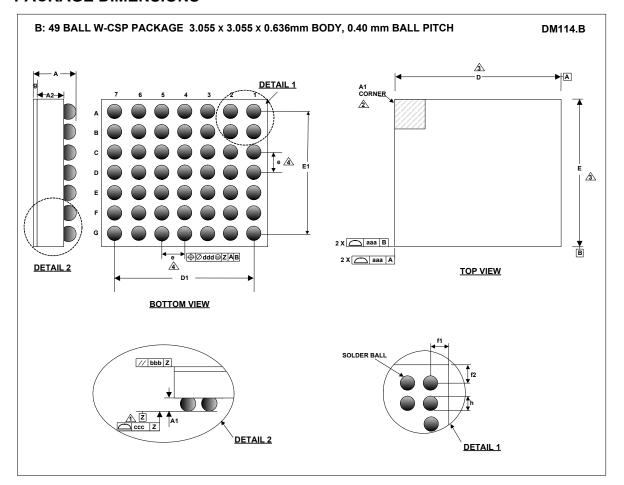

| Mounting Type           | Surface Mount                                                 |

| Package / Case          | 49-WFBGA, WLCSP                                               |

| Supplier Device Package | -                                                             |

| Purchase URL            | https://www.e-xfl.com/product-detail/cirrus-logic/wm0011ecs-r |

|                         |                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **CODE DATA DOWNLOAD**

The Software Code download comprises one Code Header packet (as described above), followed by multiple Code Data packets.

The Code Packet definition for the Code Data is:

- CMD = 0x03

- LEN = Data Length (in bytes)

- ADDR = Start Address for code data

- DAT = Data words

On completion of the full set of Code Data packet downloads, the  $\overline{\text{IRQ}}$  output is de-asserted and the WM0011 will commence execution of the downloaded software.

Note that completion of the Code Data packets is determined by the code image length that is contained within the Code Header packet (DAT). Software execution commences at the start address (ADDR) - also contained in the Code Header packet.

Boot status and error codes are reported via the UART interface, and via the SPI interface during the Code Data download - see "Boot Status and Error Reporting".

#### PLL CONFIGURATION DOWNLOAD

The PLL Configuration download operation requires a single Code Packet to be sent to the WM0011. The download may be achieved via the SPI Slave or SPI Master (eg. Flash Memory) interfaces. If the Custom fuses are not programmed, then only the SPI (Slave) download method is possible.

The Code Packet definition for PLL Configuration download is:

- CMD = 0x04

- LEN = 0x00\_0018

- ADDR = 0x0000\_0000

- DAT = PLL Configuration Data

The "DAT" portion must comprise 24 bytes, corresponding to the intended contents of the clocking configuration registers listed below. The CCM CLK CTRL1 register is transmitted first.

- CCM\_CLK\_CTRL1 (4 bytes, see Table 19)

- CCM\_CLK\_CTRL2 (4 bytes, see Table 20)

- CCM\_CLK\_CTRL3 (4 bytes, see Table 21)

- CCM\_PLL\_LOCK\_CTRL (4 bytes, see Table 22)

- UART\_BAUD\_LSW (1 byte, see Table 118)

- UART BAUD MSW (1 byte, see Table 119)

- Padding (2 bytes)

- SPI\_SCLKDIV (4 bytes, see Table 123)

On receipt of a valid PLL Configuration packet, the control registers noted above will be updated with the received data, and the new clocking configuration will become effective.

Note that the SPI\_SCLKDIV register on the WM0011 is only updated if the selected boot method is SPI Master. In all other cases, the SPI\_SCLKDIV portion of the PLL download is ignored and discarded. Note that the SPI Master boot method is only possible via the Custom fuse data settings.

Boot status and error codes are reported via the UART interface, and via the SPI interface during the PLL Configuration download - see "Boot Status and Error Reporting".

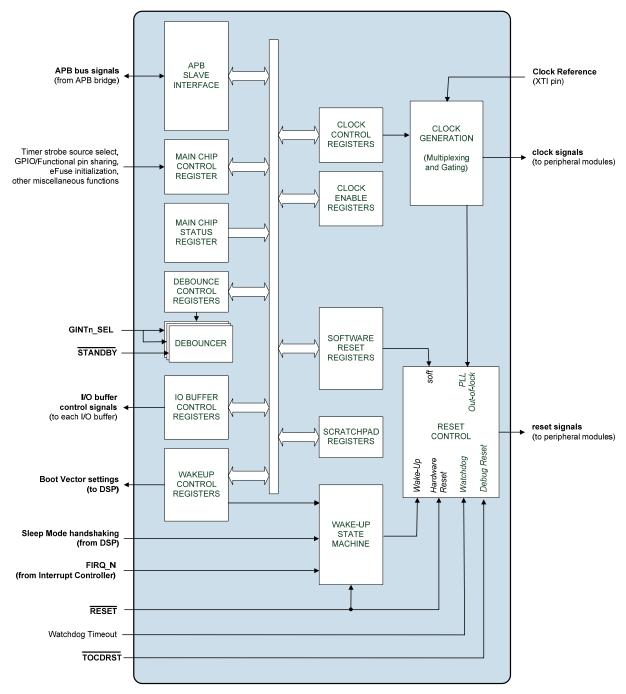

Figure 20 Chip Configuration Module (CCM) Block Diagram

## **CLOCKING CONTROL**

The CCM registers allow full configuration of the WM0011 clocking options, including clock dividers, clock multiplexers and the 2-stage Phase Locked Loop (PLL). Individual clock enable registers are provided for each peripheral module.

# **RESET CONTROL**

The CCM registers allow flexible control of the Warm Reset functions. The Warm Reset conditions are individually maskable, and status readback is also provided. Software Reset control registers allow each peripheral to be reset individually.

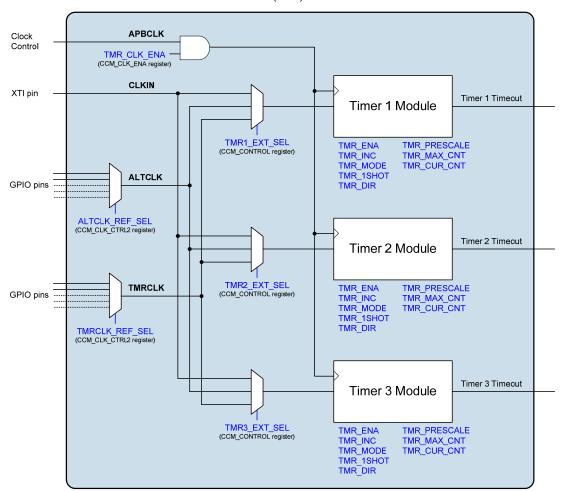

# **TIMER (TMR) MODULES**

TIMER 1 - BASE ADDRESS 0xF001\_0000

TIMER 2 - BASE ADDRESS 0xF001\_0020

TIMER 3 - BASE ADDRESS 0xF001\_0040

#### TIMER DESCRIPTION

The WM0011 provides three timers, which count up from 0, or count down from TMR\_MAX\_CNT. The counters are enabled using the TMR\_ENA bit, and count direction is selected using the TMR\_DIR bit (see Table 49).

The number of APBCLK clock cycles per count is determined by the TMR\_PRESCALE register. When TMR\_PRESCALE = 00h, the module will count at the APBCLK clock rate.

The TMR\_MODE bit enables a selectable external trigger to be used to start the timer count. The TMC\_INC bit configures the external trigger either as a 'start' trigger or as an alternate 'clock' signal. When TMR\_MODE=1 and TMR\_INC=0, the count rate is controlled only by the external trigger (ie. not by APBCLK).

The TMR\_1SHOT bit selects whether the Timer automatically re-starts after the 'end of count' condition has been reached.

Note that the timer clock enable bit (TMR\_CLK\_ENA) is on the CCM\_CLK\_ENA register, and the timer reset bit (TMR\_SOFTRST\_N) is in the CCM\_SOFTRST register. Note that these signals are common to all three Timer (TMR) modules.

Figure 23 Timer (TMR) Modules Block Diagram

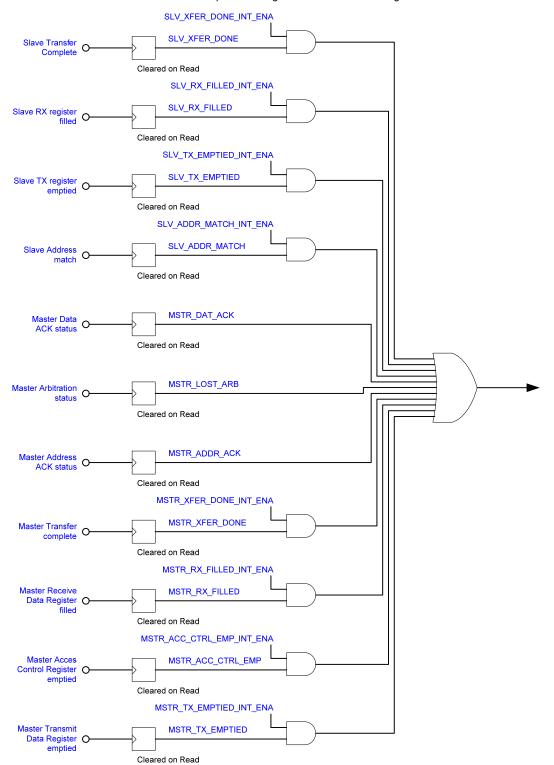

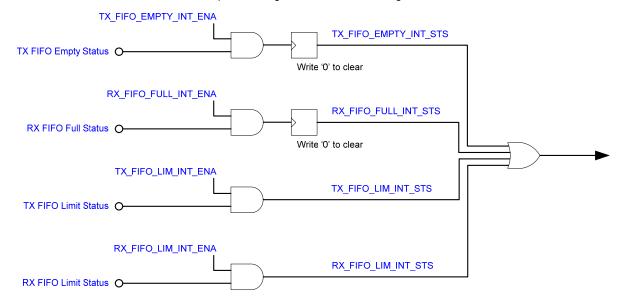

## **I2C INTERRUPTS**

The I2C module can generate an interrupt when any of the conditions described in the I2C\_STATUS register occurs. The interrupt conditions provide status indications of the I2C bus transactions.

The I2C interrupt control registers are illustrated in Figure 30.

Figure 30 I2C Interrupts

# I2C\_SLV\_ADDR - I<sup>2</sup>C SLAVE ADDRESS REGISTER

The I<sup>2</sup>C slave address is held in the SLV\_ADDR register. Note that this is the 7-bit Device Address, and does not include the Read/Write bit. The equivalent 8-bit Device Address comprises the 7 bits of SLV\_ADDR, and the R/W bit in the LSB position. This is illustrated by an example in Table 62.

| I <sup>2</sup> C ACTION | SLV_ADDR                      | 8-BIT DEVICE ADDRESS           |

|-------------------------|-------------------------------|--------------------------------|

| Write                   | 0:20 (has) 044 4000 (hinam)   | 0x70 (hex), 0111 0000 (binary) |

| Read                    | 0x38 (hex), 011 1000 (binary) | 0x71 (hex), 0111 0001 (binary) |

Table 62 Illustration of 7-bit SLV\_ADDR compared with 8-bit Device Address

|    |      |                                                                                                      |    |      |      |      |    |  |   |    | I2C | SL        |    | C_ |  | _  |    |            | GIS | TER | R  |            |    |      |      |     |     |      |     |     |   |

|----|------|------------------------------------------------------------------------------------------------------|----|------|------|------|----|--|---|----|-----|-----------|----|----|--|----|----|------------|-----|-----|----|------------|----|------|------|-----|-----|------|-----|-----|---|

| Ac | ldre |                                                                                                      |    |      |      |      |    |  |   |    |     |           |    |    |  |    |    |            |     |     |    |            | De | faul | t va | lue | = 0 | x000 | 0_0 | 000 |   |

| 31 | 30   | 29 28 27 26 25 24 23 22 21 20 19 18 17  FIELD S/W RESET VALUE  0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |    |      |      |      |    |  |   |    |     |           |    |    |  | 15 | 14 | 13         | 12  | 11  | 10 | 9          | 8  | 7    | 6    | 5   | 4   | 3    | 2   | 1   | 0 |

| ВІ |      |                                                                                                      |    |      |      |      |    |  |   |    |     |           |    |    |  |    |    |            |     |     | DE | FIE<br>SCF | LD | ION  |      |     |     |      |     |     |   |

| 31 | 1:7  |                                                                                                      |    | Re   | serv | ed   |    |  |   |    |     | 0x0<br>00 | _  |    |  |    |    |            |     |     |    |            |    |      |      |     |     |      |     |     |   |

| 6  | :0   |                                                                                                      | SL | .V_A | ADD  | R[6: | 0] |  | F | RW |     | 0x0       | 00 |    |  |    |    | the<br>not |     |     |    |            |    |      |      |     |     |      |     |     |   |

Table 63 I2C\_SLV\_ADDR Register

# INTERRUPT CONTROLLER (IRQC) MODULE

BASE ADDRESS 0xF005\_0000

## INTERRUPT CONTROLLER (IRQC) FEATURES

- 10 interrupt inputs from peripheral modules, including cascaded GPIO input

- De-bounced input from the STANDBY pin

- Register control of the IRQ output pin

- 2 register-controlled software interrupts

- Configurable interrupt logic using edge or level detection

- · Individual Mask control for each interrupt

- Configurable FIRQ\_N output to the Wake-Up FSM

- Configurable IRQ\_N and FIRQ\_N outputs to the Wake-Up FSM and HiFi EP<sup>™</sup> DSP Core

The IRQC module supports 11 inputs, comprising Interrupt signals from peripheral modules (eg. I2C Module), the cascaded input from the GPIO module, and also the de-bounced input from the STANDBY pin.

Any of the inputs may be selected as interrupt sources for the IRQC module, and used to generate the IRQ\_N and FIRQ\_N outputs to the HiFi  $EP^{TM}$ . A priority-encoded readback is available on the occurrence of an IRQ\_N or FIRQ\_N interrupt.

The FIRQ\_N ('Fast Interrupt) signal is also an input to the CCM module, providing a configurable 'Wakeup' control signal.

Note that many of the peripheral module interrupt signals are also independently provided as direct inputs to the HiFi  $\mathsf{EP}^\mathsf{TM}$ .

The IRQC module provides software capability to generate user-defined interrupts to the HiFi  $EP^{TM}$  and also to directly control the  $\overline{IRQ}$  output pin logic level.

The inputs and outputs of the IRQC module are illustrated in Figure 15.

## **INPUT / OUTPUT CONTROL**

Each signal described in the IRQC\_DIR must be configured as an input or as an output. The software interrupts (bits [15:14] and the  $\overline{\text{IRQ}}$  output (bit [0]) should be configured as outputs. All other bits should be configured as inputs.

The logic level each input is observable after de-metastability logic and inversion logic by reading IRQC\_IN. When input inversion is selected (using IRQC\_INV), value read from IRQC\_IN will be the opposite logic level from the signal source.

In the case of output signals, these are controlled by the respective IRQC\_OUT register bits. Note that these outputs are not affected by the IRQC\_INV bits.

#### LEVEL/EDGE INTERRUPT CONTROL

The interrupt inputs are configured as level sensitive or edge sensitive using the IRQC\_EDGE1 and IRQC EDGE0 registers.

In Level-sensitive configuration, the interrupt is asserted when the applicable logic level is detected. Active High is selected when IRQC\_INV=0; Active Low is selected when IRQC\_INV=1. Note that the interrupt cannot be cleared whilst the Active logic level is present (and unmasked) on the respective IRQC input.

In Edge-sensitive configuration, the interrupt is asserted when the applicable logic transition is detected. This may be the rising (leading) edge, falling (trailing) edge, or both edges. The active edge(s) will cause the respective IRQC\_IRQ\_STS and/or IRQC\_FIRQ\_STS bit to be set (as controlled by the respective mask bits). Note that the active edge(s) are inverted when IRQC\_INV=1.

WM0011

# IRQC\_EDGE0 - IRQ EDGE DETECTION 0 REGISTER

|        |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |      |     |     |  |   |    | IF | Q E |    |    | _    | ED    |       |      | EGIS | STER   | ł     |      |      |      |       |     |     |       |      |   |     |  |   |

|--------|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----|-----|--|---|----|----|-----|----|----|------|-------|-------|------|------|--------|-------|------|------|------|-------|-----|-----|-------|------|---|-----|--|---|

| Addres | ss = (                                                                         | FIELD NAME         S/W ACCESS         RESET VALUE         FIELD DESCRIPTION           Reserved         0x0         0x0           RW         0x0         Reserved - set to 0 only           RW         0x0         Reserved - set to 0 only           Reserved         0x0           Reserved         0x0           TMR2_INT_EDGE0         RW         0x0           TMR1_INT_EDGE0         RW         0x0           Selects Level or Edge interrupt detection, depending or           TMR1_INT_EDGE0         RW         0x0           Selects Level or Edge interrupt detection, depending or |      |      |     |     |  |   |    |    |     |    |    |      |       |       | =    | 0x   | 0000   | _0    | 000  |      |      |       |     |     |       |      |   |     |  |   |

| 31 30  | 29                                                                             | FIELD NAME         S/W ACCESS         RESET VALUE         FIELD DESCRIPTION           Reserved         0x0         0x0           RW         0x0         Reserved - set to 0 only           RESERVED         0x0           Reserved         0x0           Reserved         0x0           TMR2_INT_EDGE0         RW         0x0           Selects Level or Edge interrupt detection, depending on *EDGED DMA_INT_EDGE0         RW         0x0           DMA_INT_EDGE0         RW         0x0         Selects Level or Edge interrupt detection, depending on *EDGED DMA_INT_EDGE0              |      |      |     |     |  |   |    |    |     |    |    |      |       | 2     | 1    | 0    |        |       |      |      |      |       |     |     |       |      |   |     |  |   |

| BITS   |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |      |     |     |  | - |    | s  |     |    |    |      |       | ı     |      | _    |        | D     | ES   |      |      | ION   |     |     |       |      |   |     |  | ı |

| 31:16  |                                                                                | RW         0x0         Reserved - set to 0 only           RW         0x0         Reserved - set to 0 only           Reserved         0x0                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      |     |     |  |   |    |    |     |    |    |      |       |       |      |      |        |       |      |      |      |       |     |     |       |      |   |     |  |   |

| 15     |                                                                                | RW         0x0         Reserved - set to 0 only           RW         0x0         Reserved - set to 0 only           Reserved         0x0                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      |     |     |  |   |    |    |     |    |    |      |       |       |      |      |        |       |      |      |      |       |     |     |       |      |   |     |  |   |

| 14     |                                                                                | RW         0x0         Reserved - set to 0 only           RW         0x0         Reserved - set to 0 only           Reserved         0x0           Reserved         0x0                                                                                                                                                                                                                                                                                                                                                                                                                      |      |      |     |     |  |   |    |    |     |    |    |      |       |       |      |      |        |       |      |      |      |       |     |     |       |      |   |     |  |   |

| 13     | RW         0x0         Reserved - set to 0 only           Reserved         0x0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |      |     |     |  |   |    |    |     |    |    |      |       |       |      |      |        |       |      |      |      |       |     |     |       |      |   |     |  |   |

| 12     |                                                                                | RW         0x0         Reserved - set to 0 only           Reserved         0x0           Reserved         0x0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |      |     |     |  |   |    |    |     |    |    |      |       |       |      |      |        |       |      |      |      |       |     |     |       |      |   |     |  |   |

| 11     | Т                                                                              | MR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2_IN | IT_I | EDG | GE0 |  | F | RW |    | 0x  | 0  | Se | elec | ts Le | vel c | or E | Edge | e inte | errup | ot c | dete | ctio | n, de | ере | ndi | ing o | n *E | D | GE1 |  |   |

| 10     | Т                                                                              | MR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1_IN | IT_I | EDG | GE0 |  | F | RW |    | 0x  | 0  | Se | elec | ts Le | vel c | or E | Edge | e inte | erru  | ot c | dete | ctio | n, de | ере | ndi | ing o | n *E | D | GE1 |  |   |

| 9      | [                                                                              | DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | A_IN | T_E  | DG  | E0  |  | F | RW |    | 0х  | 0  | Se | elec | ts Le | vel c | or E | Edge | e inte | erru  | ot c | dete | ctio | n, de | ере | ndi | ng o  | n *E | D | GE1 |  |   |

| 8      | ١                                                                              | ND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | T_IN | T_E  | DG  | E0  |  | F | RW |    | 0x  | 0  | Se | elec | ts Le | vel c | or E | Edge | e inte | erru  | ot c | dete | ctio | n, de | ере | ndi | ing o | n *E | D | GE1 |  |   |

| 7      | S                                                                              | STB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Y_IN | T_E  | EDG | E0  |  | F | RW |    | 0x  | 0  | Se | elec | ts Le | vel d | or E | Edge | e inte | erru  | ot c | dete | ctio | n, de | ере | ndi | ing o | n *E | D | GE1 |  |   |

| 6      |                                                                                | I2C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _INT | _E   | DGE | Ξ0  |  | F | RW |    | 0x  | 0  | Se | elec | ts Le | vel d | or E | Edge | e inte | erru  | ot c | dete | ctio | n, de | ере | ndi | ing o | n *E | D | GE1 |  |   |

| 5      | 1                                                                              | AIF2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2_IN | T_E  | DG  | E0  |  | F | RW |    | 0x  | :0 | Se | elec | ts Le | vel c | or E | Edge | e inte | erru  | ot c | dete | tio  | n, de | ере | ndi | ng o  | n *E | D | GE1 |  |   |

| 4      | 1                                                                              | AIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1_IN | T_E  | DG  | E0  |  | F | RW |    | 0x  | :0 | Se | elec | ts Le | vel c | or E | Edge | e inte | erru  | ot c | dete | ctio | n, de | ере | ndi | ng o  | n *Ē | D | GE1 |  |   |

| 3      | L                                                                              | JAR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | T_IN | IT_I | EDG | GE0 |  | F | RW |    | 0x  | :0 | Se | elec | ts Le | vel c | or E | Edge | e inte | erru  | ot c | dete | ctio | n, de | ере | ndi | ing o | n *Ē | D | GE1 |  |   |

| 2      |                                                                                | SPI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _INT | _E   | DGE | E0  |  | F | RW |    | 0х  | :0 | Se | elec | ts Le | vel c | or E | Edge | e inte | erru  | ot c | dete | ctio | n, de | ере | ndi | ing o | n *E | D | GE1 |  |   |

| 1      | (                                                                              | 3PI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NI_C | T_E  | EDG | SE0 |  | F | RW |    | 0х  | 0  | Se | elec | ts Le | vel c | or E | Edge | e inte | erru  | ot c | dete | ctio | n, de | ере | ndi | ing o | n *E | D | GE1 |  |   |

| 0      |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |      |     |     |  | F | RW |    | 0x  | 0  | Re | esei | ved · | - set | to   | 0 o  | nly    |       |      |      |      |       |     |     |       |      |   |     |  |   |

Table 85 IRQC\_EDGE0 Register

# IRQC\_EDGE1 - IRQ EDGE DETECTION 1 REGISTER

|     |     |      |                                                                                                                                                                                                                                              |     |       |     |     |  |   |    | IR | Q E |    |    | _    | ED(  |       |       | SIST | ER    |      |      |       |      |      |      |       |     |     |     |   |   |

|-----|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|-----|--|---|----|----|-----|----|----|------|------|-------|-------|------|-------|------|------|-------|------|------|------|-------|-----|-----|-----|---|---|

| Ad  | dre | ss = | 0xF                                                                                                                                                                                                                                          | 00  | 5_00  | 14  |     |  |   |    |    |     |    |    |      |      |       |       |      |       | De   | faul | lt v  | /alu | е :  | = 0x | 000   | 0_0 | 000 |     |   |   |

| 31  | 30  | 29   | FIELD NAME         S/W ACCESS         RESET VALUE           Reserved         0x0           RW         0x0         Re           RW         0x0         Re           Reserved         0x0         Re           Reserved         0x0         Re |     |       |     |     |  |   |    |    |     |    |    |      |      | 14    | 13    | 12   | 11    | 10   | 9    | 8     | 7    | 6    | 5    | 5 4   | 1   | 3   | 2   | 1 | 0 |

| ВІ  | TS  |      |                                                                                                                                                                                                                                              |     |       | _   |     |  | _ |    | s  |     |    |    |      |      |       |       |      |       | DE   |      |       |      | l    |      | •     |     |     |     |   | , |

| 31: | 16  |      | NAME         ACCESS         VALUE         DESCRIPTION           Reserved         0x0                                                                                                                                                         |     |       |     |     |  |   |    |    |     |    |    |      |      |       |       |      |       |      |      |       |      |      |      |       |     |     |     |   |   |

| 1:  | 5   |      | NAME         ACCESS         VALUE         DESCRIPTION           Reserved         0x0         0x0           RW         0x0         Reserved - set to 0 only           RW         0x0         Reserved - set to 0 only                         |     |       |     |     |  |   |    |    |     |    |    |      |      |       |       |      |       |      |      |       |      |      |      |       |     |     |     |   |   |

| 14  | 4   |      | RW         0x0         Reserved - set to 0 only           RW         0x0         Reserved - set to 0 only                                                                                                                                    |     |       |     |     |  |   |    |    |     |    |    |      |      |       |       |      |       |      |      |       |      |      |      |       |     |     |     |   |   |

| 1:  | 3   |      |                                                                                                                                                                                                                                              | R   | eserv | ed  |     |  |   |    |    | 0x  | 0  |    |      |      |       |       |      |       |      |      |       |      |      |      |       |     |     |     |   |   |

| 1:  | 2   |      |                                                                                                                                                                                                                                              | R   | eserv | ed  |     |  |   |    |    | 0x  | :0 |    |      |      |       |       |      |       |      |      |       |      |      |      |       |     |     |     |   |   |

| 1   | 1   |      | TMF                                                                                                                                                                                                                                          | R2_ | _INT_ | ED  | GE1 |  | F | RW |    | 0x  | :0 | Se | lect | s Le | vel c | or Ed | dge  | inter | rupt | dete | ectio | n, d | eper | ndi  | ing c | n ' | *ED | GEO | ) |   |

| 10  | 0   |      | TMF                                                                                                                                                                                                                                          | R1_ | _INT_ | ED  | GE1 |  | F | RW |    | 0x  | :0 | Se | lect | s Le | vel c | or Ed | dge  | inter | rupt | dete | ectio | n, d | eper | ndi  | ing c | n ' | *ED | GEO | ) |   |

| 9   | )   |      | DM                                                                                                                                                                                                                                           | Α_  | INT_I | ED  | GE1 |  | F | RW |    | 0x  | 0  | Se | lect | s Le | vel c | or Ed | dge  | inter | rupt | dete | ectio | n, d | eper | ndi  | ing c | n ' | *ED | GEO | ) |   |

| 8   | 3   |      | WD                                                                                                                                                                                                                                           | T_  | INT_I | ED  | GE1 |  | F | RW |    | 0х  | 0  | Se | lect | s Le | vel c | or Ed | dge  | inter | rupt | dete | ectio | n, d | eper | ndi  | ing c | n ' | *ED | GEO | ) |   |

| 7   | ,   |      | STE                                                                                                                                                                                                                                          | BY_ | _INT_ | ED  | GE1 |  | F | RW |    | 0x  | 0  | Se | lect | s Le | vel d | or Ed | dge  | inter | rupt | dete | ectio | n, d | eper | ndi  | ing c | n ' | *ED | GEO | ) | _ |

| 6   | 6   |      | 120                                                                                                                                                                                                                                          | C_I | NT_E  | DG  | E1  |  | F | RW |    | 0x  | 0  | Se | lect | s Le | vel c | or Ed | dge  | inter | rupt | dete | ectio | n, d | eper | ndi  | ing c | n ' | *ED | GEO | ) | _ |

| 5   | 5   |      | AIF                                                                                                                                                                                                                                          | 2_  | INT_I | EDO | GE1 |  | F | RW |    | 0x  | :0 | Se | lect | s Le | vel c | or Ed | dge  | inter | rupt | dete | ectio | n, d | eper | ndi  | ing c | n ' | *ED | GE0 | ) |   |

| 4   | ļ.  |      | AIF                                                                                                                                                                                                                                          | 1_  | INT_I | EDO | GE1 |  | F | RW |    | 0х  | :0 | Se | lect | s Le | vel c | or Ed | dge  | inter | rupt | dete | ectio | n, d | eper | ndi  | ing c | n ' | *ED | GE0 | ) |   |

# IRQC\_FIRQ\_STS - IRQ FAST INTERRUPT STATUS REGISTER

|        |                                                                                                                  |                     |                 |      |     |     |   |  |   | IR | Q F | AST |    |     | _      | IRC<br>PT S | _     |      |       | EG   | ISTI  | ER   |    |      |    |      |     |       |     |     |      |     |     |     |

|--------|------------------------------------------------------------------------------------------------------------------|---------------------|-----------------|------|-----|-----|---|--|---|----|-----|-----|----|-----|--------|-------------|-------|------|-------|------|-------|------|----|------|----|------|-----|-------|-----|-----|------|-----|-----|-----|

| Addres | ss =                                                                                                             | 0xl                 | FOC             | 5_00 | )34 |     |   |  |   |    |     |     |    |     |        |             |       |      |       |      |       |      |    |      |    | De   | fau | ılt v | alu | е : | = 0x | 000 | 0_0 | 000 |

| 31 30  | 29                                                                                                               | S/W   RESET   VALUE |                 |      |     |     |   |  |   |    |     |     |    |     |        |             | 14    | 1:   | 3     | 12   | 11    | 10   | ç  | 9 8  | 3  | 7    | 6   | 5     | i 4 | 4   | 3    | 2   | 1   | 0   |

| BITS   |                                                                                                                  | ı                   | FIE             | LD N | IAM | 1E  |   |  | _ |    | s   |     |    |     |        |             |       |      |       | •    | FII   | ELD  | D  | ESC  | RI | IPTI | 101 | 1     | •   |     |      |     |     |     |

| 31:16  | Reserved                                                                                                         |                     |                 |      |     |     |   |  |   |    |     |     |    |     |        |             |       |      |       |      |       |      |    |      |    |      |     |       |     |     |      |     |     |     |

| 15     | RO         0x0         Reserved - r           RO         0x0         Reserved - r           Reserved         0x0 |                     |                 |      |     |     |   |  |   |    |     |     |    |     |        | - rea       | ads   | s ba | ick   | 0 or | ıly   |      |    |      |    |      |     |       |     |     |      |     |     |     |

| 14     | RO         0x0         Reserved - reads back           Reserved         0x0           Reserved         0x0       |                     |                 |      |     |     |   |  |   |    |     |     |    |     |        | ick         | 0 or  | nly  |       |      |       |      |    |      |    |      |     |       |     |     |      |     |     |     |

| 13     | Reserved         0x0           Reserved         0x0                                                              |                     |                 |      |     |     |   |  |   |    |     |     |    |     |        |             |       |      |       |      |       |      |    |      |    |      |     |       |     |     |      |     |     |     |

| 12     | Reserved 0x0                                                                                                     |                     |                 |      |     |     |   |  |   |    |     |     |    |     |        |             |       |      |       |      |       |      |    |      |    |      |     |       |     |     |      |     |     |     |

| 11     | Reserved 0x0                                                                                                     |                     |                 |      |     |     |   |  |   |    |     |     |    |     | 2 (Tin | ner 2       | 2)    | Inte | erru  | pt S | tatu  | s    |    |      |    |      |     |       |     |     |      |     |     |     |

| 10     |                                                                                                                  | TM                  | IR1             | _FIR | RQ_ | ST  | S |  | F | RO |     | 0x  | 0  | ΤN  | MR1    | (Tin        | ner 1 | 1) l | Inte  | erru | pt S  | tatu | s  |      |    |      |     |       |     |     |      |     |     |     |

| 9      |                                                                                                                  | DI                  | MA <sub>.</sub> | _FIR | Q_9 | ST  | S |  | F | RO |     | 0х  | 0  | DI  | MA     | Inter       | rupt  | St   | tatu  | S    |       |      |    |      |    |      |     |       |     |     |      |     |     |     |

| 8      |                                                                                                                  | W                   | DT              | _FIR | Q_9 | ST  | S |  | F | RO |     | 0x  | 0  | W   | DT     | (Wat        | chd   | og   | Tin   | ner) | ) Int | erru | pt | Stat | us |      |     |       |     |     |      |     |     |     |

| 7      |                                                                                                                  | ST                  | BY              | _FIR | Q_  | ST  | S |  | F | RO |     | 0х  | 0  | S   | TAN    | IDBY        | / Int | err  | rupt  | Sta  | atus  | ;    |    |      |    |      |     |       |     |     |      |     |     |     |

| 6      |                                                                                                                  | 12                  | 2C_             | FIRC | 2_S | TS  | 3 |  | F | RO |     | 0x  | :0 | 120 | C Ir   | terru       | ıpt S | tat  | tus   |      |       |      |    |      |    |      |     |       |     |     |      |     |     |     |

| 5      |                                                                                                                  | ΑI                  | F2              | _FIR | Q_5 | ST  | S |  | F | RO |     | 0х  | 0  | ΑI  | F2     | Interr      | upt   | Sta  | atus  | S    |       |      |    |      |    |      |     |       |     |     |      |     |     |     |

| 4      |                                                                                                                  | ΑI                  | F1              | _FIR | Q_S | ST  | S |  | F | RO |     | 0х  | 0  | Αl  | F1     | Inter       | upt   | Sta  | atus  | S    |       |      |    |      |    |      |     |       |     |     |      |     |     |     |

| 3      |                                                                                                                  | UA                  | RT              | _FIR | Q_  | ST  | S |  | F | RO |     | 0х  | :0 | UA  | 4R1    | Inte        | rrup  | t S  | Stati | us   |       |      |    |      |    |      |     |       |     |     |      |     |     |     |

| 2      |                                                                                                                  | S                   | PĪ_             | FIRO | Q_S | STS | 3 |  | F | RO |     | 0x  | :0 | SF  | Pl Ir  | nterru      | ıpt S | Sta  | tus   |      |       |      |    |      |    |      |     |       |     |     |      |     |     |     |

| 1      |                                                                                                                  | GF                  | PIO             | _FIR | Q_  | ST  | s |  | F | RO |     | 0x  | :0 | GI  | PIO    | Inte        | rrupt | S    | tatu  | ıs   |       |      |    |      |    |      |     |       |     |     |      |     |     |     |

| 0      |                                                                                                                  |                     |                 |      |     |     |   |  | F | RO |     | 0x  | 0  | Re  | esei   | ved         | - rea | ads  | s ba  | ick  | 0 or  | ıly  |    |      |    |      |     |       |     |     |      |     |     |     |

Table 94 IRQC\_FIRQ\_STS Register

|    |      |          |    |      |     |     |    |    |    | w  | ΆΤΟ | CHD         |           | /DT | _    |      | _     |      | REG | SIST | ER  |     |             |       |      |       |       |      |     |      |     |

|----|------|----------|----|------|-----|-----|----|----|----|----|-----|-------------|-----------|-----|------|------|-------|------|-----|------|-----|-----|-------------|-------|------|-------|-------|------|-----|------|-----|

| A  | ddre | WATCHDOG |    |      |     |     |    |    |    |    |     |             |           |     |      |      |       |      |     |      |     | Def | fault       | t val | ue : | = 0x  | 000   | D_FF | FFF |      |     |

| 31 | 30   | 29       | 28 | 27   | 26  | 25  | 24 | 23 | 22 | 21 | 20  | 19          | 18        | 17  | 16   | 15   | 14    | 13   | 12  | 11   | 10  | 9   | 8           | 7     | 6    | 5     | 4     | 3    | 2   | 1    | 0   |

| В  | ITS  |          |    | -    |     |     |    |    | _  |    |     |             |           |     |      |      |       |      |     |      | DE  |     | ELD<br>RIPT | ION   |      |       |       |      |     |      |     |

| 3  | 1:0  |          | W  | DT_I | MAX | _CN | ١T |    | F  | RW |     | 0x00<br>_FF | 000<br>FF | Co  | ount | valu | ie (n | neas | ure | d in | APB | CLK | сус         | les)  | befo | ore w | vatch | ndog | tim | es o | ut. |

Table 107 WDT\_MAX\_CNT Register

# WDT\_CUR\_CNT - WATCHDOG CURRENT COUNT REGISTER

|    |                                                                 |                                                                                                  |   |      |                 |     |    |  |   | w  | /AT | CHD |  |                       | _                                | UR.                | _                                   |                                   | RE                         | GIST                          | ER            |      |                        |             |               |          |       |            |     |            |        |     |

|----|-----------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---|------|-----------------|-----|----|--|---|----|-----|-----|--|-----------------------|----------------------------------|--------------------|-------------------------------------|-----------------------------------|----------------------------|-------------------------------|---------------|------|------------------------|-------------|---------------|----------|-------|------------|-----|------------|--------|-----|

| Ad | dres                                                            | WATCHDOG CU  PSS = 0xF007_000C    29   28   27   26   25   24   23   22   21   20   19   18   17 |   |      |                 |     |    |  |   |    |     |     |  |                       |                                  |                    |                                     |                                   |                            |                               |               |      |                        | De          | faul          | t v      | alue  | = 0        | )x0 | 000        | _FI    | FFF |

| 31 | 30                                                              | 29   28   27   26   25   24   23   22   21   20   19   18   17   1                               |   |      |                 |     |    |  |   |    |     |     |  | 16                    | 15                               | 14                 | 13                                  | 12                                | 11                         | 10                            | 9             | 8    | 7                      | 6           | 5             | 5 4      | 3     |            | 2   | 1          | 0      |     |

| Bľ | NAME ACCESS VALUE  The cu When watched Ox0000 After do After do |                                                                                                  |   |      |                 |     |    |  |   |    |     |     |  | •                     |                                  |                    |                                     | •                                 | DE                         | -                             | IELC<br>CRIP  |      | 1                      |             | •             | ·        |       | •          |     | •          |        |     |

| 31 | :0                                                              |                                                                                                  | W | DT_C | UR <sub>.</sub> | _CN | ΙT |  | F | ₹0 |     |     |  | Wa<br>Af<br>dis<br>va | her<br>atch<br>ter<br>sab<br>lue | WD<br>dog<br>de-as | T_C<br>is ac<br>ssert<br>NDT<br>e W | UR_<br>tiva<br>tion<br>_EN<br>DT_ | CN<br>ted.<br>of F<br>NA = | IT re<br>RESE<br>= 0),<br>X_C | T ar<br>the \ | s to | the va<br>when<br>DT_C | alue<br>eve | held<br>r the | in<br>wa | atcho | –<br>log t | im  | –<br>er is | ,<br>} |     |

Table 108 WDT\_CUR\_CNT Register

# WDT\_RST\_LEN - WATCHDOG RESET PULSE LENGTH REGISTER

WDT\_RST\_LEN controls the duration (pulse length) of the Watchdog Reset signal. This field represents the number of APBCLK cycles for which the Watchdog Reset signal is asserted (Active Low output to the Reset Controller).

|    |                                                                              |      |                                                                            |   |  |   |  |  | ٧ | VAT | СНГ | oog |    |    | _R<br>PU | -  | _  |    | ΉR    | EGI | STE | R          |             |    |      |       |      |      |     |     |     |

|----|------------------------------------------------------------------------------|------|----------------------------------------------------------------------------|---|--|---|--|--|---|-----|-----|-----|----|----|----------|----|----|----|-------|-----|-----|------------|-------------|----|------|-------|------|------|-----|-----|-----|

| Ad | ldre                                                                         | ss = | 29 28 27 26 25 24 23 22 21 20 19 18 17  FIELD NAME  S/W ACCESS RESET VALUE |   |  |   |  |  |   |     |     |     |    |    |          |    |    |    |       |     |     |            |             | De | faul | t val | ue   | = 0x | 000 | 0_0 | 0FF |

| 31 | 30   29   28   27   26   25   24   23   22   21   20   19   18   13   15     |      |                                                                            |   |  |   |  |  |   |     |     | 17  | 16 | 15 | 14       | 13 | 12 | 11 | 10    | 9   | 8   | 7          | 6           | 5  | 4    | 3     | 2    | 1    | 0   |     |     |

| Bľ | TS                                                                           |      |                                                                            | - |  | _ |  |  | _ |     |     |     |    |    |          |    |    |    |       |     | DE  | FIE<br>SCF | ELD<br>RIPT |    |      |       |      |      |     |     |     |

| 31 | 31:8 Reserved                                                                |      |                                                                            |   |  |   |  |  |   |     |     |     | _  |    |          |    |    |    |       |     |     |            |             |    |      |       |      |      |     |     |     |

| 7: | TS FIELD S/W RESET VALUE  :8 Reserved 0x00_ 0000  .0 WDT RST LEN RW 0x0000 N |      |                                                                            |   |  |   |  |  |   |     |     |     |    |    |          |    | •  |    | for v |     |     |            |             | _  |      | er R  | eset | sigr | nal |     |     |

Table 109 WDT\_RST\_LEN Register

# SERIAL PERIPHERAL INTERFACE (SPI) MODULE

BASE ADDRESS 0xF030\_0000

#### **SPI FEATURES**

- Configurable Data/Clock phase and Clock polarity

- Data word length can be on 8, 16, 24, 32 or 64 bits

- · Selectable data bit ordering (LSB first or MSB first)

- Polarity selection for the Slave Select (SPISS) signal

- Programmable soft reset capability

- Selectable "auto-retransmit" mode

- Selectable "early-tx-data transition" mode

- Byte-packing options

- Multiple Transfer mode allowing multiple data words per SPISS assertion

- Master Mode Slave Select "shaping" (configurable SPISS set-up, hold and wait times)

#### **SPI MASTER MODE**

The SPI\_MISO pin direction is Input.

The SPISS, SPISCLK, and SPIMOSI pins are driven as Outputs, but only during an actual data transfer. After a master data transfer has completed, these signals are tri-stated. This allows for lower power usage, and for usage in a multi-master SPI scenario.

Note that the above behaviour can be adjusted using the SPI\_MM\_MODE register (see Table 121), which allows constant driving of these master mode output signals whenever the SPI block is enabled.

The SPI Master mode is selected by setting SPI\_MODE=0. The user should configure the desired SPISCLK, SPISS, and MISO/MOSI parameters, and lastly set SPI\_ENA=1 to enable the SPI module.

The SPI module will then be in Master mode, and will initiate a SPI data transfer when data is written to the SPI\_DAT data register. The outgoing SPI\_DAT data is double-buffered, allowing for the queuing of the "next word" to be transferred, while the current word is being shifted out.

#### **SPI SLAVE MODE**

The SPISS, SPISCK, and SPIMOSI pin direction is input.

The SPIMISO pin is driven as Output, but only during an actual data transfer. After a slave data transfer has completed (i.e. de-assertion of SPISS by the master), this signal is tri-stated. This allows for usage in a multi-slave SPI scenario.

The SPI Slave mode is selected by setting SPI\_MODE=1. The user should configure the desired SPISCLK, SPISS, and MISO/MOSI parameters, and lastly set SPI\_ENA=1 to enable the SPI module.

The SPI module will then be in Slave mode, and will wait for a SPI data transfer from an external master. Once initiated, the incoming data bits are shifted in until one word is received. The incoming data word is placed in a holding register, allowing for the reception of the serial bits of a "new current word", while the previous word is being queued for transfer to the AHB system side.

#### SPISCLK (CLOCK) CONFIGURATION

In SPI Master mode, the SPI Clock Divisor register SPI\_SCLKDIV is used to control the frequency of SPISCLK. The register stores a 16-bit parameter that supplies the initial value for the clock generator counter. The derived frequency for SPISCLK is:

[AHBCLK frequency] / (SPI\_SCLKDIV+1) \* 2

In SPI Master mode, the maximum supported SPISCLK frequency is [AHBCLK frequency] / 8.

## **SPI DMA OPERATIONS**

DMA operations associated with the SPI interface are controlled by the SPI\_DMA\_CTRL register.

For DMA handshake in Master or Slave modes, the SPI\_DMA\_CTRL register bits must be set for the desired operation:

The WR\_RQST\_ENA bit enables the DMA Write request handshake, which indicates the transmit buffer is empty and ready for more data.

The RD\_RQST\_ENA bit enables the DMA Read request handshake, which indicates the receive buffer is full and needs to be read.

In the case where byte-packing is disabled (BP\_EN=0), the DMA requests are based on the normal buffer status (empty, full) – ie. mimics the function of the CYC\_DONE status.

When byte-packing is enabled (BP\_EN=1), the DMA requests are based on the packed BP 64-bit buffer status (empty, full), OR on the determination that the byte-packed transfer is done - ie. it mimics the function of the BP\_DONE status.

The CYC\_DONE and BP\_DONE registers are held within the SPI\_STATUS register.

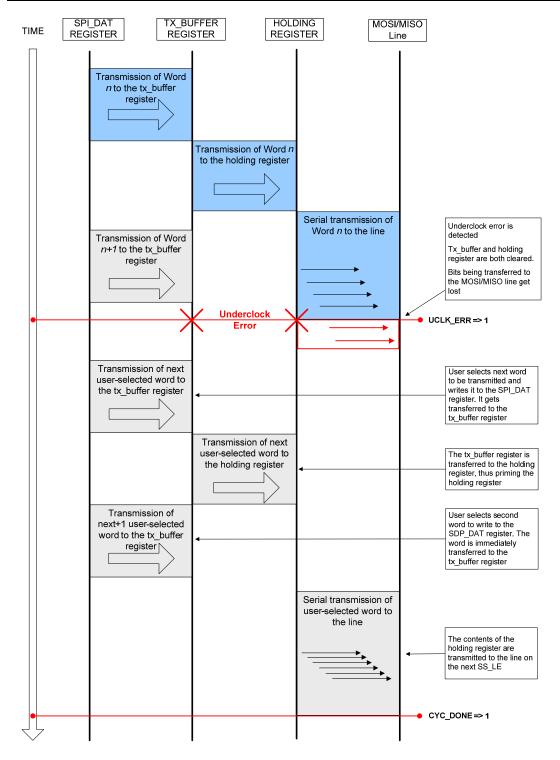

Underclock error - UCLK\_ERR = 0

Following an Underclock Error, the user determines what data to send next. Both tx\_buffer and the holding register must be primed before the next CYC\_DONE. It is recommended that this is done during the UCLK ERR interrupt.

Figure 42 SPI Transmission with Underclock Error, UCLK\_ERR=0

|        |                      |              |          |                | SPI_STATUS<br>I STATUS REGISTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------|----------------------|--------------|----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Addres | ss = 0xF030_0028     |              |          |                | Default value = 0x0000_0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 31 30  | 29 28 27 26 25 24 23 | 22 21        | 20       | 19 18          | 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BITS   | FIELD<br>NAME        | S/W<br>ACCES |          | RESET<br>VALUE | FIELD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 31:15  | Reserved             | ACCES        | 3        | 0              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 14:12  | SPI_CURRENT_STS      | RO           |          | 0x0            | Raw status of the SPI master state machine's "current_state" register:  000 = IDLE  001 = CSSETUP  010 = TRANSFER  011 = CSHOLD  100 = CSWAIT  101 = CKWAIT  110 = MTRANS  111 = CSBEGIN                                                                                                                                                                                                                                                                                                                                                                                   |

| 11     | Reserved             |              |          | 0x0            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10     | RX_BUF_FULL          | RO           |          | 0x0            | Raw indicator of Rx incoming holding register status  0 = No data in holding register  1 = Holding register contains a valid data word                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 9      | TX_BUF_FULL          | RO           |          | 0x0            | Raw indicator of Tx outgoing holding register status  0 = Holding register ready for new data word  1 = Tx Buffer is full                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8      | TX_UFL_ERR           | R/W1C        | ;        | 0x0            | Write Underflow Error indication: indicates that the outgoing data buffer did not get loaded with new data since the last transmission, and another transmission began.  0 = No Write Underflow since this bit was cleared  1 = Write Underflow detected  This bit is cleared by writing a '1' to it.  This bit is a sticky status bit, and will set upon meeting the condition regardless of the state of its corresponding interrupt enable  TX_UFL_ERR_INT_ENA.                                                                                                         |

| 7      | BP_DONE              | R/W1C        | <b>;</b> | 0x0            | Byte Packing Transfer Done: indicates a request for more packed data. This bit is set when the Byte Packing Holding Register is full (RX) and empty (TX), or when the current transfer of multiple byte-packed words is complete.  0 = Byte Packing Transfer is not complete  1 = Byte Packing Transfer is complete Only valid if byte packing is enabled (BP_EN = 1). This bit is cleared by writing a '1' to it. This bit is a sticky status bit, and will set upon meeting the condition regardless of the state of its corresponding interrupt enable BP_DONE_INT_ENA. |

| 6      | SS_TE                | R/W1C        | ;        | 0x0            | Slave Select Trailing Edge Detect:  0 = no SPISS de-assertion detected since this bit was cleared  1 = the SPISS de-assertion has been detected  This bit is cleared by writing a '1' to it.  This bit is a sticky status bit, and will set upon meeting the condition regardless of the state of its corresponding interrupt enable  SS_TE_INT_ENA.                                                                                                                                                                                                                       |

| 5      | CYC_DONE             | R/W1C        | ;        | 0x0            | Cycle Done: this bit will set when the current transfer of word-length "WL" bits is complete. It indicates that "WL" bits were sent on the transmit port and "WL" bits were sampled on the receive port.  This bit is cleared by writing a '1' to it.  This bit is a sticky status bit, and will set upon meeting the condition regardless of the state of its corresponding interrupt enable CYC_DONE_INT_ENA.                                                                                                                                                            |

WM0011

# DMA\_PRI\_DST REGISTER

|                                               |                                                                                                                                                                                                                                              |        |       |                  |       |     |     | DN  | IA P  | RIN | /AR         |      | MA_<br>STI                    | _                                 | _                                        |                                | _                                   | ESS                          | REG | GIST                          | ER                     |    |                     |              |             |              |     |     |       |      |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|------------------|-------|-----|-----|-----|-------|-----|-------------|------|-------------------------------|-----------------------------------|------------------------------------------|--------------------------------|-------------------------------------|------------------------------|-----|-------------------------------|------------------------|----|---------------------|--------------|-------------|--------------|-----|-----|-------|------|

|                                               |                                                                                                                                                                                                                                              |        |       | 40_01<br>nel, va |       | •   |     | •   |       |     |             |      |                               |                                   |                                          |                                |                                     |                              |     |                               |                        |    | De                  | faul         | lt va       | alue         | = 0 | )0x | 000_  | 0000 |

| 31                                            | 31   30   29   28   27   26   25   24   23   22   21   20   19   18   17   16   15   14   13   12   11   10   9   8   7   6   5   4   3   2   1    BITS FIELD NAME S/W ACCESS NALUE FIELD DESCRIPTION  DMA Destination Address (Channel 'n') |        |       |                  |       |     |     |     |       |     |             |      |                               |                                   |                                          | 0                              |                                     |                              |     |                               |                        |    |                     |              |             |              |     |     |       |      |

| BITS FIFT D NAME S/W RESET FIFT D DESCRIPTION |                                                                                                                                                                                                                                              |        |       |                  |       |     |     |     |       |     |             |      |                               |                                   |                                          |                                |                                     |                              |     |                               |                        |    |                     |              |             |              |     |     |       |      |

| 31                                            | :0                                                                                                                                                                                                                                           |        | DMA   | _PRI_            | DST   | n   |     | F   | RW    |     | 0x00<br>000 |      | Ea<br>Tra<br>Un<br>are<br>igr | ich re<br>ansfe<br>aligr<br>e ign | egister for<br>ned<br>ored<br>d.<br>be w | ter h<br>r its<br>Add<br>d. Fo | resportes<br>ressortes<br>ressortex | s bas<br>bect<br>bits<br>amp |     | ddre<br>hani<br>all S<br>wher | ss fonel.<br>RC,<br>DM | DS | e de<br>T, a<br>SRC | nd L<br>:_HS | INK<br>SIZE | (_A[<br><0== | DDR | reg | jiste |      |

| Not                                           | e tha                                                                                                                                                                                                                                        | at 'n' | repre | sents            | the I | DMA | cha | nne | l nur | nbe | er, ie.     | 0, 1 | 1, 2 .                        | 31                                |                                          |                                |                                     |                              |     |                               |                        |    |                     |              |             |              |     |     |       |      |

Table 148 DMA\_PRI\_DST\_n Register

# DMA\_PRI\_LEN REGISTER

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  | DI | /IA F |  | - | _ | _                   |                                          | _                      | ENG                                         | тн                           |                                |                                 |                      |                       |                      |                   |           |      |     |     |     |